第五章 同步时序逻辑电路

- 格式:ppt

- 大小:682.50 KB

- 文档页数:64

第五章时序逻辑电路前面介绍的组合逻辑电路无记忆功能。

而时序逻辑电路的输出状态不仅取决于当时的输入信号,而且与电路原来的状态有关,或者说与电路以前的输入状态有关,具有记忆功能。

触发器是时序逻辑电路的基本单元。

本章讨论的内容为时序逻辑电路的分析方法、寄存器和计数器的原理及应用。

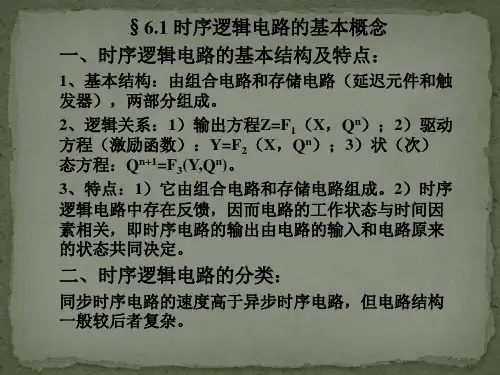

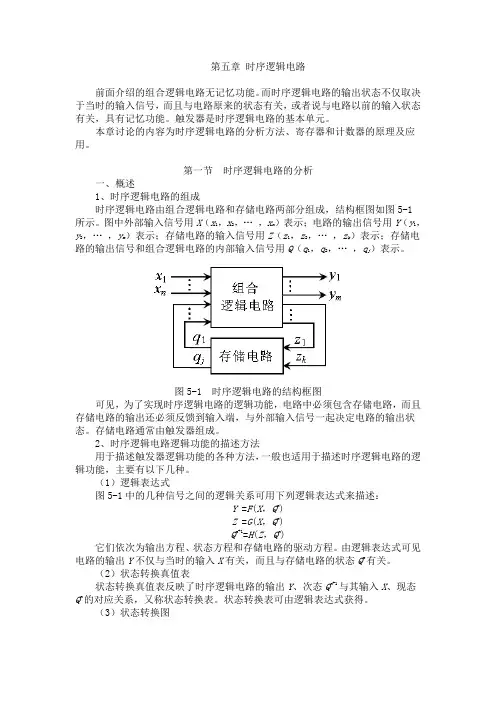

第一节时序逻辑电路的分析一、概述1、时序逻辑电路的组成时序逻辑电路由组合逻辑电路和存储电路两部分组成,结构框图如图5-1所示。

图中外部输入信号用X(x1,x2,…,x n)表示;电路的输出信号用Y(y1,y,…,y m)表示;存储电路的输入信号用Z(z1,z2,…,z k)表示;存储电2路的输出信号和组合逻辑电路的内部输入信号用Q(q1,q2,…,q j)表示。

图5-1 时序逻辑电路的结构框图可见,为了实现时序逻辑电路的逻辑功能,电路中必须包含存储电路,而且存储电路的输出还必须反馈到输入端,与外部输入信号一起决定电路的输出状态。

存储电路通常由触发器组成。

2、时序逻辑电路逻辑功能的描述方法用于描述触发器逻辑功能的各种方法,一般也适用于描述时序逻辑电路的逻辑功能,主要有以下几种。

(1)逻辑表达式图5-1中的几种信号之间的逻辑关系可用下列逻辑表达式来描述:Y =F(X,Q n)Z =G(X,Q n)Q n+1=H(Z,Q n)它们依次为输出方程、状态方程和存储电路的驱动方程。

由逻辑表达式可见电路的输出Y不仅与当时的输入X有关,而且与存储电路的状态Q n有关。

(2)状态转换真值表状态转换真值表反映了时序逻辑电路的输出Y、次态Q n+1与其输入X、现态Q n的对应关系,又称状态转换表。

状态转换表可由逻辑表达式获得。

(3)状态转换图状态转换图又称状态图,是状态转换表的图形表示,它反映了时序逻辑电路状态的转换与输入、输出取值的规律。

(4)波形图波形图又称为时序图,是电路在时钟脉冲序列CP的作用下,电路的状态、输出随时间变化的波形。

应用波形图,便于通过实验的方法检查时序逻辑电路的逻辑功能。

思考题与习题题解5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与电路原来所处的状态无关;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与信号作用前电路原来所处的状态有关。

(2)构成一异步2n进制加法计数器需要n 个触发器,一般将每个触发器接成计数或T’型触发器。

计数脉冲输入端相连,高位触发器的CP端与邻低位Q端相连。

(3)一个4位移位寄存器,经过 4 个时钟脉冲CP后,4位串行输入数码全部存入寄存器;再经过4个时钟脉冲CP后可串行输出4位数码。

(4)要组成模15计数器,至少需要采用 4 个触发器。

5-2判断题(1)异步时序电路的各级触发器类型不同。

(×)(2)把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。

(×)(3)具有N个独立的状态,计满N个计数脉冲后,状态能进入循环的时序电路,称之模N计数器。

(√)(4)计数器的模是指构成计数器的触发器的个数。

(×)5-3单项选择题(1)下列电路中,不属于组合逻辑电路的是(D)。

A.编码器B.译码器C.数据选择器D.计数器(2)同步时序电路和异步时序电路比较,其差异在于后者( B)。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关(3)在下列逻辑电路中,不是组合逻辑电路的有( D)。

A.译码器B.编码器C.全加器D.寄存器(4)某移位寄存器的时钟脉冲频率为完成该操作需要(B)时间。

100KHz,欲将存放在该寄存器中的数左移8位,A.10μSB.80μSC.100μSD.800ms(5)用二进制异步计数器从0做加法,计到十进制数178,则最少需要(C )个触发器。

A.6B.7C.8D.10(6)某数字钟需要一个分频器将32768Hz的脉冲转换为1HZ的脉冲,欲构成此分频器至少需要(B)个触发器。

A.10B.15C.32D.32768(7)一位8421BCD 码计数器至少需要(B)个触发器。

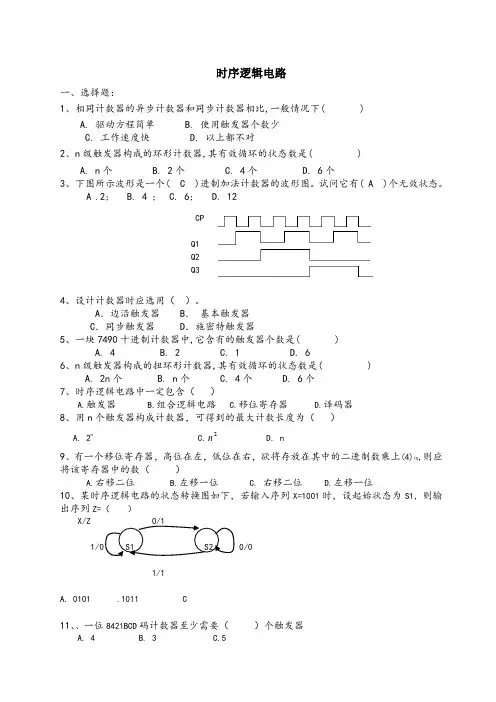

时序逻辑电路一、选择题:1、相同计数器的异步计数器和同步计数器相比,一般情况下( )A. 驱动方程简单B. 使用触发器个数少C. 工作速度快D. 以上都不对2、n级触发器构成的环形计数器,其有效循环的状态数是( )A. n个B. 2个C. 4个D. 6个3、下图所示波形是一个( C )进制加法计数器的波形图。

试问它有( A )个无效状态。

A .2; B. 4 ; C. 6; D. 12CPQ1Q2Q34、设计计数器时应选用()。

A.边沿触发器 B.基本触发器C.同步触发器 D.施密特触发器5、一块7490十进制计数器中,它含有的触发器个数是( )A. 4B. 2C. 1D. 66、n级触发器构成的扭环形计数器,其有效循环的状态数是( )A. 2n个B. n个C. 4个D. 6个7、时序逻辑电路中一定包含()A.触发器B.组合逻辑电路C.移位寄存器D.译码器8、用n个触发器构成计数器,可得到的最大计数长度为()A. 2n C.2n D.n9、有一个移位寄存器,高位在左,低位在右,欲将存放在其中的二进制数乘上(4)10,则应将该寄存器中的数()A.右移二位B.左移一位C. 右移二位D.左移一位10、某时序逻辑电路的状态转换图如下,若输入序列X=1001时,设起始状态为S1,则输出序列Z=()X/Z 0/11/0 S1 S2 0/01/1A. 0101 .1011 C11、、一位8421BCD码计数器至少需要()个触发器A. 4B. 3C.512、利用中规模集成计数器构成任意进制计数器的方法有( ABC )A.复位法 B .预置数法 C .级联复位法 13、在移位寄存器中采用并行输出比串行输出 ( )。

A.快B.慢C.一样快D.不确定14、用触发器设计一个24进制的计数器,至少需要( )个触发器。

A. 5 .4 C D. 315、在下列逻辑电路中,不是组合逻辑电路的有( )。

A. 寄存器B.编码器C.全加器D. 译码器 16、一个 4 位移位寄存器可以构成最长计数器的长度是( )。

同步时序逻辑电路的设计同步时序逻辑电路是一种电路设计技术,它通过使用锁存器和触发器等特定的时钟信号来确保电路的操作在特定的时间序列内发生。

在本文中,我们将讨论同步时序逻辑电路的设计原理和流程,并通过一个实际的案例来说明如何设计一个同步时序逻辑电路。

同步时序逻辑电路的设计原理主要基于时钟信号的使用。

时钟信号是一个周期性的脉冲信号,它指示了电路中各个操作的发生时机。

同步时序逻辑电路中的数据操作只能在时钟信号的上升沿或下降沿发生,这样可以确保数据的稳定性和一致性。

1.确定需求和功能:首先,需要明确电路的需求和功能。

这包括输入输出信号的数量和特性,以及电路要实现的逻辑功能。

2.确定时钟信号:根据电路的需求和功能,确定时钟信号的频率和周期。

时钟信号的频率决定了电路操作的速度,周期决定了电路操作的时间序列。

3.确定触发器和锁存器:根据电路的需求和功能,选择适合的触发器和锁存器来实现电路的时序控制。

触发器和锁存器是存储元件,可以存储和传输电路中的数据。

4.确定逻辑门和电路结构:根据电路的需求和功能,选择适合的逻辑门来实现电路的逻辑功能。

逻辑门是将输入信号进行逻辑运算的元件,常见的逻辑门有与门、或门和非门等。

5.进行逻辑设计:根据电路的需求和功能,进行逻辑设计。

逻辑设计包括将输入信号经过逻辑门的运算得到输出信号的表达式,以及设计触发器和锁存器的实现电路。

6.进行位宽设计:根据电路的需求和功能,确定各个信号的位宽。

位宽是指信号在逻辑门和触发器中占据的位数,它决定了电路的运算和存储的精度和范围。

7.进行时序设计:根据电路的需求和功能,进行时序设计。

时序设计包括确定电路的时钟信号的频率和周期,以及电路操作在时钟信号的上升沿或下降沿发生。

8.进行电路调试:将设计好的电路进行实现和调试。

可以使用常见的电路设计软件进行仿真和验证,以确保电路的正确性和可靠性。

以上就是同步时序逻辑电路的设计原理和流程。

下面我们将通过一个实际的案例来说明如何设计一个同步时序逻辑电路。

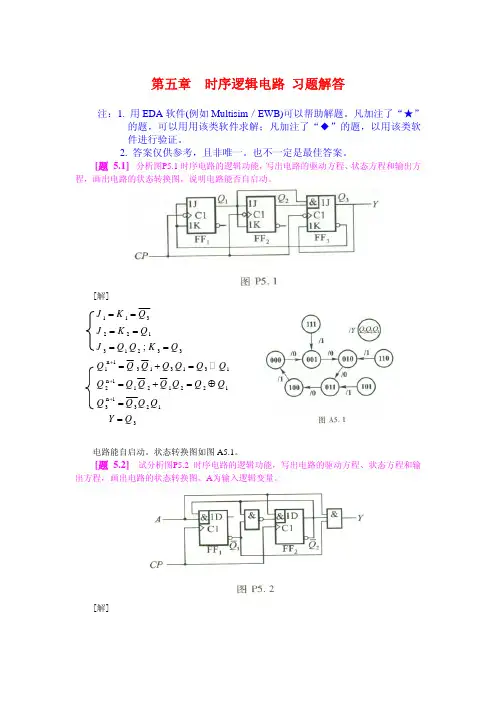

第五章 时序逻辑电路 习题解答注:1. 用EDA 软件(例如Multisim /EWB)可以帮助解题。

凡加注了“★”的题,可以用用该类软件求解;凡加注了“◆”的题,以用该类软件进行验证。

2. 答案仅供参考,且非唯一。

也不一定是最佳答案。

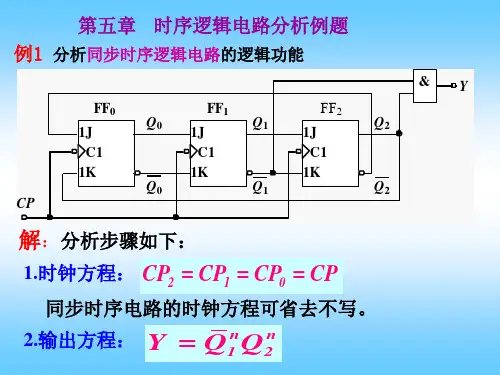

[题 5.1] 分析图P5.1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

[解]11322131233n 113131n 1212212n 133213311;J K Q J K Q J Q Q K Q Q Q Q Q Q QQ Q Q Q Q Q Q Q Q Q Q Q Y Q +++=======+==+=⊕==电路能自启动。

状态转换图如图A5.1。

[题 5.2] 试分析图P5.2时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入逻辑变量。

[解]12212+12n 112n 1212 ()(+)D A Q D A Q Q A Q Q QAQ Q A Q Q ++===== 21=Y A Q Q电路的状态转换图如图A5.2。

[题 5.3] 试分析图P5.3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。

[解]12312121331232n 11231n 12123132n+13123223;1 ; ;=J Q Q K J Q K Q Q J Q Q K Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Y Q Q ++=======+=+= 电路的状态转换图如图A5.3。

电路能自启动。

[题 5.4] 分析图P5.4给出的时序电路,画出电路的状态转换图,检查电路能否自启动,说明电路实现的功能。

A 为输入变量。

[解]n+11111n 122221212121=+J K Q Q J K A Q Q A Q Q Y A Q Q A Q Q +=====⊕=⊕⊕电路状态转换图如图A5.4。