5、F28335存储器以及地址分配全解

- 格式:ppt

- 大小:1.02 MB

- 文档页数:10

T M S320F28335中文资料TMS320F28335中文资料TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序。

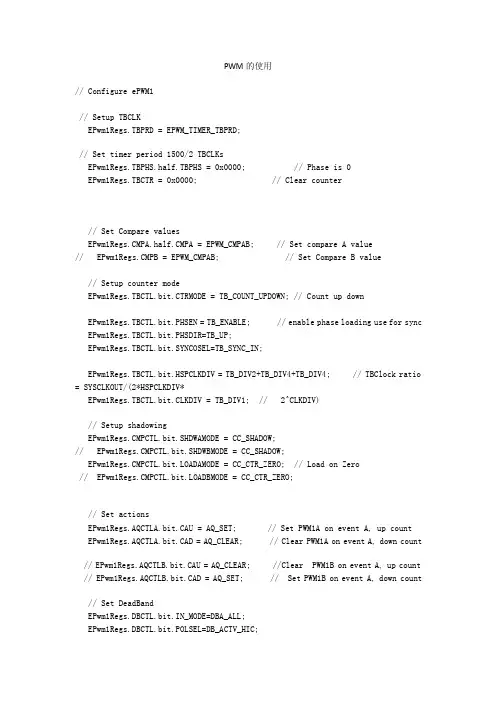

PWM的使用// Configure ePWM1// Setup TBCLKEPwm1Regs.TBPRD = EPWM_TIMER_TBPRD;// Set timer period 1500/2 TBCLKsEPwm1Regs.TBPHS.half.TBPHS = 0x0000; // Phase is 0EPwm1Regs.TBCTR = 0x0000; // Clear counter// Set Compare valuesEPwm1Regs.CMPA.half.CMPA = EPWM_CMPAB; // Set compare A value// EPwm1Regs.CMPB = EPWM_CMPAB; // Set Compare B value// Setup counter modeEPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up downEPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE; // enable phase loading use for sync EPwm1Regs.TBCTL.bit.PHSDIR=TB_UP;EPwm1Regs.TBCTL.bit.SYNCOSEL=TB_SYNC_IN;EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV2+TB_DIV4+TB_DIV4; // TBClock ratio = SYSCLKOUT/(2*HSPCLKDIV*EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; // 2^CLKDIV)// Setup shadowingEPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;// EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero// EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;// Set actionsEPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on event A, up count EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR; // Clear PWM1A on event A, down count// EPwm1Regs.AQCTLB.bit.CAU = AQ_CLEAR; //Clear PWM1B on event A, up count // EPwm1Regs.AQCTLB.bit.CAD = AQ_SET; // Set PWM1B on event A, down count// Set DeadBandEPwm1Regs.DBCTL.bit.IN_MODE=DBA_ALL;EPwm1Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;EPwm1Regs.DBCTL.bit.OUT_MODE=DB_FULL_ENABLE;EPwm1Regs.DBRED=Dbred; // Dead-band rising edge delayEPwm1Regs.DBFED=Dbfed; // Dead-band falling edge delay// Set Trip ZoneEPwm1Regs.TZSEL.bit.OSHT1=TZ_ENABLE;EPwm1Regs.TZCTL.bit.TZA=TZ_FORCE_LO;EPwm1Regs.TZCTL.bit.TZB=TZ_FORCE_LO;// Interrupt where we will change the Compare ValuesEPwm1Regs.ETSEL.bit.SOCBSEL= ET_CTR_ZERO;// Select start ADC (EPWMxSOCB) on Zero eventEPwm1Regs.ETSEL.bit.SOCBEN= Enable; // EnableEPwm1Regs.ETPS.bit.SOCBPRD=ET_1ST;主要注意的就是EPWM的死区子模块。

Tms320F28335中AD采样存储地址问题记录最近使⽤Tms320F28335采样程序,将容易误解的地⽅分享个⼈看法。

⽅便后来⼩朋友们少⾛弯路,也提醒⾃⼰。

(如有错误,请⼤家多多指导。

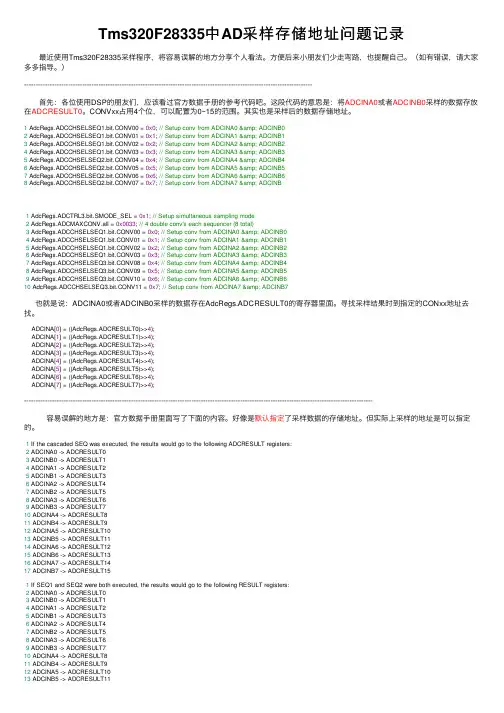

)----------------------------------------------------------------------------------------------------------------------------⾸先:各位使⽤DSP的朋友们,应该看过官⽅数据⼿册的参考代码吧。

这段代码的意思是:将ADCINA0或者ADCINB0采样的数据存放在ADCRESULT0。

CONVxx占⽤4个位,可以配置为0~15的范围。

其实也是采样后的数据存储地址。

1 AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB02 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB13 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB24 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB35 AdcRegs.ADCCHSELSEQ2.bit.CONV04 = 0x4; // Setup conv from ADCINA4 & ADCINB46 AdcRegs.ADCCHSELSEQ2.bit.CONV05 = 0x5; // Setup conv from ADCINA5 & ADCINB57 AdcRegs.ADCCHSELSEQ2.bit.CONV06 = 0x6; // Setup conv from ADCINA6 & ADCINB68 AdcRegs.ADCCHSELSEQ2.bit.CONV07 = 0x7; // Setup conv from ADCINA7 & ADCINB1 AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1; // Setup simultaneous sampling mode2 AdcRegs.ADCMAXCONV.all = 0x0033; // 4 double conv's each sequencer (8 total)3 AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB04 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB15 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB26 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB37 AdcRegs.ADCCHSELSEQ3.bit.CONV08 = 0x4; // Setup conv from ADCINA4 & ADCINB48 AdcRegs.ADCCHSELSEQ3.bit.CONV09 = 0x5; // Setup conv from ADCINA5 & ADCINB59 AdcRegs.ADCCHSELSEQ3.bit.CONV10 = 0x6; // Setup conv from ADCINA6 & ADCINB610 AdcRegs.ADCCHSELSEQ3.bit.CONV11 = 0x7; // Setup conv from ADCINA7 & ADCINB7也就是说:ADCINA0或者ADCINB0采样的数据存在AdcRegs.ADCRESULT0的寄存器⾥⾯。

EPWMTMSF28335所需配置的EPWM寄存器一.TB模块需要设置的寄存器TBCTL_BITS {// bits descriptionUint16 CTRMODE:2; // 1:0 Counter ModeUint16 PHSEN:1; // 2 Phase load enable Uint16 PRDLD:1; // 3 Active period load Uint16 SYNCOSEL:2; // 5:4 Sync output select Uint16 SWFSYNC:1; // 6 Software force sync pulseUint16 HSPCLKDIV:3; // 9:7 High speed time pre-scaleUint16 CLKDIV:3; // 12:10 Timebase clock pre-scaleUint16 PHSDIR:1; // 13 Phase DirectionUint16 FREE_SOFT:2; // 15:14 Emulation mode1.TBCTL:TB控制寄存器设置TBCTL_REG.BITS.CTRMODE:2 (计数模式设置)TB_COUNT-UP 0x0;TB_COUNT_DOWN 0x1;TB_COUNT_UPDOWN 0x2;TB_FREEZE 0x3;TBCTL_REG.BITS.PHSEN:1 (相位装载使能控制)TB_DISABLE 0x0;TB_ENABLE 0x1; 直接将计数器中的值装载到TBCTR计数控制寄存器中。

TBCTL_REG.BITS.PRDLD:1 (时基周期映射使能)TB_SHADOW 0x0 使能TBPRD映射寄存器,读写TBPRD寄存器地址直接操作映射寄存器,当时基计数器计数值等于0时,映射寄存器内容传送到工作寄存器。

默认状态下TBPRD映射寄存器被使能。

TB_IMMEDIATE 0x1 立即装载模式,不需要等到时基计数器计数值等于0时,就直接将TBPRD的存储地址直接操作工作寄存器中。

dspf28335启动过程1.DSP reset后运行的起始地址是多少?0x3FFFC02.仿真器烧写程序的步骤是?根据cmd文件把程序烧到指定位置,然后执行。

3.DSP的Flash启动过程是什么?首先硬件配置GPIO84~87上拉为1,即处于Flash启动过程。

当DSP复位后,会从复位向量0x3FFFC0处取得复位向量,并跳转到InitBoot处开始执行,InitBoot会读GPIO84~87的值发现全为1判断为Flash启动方式。

然后会跳到0x33FFF6处执行。

在CCS5.2工程的cmd文件中有如下代码:MEMORY{PAGE 0 :BEGIN : origin = 0x33FFF6, length = 0x000002 /* Boot to M0 will go here */...}SECTIONS{...codestart : > BEGIN PAGE = 0...}即表示把codestart段放到0x33FFF6位置处,文件“DSP2833x_CodeStartBranch.asm”中有codestart段的定义,实际上codestart段只是包含了一个跳转指令,是程序跳转到_c_int00处,_c_int00在boot.asm in RTS library中有定义,_c_int00的代码最终会调用c的main 函数,之后就是main函数的执行。

总的就是:Reset(0x3fffc0)—>initBoot()—>判断启动方式—>codestart(0x33fff6)—>_c_int00—>main函数4.F28335如何烧写代码到flash中并运行?首先使用添加C:\ti\controlSUITE\device_support\f2833x\v133\DSP2833x_com mon\cmd\F28335.cmd。

此文件即为配置代码到flash中的TI官方配置文件。

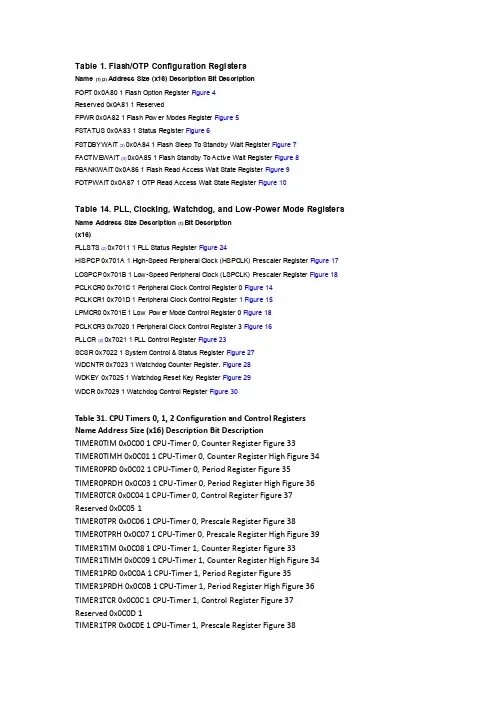

Table 1. Flash/OTP Configuration RegistersName (1) (2) Address Size (x16) Description Bit D escriptionFOP T 0x0A80 1 Flash Option Register Figure 4Reserved 0x0A81 1 ReservedFP WR 0x0A82 1 Flash P ow er Modes Register Figure 5FSTATUS 0x0A83 1 Status Register Figure 6FSTDBYWAIT (3) 0x0A84 1 Flash Sleep To Standby Wait Register Figure 7FACTIVE WAIT (3) 0x0A85 1 Flash Standby To Acti v e Wait Register Figure 8 FBANKWAIT 0x0A86 1 Flash Read Access Wait State Register Figure 9FOTPWAIT 0x0A87 1 OTP Read Access Wait State Register Figure 10Table 14. PLL, Clocking, Watchdog, and Low-Power Mode Registers Name Address Size Description (1) Bit Description(x16)P LLSTS (2) 0x7011 1 P LL Status Register Figure 24HISPCP 0x701A 1 High-Speed P eripheral Clock (HSPCLK) P rescaler Register Figure 17 LOSPCP 0x701B 1 Low-Speed P eripheral Clock (LSPCLK) P rescaler Register Figure 18 PCLKCR0 0x701C 1 P eripheral Clock Control Register 0 Figure 14PCLKCR1 0x701D 1 P eripheral Clock Control Register 1 Figure 15LPMCR0 0x701E 1 Low P ow er Mode Control Register 0 Figure 18PCLKCR3 0x7020 1 P eripheral Clock Control Register 3 Figure 16P LLCR (2) 0x7021 1 P LL Control Register Figure 23SCSR 0x7022 1 System Control & Status Register Figure 27WDCNTR 0x7023 1 Watchdog Counter Register. Figure 28WDKE Y 0x7025 1 Watchdog Reset Key Register Figure 29WDCR 0x7029 1 Watchdog Control Register Figure 30Table 31. CPU Timers 0, 1, 2 Configuration and Control RegistersName Address Size (x16) Description Bit DescriptionTIMER0TIM 0x0C00 1 CPU-Timer 0, Counter Register Figure 33TIMER0TIMH 0x0C01 1 CPU-Timer 0, Counter Register High Figure 34 TIMER0PRD 0x0C02 1 CPU-Timer 0, Period Register Figure 35TIMER0PRDH 0x0C03 1 CPU-Timer 0, Period Register High Figure 36 TIMER0TCR 0x0C04 1 CPU-Timer 0, Control Register Figure 37Reserved 0x0C05 1TIMER0TPR 0x0C06 1 CPU-Timer 0, Prescale Register Figure 38TIMER0TPRH 0x0C07 1 CPU-Timer 0, Prescale Register High Figure 39 TIMER1TIM 0x0C08 1 CPU-Timer 1, Counter Register Figure 33TIMER1TIMH 0x0C09 1 CPU-Timer 1, Counter Register High Figure 34 TIMER1PRD 0x0C0A 1 CPU-Timer 1, Period Register Figure 35TIMER1PRDH 0x0C0B 1 CPU-Timer 1, Period Register High Figure 36 TIMER1TCR 0x0C0C 1 CPU-Timer 1, Control Register Figure 37Reserved 0x0C0D 1TIMER1TPR 0x0C0E 1 CPU-Timer 1, Prescale Register Figure 38TIMER1TPRH 0x0C0F 1 CPU-Timer 1, Prescale Register High Figure 39TIMER2TIM 0x0C10 1 CPU-Timer 2, Counter Register Figure 33TIMER2TIMH 0x0C11 1 CPU-Timer 2, Counter Register High Figure 34TIMER2PRD 0x0C12 1 CPU-Timer 2, Period Register Figure 35TIMER2PRDH 0x0C13 1 CPU-Timer 2, Period Register High Figure 36TIMER2TCR 0x0C14 1 CPU-Timer 2, Control Register Figure 37Reserved 0x0C15 1TIMER2TPR 0x0C16 1 CPU-Timer 2, Prescale Register Figure 38TIMER2TPRH 0x0C17 1 CPU-Timer 2, Prescale Register High Figure 39Table 39. GPIO Control RegistersName (1) Address Size (x16) Register Description Bit DescriptionGPACTRL 0x6F80 2 GPIO A Control Register (GPIO0-GPIO31) Figure 53GPAQSEL1 0x6F82 2 GPIO A Qualifier Select 1 Register (GPIO0-GPIO15) Figure 55 GPAQSEL2 0x6F84 2 GPIO A Qualifier Select 2 Register (GPIO16-GPIO31) Figure 56 GPAMUX1 0x6F86 2 GPIO A MUX 1 Register (GPIO0-GPIO15) Figure 47GPAMUX2 0x6F88 2 GPIO A MUX 2 Register (GPIO16-GPIO31) Figure 48GPADIR 0x6F8A 2 GPIO A Direction Register (GPIO0-GPIO31) Figure 59GPAPUD 0x6F8C 2 GPIO A Pull Up Disable Register (GPIO0-GPIO31) Figure 62GPBCTRL 0x6F90 2 GPIO B Control Register (GPIO32-GPIO63) Figure 54GPBQSEL1 0x6F92 2 GPIO B Qualifier Select 1 Register (GPIO32-GPIO47) Figure 57 GPBQSEL2 0x6F94 2 GPIO B Qualifier Select 2 Register (GPIO48 - GPIO63) Figure 58 GPBMUX1 0x6F96 2 GPIO B MUX 1 Register (GPIO32-GPIO47) Figure 49GPBMUX2 0x6F98 2 GPIO B MUX 2 Register (GPIO48-GPIO63) Figure 50GPBDIR 0x6F9A 2 GPIO B Direction Register (GPIO32-GPIO63) Figure 60GPBPUD 0x6F9C 2 GPIO B Pull Up Disable Register (GPIO32-GPIO63) Figure 63GPCMUX1 0x6FA6 2 GPIO C MUX 1 Register (GPIO64-GPIO79) Figure 51GPCMUX2 0x6FA8 2 GPIO C MUX 2 Register (GPIO80-GPIO87) Figure 52GPCDIR 0x6FAA 2 GPIO C Direction Register (GPIO64-GPIO87) Figure 61GPCPUD 0x6FAC 2 GPIO C Pull Up Disable Register (GPIO64-GPIO87) Figure 64(1)The registers in this table are EALLOW protected. See Section 7.2 for more information. Table 40. GPIO Interrupt and Low Power Mode Select RegistersName (1) Address Size Register Description Bit Description (x16)GPIOXINT1SEL 0x6FE0 1 XINT1 Source Select Register (GPIO0-GPIO31) Figure 71 GPIOXINT2SEL 0x6FE1 1 XINT2 Source Select Register (GPIO0-GPIO31) Figure 71 GPIOXNMISEL 0x6FE2 1 XNMI Source Select Register (GPIO0-GPIO31) Figure 71 GPIOXINT3SEL 0x6FE3 1 XINT3 Source Select Register (GPIO32 - GPIO63) Table 82 GPIOXINT4SEL 0x6FE4 1 XINT4 Source Select Register (GPIO32 - GPIO63) Table 82 GPIOXINT5SEL 0x6FE5 1 XINT5 Source Select Register (GPIO32 - GPIO63) Table 82 GPIOXINT6SEL 0x6FE6 1 XINT6 Source Select Register (GPIO32 - GPIO63) Table 82 GPIOXINT7SEL 0x6FE7 1 XINT7 Source Select Register (GPIO32 - GPIO63) Table 82GPIOLPMSEL 0x6FE8 1 LPM wakeup Source Select Register (GPIO0-GPIO31) Figure 72Table 41. GPIO Data RegistersName Address Size (x16) Register D escription Bit DescriptionGP ADAT 0x6FC0 2 GPIO A Data Register (GPIO0-GPIO31) Figure 65GP ASE T 0x6FC2 2 GPIO A Set Register (GPIO0-GPIO31) Figure 68GP ACLE AR 0x6FC4 2 GPIO A Clear Register (GPIO0-GPIO31) Figure 68GP ATOGGLE 0x6FC6 2 GPIO A Toggle Register (GPIO0-GPIO31) Figure 68GPBDAT 0x6FC8 2 GPIO B Data Register (GPIO32-GPIO63) Figure 66GPBSE T 0x6FCA 2 GPIO B Set Register (GPIO32-GPIO63) Figure 69GPBCLE AR 0x6FCC 2 GPIO B Clear Register (GPIO32-GPIO63) Figure 69GPBTOGGLE 0x6FCE 2 GPIO B Toggle Register (GP IO32-GP IO63) Figure 69Table 41. GPIO Data Registers (continued)Name Address Size (x16) Register D escription Bit DescriptionGPCDAT 0x6FD0 2 GPIO C Data Register (GPIO64 - GPIO87) Figure 67GPCSET 0x6FD2 2 GPIO C Set Register (GPIO64 - GPIO87) Figure 70GPCCLE AR 0x6FD4 2 GPIO C Clear Register (GP IO64 - GPIO87) Figure 70GPCTOGGLE 0x6FD6 2 GPIO C Toggle Register (GP IO64 - GPIO87) Figure 70Table 46. Default State of Peripheral InputPeripheral Input Description Default Input (1)TZ1-TZ6 Trip zone 1-6 1EP WMSYNCI eP WM Synch Input 0ECAP neCAP input 1E QEPnAeQEP input 1E QEPnIeQEP index 1E QEPnSeQEP strobe 1SPICLKx SPI clock 1SPISTE x SPI transmit enable 0SPISIMOx SPI Slave-in, master-out 1SPISOMIx SPI Slave-out, master-in 1SCIRXDx SCI receive 1CANRXx CAN receive 1SDAA I2C data 1SCLA1 I2C clock 1。

通过串口SCI更新DSP28335的用户程序一、FLASH地址分配及cmd文件改写1.存储器flash分配0x30 0000 - 0x30 7FFF FLASHH0x30 8000 - 0x30 FFFF FLASHG0x31 0000 - 0x31 7FFF FLASHF0x31 8000 - 0x31 FFFF FLASHE0x32 0000 - 0x32 7FFF FLASHD0x32 8000 - 0x32 FFFF FLASHC0x33 0000 - 0x33 7FFF FLASHB0x33 8000 - 0x33 FF7F FLASHA/*内存分配* 用户程序可写入下面的区域,目前128K,如果不够还可以将F盘添加进来;* 也可将A盘添加进来,但是A盘有程序锁,添加该部分需要做相应的处理。

** FLASHE : origin = 0x318000, length = 0x008000 // on-chip FLASH* FLASHD : origin = 0x320000, length = 0x008000 // on-chip FLASH* FLASHC : origin = 0x328000, length = 0x008000 // on-chip FLASH* FLASHB : origin = 0x330000, length = 0x008000 // on-chip FLASH**USER_CODE: SECTORB|SECTORC|SECTORD|SECTORE *BOOT_LOADER_CODE: SECTORG|SECTORF //(F 盘为BOOT备用盘,目前没有使用)* FLASH_API_CODE: SECTORH2.cmd文件其中用户程序中的cmd文件请注意:我把codestart写到了FLASHE的起始地址,这样当升级完程序后bootload程序应该接着运行USER_CODE段,此段正好在FLASHE中,所以程序就开始从更新的用户程序运行。

TMS320F28335中⽂资料资料讲解T M S320F28335中⽂资料TMS320F28335中⽂资料TMS320F28335采⽤176引脚LQFP四边形封装,其功能结构参见参考⽂献。

其主要性能如下:⾼性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;⾼性能的32位CPU,单精度浮点运算单元(FPU),采⽤哈佛流⽔线结构,能够快速执⾏中断响应,并具有统⼀的内存管理模式,可⽤C/C++语⾔实现复杂的数学算法;6通道的DMA控制器;⽚上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有⽚上振荡器,看门狗模块,⽀持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU 的输⼊时钟频率;8个外部中断,相对TMS320F281X系列的DSP,⽆专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00⼀GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3⼀XINT7外部中断;⽀持58个外设中断的外设中断扩展控制器(PIE),管理⽚上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个⾼分辨率脉宽调制模块(HRPWM)、6个事件捕获输⼊,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1⽤作⼀般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2⽤于DSP /BIOS的⽚上实时系统,连接到中断INTl4,如果系统不使⽤DSP/BIOS,定时器2可⽤于⼀般定时器;串⾏外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串⾏接⼝)模块、1个SPI模块、1个I2C主从兼容的串⾏总线接⼝模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时⽀持多通道转换;88个可编程的复⽤GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的⽚内扫描仿真接⼝(JTAG);TMS320F28335的存储器映射需注意以下⼏点:⽚上外设寄存器块0~3只能⽤于数据存储区,⽤户不能在该存储区内写⼊程序。

DSP程序中寄存器如何分配地址DSP中某个寄存器怎么分配地址?在数据⼿册中,我们常常看到说某个寄存器地址是多少,以TMS320F28335的时钟系统寄存器为例,在ti公司给出的⼿册我们看到如下信息我们看到HISPCP中的地址为0x701A;翻看ti公司给的⼀系列库我们发现其寄存器定义在结构体SYS_CTRL_REGS中,经过⼀系列查找,我们发现SYS_CTRL_REGS映射的是 DSP281x_Headers_nonBIOS.cmd⽂件中,其对应的地址映射是System:0我们发现其⾸地址是0x7010;⽽resvd1不代表任何含义,仅仅⽅便位置偏移设数,⽽结构体中HISPCP前⾯有10个16进制变量,HISPCP是第11个,在C语⾔中,下标是从0开始,所有HISPCP是第10个,也就是A,那么HISPCP地址是0x701A,查看芯⽚数据发现吻合,相关内容,可参考下⾯⼀⽚博客⽤过F2812的朋友⼀定会对cmd⽂件很熟悉,因为这个⽂件中为每个程序和数据分配了相应的地址。

我们常⽤的cmd⽂件包括连个:(1) DSP281x_Headers_nonBIOS.cmd(2) F2812_EzDSP_RAM_lnk.cmdDSP281x_Headers_nonBIOS.cmd上⾯第⼀个⽂件⽤于对DSP外设分配地址,⽽第⼆个⽂件是为系统的程序和数据分配地址。

当然,如果DSP的外设地址我们⽤C 语⾔已经⾃⼰定义,那第⼀个⽂件我们就可以不⽤了,笔者就是⾃⼰定义的,所以没有⽤到第⼀个⽂件。

对于为什么要⾃⼰定义外设寄存器以及中断地址,有这⼏个原因:(1) ⾃⼰定义外设寄存器地址可以很清楚的了解DSP的⼯作原理,虽然这样很耗费时间,但是会了解到DSP的中断等等是怎么⼯作的。

(2) 因为DSP外设寄存器地址的分配时采⽤寄存器形式分配到的。

举个例⼦,以sci串⼝通信为例,其他的外设以及中断都⼀样。

⽐如我们设置波特率,肯定是设置某个寄存器的相应位来实现。