基于FPGA的DDC(数字下变频)设计与实现

- 格式:docx

- 大小:1.43 MB

- 文档页数:45

基于FPGA的多相DDC设计与实现摘要:雷达数字接收机中往往存在前端ADC输出的高速数据流与后端DSP的低吞吐率之间难以匹配的问题。

因此,本文从工程角度出发,给出了一种基于现场可编程门阵列(FPGA,Field Programmable Gate Array)的数字下变频设计方案,通过对中频信号分为4相处理以及对FIR滤波器、NCO模块进行优化,在得到有效信号的同时可以节省部分资源。

关键词:DDC;FPGA;FIR滤波器;NCO;0 引言为了提高雷达系统的作用距离和分辨力,数字阵列雷达必须具有较大的时宽和带宽,同时也就需要较高的采样率。

这就推动着高速采样器件的不断发展,使中频采样甚至射频直接采样成为可能。

然而,高速采样器件与数字信号处理器件的处理速度往往不在一个量级,很大程度上限制了电子侦察系统的发展。

目前,解决这一问题的通用方法是:高频模拟信号先进行模拟下变频至中频,AD采样中频信号,然后通过数字下变频技术,使高速率的中频信号变为低速率的基带信号,提供给后端进行数字信号处理。

同时,FPGA因其开发成本低、研发周期短、灵活方便等优点,成为复杂的数字电路或器件开发的必备手段。

因此,本文介绍一种基于FPGA的多相DDC技术,将高速率的中频信号进行多相DDC处理变为低速率的基带信号。

1 多相DDC的设计1.1DDC基本架构数字下变频(Digital Down Converter-DDC)是指将数字中频信号下变频至零中频且使数据率降至适宜DSP处理的过程。

其基本架构如图1所示,主要由数字混频器、数字控制振荡器(Numerically Controlled Osillator-NCO)、FIR滤波器以及抽取等部分构成。

图1 DDC基本架构示意图NCO产生正交本振信号送入数字混频器中,对A/D采样得到的中频信号进行混频处理,处理结果传入FIR滤波器以滤除谐波分量以及带外信号,再经过抽取模块降低数据率。

1.2多相DDC架构本实验中采用的A/D转换芯片为AD9680,有效位数14位,采样率设置为800M,中心频率为600M,传输方式采用204b协议。

软件无线电数字下变频技术研究及FPGA实现发布时间:2011-1-18 发布人:21世纪电子网软件无线电的核心思想是以模块化、标准化的硬件功能单元构建一个具有高度灵活性、开放性的通用硬件平台,将高速、宽带的A/D、D/A尽可能地靠近天线,通过软件编程的方式实现通信系统的各种功能,从而屏蔽不同通信系统的差异,实现多个通信系统的互通与兼容。

数字下变频DDC(Digitial Down Conversion)是软件无线电接收系统构成的核心,它主要是把A/D技术应用于中频信号,通过软件编程实现混频、抽取和滤波等信号处理功能,以数字化方式将中频信号搬移至基带并同时降低数据速率。

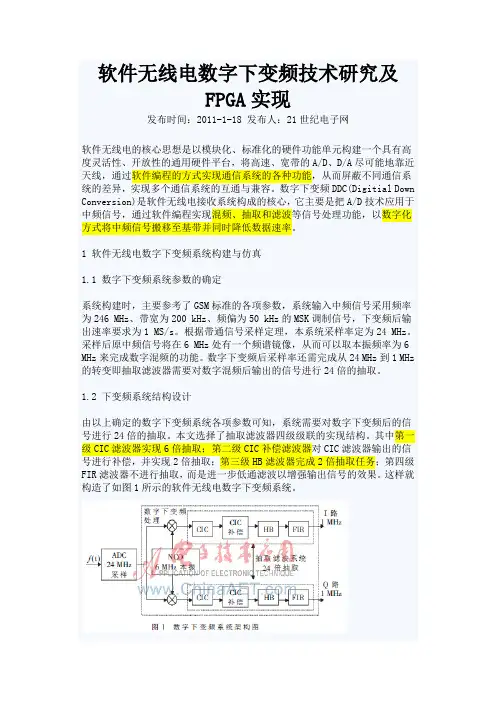

1 软件无线电数字下变频系统构建与仿真1.1 数字下变频系统参数的确定系统构建时,主要参考了GSM标准的各项参数,系统输入中频信号采用频率为246 MHz、带宽为200 kHz、频偏为50 kHz的MSK调制信号,下变频后输出速率要求为1 MS/s。

根据带通信号采样定理,本系统采样率定为24 MHz。

采样后原中频信号将在6 MHz处有一个频谱镜像,从而可以取本振频率为6 MHz来完成数字混频的功能。

数字下变频后采样率还需完成从24 MHz到1 MHz 的转变即抽取滤波器需要对数字混频后输出的信号进行24倍的抽取。

1.2 下变频系统结构设计由以上确定的数字下变频系统各项参数可知,系统需要对数字下变频后的信号进行24倍的抽取。

本文选择了抽取滤波器四级级联的实现结构。

其中第一级CIC滤波器实现6倍抽取;第二级CIC补偿滤波器对CIC滤波器输出的信号进行补偿,并实现2倍抽取;第三级HB滤波器完成2倍抽取任务;第四级FIR滤波器不进行抽取,而是进一步低通滤波以增强输出信号的效果。

这样就构造了如图1所示的软件无线电数字下变频系统。

1.3 抽取滤波器系统的实现M、D分别为CIC滤波器的抽取倍数和微分延迟因子。

可见其阻带衰减较差,难以满足一般的应用需要。

基于FPGA的高速数字下变频系统设计摘要:基于FPGA设计了一高速数字下变频系统,在设计中利用并行NCO和多相滤波相结合的方法有效的降低了数据的速率,以适合数字信号处理器件的工作频率。

为了进一步提高系统的整体运行速度,在设计中大量的使用了FPGA中的硬核资源DSP48。

Xilinx ISE14.4分析报告显示,电路工作速度可达360MHz。

最后给出了在Matlab和ModelSim中仿真的结果,验证了各个模块以及整个系统的正确性。

数字下变频(Digital Down Conversion,DDC)是软件无线电系统的关键模块之一,其可将高频数据流信号变成易于后端数字信号处理器(Digital Signal Processor,DSP)设备实时处理的低频数据流信号。

在数字下变频实现中,随着信号采样率的不断提高,数据率也会相应的提高,但是实际应用中随着数据速率的不断提高,数据处理器件(如FPGA)的处理速度会无法满足要求而不能正常工作,从而带来了数字信号处理的瓶颈问题。

本设计就是以多路并行NCO技术为基础,研究了如何在FPGA中用多路并行采样数据的方式来解决数据处理器件无法提供高速率的匹配信号的问题,并给出了高速DDC实现的架构和仿真结果。

1 数字下变频基本原理数字下变频主要由频谱搬移和抽取两部分组成,如图1所示,其中频谱搬移包含数控振荡器(Numerically Controlled Oscillators,NCO)、乘法器和低通滤波器(LPF,Low Pass Filter);抽取包含抽取滤波器(LPF2)和D倍的抽取,LPF2是为了限制信号的频谱,以免抽取后发生混叠。

模拟信号经过A/D转换后分成两路信号,一路信号和NCO输出的正弦信号相乘(同相分量),一路和NCO输出的余弦信号相乘(正交分量),之后经过低通滤波器(LPF1)将高频分量滤除,然后信号经过抽取滤波以降低速率,最终输出的两路信号就可以送往后续的数字信号处理器中做进一步的处理。

基于FPGA的数字下变频设计与实现在扩频通信中,数字下变频(DDC)是一种很重要的技术,它包括数字混频器、数控振荡器以及数字滤波器三部分。

而传统的DDC 大多采用专用芯片,虽然其外围电路简单、功能实现容易控制,但其大部分功能已经固化,存在兼容性较差、产品开发灵活性低、后续升级困难等缺陷。

本文利用FPGA 运算快速、易于升级等优点,在简化算法的基础上,用最短的时间进行混频滤波得到两路相交信号。

用Verilog 语言对整个下变频进行行为描述建模,并给出相应的仿真综合结果。

1 正交下变频方案理论分析因为DDC 的数据流是采样信号的速率,DSP 处理芯片很难完成高频实时处理任务,而且FPGA 中通常有大容量ROM 资源,满足查找表所需ROM 资源,所以更适合用FPGA 实现数字正交下变频。

数字正交下变频是借助数控振荡器NCO 通过查找表的方式产生本地正交载波信号,与输入信号进行正交混频,经过低通滤波得到I―Q基带信号。

图1 为其方案框图。

接收机收到的高频信号表达式为:式中,为接收信号的幅值,d(t)为数据信息的波形,c(t)为伪码波形,fc=891 MHz,fd=18.176 MHz 为信号频偏,n(t)为高斯白噪声。

根据带通采样定理,引入单位冲激函数δ(t)构成冲激函数P(t):输入信号为x(t),其傅里叶变换为x(ω),则用fS 抽样后得到抽样信号可表示为:由傅里叶变换性质得到XS(ω),可表示为:由式(5)可知,A/D 采样使信号频谱发生了周期延拓。

中心频率fC=891 MHz(如图2)经带通欠采样后将信号频谱搬移至fO=18.533 MHz。

fO 是fC 除以fS 后的余数。

这样A/D 采样实现了一个下变频功能。

tips:感谢大家的阅读,。

数字下变频基于FPGA的软件设计与实现【摘要】雷达的数字下变频功能主要是将天线接收到的中频回波信号通过A/D变换后,进行数字下变频处理,转为两路I/Q基带数据。

本文主要设计了一种基于FPGA的数字下变频方法,通过对数字控制振荡器(NCO)及低通滤波器(FIR)的设计及实现,完成了对于不同频率本振信号的数字下变频处理。

结果表明,基于该方案设计的数字下变频功能已在实际系统中得到应用。

【关键词】数字下变频(DDC);FPGA;数字滤波器【Abstract】The function of DDC is mainly to convert the signal received after A/D conversion by the antenna to Digital Down Convert(DDC),finally into two I/Q baseband data. This paper mainly design a method about Digital Down Conversion based on FPGA,by designing the numerically controlled oscillator (NCO)and a low-pass filter (FIR),to convert different frequency signal with DDC. The results showed that the conversion function has been used in the actual system.【Key words】DDC(Digital Down Convert);FPGA;FIR Filter0 引言软件无线电是现今无线通信系统的关键技术,其核心思想是让数字化处理功能尽量的靠近天线,从而将更多的处理通过数字的方式完成。

[1]而数字下变频是软件无线电的关键部分,主要完成对信号的AD变换、混频、滤波以及抽取等工作,包括数字混频模块和抽取滤波模块。

基于FPGA的数字下变频器的设计作者:周军晓王明远来源:《硅谷》2013年第13期摘要数字下变频系统为实现数字信号处理器件处理低速数据的性能,提供了降低数模转换器的数据流的速率的功效,是软件无线电接收机中关键的一部分,因此,高性能的数字下变频器是能够保证软件无线电系统的稳定性。

本设计重点对数字下变频的各个模块的实现方法进行深入研究,在一块FPGA芯片上实现数字下变频系统。

关键词软件无线电;数字下变频器;FPGA中图分类号:TN773 文献标识码:A 文章编号:1671-7597(2013)13-0049-01软件无线电是在通用的标准化的硬件平台上实现的,是通过加载不同的通信软件进而实现各种通信方式的转换,形成一个较好兼容性与可编程性的软件无线电台。

其体系机构模型图如图1所示。

由体系结构图可以看出,其工作过程是将最初的天线发射的信号,经过射频端的处理和变换,由宽带A/D数字化,在模拟混频后,将经射频端处理过后的信号转化为中频信号,最后经数字信号处理器后,得到我们所需的高速中频数字信号。

数字信号频率合成、宽带数字的滤波、数字信号下变频和调制解调的各个功能则用软件编程来予于实现。

软件无线电的频率段在最低0.1 MHz,最高2 GHz之间,依据奈奎斯特带通信号抽样定理和低通信号抽样定理,下一级的数字信号处理器的处理速度、数字信号和模拟信号的转换速率及其工作范围必须要在规定指标以内。

软件无线电是将射频模拟信号数字化,经过模拟下变频转化为模拟中频信号,经中频把信号转化为数字中频信号,最终得到我们所需的低速的基带信号。

当然,得到上述所需的基带信号之前须经变频器的变频、抽取及低通的滤波等一系列的处理。

最后,数字信号处理器对所得的基带信号进行解调、解码、抗衰落、抗干扰及均衡的处理。

数字下变频是连接高速射频信号和其下一级的低速数字信号处理器的重要部件,实现了将所有信道里的信号,信道分离的功能,将信道里的宽带信号转化为所需的窄带信号;或者用来减小采样速率,实现减轻基带部分的工作量。

集成电路应用App恻。

nofIntegraledc.删ts减小到了l%;根据抽头系数的对称性减少了寄存器的【3】张欣.VLsI数字信号处理。

设计与实现【M】.北京:科学出使用,节约了读取存储的时间。

版社,2003.参考文献【4】王华.基于低通滤波器的数字下变频性能【J】.舰船电子对【l】张欣.扩频通信数字基带信号处理算法及其VLSI实现[M】.抗,2008,31(2).北京:科学出版社,2004.【5】张进,苏凯雄.基于FPGA的数控振荡器的设计与实现[J】.【2】薛年喜.MA,I’LAB在数字信号处理中的应用【M】.北京:清福州大学学报(自然科学版),2005(5):584—587.华大学出版社,2003.(收稿日期:2008—07—23)■}薯}■士■t奄kd●}誓e坐■e—喀—‘■}■tq}誓}■}—k■}重}'I叠■}坐薯}■}j-}誓士jkj‘}!-电■P■}■}jk■}■},妊业■}—}jk■皇螺坐jklI譬盥坐坐(上接第53页)参考文献此外,监控系统还应用了带扩展AT+I指令集功能的CDMA通信软件。

其指令集以及实现编程不赘述。

由于移动通信系统为一个现有的平台,在电力监控系统中采用CDMAlX网进行数据传输,可以大大降低通信系统的一次性投资,而且可减少工程实施中调试通信系统的时间,降低通信系统的维护费用,减轻工作人员的劳动强度,提高工作效率及配网自动化管理水平。

该系统已在广西某电力部门应用一年多。

现场实际应用效果证明采用ARM嵌入式控制器LPC2210和高精度电量计量芯片ADE7758使智能无功补偿控制器工作更加稳定,实时性更好,是一种理想的无功补偿控制器升级换代产品,具有很好的推广应用前景。

56欢迎网上投稿www.chinaaet.∞m【l】王云,贾清寒,胡晓龙.基于无线网的配电变压器监测系统应用【J1.电力系统自动化,2002,26(16):75—78.【2】林功平,徐石明,罗剑波.配电自动化终端技术分析【J】.电力系统自动化,2003,27(12).【31杨彩虹,王芙蓉,贺德华.GSM的数据业务和承载能力【J】.电讯技术,2002,42(1):10l—105.【4】广州周立功单片机发展有限公司.LPC2210,2220UserManual『EB/OLl.www.zl肿cu.com,2005.【5】AnalogDe、rices.ADE7758DateSheet,PblyPha跎Multifunc—tionEnergyMete血gIC埘thperPhaseIr怕瑚ation【Z】.ANALOGDEVICES.2006.【6】杜春雷.ARM体系结构与编程【M】.北京:清华大学出版社,2003.(收稿日期:2008一08—12)《电子技术应用》2009年第2期基于FPGA的数字下变频设计与实现作者:赵远鸿, 宋学瑞, ZHAO Yuan Hong, SONG Xue Rui作者单位:中南大学,信息科学与工程学院,湖南,长沙,410083刊名:电子技术应用英文刊名:APPLICATION OF ELECTRONIC TECHNIQUE年,卷(期):2009,35(2)被引用次数:3次1.张进;苏凯雄基于FPGA的数控振荡器的设计与实现[期刊论文]-福州大学学报(自然科学版) 2005(05)2.王华基于低通滤波器的数字下变频性能[期刊论文]-舰船电子对抗 2008(02)3.张欣VLSI数字信号处理.设计与实现 20034.薛年喜MATLAB在数字信号处理中的应用 20035.张欣扩频通信数字基带信号处理算法及其VLSI实现 20041.汪敏.肖斌基于FPGA的数字中频系统设计[期刊论文]-通信技术 2011(1)2.黄鹏.赵远鸿基于FPGA伪码快速捕获的优化设计[期刊论文]-现代电子技术 2011(3)3.刘宏鹤.程婷.贾可新.何子述基于ISL 5416的数字下变频原理及实现[期刊论文]-信息安全与通信保密 2010(7)本文链接:/Periodical_dzjsyy200902024.aspx。

基于FPGA的数字下变频设计与实现赵艳杰;王东;刘志红;贾晨【摘要】数字下变频是全数字解调器中的关键技术之一,其性能好坏直接决定解调器的工作性能.给出一种基于FPGA的数字下变频设计,详细介绍正交变换、CIC抽取滤波及根升余弦滚降FIR低通滤波器的原理设计,并可编程设置各个模块参数,自动生成及动态配置滤波器系数.该设计在Xilinx公司XC3S4000 FPGA芯片的硬件平台和ISE 9.2开发环境下,采用Verilog语言编程实现,经过实际通信系统验证,在全数字解调器中很好地完成了多载波、多速率信号的数字下变频处理功能,具有很强的灵活性、稳定性和可扩展性.【期刊名称】《农业科技与装备》【年(卷),期】2014(000)006【总页数】4页(P51-54)【关键词】数字下变频;CIC;FPGA【作者】赵艳杰;王东;刘志红;贾晨【作者单位】;;;【正文语种】中文【中图分类】TN92为了更好地体现软件无线电体系中在尽可能靠近天线的地方使用A/D 的核心思想,全数字化解调器的设计大多采用直接在中频进行信号采样,即高频模拟信号先经过模拟下变频到适当中频,然后在中频阶段对其进行A/D 采样以输出高速的数字中频信号[1],经过数字下变频技术的抽取和低通滤波处理,使其变为较低速率的基带信号再送给后端数字信号处理模块进行解调、译码等相关处理。

数字下变频(DDC)技术连接着前端ADC 和后端DSP,其性能好坏直接影响解调器的可靠性与稳定性,是全数字解调器的核心技术之一。

目前,数字下变频模块的实现基本分两种方式:一种是利用专用DDC 芯片完成数字下变频功能,另一种是利用自主搭建的软硬件平台编程设计实现。

专用数字下变频芯片具有抽取比率大、性能稳定等优点,但专用数字下变频芯片价格昂贵、灵活性不强,不能充分体现软件无线电的优势[2]。

近年来,FPGA 器件在工艺方面的进步,为之带来了前所未有的逻辑规模和强大的处理性能,用FPGA 来实现比用专用芯片可以带来更多的好处。

基于FPGA的DDC设计及仿真王力;薛红喜【摘要】在软件无线电数字接收机中,从AD前端采集过来的数字信号频率高达72 MHz,如此高的频率使得后端DSP不能直接完成相关的数字信号处理任务。

因此合理的设计基于FPGA的DDC,以降低数字信号频率,方便后端DSP实时完成相关的数字信号处理任务就显得尤为重要。

在很多数字信号处理系统中,数字信号频率是非常高的,而后端数字信号处理器件几乎不能满足系统的实时性要求,此时通过合理的设计DDC就可以解决上述问题。

%In the software radio receiver,the frequency of digital signal which comes from AD front-end is up to 72 MHz.Such a high frequency makes the DSP cannot directly complete digital signal processing tasks.So how to rational design DDC which based FPGA is very important,it can reduce the digital signal frequency,and make the digital signal processing tasks convenient.In many digital signals processing system,the frequency of the Digital signal is very high.The back-end digital signal processors can hardly meet the real-time requirements;the problems above can be resolved through rational design of DDC.【期刊名称】《电子设计工程》【年(卷),期】2012(020)010【总页数】4页(P158-161)【关键词】FPGA;DDC;数字信号处理;软件无线电【作者】王力;薛红喜【作者单位】电子科技大学电子工程学院,四川成都610054;电子科技大学电子工程学院,四川成都610054【正文语种】中文【中图分类】TN492近年来,软件无线电已经成为通信领域一个新的发展方向,数字下变频技术(Digital Down Converter-DDC)是软件无线电的核心技术之一,也是计算量最大的部分[1]。

计算机工程应用技术本栏目责任编辑:梁书基于FPGA 的数字下变频设计许丹(咸阳职业技术学院,陕西咸阳712000)摘要:理想的软件无线电系统需要尽可能地减少模拟环节,而将数字化处理(包括A/D ,D/A 等)尽可能靠近天线端。

数字下变频(DDC)系统作为ADC 与DSP 器件之间的桥梁,主要用来实现对前端高速A/D 采集到的中频信号进行混频、降速和滤波,完成信号的下变频处理。

鉴于FPGA 在工程上的可实现纯并行运算、速度稳定可靠等优点,完成了数字下变频的电路设计和下变频系统多级滤波结构的设计。

关键词:软件无线电;数字下变频;数字控制振荡器;滤波器中图分类号:TP393文献标识码:A文章编号:1009-3044(2021)13-0255-02开放科学(资源服务)标识码(OSID ):Design of Digital Down Conversion Based on FPGA XU Dan(Xianyang Vocational Technical College,Xianyang 712000,China)Abstract:The ideal software radio system needs to minimize the analog part,while the digital processing (including A/D,D/A,etc.)should be as close to the antenna end as possible.Digital Down Conversion (DDC)system,as A bridge between ADC and DSP de⁃vices,is mainly used to realize frequency mixing,speed reduction and filtering of intermediate frequency signals collected from the front-end high-speed A/D,and complete down-conversion processing of signals.Given the FPGA can be realized in engineering pure by its parallel computing,it completes the circuit and multi-stage filter structure design of the digital down conversion .Keywords:Software radio;Digital down converter;Numerical controlled oscillator;filter第五代移动通信系统(5G )是以用户为中心的全方位信息生态环境,其超低时延、超快传输速率、超高流量密度和超高移动性为用户提供极致的体验。

1 引言数字下变频DDC(digital down lonvwrsionl作为系统前端A/D转换器与后端通用DSP器件间的桥梁,通过降低数据流的速率,将低速数据送给后端通用DSP器件处理,其性能的优劣将对整个软件无线电系统的稳定性产生直接影响。

采用专用DDC器件完成数字下变频,虽具有抽取比大、性能稳定等优点,但价格昂贵,灵活性不强,不能充分体现软件无线电的优势。

FPGA工艺发展迅速,处理能力大大增强,相对于ASIC,DSP,其具有吞吐量高、开发周期短、可实现在线重构诸多优势。

基于这些优点,FPGA在软件无线电的研发中具有重要作用。

2 数字下变频系统数字下变频器在软件无线电系统中完成的功能结构如图1所示,其中包括直接数字频率合成器DDS(direct digital synthesizer)、数字混频器、FIR滤波器、抽取等模块。

原始模拟中频信号经A/D转换器带通采样后得到数字中频信号,输入DDC后先与DDS产生的两路正交本振信号相乘(数字混频),将数字中频搬移到基带。

混频后得到的数据率和采样率一致,后级FIR滤波器要达到该处理速率。

硬件实现相当困难,因此首先通过抽取模块大大降低数据速率,然后使用高阶FIR低通滤波器对整个信道整形滤波。

滤波输出的两路正基带信号交由下一级DSP器件进行处理。

2.1 混频器的FPGA实现数字混频器将原始采样信号与查找表生成的正、余弦波形分别相乘,最终得到两路互为正交的信号。

由于输入信号的采样率较高,因此要求混频器的处理速度大于等于信号采样率。

单通道的数字下变频系统需要两个数字混频器.也就是乘法器。

XC2V1000器件内嵌64个18×18位硬件乘法器,其最高工作频率为500 MHz,因此采用硬件乘法器完全能够满足混频器的设计要求。

使用Xilinx公司的Multiplier IP核可以轻松实现硬件乘法器的配置。

该设计中采用两路14位的输入信号,输出信号也为14位。

基于FPGA的高效动态可配数字下变频发表时间:2020-07-17T06:13:50.901Z 来源:《现代电信科技》2020年第4期作者:葛孟霞石玉[导读] 数字下变频(DDC)作为软件无线电接收机的核心技术之一,在射频模拟端(AD)和后级数字信号处理(DSP)端扮演者举足轻重的作用,成功解决了DSP处理过程中AD速度过高的问题,同时解决了过大的资源消耗及数字化程度和运算速度的提高问题。

葛孟霞石玉(电子科技大学电子科学与技术学院四川成都 611731)摘要:数字下变频(DDC)作为软件无线电接收机的核心技术之一,在射频模拟端(AD)和后级数字信号处理(DSP)端扮演者举足轻重的作用,成功解决了DSP处理过程中AD速度过高的问题,同时解决了过大的资源消耗及数字化程度和运算速度的提高问题。

然而,随着采样频率的增大和带宽数量的增多,资源消耗也是成倍增加,因此DDC的优化成为了亟待解决的问题。

本文对数字下变频技术进行深入研究,结合坐标旋转数字计算机(CORDIC)算法和多相滤波提出一种多带宽,完全动态可配的高效数字下变频,并且完成MATLAB算法仿真,在Xilinx公司的vivado硬件设计工具中仿真验证。

关键词:软件无线电;数字下变频;数字信号处理;CORDIC算法;多相滤波;动态可配1.前言数字下变频(DDC)中常用的混频技术通常是基于查找表的NCO和乘法器共同实现,基于查找表的NCO在本振信号精度要求较高时,会占用了大量的BRAM资源和乘法器,而利用直接数字频率合成(DDS)IP核时,输出的信号有较大的杂散,图1中(a)为通用DDC的结构图,其后级的滤波通常用IP核的方式直接实现。

图中(b)为改进后的DDC结构图,CORDIC算法仅仅通过移位累加就可达到混频的效果,因此用此算法替代常规的NCO算法能够节约很多资源。

本文中数字下变频的积分梳状滤波(CIC)环节通过采用两个CIC级联方式,其中每个CIC均能实现可编程的级联级数可配,抽取可配,并且通过这种方式能够有效的抑制和滤除带外信号。

基于FPGA的DDC(数字下变频)设计与实现微系统设计、测试与控制课程大作业之基于FPGA的DDC(数字下变频)的设计与仿真摘要 (1)ABSTRACT (2)第一章绪论 (3)1.1 数字下变频(DDC)研究背景 (3)1.2 DDC概述 (4)1.3 本文研究内容和结构安排 (5)第二章数字下变频(DDC)基础理论 (7)2.1 数字下变频器 (7)2.1.1 数字变频的基本原理与结构 (7)2.1.2影响数字变频器性能的主要因素72.2 数字信号采样理论 (8)2.2.1低通信号采样理论 (8)2.2.2 带通信号采样理论 (9)2.3 数字正交检波 (10)2.3.1 低通滤波法 (10)2.3.2 多相滤波结构变换法 (11)2.4 多抽样率数字信号处理理论 (13)2.4.1 整数倍抽取和内插 (13)2.4.2 多抽样率系统的恒等变换 (16)2.4.3 多相滤波结构 (17)2.5 相关算法介绍 (19)2.5.1 CORDIC算法 (19)2.5.2 FIR滤波器 (21)2.6 本章小结 (22)第三章数字下变频(DDC)各模块设计 (23)3.1 数字下变频的基本实现方案 (23)3.2 基于DDS的数控振荡器的设计 (23)3.2.1 混频器模块设计 (23)3.2.2 DDS的特点 (25)3.3抽取滤波 (27)3.4 本章小结 (29)第四章数字下变频器设计验证和逻辑综合 (30)4.1基于DDS的数控振荡器的仿真和验证304.2 FIR滤波器的仿真和验证 (32)4.3 抽取模块仿真验证 (33)4.4 DDC整体的仿真和验证 (33)4.4.1 MATLAB与modelsim仿真 (34)4.4.2 FPGA综合报告 (35)4.5 本章小结 (36)第五章总结与展望 (37)参考文献 (39)摘要数字下变频(Digital Down Convert—DDC)是将中频信号下变频至零频,且使信号速率降至适宜通用DSP器件处理速率的技术。

实现这种功能的数字下变频器是软件无线电的核心部分。

本文首先对软件无线电数字下变频的国内外现状进行了分析,然后对于FPGA实现数字下变频设计的优势作了阐述。

基于本论文在FPGA中实现的结构,结合软件无线电理论基础讨论了DDC的工作原理,给出数字下变频器的常用结构,然后设定整体系统方案,并按功能完成模块划分和接口定义,主要分为混频器、FIR低通滤波器及抽取。

通过使用Verilog和调用部分IP核相结合的方法完成多通道DDC各个模块的设计与仿真调试,通过Matlab对各模块进行验证,结果表明设计的思想和结构是正确的。

基于FPGA实现的DDC,能充分体现软件无线电系统高的灵活性和宽的适应性,本文所设计的数字下变频系统有一定的通用性。

关键字:软件无线电,数字下变频,FIR滤波器, FPGAABSTRACTDigital Down Convert(DDC) converts digitized IF data into filtered based and data which call be processed by a standard DSP microprocessor.DDC is a core part of a Software Radio system.In this paper, the DDC’S current technology at home and abroad was analyzed, and then the advantages of using FPGA to complete the design of DDC were described.This paper is based on the structure implemented in FPGA, combined with the software radio theoretical to discuss the DDC’s works, and then gives the structure of common digital down converter, and then set the whole system solutions, and then complete the module division and functional interface definition, mainly divided into mixer, FIR low-pass filter and decimation. By using Verilog and part of IP core to complete the design and simulation of multi-channel DDC commissioning of each module, validated by MATLAB for each module, the results indicate that the design and structure of thinking is correct.The DDC based on the FPGA can show adequately the great flexible and broad adaptability of software radio.The DDC system in this paper has definite generality.Keywords: Digital down converter, Direct digital synthesis, FIR filter, FPGA第一章绪论1.1 数字下变频(DDC)研究背景雷达(Radar)是用无线电方法发现目标并测定它们的空间位置、速度等信息的一项非常实用的技术。

最初,雷达是为了满足对空监视和武器控制的军事需求而研制的,军事应用使得雷达技术的开发得到各国大量的财政支持。

随着科技人员更深入的研究,雷达开始在许多重要的民用场合,如飞机、轮船、宇宙飞船的安全飞行,环境遥感,特别是气象遥感等方面也获得了广泛的应用[1]。

在早期的雷达收发系统中,都是采用模拟器件来实现各个功能模块,设计过程中经常会出现温度漂移、增益变化等问题。

相对于模拟电路来说,数字电路具有可自检、可编程等优点,上面所述的系统很多部分都已经逐步数字化。

在数字化进程中,数字信号处理技术的应用也受到了雷达系统研究工作者的重视,成为相关积累(如FFT、数字滤波、脉冲压缩等)、非相关积累(视频积累)、目标检测以及图像处理等功能的技术保证。

随着数字信号处理理论的不断成熟和完善,微电子技术的飞速发展,雷达技术和其它的电子信息化技术的发展,尤其是软件无线电技术的兴起,更加方便了雷达数字化系统的实现。

在这样的发展趋势下,除了微波发射和射频部分,整个雷达系统将全部由数字电路实现,在数字信号处理的优势能得到全面的发挥的同时,还使具有体制标准化、系统数字化,功能模块化,低功耗,高度开放性以及灵活性等性能,这将成为了现代雷达系统的关键技术和发展趋势[2]。

在现今的高科技发展的时代,人们纷纷打起的信息战和电子战,雷达系统在其中扮演的角色尤为重要。

为了能更好的适应现代战争的需求,对现今的雷达系统也提出抗干扰、反隐形,具有高分辨力以及强大的自我生存等能力,高要求的提出,使得雷达信号处理技术的研究也得到了快速的进步。

目前雷达信号处理正在由视频处理阶段向中频处理阶段迈进,目的就是实现雷达中频以下的处理全部数字化,采用数字中频技术结合以DSP为基础的软件无线电技术正成为现代雷达领域的一个研究热点。

现代雷达处理的数据吞吐量基本在每秒几兆到几十兆复数字,使得雷达信号处理必须具有很高的数据处理能力以及运算速度,实时处理要求很高。

如果在中频阶段能够直接对数据进行处理,在保留有用信息的基础上减少信号采样点数,可以有效的降低后续数据处理的压力;同时若能在发射时利用数字的方式提高信号采样频率,减少由于模拟器件带来的不利影响,可以提高系统可靠性和灵活性。

基于此提出了本课题——数字变频器的设计。

1.2 DDC概述软件无线电起源于军事需求,最早的研究和发展也是在军用无线电台中。

然而随着软件无线电概念的不断发展和完善,它不仅在军事应用方面受到重视,民用需求如移动通信领域也开始加大对软件无线电技术的研究,已经逐渐成为未来无线电通信发展的方向。

1992年5月,在美国电信系统会议(IEEE National Telesystems Conference)上,Joe Mitola首次明确提出了软件无线电的概念[3],核心思想是搭建具有标准化和模块化特点的一个通用硬件平台,在系统结构相对通用和稳定的前提下,利用软件实现各种功能,使得不同系统之间能够兼容和互联,从而摆脱基于硬件系统结构设计的束缚。

由于技术的变化和应用的扩展,目前很难给软件无线电一个严格而全面的定义。

但是根据大多同行专家的理解,可以这样定义:软件无线电是将模块化、标准化的硬件单元以总线方式连接成基本平台,并通过软件加载实现各种无线通信功能的一种开放式体系结构。

关键思想是:将宽带A/D、D/A尽可能靠近天线,用软件实现尽可能多得无线电功能。

现阶段,受各种关键器件特别是A/D、D/A采样速率、工作带宽以及通用DSP器件处理速度的限制,用可编程器件和高速数字信号处理器来代替模拟射频电路是很难实现的,数字中频正成为一种经济、适用的选择[4]。

数字下变频的处理方式是将雷达回波中频信号下变频至零中频,并降低数据采样速率。

数字上下变频器在这里起到了连接基带DSP与ADC/DAC后端器件的作用,它们的目的是把信号的频谱搬移到更高或更低的频率上,改变数据速率,这样能在很大程度上降低对ADC/DAC转换器以及DSP器件性能的要求,便于实现和降低成本。

数字下变频不仅在军、民无线通信中获得了应用,而且在其他领域例如电子战,雷达[5],信息化家电等领域也得到推广。

数字下变频是软件无线电核心技术之一,数据运算量最大,也是最难完成的部分。

目前,实现方案主要有三种。

第一种方案是使用DSP数字信号处理芯片,该方案的优点是灵活性高、适应性强,但会受到处理速度等因素的制约,适合于数据速率比较低的各种处理。

第二种方案是使用FPGA来实现,可以采用并行或者串行的工作方式,在处理速度上优于DSP芯片,灵活性上优于ASIC 设计,但消耗的硬件资源比较多。

第三种方案是利用ASIC来完成数字下变频的功能,该方案具有计算速度快,单片成本低等优点[6]。

现在市场上成熟的数字下变频芯片则有Intersil公司的HSP50016,ADI公司的AD6640[7]等,它们的功能已经不仅仅是简单的“数字下变频”。