《Intel微处理器(第七版)》第二至第八章作业

- 格式:doc

- 大小:42.00 KB

- 文档页数:8

汇编语言第2章Intel微处理器本文讨论《汇编语言第2章Intel微处理器》这个话题。

首先,我将以合适的段落和格式来阐述汇编语言和Intel微处理器的相关内容。

Intel微处理器是现代计算机中广泛使用的重要组成部分。

作为一种关键的处理器架构,它拥有强大的功能和广泛的应用领域。

在本文中,我们将重点关注汇编语言和Intel微处理器的基本知识和原理。

1. 汇编语言简介在计算机编程中,汇编语言是一种低级语言,用于编写与特定处理器架构相对应的程序。

它相对于高级语言来说更加接近计算机硬件,因此编写的程序可以更直接地操作计算机资源。

在汇编语言中,程序员使用指令、寄存器和内存地址来编写代码。

2. Intel微处理器的发展历程Intel微处理器自1971年问世以来,经历了多个世代的变迁和升级。

每一代处理器都带来了更高的性能和更多的功能。

从最初的Intel 4004到现在的Intel Core处理器系列,每一代处理器都在不断地刷新计算机的性能极限。

3. Intel微处理器的组成和特点由于篇幅有限,这里只简要介绍Intel微处理器的基本组成和特点。

具体的细节可以参考相关参考资料。

Intel微处理器由控制单元、运算单元、寄存器、高速缓存和总线等多个部分组成。

控制单元负责指令的解码和执行,而运算单元执行指令中指定的计算操作。

寄存器用于存储临时数据和指令地址等信息。

高速缓存作为存储器的一种,提供了更快的数据访问速度。

总线则负责处理不同部件之间的数据传输。

4. 汇编语言与Intel微处理器的关系汇编语言是Intel微处理器编程的重要一环。

汇编语言在编程过程中提供了对处理器硬件的直接控制,使得程序员可以更加精确地操作处理器。

通过学习和应用汇编语言,程序员可以更好地理解和利用Intel 微处理器的功能和性能。

5. 汇编语言编程的应用领域汇编语言编程广泛应用于操作系统、嵌入式系统、驱动程序和高性能计算等领域。

通过使用汇编语言,程序员可以最大限度地发挥Intel 微处理器的潜力,实现高效的程序和系统。

同济大学电信学院2.3 Intel 80386/486 CPU2.3.1 80386/80486的主要特点2.3.2 80386/80486的内部结构2.3.3 80386/80486的三种工作方式2.3.1 80386/80486的主要特点●采用全32位结构,其内部寄存器、ALU和操作是32位,数据线和地址线均为32位●提供32位外部总线接口,最大数据传输率为32MB/s,具有自动切换数据总线宽度的功能●具有片内集成的存储器管理部件MMU,可支持虚拟存储和特权保护,虚拟存储器空间可达64太字节(TB)●具有实地址方式、保护方式和虚拟8086方式3种工作方式●采用了比8086更先进的流水线结构,使其能高效、并行地完成取指、译码、执行和存储管理功能(指令队列16字节长)同济大学电信学院2.3.2 80386/80486内部结构同济大学电信学院同济大学电信学院80386内部结构●总线接口部件(BIU )●指令预取部件(IPU )●指令译码部件(IDU )●指令执行部件(EU )●分段部件(SU )●分页部件(PU )80386内部结构●总线接口部件(BIU)◆微处理器与系统的接口,其功能是:在取指令、取数据、分段部件请求和分页部件请求时,有效地满足微处理器对外部总线的传输要求。

◆BIU能接收多个内部总线请求,并且能按优先权加以选择,最大限度地利用所提供的总线宽度,为这些请求服务。

●指令预取部件(IPU)◆职责是从存储器预先取出指令◆有一个能容纳16条指令的队列同济大学电信学院同济大学电信学院80386内部结构●指令译码部件(IDU )◆职责是从预取部件的指令队列中取出指令字节,对它们进行译码后存入自身的已译码指令队列中,并且作好供执行部件处理的准备工作。

◆如果在预译码时发现是转移指令,可提前通知总线接口部件BIU去取目标地址中的指令,取代原预取队列中的顺序指令。

80386内部结构●指令执行部件(EU)◆由控制部件、数据处理部件和保护测试部件组成。

《Intel微处理器(第七版)》第二至第八章作业第二章2、80286可寻址的寄存器为8位和16位宽。

例如:AL为8位,AX为16位。

两种寄存器都可以用于各种寻址。

8、如果带符号数FFH与01H相加,会溢出吗?答:不会。

FFH = -1;-1与1相加的结果为0。

14、为处理器工作在实模式下,对于下列CS:IP组合,找出要执行下一条指令的存储器地址。

(a)CS = 1000H和IP = 2000H(b)CS = 2000H和IP = 1000H(c)CS = 2300H和IP = 1A00H(d)CS = 1A00H和IP = B000H(e)CS = 3456H和IP = ABCDH答:利用“地址= CS*10H + IP”,可以得出(a)12000H;(b)21000H;(c)24A00H;(d)25000H;(e)3F12DH20、80286工作在实模式下下,给出下列寄存器组合所寻址的存储单元地址。

(a)DS = 1000H,DI = 2000H(b)DS = 2000H,SI = 1002H(c)SS = 2300H,BP = 3200H(d)DS = A000H,BX = 1000H(e)SS = 2900H,SP = 3A00H答:本题考查对默认寄存器组合的认识,(a)DS:DI为数据地址,结果为12000H;(b)DS:SI为数据地址,结果为21002H;(c)SS:SP为堆栈地址,结果为26200H;(d)DS:BX为数据地址,结果为A100H;(d)SS:SP为堆栈地址,结果为32A00H。

28、一个Pentium 4微处理器的描述符中含有基地址00280000H,界限00010H,并且G = 1,由这个描述符寻址的起始地址和结束地址是什么?答:本题考查对保护模式寻址方式的理解。

保护模式下,段寄存器中包含选择子,由选择子从描述符表中选择一个描述符,描述符中包含有段的基地址和界限等信息。

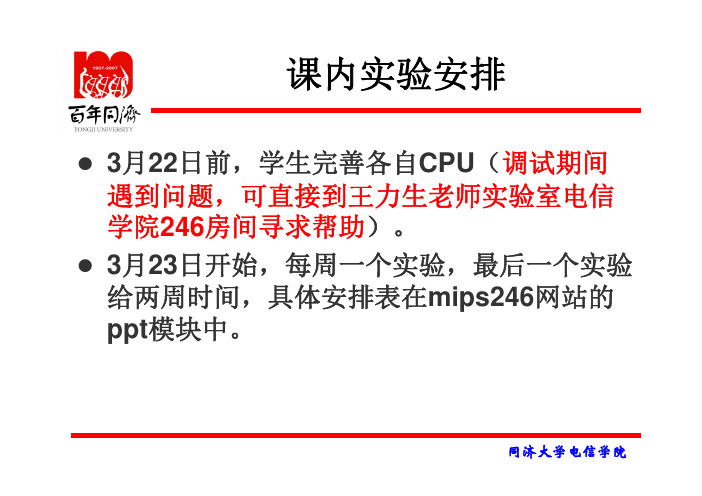

同济大学电信学院课内实验安排●3月22日前,学生完善各自CPU (调试期间遇到问题,可直接到王力生老师实验室电信学院246房间寻求帮助)。

●3月23日开始,每周一个实验,最后一个实验给两周时间,具体安排表在mips246网站的ppt 模块中。

同济大学电信学院Vcc(5V)HLDA (RQ/GT 1)ALE (QS 0)AD 15A 17/S 4A 16/S 3A 18/S 5A 19/S 6INTA (QS 0)HOLD (RQ/GT 0)DT/R (S 1)DEN (S 0)GND NMI GNDINTR CLK 1247113581216691317201014181519BHE/S 7MN/MX WR (LOCK)AD 14AD 12AD 9AD 5AD 13AD 11AD 8AD 4AD 0AD 10AD 7AD 3AD 6AD 2AD 1RDM/IO (S 2)RESETTEST READY 40393734303836332925353228242131272326228086CPUGND A 14A 12A 9AD 5A 13A 11A 8AD 4AD 0A 10AD 7AD 3NMI GNDAD 6AD 2INTR AD 1CLK 1247113581216691317201014181519Vcc(5V)A 15A 17/S 4SS 0HLDA (RQ/GT 1)A 16/S 3A 18/S 5MN/MX WR (LOCK)ALE (QS 0)A 19/S 6RDM/IO (S 2)INTA (QS 0)RESETHOLD (RQ/GT 0)DT/R (S 1)TEST DEN (S 0)READY 40393734303836332925353228242131272326228088CPU2.1.4 8086/8088芯片的引脚信号同济大学电信学院地址数据及状态信号线Vcc(5V)HLDA (RQ/GT 1)ALE (QS 0)AD 15A 17/S 4A 16/S 3A 18/S 5A 19/S 6INTA (QS 0)HOLD (RQ/GT 0)DT/R (S 1)DEN (S 0)GND NMI GNDINTR CLK 1247113581216691317201014181519BHE/S 7MN/MX WR (LOCK)AD 14AD 12AD 9AD 5AD 13AD 11AD 8AD 4AD 0AD 10AD 7AD 3AD 6AD 2AD 1RDM/IO (S 2)RESETTEST READY 40393734303836332925353228242131272326228086CPU1. AD 15--AD 0 :地址/数据复用引脚(双向、三态)●在总线周期的T 1状态用来输出要访问的存储器或I/O 端口地址。

第二章Intel32位微处理器Intel公司生产的80386,80486,MMX Pentium,PentiumⅡ以及PentiumⅢ都属于32位的微处理器。

然而它们在电路结构,芯片性能、主频等方面差异甚大,由不同的微处理器组成的微机系统,其系统功能也有明显的差异。

但是,从用户编程的角度,由这些微处理器组成的微机系统,其基本工作原理相同,在基本编程结构、基本工作模式、存储器管理模式、中断管理模式、任务管理模式等方面大同小异,它们的指令集保持向上兼容。

因此本节在讨论微机原理时,主要论述这些微处理器的共同特点。

从讨论微机系统基本工作原理的观点看,80486在Intel32位微处理器的体系演化过程中,具有承上启下的地位。

一方面它上承80386,从芯片特征上可看出其将80386及运算协处理器80387、高速缓存器集成于一体。

另一方面它下启Pentium系列微处理器的基本体系结构。

虽然Pentium采用了超标量设计,有两条流水线及配套的辅助部件,有多媒体控制能力等,但在涉及微机系统基本工作原理的部分,仍然保持了80486的逻辑部件及功能。

因此本书以80486作为论述Intel32位微处理器的基本模型。

所谓32位微处理器是指在微处理器内部以32位寄存器为单位进行数据处理。

而在数据传送时,根据发送端与接收端处理数据的速度不同,可能以128位、64位、32位、16位或8位二进制位为单位,进行数据的传送。

但在内存中总是以8位二进制位(字节)为单位来存放数据。

2.1 微处理器的基本结构2.1.1微处理器的内部基本结构对每一种类型的微处理器,从不同的观点都可以勾划出差别很大的内部详细结构框图。

本节我们只以80486为例,给出32位微处理器的基本结构框图,图2.1描述了32位微处理器内部的基本逻辑部化部件之间的基本联系、各部件的主要功能、数据在微处理器中的主要流动趋向。

其中每个图框都可以进一步细化成一个局部结构图,用于反映该部件内的情况。

第二章2、80286可寻址的寄存器为8位和16位宽。

例如:AL为8位,AX为16位。

两种寄存器都可以用于各种寻址。

8、如果带符号数FFH与01H相加,会溢出吗?答:不会。

FFH = -1;-1与1相加的结果为0。

14、为处理器工作在实模式下,对于下列CS:IP组合,找出要执行下一条指令的存储器地址。

(a)CS = 1000H和IP = 2000H(b)CS = 2000H和IP = 1000H(c)CS = 2300H和IP = 1A00H(d)CS = 1A00H和IP = B000H(e)CS = 3456H和IP = ABCDH答:利用“地址= CS*10H + IP”,可以得出(a)12000H;(b)21000H;(c)24A00H;(d)25000H;(e)3F12DH20、80286工作在实模式下下,给出下列寄存器组合所寻址的存储单元地址。

(a)DS = 1000H,DI = 2000H(b)DS = 2000H,SI = 1002H(c)SS = 2300H,BP = 3200H(d)DS = A000H,BX = 1000H(e)SS = 2900H,SP = 3A00H答:本题考查对默认寄存器组合的认识,(a)DS:DI为数据地址,结果为12000H;(b)DS:SI为数据地址,结果为21002H;(c)SS:SP为堆栈地址,结果为26200H;(d)DS:BX为数据地址,结果为A100H;(d)SS:SP为堆栈地址,结果为32A00H。

28、一个Pentium 4微处理器的描述符中含有基地址00280000H,界限00010H,并且G = 1,由这个描述符寻址的起始地址和结束地址是什么?答:本题考查对保护模式寻址方式的理解。

保护模式下,段寄存器中包含选择子,由选择子从描述符表中选择一个描述符,描述符中包含有段的基地址和界限等信息。

描述符中的G位表示粒度,G = 1,则该地址寻址的单位为4KB,所以这里的起始地址是00280000H,结束地址= 起始地址+ (界限+1)* 寻址单位- 1,结果为290FFFH。

44、如果微处理器将线性地址00200000H送到具有分页机制的系统,哪个页目录项被访问?哪个页表项被访问?答:本题考查内存的分页机制。

线性地址通过页目录和页表的转化将成为物理地址,具体而言线性地址的22~31位访问对应的页目录项,12~21位访问对应的页表项。

这里给出的线性地址将访问页目录第0H项和页表第200H项。

第三章6、指令MOV BL, CX存在什么错误?答:BL寄存器和CX寄存器的长度不匹配。

20、符号[]指示什么?答:指示间接寻址。

22、指令MOV [BX], [DI]的错误是什么?答:存储器到存储器之间的数据传输时非法的,处理MOVS指令。

26、说明MOV BX, DATA 和MOV BX, OFFSET DATA指令之间的区别。

答:MOV BX, DATA将DATA所指向内存的内容复制到BX中,而MOV BX, OFFSET DATA将DATA在内存中的偏移地址复制到BX。

30、给定DS = 1100H,BX = 0200H,LIST = 0250H 和SI = 0500H。

假定按实模式操作,确定下面每条指令寻址的存储器地址。

(a)MOV LIST [SI], EDX(b)MOV CL, LIST[BX + SI](c)MOV CH, [BX +SI]答:本题主要考察各种寻址方式。

(a)由LIST地址加SI的地址,然后和DS的地址组合成寻址的地址。

结果为11750H。

(b)与(a)类似,结果为11950H。

(c)与(a)类似,结果为11700H。

34、给出有5个字段的字数据结构,字段名是F1, F2, F3, F4和F5,结构名是FIELDS。

答:FIELDS STRUCF1 WORD ?F2 WORD ?F3 WORD ?F4 WORD ?F5 WORD ?FIELDS ENDS第四章10、如果MOV SI, [BX + 2]指令出现在程序中,与它等效的机器语言是什么?答:本题考查Intel机器语言与汇编语言的转换,这里默认使用16位指令系统。

通过查询课本的附录B,我们可以知道“MOV reg, mem”的机器语言格式为“100010dw oorrrmmm disp”,而这里是从mem到reg传送数据,所以d = 1;SI 为16位,所以w = 1;寻址方式为寄存器相对寻址,包含8位的偏移量,所以oo = 01;查表可知rrr = 110,mmm = 111;disp(偏移量)= 00000010B;综上,可得“MOV SI, [BX + 2]”的机器码为:“10001011 01110111 00000010B”= “8B 77 02H”。

12、MOV CS, AX指令会带来什么错误?答:CS是指令段寄存器,仅仅改变该寄存器的值将导致程序的下一条指令成为不可知的指令,这在多数情况下将导致系统的混乱。

24、LEA SI, NUMB指令和MOV SI, OFFSET NUMB指令直接的区别是什么?答:这里考查LEA指令和OFFSET指令的区别。

题目中的两条指令都将NUMB的偏移量存入SI寄存器,但是执行LEA指令需要更多的时钟周期,因为LEA指令是在微处理器执行时才计算NUMB的偏移量的,而OFFSET是在执行该指令前就由汇编程序计算好了NUMB的偏移量。

32、说明LODSB指令的操作。

答:将DS:[SI]所指向的存储器中的字节存入AL寄存器中。

36、设计指令序列,将12个字节的数据由SOURCE寻址的存储区域复制到由DEST 寻址的存储区域内。

答:MOVS指令可以实现从存储器到存储器的数据转移,所以这里主要采用该条指令实现。

MOV SI, OFFSET SOURCEMOV DI, OFFSET DESTMOV CX, 12REP MOVSB60、设计近过程,将AL的内容存入数据段中用DI寄存器寻址的4个连续存储单元中。

答:STOSB指令可以将AL寄存器的内容存储到由ES: [DI]寻址的存储器中。

题目要求将AL的内容存入数据段中用DI寄存器寻址的4个连续存储单元中,所以要将DS的值赋给ES,可以通过POSH 和POP指令实现。

近过程的伪指令为PROC NEAR。

STORE PROC NEARPUSH DSPOP ESMOV CX, 4REP STOSBSTORE ENDP第五章10、INC [BX]指令的错误是什么?答:对于只有一个操作数的算术或逻辑运算指令,如果操作数采用寄存器间接寻址方式,则必须由BYTE/WORD/DWROD PTR来指定该内存单元的大小。

12、如果DL = 0F3H,BH = 72H,列出从DL内容减去BH内容以后的差,并且给出标志寄存器各位的内容。

答:减法运算包括带符号和不带符号两种,这两种运算对寄存器的操作完全相同,只是无符号减法不考虑符号位标志寄存器。

采用双符号位计算法,可知结果为DL = 81 H,无溢出O = 0,无进位C = 0,有半进位A = 1,结果为负S = 1,不为零Z = 0。

16、说欧盟SUB和CMP指令之间的区别。

答:这两条指令都通过操作数的减法而改变标志寄存器,不同之处在于CMP不改变被减数,而SUB改变被减数。

36、设计短指令序列,将DH中的最左3位清0,而不改变DH中其它位,结果存入BH中。

答:通过AND指令可以实现对部分位的屏蔽。

MOV BH, DHAND BH, 00011111B40、设计短指令序列,把AX中的最右4位置为1,将AX中的最左3位清0,并且把AX中的7、8、9位取反。

答:XOR指令可以实现对个别位的取反。

OR AX, 000FHAND AX, 1FFFHXOR AX, 0000 0011 1000 0000B44、选择正确的指令实现以下的任务:(a)DI右移3位,并把零移入最高位(b)AL中所有位左移1位,并使0移入最低位(c)AL循环左移3位(d)EDX带进位位循环右移1位(e)DH寄存器右移1位,并且使结果的符号位与原数符号相同答:逻辑移位指令不考虑符号位,算术移位指令需要考虑符号位。

带进位的循环移位指令顾名思义,不带进位的循环移位指令只是进位不会移入寄存器中,但移位操作仍然影响进位位。

(a)SHR DI, 3(b)SHL AL, 1(c)ROL AL, 3(d)RCR EDX, 1(e)SAR DH, 1第六章12、比较JMP [DI] 与JMP FAR PTR[DI]指令的操作。

答:两条指令都是采用间接寻址方式的转移指令,系统默认为16位位移量,即近转移。

如果程序中出现JMP FAR PTR[SI]指令,或者用DD伪指令定义TABLE数据的JMP TABLE[SI]指令,则微处理器认为转移表中包含32位的双字地址(IP和CS)。

所以,题目中第一条指令将跳转到由CS作为段地址和DS:[DI]的内容作为偏移量的新地址;第二条指令将跳转到由DS:[DI+2]的内容作为段地址和DS:[DI]的内容作为偏移量的新地址。

22、Pentium 4的LOOPD指令使ECX寄存器减1,并且为了决定是否发生转移测试它是否为0。

24、设计指令序列,吧00H存储到附加段起始地址为DATAZ的150H个字节的存储区中。

必须用LOOP指令帮助实现这个任务。

答:通过将CX赋值为150,采用LOOP指令可以实现题目要求的功能。

MOV CX, 150HMOV DI, OFFSET DATAZMOV AL, 00HCLDL1: STOSBLOOP L138、写一个近过程,求CX寄存器内容的三次方,这个过程除了CX寄存器以外不影响任何其他的寄存器。

答:在PROC伪指令后加上USES伪指令可以使其他寄存器不受影响。

CUBE PROC NEAR USES AX DXMOV AX, CXMUL CXMUL CXMOV CX, AXRETCUBE ENDP44、0号向量中断的用途是什么?答:通过查表可知0号向量用来处理除法错误,即除法运算中除数为0的情况。

50、什么指令控制INTR引脚的功能?答:STI指令时能INTR;CLI指令禁止INTR。

第七章2、在内嵌汇编程序中可以用伪指令DB定义字节吗?答:不可以。

内嵌汇编中的变量都是由C/C++ 语言定义的,而C/C++语言本身无法识别DB伪指令。

4、在汇编语言(内嵌汇编程序或链接模块)中,哪些寄存器不需要保留就可以使用?答:由于Microsoft C/C++没有使用AX、BX、CX、DX和ES寄存器,所以在汇编和C/C++混合编程中不需要保留。

如果使用80386或更高的处理器作为程序的基础,则EAX、EBX、ECX、EDX和ES寄存器不需要保留。