锁相技术译文翻译

- 格式:pdf

- 大小:113.16 KB

- 文档页数:11

锁相技术学习心得体会篇一:锁相技术锁相技术论文题目:专业班级:学生姓名:学号:任课老师:陈燕锁相技术的核心 XX级通信工程1班 XX 年 6 月13日摘要本文介绍了锁相技术的核心锁相环路:一个实现相位自动锁定的控制系统。

锁相环路有两个突出的特性:1是窄带滤波特性;2是宽带跟踪特性。

这两个特性使得锁相技术在电子技术领域得到了广泛的应用,特别是随着集成电路技术、数字技术以及通讯和计算机技术的发展,极大地推动了锁相技术的发展和应用。

现在锁相技术已经形成一门比较系统的理论科学,锁相技术的应用主要包含以下几个方面:跟踪滤波、频率合成与频率变换、模拟和数字信号的相干解调、数字通讯、调制与解调、检波、稳频和位频等。

下面来主要介绍一下锁相技术的核心,掌握核心就能运用得当。

关键字:核心,锁相环路,运用锁相环路的工作原理:锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。

其作用是使得电路上的时钟和某一外部时钟的相位同步。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地 80MHz和20MHz 时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

锁相环路是一个相位反馈自动控制系统。

它由以下三个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

锁相环的工作原理:1. 压控振荡器的输出经过采集并分频;2. 和基准信号同时输入鉴相器;3. 鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4. 控制VCO,使它的频率改变;5. 这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相技术译文翻译英文原文:An On-Chip All-Digital Measurement Circuit to Characterize Phase-Locked Loop Response in 45-nm SOI译文:45纳米SOI全数字片上测量电路表征锁相环响应特性年级专业:姓名:学号:2013 年 6 月 2 日英文中文An On-Chip All-Digital Measurement Circuit to Characterize Phase-Locked Loop Response in 45-nm SOIAbstract—An all-digital measurement Circuit , built in 45-nm SOI-CMOS enabl es on-chip characterization of phase-loc ked loop (PLL) response to a self-induce d phase step.This technique allows estimationof PLL closed-loop bandwidth and jitterpeaking. The circuit canbe used to plot step-response vs.time, measure static phase error,and observe phase-lock status. INTRODUCTIONMany applications such as PCI Express ? require a PLL to produce alow-jitter cl ock at a given frequency while meeting stringent bandwidth and jitter peaking r 45纳米SOI全数字片上测量电路表征锁相环响应特性摘要---建立在45纳米的SOI-CMOS上一个全数字测量电路,它能够表征PLL对自诱导相步进的响应这项技术允许对PLL闭环带宽和抖动峰值的估计。

锁相技术译文翻译英文原名:High Speed Digital Hybrid PLL Frequency Synthesizer译文:高速数字混合锁相环频率合成器年纪专业:08级通信工程班姓名:学号:2011年 5月2日To get the high-speed, it is necessary to prepare the precise synchronization of the complicated design.In 2001, H. G. Ryu proposed a simplified structure of the DDFS (direct digital frequency synthesizer)-driven PLL for the high switching speed [2].However, there is a problem that the speed of the whole system is limited by PLL.Y. Fouzar proposed a PLL frequency synthesizer of dual loop configuration using frequency-to-voltage converter (FVC) [3].It has a fast switching speed by the PD (phase detector), FVC using output signal of VCO and the proposed coarse tuning controller.However, H/W complexity is increased for the high switching speed.Also, it shows the fast switching characteristic only when the FVC works well.Another method is pre-tuning one which is called DH-PLL in this study [4].It has very high speed switching property, but H/W complexity and power consumption are increased due to digital look-up table (DLT) which is usually implemented by the ROM including the transfer characteristic ofVCO(voltage controlled oscillator).For this reason, this paper proposes a timing synchronization circuit for the rapid frequency synthesis and a very simple DLT replacement digital logic block instead of the complex ROM type DLT for high speed switching and low power consumption. Also, the requisite condition is solved in the proposed method. The fast switching operation at every the frequency synthesis process is verified by the computer circuit simulation.II.DH-PLL synthesizerAs shown in Fig.1, the open-loop synthesizer is a direct frequency synthesis type that VCO 要得到高运行速度,事先做好复杂设计的精确同步是必要的。

Unit 1 电子学:模拟和数字Unit 1-1第一部分:理想运算放大器和实际限制为了讨论运算放大器的理想参数,我们必须首先定义一些指标项,然后对这些指标项讲述我们所认为的理想值。

第一眼看运算放大器的性能指标表,感觉好像列出了大量的数值,有些是陌生的单位,有些是相关的,经常使那些对运放不熟悉的人感到迷惑。

对于这种情况我们的方法是花上必要的时间有系统的按照列出的次序阅读并理解每一个定义。

如果没有对每一项性能指标有一个真正的评价,设计人员必将失败。

目标是能够依据公布的数据设计电路,并确认构建的样机将具有预计的功能。

对于线性电路而言,它们与现在的复杂逻辑电路结构相比看起来较为简单,(因而在设计中)太容易忽视具体的性能参数了,而这些参数可极大地削弱预期性能。

现在让我们来看一个简单但很引人注意的例子。

考虑对于一个在50kHz频率上电压增益为10的放大器驱动10kΩ负载时的要求。

选择一个普通的带有内部频率补偿的低价运放,它在闭环增益为10时具有所要求的带宽,并且看起来满足了价格要求。

器件连接后,发现有正确地增益。

但是它只能产生几伏的电压变化范围,然而数据却清楚地显示输出应该能驱动达到电源电压范围以内2到3伏。

设计人员忽视了最大输出电压变化范围是受频率严格限制的,而且最大低频输出变化范围大约在10 kHz受到限制。

当然,事实上这个信息也在数据表上,但是它的实用性并没有受到重视。

这种问题经常发生在那些缺乏经验的设计人员身上。

所以这个例子的寓意十分明显:在开始设计之前总要花上必要的时间来描写全部的工作要求。

关注性能指标的详情总是有益的。

建议下面列出的具体的性能指标应该考虑:1. 在温度,时间和供给电压下的闭环增益的精确性和稳定性2. 电源要求,电源和负载阻抗,功率消耗3. 输入误差电压和偏置电流,输入输出电阻,随着时间和温度的漂移4. 频率响应,相位偏移,输出变化范围,瞬态响应,电压转换速率,频率稳定性,电容性负载驱动,过载恢复5. 线性,失真和噪声6. 输入,输出或电源保护要求,输入电压范围,共模抑制7. 外部补偿调整要求不是所有的指标项都是有关的,但要记住最初就考虑它们会更好,而不要被迫返工。

专业术语翻译6[1]人工智能Artificial Intelligence人和自然Man & Nature人口经济方法Economical Method for Population人体生理Human Physiology日本物流Material Flow of Japan日语阅读Japanese Reading熔焊原理及工艺Principle & Technique of Melting and Welding熔炼原理Principle of Melting容错与诊断Tolerance & Diagnosis容积式压缩机数学模型Mathematical Model of Displacement Compressor软件工程Software Engineering软件技术基础Basis of Software Technique软件开发工具与环境Tools & Environment for Software Developing弱信号检测Testing of Feeble Signals色彩Color色谱Color Spectrum摄影技巧Techniques for Photography涉外企业管理Enterprise Administration Concerning Foreign Natio社会调查的理论与方法Theories & Methods for Social Investigation社会调查方法Methods for Social Investigation社会工作Social Work社会统计分析与SYSTAT应用Social Statistics Analysis & SYSTAT Application社会统计学Social Statistics社会问题研究Research on Social Problems社会心理学Social Psychology社会学概论Introduction to Sociololgy社会学简论Brief Introduction to Sociology社会学理论专题Current Issues in Theories of Socilolgy社会学问题研究Research on Problems of Sociology社会学研究方法Research Methods of Sociology社会主义财政学Finance of Socialism社会主义各国政,经体制讨论Discussion on Political & Economic Systems in Socialism审计学Science of Auditing生产管理Administration of Manufacturing生产过程计算机控制Computer Control in Manufacturing Process生产过程自动化Water-Turbine Engine生理学Physiology生命科学与无机化学Life Science and Inorganic Chemistry生物工程产品Bio-engineering Products生物工程导论Introduction to Bio-engineering生物化学Biochemistry生物化学工程Biochemical Engineering生物化学及实验Biochemistry Experiment生物检测技术Measurement for Biotechnique 生物控制论Biocybernetics生物流变学Biorheology生物物理Biophysi生物学专题Currents Issues in Biology生物医学超声学Biomedical Supersonics失效分析Invalidation Analysis诗歌美学Aesthetics of Poetry时间序列Time Sequence实变函数Functions of Real Variable实验分析Experimental Analysis实验力学Experimental Mechanics实验力学基础Basis of Experimental Mechanics实验流体Experimental Flowing Object实验应力分析Analysis of Experimental Stress世界近现代经济史Modern History of World Economy世界近现代史Modern History of the World世界文化史History of World Culture世界政治经济与国际关系World Politic Ecomony &International Relationship适应控制系统Adaption Control System市场学Science of Market市场研究Research on Market市场预测Market Predicting输入输出设计原理Principle of Input and Output Designing 书法Handwriting数据结构Data Structure数据库概论Introduction to Database数据库基础Basis of Database数据库技术Technique of Database数据库设计与分析Design & Analysis of Database数据库系统原理Principles of Database System数据库应用Application of Database数据库原理及应用Principle & Application of Database数控机床Digit Control Machine Tool数控技术Digit Control Technique数理方程Mathematical Equations数理方程积分变换Integral Transmission of Mathematical Equation数理方程与特殊函数Equations of Mathmatical Physics & Special Functions数理逻辑Mathematical Logic数理统计Mathematical statistics数量经济Quantity Economics数学分析Mathematical Analysis数学规划Mathematical Planning数学模型Mathematical Modening数学物理方法Method of Mathematical Physics数值电路Digital Circuit数值分析Numerical Analysis数值计算Digital Computation数字测量技术Digital Measuring Technique数字测量实验技术Experimental Technique of Digital Measuring 数字测试实验技术Experimental Technique of Digital Testing数字电路Digital Circuit数字电路及微机原理Digital Circuit & Computer Principles数字电视Digital Television数字电子基础Fundamental Digital Electionics数字电子技术Digital Electronic Technique数字电子技术基础Fundamental Digital Electronic Technique数字电子技术设计与实验Experiment & Design of Digital Electron Technique数字电子线路Digital Electrical Circuitry数字电子与微机原理Digital Electronics & Principle of Microcomputer数字仿真Digital Simulation数字化测量技术Digital Measuring Technique数字控制及微机控制技术Digital Control & Microcomputer Control Technique数字逻辑Digital Logic数字图象处理Digital Image Processing数字系统逻辑设计Logical Design of Digital System数字系统设计Design of Digital System数字信号处理Digital Signal Processing双曲线方程Hyperbolic Equation水电能源学Science of HydrOelectric Enelgy水电站过渡过程的特殊问题Special Problems in the Transition ofa Hydropower Station水电站计算机控制Computer Control in Hydropower Station水电站经济运行Economic Operation in Hydropower Station水电站控制系统分析Analysis of Control System in Hydropower Station水电站自动化Automation of Hydropower Station水动力学Water Dynamics水机工艺结构分析Technics Structure Analysis of Hydraulic Machinery水力机械测试技术Test Technique of Hydraulic Machinery水力机械的汽蚀Gas Etching of Hydraulic Machinery水力机械调节Adjustment of Hydraulic Machinery水力机械强度计算Intensity Calculation of Hydraulic Machinery水力机械原理Principles of Hydraulic Machinery水力机械制造工艺及结构分析Manufacturing Technique & Structure Analysis of Hydraulic Machinery水力机械制造工艺学Manufacturing Technique for Hydraulic Machinery水力学Hydraulics水轮机Water-Turbine Engine水轮机调节Water-Turbine Engine Adaption水轮机调节系统Adaptive System of Water-Turbine Engine水轮机水力设计Hydraulic Design of Water Engine水轮机原理及水力设计Principles of Water-Turbine Engine & Design of Water Engine水轮机原理与CAD Principle of Water-Turbine Engine & CAD水轮水力设计Hydraulic Design of Water Engine水现代控制理论Modern Theory of Water Controling 水质稳定技术Stability Technique of Water Quality思想教育Virtue Education素描Pencil Sketch速冻技术Technique of Speed Freezing塑性力学Plastic Machanics算法语言Algorithmic Language随机过程Stochastic Process & Time Series Analysis 随机运筹学Randomized Operational Research锁相技术Phase Lock Technique谈判技巧Negotiation Skills唐宋诗词Poetry & Prose of Tang & Song Dynasties 陶瓷材料学Science of Ceramic Material陶瓷工艺原理Principle of Pottery Technology特种泵Special Pump特种加工工艺Special Working Technology特种压缩机Special Compressor特种铸铁Special Casting Iron特种铸造Special Processes of Metal Castings体育Physical Education天线原理Principle of Antenna铁磁学Ferromagnetics铁电半导体Ferro-Electric Semiconductor铁电材料与器件Ferro-Electric Material and Element铁电压电材料与器件Ferro-V oltage Electric Material and Element 铁氧体材料Ferrite Material听说训练Practice on Listening & Speaking通风机Ventilator通信电子线路Electronic Circuit of Communication通信原理Principle of Communication通讯写作专题Current Issues on Report Writing同步控制原理Principle of Synchronic Control统计Statistics统计计算Experiment of Applied Physics统计检查与质量控制Statistic Check and Quality Control统计物理Statistical Physics统计信号分析Analysis of Statistical Signal统计学Statistics统计学原理Principle of Statistics统计学原理与工业统计Principle of Statistics & Industrial Statistics统计原理Statistics投入产出分析Analysis of Input and Output投入产出技术Input and Output Technique透平机械三元流动Three-dimensional Flow of Turbine Machinery 透平膨胀机Turbine Expansion Engine透平式压缩机特性模拟Analog of Performance ofTurbine Compressor透平压缩机强度Tensile of Turbine Compressor图论Graph Theory图论算法Algorithm on Graph Theory图论与组合Graphing & Grouping图论与组合优化Graphing & Optimal Grouping土力学与地基Soil Mechanics and Foundations托福测试Test of English as a Foreign Language拓朴学Topology外部设备讲座Lectures on Peripherial Equipment外部设备维修Repairment of Peripheral Equipment外国古代建筑史History of Western Ancient Architecture外国文献阅读Readings of Foreign Literature外国文学史History of Foreign Literature外国文学作品选译Selected Translations of Foreign Literary Works外国物流Foreign Material Flow外国物资管理Overseas Material Management外国新闻事业史History of Overseas Journalism外贸会计Foreign Business Accountancy外贸英语Foreign Business English外设概论Introduction to Peripheral Equipment外设实验Experiment on Peripheral Equipment往复泵及其它类型泵Reciprocating Pump & Other type Pumps 微波测量技术Microwave Measurement Technique微波电路计算机辅助设计CAD of Microwave Circuit微波技术Microwave Technique微波技术基础Basis of Microwave Technique微波技术与天线Microwave Technique and Antenna 微波器件Microwave Device微波器件及电路Microwave Device and Circuitry 微波铁氧体器件Microwave Iron Oxide Elements 微波网络Microwave Net。

外文资料Phase-locked loop Technology :A phase-locked loop or phase lock loop (PLL) is a control system that generates a signal that has a fixed relation to the phase of a "reference" signal. A phase-locked loop circuit responds to both the frequency and the phase of the input signals, automatically raising or lowering the frequency of a controlled oscillator until it is matched to the reference in both frequency and phase. A phase-locked loop is an example of a control system using negative feedback. In the order of the PLL is the way of made the frequency stability in the send up wireless,include VCO and PLL integrated circuits,VCO send up a signal,some of the signal is output,and the other through the frequency division with PLL integrated circuits generate the local signal making compared.In the order to remain the same,it’s must be remain the phase displacement same.If the phase displacement have some changes,the output of the PLL integrated circuits have some changes too,to controlle VCO until phase diffe rence to restore,make both cotrolled oscillator’s frequency and phase with input signal which is close-loop electronic circuit keep firm relationship.Phase-locked loops are widely used in radio, telecommunications, computers and other electronic applications. They may generate stable frequencies, recover a signal from a noisy communication channel, or distribute clock timing pulses in digital logic designs such as microprocessors. Since a single integrated circuit can provide a complete phase-locked-loop building block, the technique is widely used in modern electronic devices, with output frequencies from a fraction of a cycle per second up to many gigahertz.Earliest research towards what became known as the phase-locked loop goes back to 1932, when British researchers developed an alternative to Edwin Armstrong's superheterodyne receiver, the Homodyne. In the homodyne or synchrodyne system, a local oscillator was tuned to the desired input frequency and multiplied with the input signal. The resulting output signal included the original audio modulation information.The intent was to develop an alternative receiver circuit that required fewer tuned circuits than the superheterodyne receiver. Since the local oscillator would rapidly drift in frequency, an automatic correction signal was applied to the oscillator, maintaining it in the same phase and frequency as the desired signal. The technique was described in 1932, in a paper by H.de Bellescise, in the French journal Onde Electrique.In analog television receivers since at least the late 1930s, phase-locked-loop horizontal and vertical sweep circuits are locked to synchronization pulses in the broadcast signal. When Signetics introduced a line of monolithic integrated circuits that were complete phase-locked loop systems on a chip in 1969, applications for the technique multiplied. A few years later RCA introduced the "CD4046" CMOS Micropower Phase-Locked Loop, which became a popular integrated circuit. Applications:Phase-locked loops are widely used for synchronization purposes; in space communications for coherent carrier tracking and threshold extension, bit synchronization, and symbol synchronization. Phase-locked loops can also be used to demodulate frequency-modulated signals. In radio transmitters, a PLL is used to synthesize new frequencies which are a multiple of a reference frequency, with the same stability as the reference frequency.Clock recovery :Some data streams, especially high-speed serial data streams (such as the raw stream of data from the magnetic head of a disk drive), are sent without an accompanying clock. The receiver generates a clock from an approximate frequency reference, and then phase-aligns to the transitions in the data stream with a PLL. This process is referred to as clock recovery. In order for this scheme to work, the data stream must have a transition frequently enough to correct any drift in the PLL's oscillator. Typically, some sort of redundant encoding is used; 8B10B is very common.Deskewing :If a clock is sent in parallel with data, that clock can be used to sample the data.Because the clock must be received and amplified before it can drive the flip-flops which sample the data, there will be a finite, and process-, temperature-, and voltage-dependent delay between the detected clock edge and the received data window. This delay limits the frequency at which data can be sent. One way of eliminating this delay is to include a deskew PLL on the receive side, so that the clock at each data flip-flop is phase-matched to the received clock. In that type of application, a special form of a PLL called a Delay-Locked Loop (DLL) is frequently used.Clock generation:Many electronic systems include processors of various sorts that operate at hundreds of megahertz. Typically, the clocks supplied to these processors come from clock generator PLLs, which multiply a lower-frequency reference clock (usually 50 or 100 MHz) up to the operating frequency of the processor. The multiplication factor can be quite large in cases where the operating frequency is multiple gigahertz and the reference crystal is just tens or hundreds of megahertz.Spread spectrum:All electronic systems emit some unwanted radio frequency energy. Various regulatory agencies (such as the FCC in the United States) put limits on the emitted energy and any interference caused by it. The emitted noise generally appears at sharp spectral peaks (usually at the operating frequency of the device, and a few harmonics).A system designer can use a spread-spectrum PLL to reduce interference with high-Q receivers by spreading the energy over a larger portion of the spectrum. For example, by changing the operating frequency up and down by a small amount (about 1%), a device running at hundreds of megahertz can spread its interference evenly over a few megahertz of spectrum, which drastically reduces the amount of noise seen by FM receivers which have a bandwidth of tens of kilohertz.中文翻译锁相环技术:锁相环或锁相回路(PLL)是一个信号控制系统,即用来锁定一系列的“参考”信号。

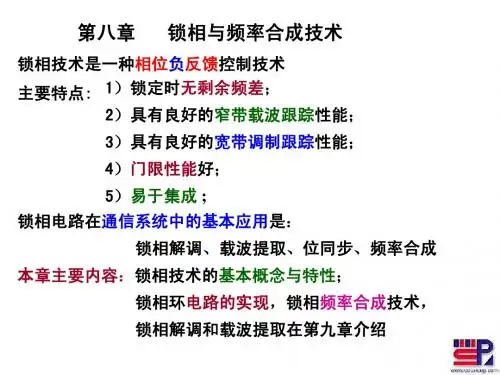

名词解释和简答题整理第一章锁相环路的基本工作原理:1.锁相环(PLL)---锁相环是一个能够跟踪输入信号相位的闭环自动控制系统。

2.捕获带:环路能通过捕获过程而进入同步状态所允许的最大固有频差|Δωo|max。

3.同步带:锁相环路能够保持锁定状态所允许的最大固有频差|Δωo|max。

4.快捕带:保证环路只有相位捕获一个过程的最大固有频差值|Δωo|max。

5.输入信号频率与环路自由振荡频率之差,称为环路的固有频率环路固有角频差:输入信号角频率ωi与环路自由振荡角频率ωo之差。

瞬时角频差:输入信号频率ωi与受控压控振荡器的频率ωv之差。

控制角频差:受控压控振荡器的频率ωv与自由振荡频率ωo之差。

三者之间的关系:瞬时频差=固有频差-控制频差。

6.鉴相器是一个相位比较装置,用来检测输入信号相位θ1(t)与反馈信号相位θ2(t)之间的相位差θe(t)。

输出的误差信号u d(t)是相差θe(t)的函数。

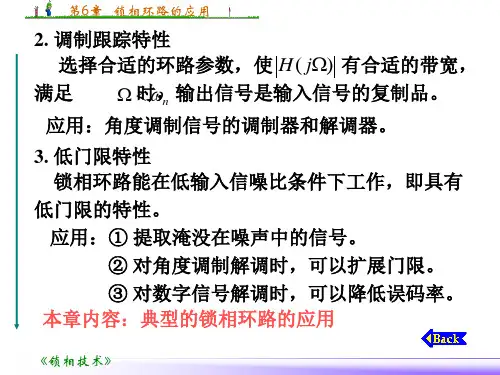

7.锁相环路由鉴相器、环路滤波器和压控振荡器三个主要部件构成;其独特的性能有载波跟踪特性、调制跟踪特性和低门限特性。

8.环路滤波器---即低通滤波器,滤除鉴相器输出电压中的高频分量,起平滑滤波的作用,提高环路的稳定性。

9.压控振荡器---压控振荡器是一个电压-频率变换装置,它的振荡频率应随输入控制电压u c(t)线性地变化。

10.环路的动态方程:pθe(t)= pθ1(t)-K o U d F(p)sin θ1(t)11.相平面:将瞬时频差与瞬时相差的关系在平面直角坐标系中所做的图。

相点:是相平面上相轨迹上的一个点,表示环路在某一时刻的状态。

12.如果锁相环路的起始状态处于不稳定平衡点时,环路自身没有能力摆脱这种状态,只有依靠外力(噪声或人为扰动)才能使环路偏离这个状态而进行捕获;所以一旦遇到这种情况就可能出现在不稳定平衡状态的滞留,致使捕获过程延长。

这种现象称为锁相环路的延滞现象。

13.环路固有频差Δωo大于环路增益K,锁相环路处于失锁差拍状态,被控振荡器未被输入信号锁定;但是由于锁相环路的控制作用,使锁相环路的平均频率向输入信号频率方向牵引。

锁相技术译文翻译英文原文:An On-Chip All-Digital Measurement Circuit to Characterize Phase-Locked Loop Response in 45-nm SOI译文:45纳米SOI全数字片上测量电路表征锁相环响应特性年级专业:姓名:学号:2013 年 6 月 2 日英文中文An On-Chip All-Digital MeasurementCircuit to Characterize Phase-LockedLoop Response in 45-nm SOIAbstract—An all-digital measurement Circuit , built in 45-nm SOI-CMOS enables on-chip characterization of phase-locked loop (PLL) response to a self-induced phase step.This technique allows estimationof PLL closed-loop bandwidth and jitterpeaking. The circuit canbe used to plot step-response vs.time, measure static phase error,and observe phase-lock status. INTRODUCTIONMany applications such as PCI Express? require a PLL to produce alow-jitter clock at a given frequency while meeting s tringent bandwidth and jitter peaking r 45纳米SOI全数字片上测量电路表征锁相环响应特性摘要---建立在45纳米的SOI-CMOS上一个全数字测量电路,它能够表征PLL对自诱导相步进的响应这项技术允许对PLL闭环带宽和抖动峰值的估计。

这个电路被用来绘制阶跃响应随时间变化的曲线,测量静态相位误差和观察相位锁定状态。

介绍很多应用例如PCI Express?需要一个PLL来产生一个低抖动的在一个给定频率的时钟,这个频率满足精确带宽和抖动峰值的要求。

equirements. Process, voltage, and tem perature (PVT) variations as well as rand om device mismatch make it difficult toguarantee a narrow range for PLL resp onse. For example ,loop parameters suc h as VCO gaincould vary by more than 2X overPVT corners. In Fig. 1, we see the closed-loop jitter transfer functions of two PLLs with identical reference clock and output frequencies. One PLL exhibits largepeaking and low bandwidth while theother shows little peaking but high ban dwidth. Although differences in this exa mple are more extreme than usual, similar but smaller differences often result from PVT variations.PLL response is often measured on atest bench using signal generators, osci lloscopes, and/or spectrum analyzers.For example, the transfer functions in Fi 工艺,电压,和温度(PVT)变化以及随机的选择不搭配的器件都使得很难保证一个窄的变化范围的PLL响应,例如,环路参数如VCO增益变化可能超过PVT角2倍上以。

图一中,我们可以看到两个具有相同参考时钟和输出频率PLL的闭环抖动传递函数一个PLL展现大的峰值和低带宽,而另一个展示了小峰值但是高带宽虽然这个例子中显示的差异比通常的要极端,这种相似会随着PVT的变化而变小PLL的响应往往使用一个信号发生器、示波器,和/或频谱分析仪。

g. 1 were automatically generated by modulating the 100-MHz reference clock with various frequencies while observin g the amplitudes of the resulting output spurs. Such methods, which may requi re many seconds to complete, motivate the need for faster, less expensive, and preferably on-chip techniques to charac terize PLL response [1]-[3]. Fig. 2 shows the PLL output phase transient respons e to an induced phase step. Similar to other second-order feedback systems, t he PLL tends to overcorrect (or oversho ot) as it works to eliminate the induced phase error. If the PLL is underdamped, as in this example, the PLL may ring sev eral times before settlingto its final lock state. A key metric in the PLL step-resp onse is crossover, defined here as the elapsed time from input step toonset of phase overshoot. Another key metric is MaxOvershoot. It 例如,在图一中传递函数是通过调制100MHz能产生各种频率的参考时钟同时观察输出马刺产生的幅值自动生成的。

这种方法,可能需要一些时间去完成,这促进了更快,更便宜的方法的需要。

比较好的方法是片上系统来表征PLL的响应特性[1]-[3]。

表二表明致相步进响应的输出瞬态相位。

类似于其他二阶反馈系统,PLL倾向于过调(或过调),那是因为它是为了消除相位误差。

如果锁相环工作在欠阻尼状态,在这种状态下,PLL可能要经过几次锁存在达到最终锁measures the maximum overcorrectionin the step response.Transient simulations and closed-form loop equations [4] show that crossover is inversely proportional to the PLL’s 3dB closed-loop bandwidth; the smaller crossoveris, the higher the bandwidth (Fig. 3). Notice that crossover is largely independent of the size ofthe phasestep. Both simulations and loop equations also predict that MaxOvershoot is p roportional to the maximum peaking inthe closed-loop transfer function; the larger MaxOvershoot is, the greaterthe peaking (Fig. 4). Notice thatthe magnitude of the overshoot isalso proportional to theinput stepsize .These relations hips between time- and frequency-domain behaviors allow us to make fast time-domain measurements and then relate the results back to frequency-domain performance specifications. The 存状态之前锁相环阶跃响应的一个关键指标是交叉反应。

在此定义为从输入步进到相位超调开始出现所用的时间另一个关键指标是最大超调量。

它可以测量阶跃响应的最大过调量。

瞬态模拟和闭环回路方程[4]表明交叉反应和PLL的3dB闭环带宽成反比;交叉反应越小,带宽越大(图3)。

请注意,交叉反应在很大程度上与相位步长无关。

模拟和回路方程还预测到闭环传递函数中最大超调与最大峰值是成正比的;circuitimplementation presented in this papershows that the PLL step response maybe captured byanall-digital, on-chip finite statemachine, allowing for fast PLL characterization.Silicon results indicate that this circuit could allow for Power-on calibration of the PLL bandwidth and peaking for com pensation of process variations.CIRCUIT DESIGNThe PLL under test (Fig. 5) isa standard integer-N charge-pump PLL. The only modification is theaddition of loop measurement circuitry.The feedback divisor (N) isprogrammable from 5 to 63 ,although N>=8 during loop measurement tests. The charge-pump current, loop-filter resistance, and VCO gain are pro grammable to allow for bandwidth andpeaking adjustments aswell as jitter opt 最大超调越大,峰值越高(图4)。