PLL 锁相环的ADS 仿真

- 格式:pdf

- 大小:603.04 KB

- 文档页数:24

锁相环学习总结通过这段的学习,我对锁相环的一些基本概念、结构构成、工作原理、主要参数以及simulink 搭建仿真模型有了较清晰的把握与理解,同时,在仿真中也出现了一些实际问题,下面我将对这段学习中对锁相环的认识和理解、设计思路以及中间所遇到的问题作一下总结:1. 概述锁相环(PLL )是实现两个信号相位同步的自动控制系统,组成锁相环的基本部件有检相器(PD )、环路滤波器(LF )、压控振荡器(VCO ),其结构图如下所示:2.锁相是相位锁定的简称,表示两个信号之间相位同步。

若两正弦信号如下所示:相位同步是指两个信号频率相等,相差为一固定值。

当i ω=o ω,两个信号之间的相位差 为一固定值,不 随时间变化而变化,称两信号相位同步。

o i t t θθθθ-=-)()('当i ω≠o ω,两个信号的相位差 ,不论iθ 是否等于o θ,只要时间有变化,那么相位差就会随时间变化而变化,称此时两信号不同步。

若这两个信号分别为锁相环的输入和输出,则此时环路出于失锁状态。

当环路工作时,且输入与输出信号频差在捕获带范围之内,通过环路的反馈控制,输出信号的瞬时角频率)(t v ω便由o ω向i ω方向变化,总会有一个时刻使得i ω=o ω,相位差等于0或一个非常小的常数,那么此时称为相位锁定,环路处于锁定状态。

若达到锁定状态后,输入信号频率变化,通过环路控制,输出信号也继续变化 并向输入信号频率靠近,相位差保持在一个固定的常数之内,则称环路此时为跟踪状态。

锁定状态可以认为是静态的相位同步,而跟踪状态则为动态的相位同步。

环路从失锁进入到锁定状态称为捕获状态。

其他几个环路工作时的重要概念:快捕带:能使环路快捕入锁的最大频差称为环路的快捕带,记为L ω∆,两倍的快捕带为快捕范围。

捕获带:能使环路进入锁定的最大固有频差,用P ω∆表示,两倍的捕获带为捕获范围。

同步带:环路在所定条件下,可缓慢增加固有频差,直到环路失锁,把能够维持环路锁定的最大固有频差成为同步带,用H ω∆,2H ω∆为同步范围。

标题:MATLAB中的PLL锁相环原理一、介绍PLL锁相环的概念PLL(Phase-Locked Loop)锁相环是一种常用的控制系统,广泛应用于通信系统、数字信号处理和电力系统等领域。

它通过比较输入信号与本地参考信号的相位差,实现对输入信号的精确跟踪和同步。

在MATLAB中,我们可以通过编写代码来模拟PLL锁相环,并深入理解其工作原理。

二、PLL锁相环的基本结构PLL锁相环由相位比较器、低通滤波器、VCO(Voltage-Controlled Oscillator)和分频器等组成。

它的基本结构如下:1. 相位比较器:用于比较输入信号和本地参考信号的相位差,并产生控制电压。

2. 低通滤波器:将相位比较器输出的控制电压进行滤波,去除高频噪声,得到稳定的调节电压。

3. VCO:根据低通滤波器输出的调节电压,调节其输出频率,实现对输入信号的跟踪。

4. 分频器:将VCO输出的信号进行分频,得到本地参考信号,用于与输入信号进行比较。

三、PLL锁相环的工作原理PLL锁相环的工作过程可以分为锁定和跟踪两个阶段。

1. 锁定阶段:在初始时刻,输入信号的频率与VCO的输出频率不同步。

相位比较器会检测到二者之间存在相位差,产生相应的控制电压,通过低通滤波器传递给VCO。

VCO根据控制电压,调节其输出频率,使其逐渐与输入信号频率同步,最终达到锁定状态。

2. 跟踪阶段:一旦锁定完成,PLL锁相环会持续监测输入信号的频率变化,并调节VCO的输出频率,确保其始终与输入信号同步。

低通滤波器起到平稳调节的作用,使得VCO的输出频率能够迅速跟随输入信号的变化。

四、MATLAB中的PLL锁相环模拟在MATLAB中,我们可以利用Simulink工具箱来建立PLL锁相环的模型,并进行仿真分析。

我们需要使用Simulink中的基本模块,如正弦波源、相位比较器、低通滤波器、VCO和分频器等,按照PLL锁相环的基本结构进行搭建。

1. 步骤一:建立模型我们在Simulink中建立PLL锁相环的模型,将各个基本模块按照PLL 锁相环的基本结构进行连接,确保输入信号能够经过相位比较器、低通滤波器和VCO等模块,最终输出同步的信号。

锁相环环路滤波器噪声特性分析与仿真金玉琳;余世刚;周毅;保玲【摘要】为估计环路滤波器对锁相频率合成器输出相位噪声的贡献,建立了一种常用的有源差分环路滤波器噪声模型,并推导出滤波器中各噪声源贡献的噪声的理论公式.针对一实际滤波器贡献的相位噪声进行理论计算,考虑了滤波器中运放的非理想特性后,对滤波器中各个噪声源贡献的相位噪声进行了仿真.通过理论结果和仿真结果对比,得出理论公式对实际环路滤波器噪声进行了很好的估计.最后给出环路滤波器设计时在噪声性能方面的考虑.%It is necessary to accurate phase noise prediction of synthesizer for loop filter's contribution, a noise model for loop filter that is used for differential output phase detector is built, and theoretical formula of the output phase noise contribution from each noise source in loop filter is derived. Theoretical value of phase noise is calculated aimed at the contribution from a actual loop filter, and the phase noise is simulated after considered the actual character of op-amp. Comparing the theoretical value and simulated value, the noise of the actual loop filter can be estimated by theoretical formula, and some considerations of loop filter design about the noise performance are provided.【期刊名称】《现代电子技术》【年(卷),期】2011(034)021【总页数】4页(P193-195,198)【关键词】频率合成器;锁相环;有源环路滤波器;相位噪声【作者】金玉琳;余世刚;周毅;保玲【作者单位】兰州空间技术物理研究所,甘肃兰州 730000;兰州空间技术物理研究所,甘肃兰州 730000;兰州空间技术物理研究所,甘肃兰州 730000;兰州空间技术物理研究所,甘肃兰州 730000【正文语种】中文【中图分类】TN713-34锁相频率合成器其潜在的出色性能、相对简单性和低成本而被普遍使用[1]。

锁相环设计与MATLAB仿真锁相环(Phase-Locked Loop,PLL)是一种电路设计技术,用于提取输入信号中的相位信息,并在输出信号中保持输入信号与输出信号的相位差稳定。

PLL广泛应用于通信系统、时钟生成器、频率合成器等领域。

锁相环主要由相位检测器(Phase Detector,PD)、环路滤波器(Loop Filter,LF)、振荡器(Voltage-Controlled Oscillator,VCO)和分频器(Divider)组成。

相位检测器用于比较输入信号和VCO输出信号的相位差,并产生一个低频的误差信号。

传统的相位检测器包括异或门相位检测器(XOR PD)和倍频器相位检测器(Multiplier PD)。

异或门相位检测器适用于窄带相位差测量,倍频器相位检测器适用于宽带相位差测量。

MATLAB提供了用于建模和仿真PLL的工具箱,可以方便地进行相位检测器的设计和性能分析。

环路滤波器用于滤波相位误差信号,根据滤波器的设计方法不同,可以实现不同的环路特性。

传统的环路滤波器包括积分环路滤波器和比例积分环路滤波器。

积分环路滤波器对误差信号进行积分,使得环路系统具有很高的稳定性和抗干扰能力,但响应时间较长。

比例积分环路滤波器在积分环路滤波器的基础上引入比例增益,可以更快地响应相位误差的变化。

振荡器(VCO)根据环路滤波器输出的控制电压来生成输出信号,并提供给分频器进行频率除法操作。

振荡器通常采用压控振荡器(VCO)或电流模式逻辑(Current Mode Logic,CML)结构,可以根据应用需求选择合适的振荡器设计。

分频器用于将振荡器输出的高频信号按照设定的分频比例进行分频,生成与输入信号相位对齐的输出信号。

分频器采用计数器和锁存器设计,计数器用于记录输入信号的周期数,锁存器将计数器的值锁定在一个周期,输出给相位检测器进行相位比较。

锁相环的设计和仿真可以通过MATLAB工具箱进行。

首先,设计相位检测器的传输函数和特性,选择适当的相位检测器类型和设计参数。

目录中文摘要 (3)英文摘要 (4)前言 (6)第一章绪论 (7)1.1 锁相环的发展及国内外研究现状 (7)1.2 本文的主要内容组织 (9)第二章锁相环的基本理论 (10)2.1锁相环的工作原理 (11)2.1.1鉴相器 (11)2.1.2 低通滤波器 (13)2.1.3 压控振荡器 (15)2.2锁相环的工作状态 (15)2.3锁相环的非线性工作性能分析 (17)2.3.1跟踪性能 (18)2.3.2捕获性能 (18)2.3.3失锁状态 (19)2.4锁相环的稳定性 (20)2.5信号流程图 (21)2.6锁相环的优良特性 (21)2.7锁相环的应用 (22)2.7.1锁相环在调制和解调中的应用 (22)2.7.2锁相环在频率合成器中的应用 (23)2.8本章小结 (23)第三章锁相环的噪声分析 (24)3.1锁相环的输入噪声 (24)3.2压控振荡器的噪声 (24)3.3相位噪声的抑制 (26)3.4本章小结 (27)第四章二阶锁相环仿真及结果 (28)4.1仿真介绍 (28)4.2程序代码 (28)4.3仿真结果 (34)4.4本章小结 (36)结论 (38)致谢 (39)参考文献 (40)毕业设计小结 (41)摘要锁相环电路是使一个特殊系统跟踪另外一个系统,更确切的说是一种输出信号在频率和相位上能够与输入参考信号同步的电路,它是模拟及数模混合电路中的一个基本的而且是非常重要的模块。

由于锁相环具有捕获、跟踪和窄带滤波的作用,因此被应用在通信、微处理器、以及卫星等许多领域。

锁相环是通信电路里时钟电路的一个重要模块。

本文详细介绍了锁相环设计中所涉及的各项指标计。

论文首先对锁相环的发展历史和研究现状做了介绍,然后从其基本工作原理出发,以传统锁相环的结构为基础,得到了锁相环的数学模型,对锁相环的跟踪性能、捕获性能、稳定性以及噪声性能等各种性能进行了分析,对锁相环的各项指标参数进行了详细推导,得出了锁相环数学分析的结论。

三相锁相环及仿真Newly compiled on November 23, 20202三相电压软件锁相环仿真实现锁相环有很多种方法,目前在电力电子装置实际应用中常用的锁相环技术是过零比较方式,就是通过硬件电路检测电网电压的过零点来获得相位差的信号,然后用硬件或者软件实现锁相。

这种方案原理和结构都很简单,也易于工程上的实现。

但是一个工频周期内电网电压只能检测到两个过零点,这限制了锁相环的锁相速度;而且,当电网侧电压中有含有的谐波或这三相不平衡时,这种方法就不能准确的确定基波正序的过零点了,进而而影响了锁相的精度[38]。

为了避免过零点检测方法带来的问题,本文采用三相软件锁相环(SPLL)[39]方法。

电压合成矢量u s与d、q轴电压分量u sd、u sq的关系图如图所示,对于三相电网,电压合成矢量u s的幅值是不变的,则q轴电压分量u sq反映了d轴电压分量u sd与电网电压合成矢量u s的相位关系。

从图中可以看出,当u sq<0时,说明d轴超前u s,应该减小同步信号的频率;u sq>0时,说明d 轴滞后u s,此时应该增大同步信号频率;u sq=0时,说明d轴与u s同相。

可见,可以通过控制电网电压q轴分量u sq=0恒成立,使电网电压合成矢量u s定向于d轴电压分量u sd,实现两者同相位,因此可以得到一个对电压矢量u s进行锁相的方法。

采集得到的压三相对称正弦相电压的瞬时值可以表示为:a m1b m1c m1cos2cos()32cos()3u Uu Uu Uθθπθπ⎧⎪=⎪⎪=-⎨⎪⎪=+⎪⎩(2-36)式中,θ1=ω1t,为输入相位角,ω1为电网角频率;U m为电网电压幅值。

三相对称电压变换到两相静止坐标系α、β轴电压分量u sα、u sβ,两相静止αβ坐标系再经两相旋转坐标系变换后得到的d、q轴电压分量u sd、u sq可以表示为:sd m1sq m1cos()sin()u Uu Uθθθθ=-⎧⎪⎨=-⎪⎩(2-36) 式中,θ=ωt,三相电压SPLL的输出相位角,ω输出角频率。

锁相环的matlab的仿真程序(PLL matlab simulation program)% phasell。

M%锁相环(PLL),调整一个本地振荡器的相位。

%与输入的调制信号。

这样的阶段%输入信号被锁定,信号解调。

%也用于PM和FM。

我们将使用闭环系统来实现它。

控制系统这里应用了%技术。

%*********************************************************** ***锁相环一阶闭环透过率的%阶跃响应% h(s)= 1;%系统类型号= 1;%道/ thetai(输出/输入阶段)关闭所有千伏= 1;KD=1;DT = 0.01T=0:dt:2u =(1,长度(t))G11 = [ TF([ 2 * pi *千* KD ]、[ 1 2 * pi *千* KD ])]为其传递函数在给定的讲义[ 11 ] = lsim(G11,U,T)图形情节(t,Y11)xlabel(秒的时间)ylabel(幅度标准”)标题(第一阶'step响应闭环率”)%*********************************************************** ****锁相环一阶闭环误差透过率的阶跃响应所有其他因素h(s)等在这里都一样。

%中来/ thetai(相同的解释。

如上)G12 = [([ 1,0 ],TF [ 1 2 * pi *千* KD ])]误差透过讲义中给出[ 12 ] = lsim(G12,U,T)图形情节(t,Y12)xlabel(秒的时间)ylabel(幅度标准”)标题(第一阶'step响应闭环误差率”)%*********************************************************** *****锁相环一阶闭环透过率的%阶跃响应VCO与输入信号相位之间的百分比% h(s)= 1;%系统类型号= 1;% v2 / thetaiKD=1;G13 = [ TF([ 0 ] [ 1 KD,2 * pi *千* KD ])]为压控振荡器的电压和输入信号透过率[ 13 ] = lsim(G13,U,T)图形情节(t,Y13)xlabel(秒的时间)ylabel(幅度标准”)标题(第一阶'step响应闭环透光率的B / W的VCO和输入阶段”)%*********************************************************** *********锁相环二阶闭环透射率的阶跃响应%系统类型号= 2;%道/ thetai= 3.15ζ= sqrt((π*千* KD)/(2 *))omegan = sqrt(2 * pi *伏* KD *)G21 = [([ 2 *泽塔* TF omegan omegan ^ 2 ]、[ 1 2 *泽塔* omegan omegan ^ 2 ])]【Y21 T ] = lsim(G21,U,T)图形情节(t,Y21)xlabel(秒的时间)ylabel(幅度标准”)标题(二阶锁相环的环路闭合'step响应率)%*********************************************************** **********锁相环二阶闭环误差透过率的阶跃响应%系统类型号= 2;% / thetai中来G22 = [([ 0 ] 0 TF 1,[ 1 2 *泽塔* omegan omegan ^ 2 ])]【Y22 T ] = lsim(G22,U,T)图形情节(t,Y22)xlabel(秒的时间)ylabel(幅度标准”)标题(二阶锁相环的环路闭合'step响应误差率)%*********************************************************** **********锁相环二阶闭环透射率的阶跃响应VCO与输入信号相位之间的百分比%系统类型号= 2;% v2 / thetaiG23 = [ TF(KD KD * [ 0 ]、[ 1 2 * pi *千* 2 * pi *千* KD KD ])]【Y23 T ] = lsim(G23,U,T)图形情节(t,Y23)xlabel(秒的时间)ylabel(幅度标准”)标题(二阶'step响应闭环透光率的B / W的VCO和输入阶段”)%*********************************************************** ***************%锁相环。

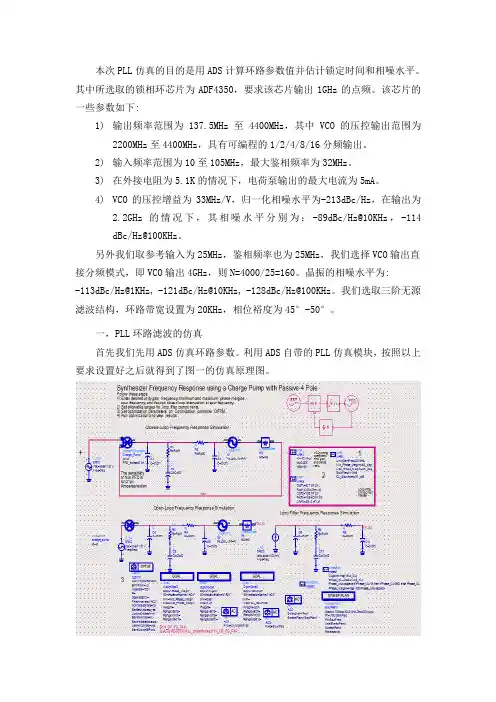

本次PLL仿真的目的是用ADS计算环路参数值并估计锁定时间和相噪水平。

其中所选取的锁相环芯片为ADF4350,要求该芯片输出1GHz的点频。

该芯片的一些参数如下:1)输出频率范围为137.5MHz至4400MHz,其中VCO的压控输出范围为2200MHz至4400MHz,具有可编程的1/2/4/8/16分频输出。

2)输入频率范围为10至105MHz,最大鉴相频率为32MHz。

3)在外接电阻为5.1K的情况下,电荷泵输出的最大电流为5mA。

4)VCO的压控增益为33MHz/V,归一化相噪水平为-213dBc/Hz,在输出为2.2GHz的情况下,其相噪水平分别为:-89dBc/Hz@10KHz,-114dBc/Hz@100KHz。

另外我们取参考输入为25MHz,鉴相频率也为25MHz,我们选择VCO输出直接分频模式,即VCO输出4GHz,则N=4000/25=160。

晶振的相噪水平为:-113dBc/Hz@1KHz, -121dBc/Hz@10KHz, -128dBc/Hz@100KHz。

我们选取三阶无源滤波结构,环路带宽设置为20KHz,相位裕度为45°-50°。

一,PLL环路滤波的仿真首先我们先用ADS仿真环路参数。

利用ADS自带的PLL仿真模块,按照以上要求设置好之后就得到了图一的仿真原理图。

图一 PLL的ADS仿真原理图其中以上模块包括了PLL的闭环特性、参数设置区、PLL的开环特性、环路滤波器部分以及仿真所需要的仿真器和优化目标等。

根据我们仿真的要求,我们只需要把PLL的参数区设置成如图二所示的即可。

图二 PLL变量区的参数设置在图二中,VAR1部分的Kv为VCO的鉴相增益,Id为CP的输出电流,NO为分频因子。

VAR2的五个参数为环路滤波器的参数值,其范围是可以设置的。

VAR3部分的UnityGainFreq为期望的环路带宽值,我们定为20KHz。

Min_Phase_Margin 和Max_Phase_Margin分别是最小和最大的相位裕度值,我们希望相位裕度的值为45至50度。

摘要随着计算机技术的发展,系统仿真技术在电子工程领域的应用已越来越广泛。

SystemView的出现标志着仿真技术在通信领域的应用达到了一个新的水平。

锁相环路作为能自动跟踪信号相位的闭环自动控制系统已获得非常广泛的应用.将锁相技术应用应用于频率合成器的设计中,既可以满足频率合成器的高精度、高稳定度的性能要求;又可使频率合成器的体积缩小、成本降低;同时频道转换便捷,使之能方便的应用于移动通信领域.论文介绍了锁相环路的基本工作原理及特性,在分析了锁相频率合成器的组成原理后,提出了在SystemView环境下的锁相环路频率合成器的设计方案,并调试成功。

关键词:SystemView;锁相技术;频率合成器;仿真ABSTRACTSystem simulation skills are widely used in area of electronic engineering as the developing of computer technique。

Appearance of the software SystemView represents a new level of simulation skills in communication fields. The phase—lock loop (PLL) can not only satisfy the requirement of high frequency stability and high frequency precision, but also reduce the scale and cost of frequency synthesizer。

At the same time, the channel conversion can be realized conveniently,so the phase-lock frequency synthesizer can be used in the field of the mobile communication。

本次PLL仿真的目的是用ADS计算环路参数值并估计锁定时间和相噪水平。

其中所选取的锁相环芯片为ADF4350,要求该芯片输出1GHz的点频。

该芯片的一些参数如下:1)输出频率范围为137.5MHz至4400MHz,其中VCO的压控输出范围为2200MHz至4400MHz,具有可编程的1/2/4/8/16分频输出。

2)输入频率范围为10至105MHz,最大鉴相频率为32MHz。

3)在外接电阻为5.1K的情况下,电荷泵输出的最大电流为5mA。

4)VCO的压控增益为33MHz/V,归一化相噪水平为-213dBc/Hz,在输出为2.2GHz的情况下,其相噪水平分别为:-89dBc/Hz@10KHz,-114dBc/Hz@100KHz。

另外我们取参考输入为25MHz,鉴相频率也为25MHz,我们选择VCO输出直接分频模式,即VCO输出4GHz,则N=4000/25=160。

晶振的相噪水平为:-113dBc/Hz@1KHz,-121dBc/Hz@10KHz,-128dBc/Hz@100KHz。

我们选取三阶无源滤波结构,环路带宽设置为20KHz,相位裕度为45°-50°。

一,PLL环路滤波的仿真首先我们先用ADS仿真环路参数。

利用ADS自带的PLL仿真模块,按照以上要求设置好之后就得到了图一的仿真原理图。

图一 PLL的ADS仿真原理图其中以上模块包括了PLL的闭环特性、参数设置区、PLL的开环特性、环路滤波器部分以及仿真所需要的仿真器和优化目标等。

根据我们仿真的要求,我们只需要把PLL的参数区设置成如图二所示的即可。

图二 PLL变量区的参数设置在图二中,VAR1部分的Kv为VCO的鉴相增益,Id为CP的输出电流,NO为分频因子。

VAR2的五个参数为环路滤波器的参数值,其范围是可以设置的。

VAR3部分的UnityGainFreq为期望的环路带宽值,我们定为20KHz。

Min_Phase_Margin 和Max_Phase_Margin分别是最小和最大的相位裕度值,我们希望相位裕度的值为45至50度。

锁相环的ADS仿真实验报告一.ADF4113芯片介绍1.概述频率合成器中的ADF4113可用于在上变频和下变频上执行本地振荡器,无线接收器和发送器部分。

他们包括一个低噪声数字PFD(相位频率侦测器),一个精密电荷泵,一个可编程参考分频器,可编程A和B计数器和一个双模预置分频器性(P/P+1)。

A(6-bit)和B(13-bit)计数器,会同双模分频器性(P/P+1),实现一个N分频器(N =BP+A)。

此外,14位的参考计数器(R计数器)在PFD 输入时允许投入可选REFIN频率。

如果用合成器被一个外部环路滤波器和电压控制振荡器使用,那么一个完整的PLL(锁相环)就可实现。

该器件工作在2.7 V至5.5 V的电压供应范围内,并且可以不使用时使其开路。

2.电路描述参考输入部分:参考输入级如图24。

SW1和SW2是常闭开关。

SW3是常开。

当电源关闭时,SW3是封闭的和SW1和SW2打开。

这将确保在电源关闭在REFIN引脚上没有加载。

射频输入级:RF输入阶段如图25所示。

其次是一个2级限幅放大器生成一个CML(电流模式逻辑)时钟电平所需的预分频器。

预分频器性(P / P+1)该双模预置分频器性(P / P+1),随着A和B计数器,使大型分频比,N,实现(每组的BP +A)。

该双模预分频器,操作在CML时钟电平,对CMOS A 和B计数器需要设置时钟从射频输入级平台并划分到了可管理的频率。

预分频器是可编程的。

它可以设置软件到达8 / 9,16/17,32/33,或64/65。

它是基于同步4 / 5的核心。

A和B计数器A和B的CMOS计数器连结模数双重预分频器,使其允许在一个广泛的区域的PLL反馈比例不等计数器。

计数器将被指定的工作,当预分频器的输出小于等于200MHz。

因此,随着一个 2.5GHz的RF输入,分频器16/17的频率值是有效的,但对8 / 9值无效。

相位频率侦测器(PFD)和电荷泵在PFD需要从R计数器和N计数器输入(N=BP + A)并且按比例生成的、输出相位和它们之间的频率差。

PLL(锁相环电路原理及设计[收藏]PLL(锁相环电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环(相位锁栓回路,PhaseLockedLoop技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一 PLL(锁相环电路的基本构成PLL(锁相环电路的概要图1所示的为PLL(锁相环电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率成为一致。

PLL(锁相环可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

如果有相位差存在时,便会产生正或负的脉波输出。

一种捷变频锁相环设计研究厉家骏;张福洪;陆家明【摘要】VCO预置电压技术为实现锁相环快速锁定提供了较好的解决方案.分析了电压预置的原理的实现可行性和针对具体PLL的优化设计.提出了电压预置技术具体的系统实现流程和电压预置后可能会产生环路失锁等现象,通过一些具体辅助电路的加入来解决快速跳频和环路锁定的问题.运用ADS仿真设计软件搭建PLL框架,观察预置电压后的锁定时间.仿真结果表明,使用该技术后环路的锁定时间大幅度缩短.【期刊名称】《通信技术》【年(卷),期】2015(048)010【总页数】4页(P1192-1195)【关键词】锁相环;捷变频;电压预置;频率合成器【作者】厉家骏;张福洪;陆家明【作者单位】杭州电子科技大学通信工程学院,浙江杭州310018;杭州电子科技大学通信工程学院,浙江杭州310018;杭州电子科技大学通信工程学院,浙江杭州310018【正文语种】中文【中图分类】TN911.8经历80年的时间沉淀,频率合成技术的理论已经达到了一定的高度。

在电子系统方面的应用实践也日益增加,频率合成技术也相继的走向成熟,也逐渐的走向辉煌。

频率源作为电子系统的关键设备之一,同时也作为跳频系统中不可或缺的一部分,对整个系统起到了关键性作用。

跳频通信系统被作为当代军事,雷达和卫星导航的热门话题,那么一个好的频率源对整个跳频系统来说是至关重要。

在现代局部战争中,电子对抗与反对抗都对频率合成器的性能提出了新的较高的要求,而快跳频率源[1]为抗干扰,抗捕获提供了重要的保证。

所以本设计的核心内容是对频率源的频率切换速度进行提高即致力于研究一个快速跳频的频率合成系统。

一般的锁相环(Phase Locked Loop,PLL)式频率合成系统的跳频时间都在几十微秒至二百微秒,如果能将跳频时间缩短到10 μs以内,那么会对频率合成系统的研制和跳频通信系统的发展都有着重要的意义。

而由HITTITE公司出的HMC830、HMC833等PLL芯片内部均采用了电压预置的手段来提高跳频速度。

锁相环设计调试小结一、系统框图二、锁相环基础知识及所用芯片资料(摘录)(一)、并行输入 PLL (锁相环)频率合成器MC145152-2MC145152 是 MOTOROLA 公司生产的大规模集成电路,它是一块采用并行码输入方式设定,由16根并行输入数据编程的双模 CMOS-LSI 锁相环频率合成器,其内部组成框图如图 3-32-3 所示。

N 和 A 计数器需要 16 条并联输入线,而 R 计数器则需要三条输入线。

该芯片内含参考频率振荡器,可供用户选择的参考频率分频器(12X8 ROM 参考译码器和12BIT ÷R 计数器组成的参考频率fr ),双端输出相位检测器,逻辑控制,10比特可编程序的÷N(N=3~1023) 计数器和 6比特可编程的÷A(A=3~63)计数器和锁定检测部分.10比特 ÷ N 计数器,6 比特÷ A 计数器,模拟控制逻辑和外接双模前置分频器(÷P /÷P +1)组成吞食脉冲程序分频器,吞脉冲程序分频器的总分频比为:N T =P*N+A 。

MC145152 的功能:* 借助于 CMOS 技术而取得的低功耗。

* 电源电压范围 3~9V 。

* 锁相检测信号。

* 在片或离片参考振荡器工作。

* 双模并行编程。

* N 范围 =3~1023,A 范围 =0~63。

*用户可选的 8 个 R 值:8 ,64 , 128 , 256 , 512 , 1024 , 1160 ,2048. * 芯片复杂度——8000 个场效应管或 2000 个等效门。

鉴相器MC145152 环路滤波器 LPF压控振荡器 MC1648分频器MC12017频率输出引脚说明:N0-N9 (11-20 ):÷ N 计数器的编程输入端。

当÷ N 计数器的计数为0 时,这N个输入供给预置÷ N 计数器的数据。

N0 为最低位,N9 为最高位。