飞思卡尔新手上路——总线频率设置

- 格式:pdf

- 大小:146.49 KB

- 文档页数:4

飞思卡尔寄存器使⽤PLLSEL:选定锁环位 1 选定锁相环时钟0 选定外部时钟PSTP:选定伪停⽌位伪停⽌模式下振荡器(⼯作1)/(停⽌0)SYSWAI:选定时钟停⽌位等待模式下系统时钟(停⽌1)/(继续⼯作0)ROAWAI:等待模式下降低振荡器放⼤倍数位1 等待模式下降低振荡器放⼤倍数0 等待模式下振荡器正常放⼤倍数PLLWAI:等待模式下锁相环停⽌⼯作位1等待模式下锁相环停⽌⼯作0等待模式下锁相环正常⼯作CWAI:等待模式下内核时钟停⽌⼯作位1 等待模式下内核时钟停⽌⼯作0 等待模式下内核时钟正常⼯作RTIWAI:等待模式下实时时钟停⽌⼯作位1 等待模式下实时时钟停⽌⼯作0 等待模式下实时时钟正常⼯作COPWAI:等待模式下看门狗时钟停⽌⼯作位1 等待模式下看门狗时钟停⽌⼯作0 等待模式下看门狗时钟正常⼯作CME:时钟监控使能位。

PLLON:锁相环电路使能位。

AUTO:⾃动带宽控制位 1 选择⾼频带宽控制0 选择低频带宽控制ACQ:⾃动带宽控制滤波器选择位(当AUTO=1时,该位⽆意义)。

PRE:CPU 伪停⽌状态时,实时中断(RT1)允许位。

PCE:CPU 虚拟停⽌时,看门狗(COP)允许位。

SCEM:⾃给时钟⽅式使能位,默认为1,探测到外部晶振停振时进⼊⾃给时钟模式,为0时,禁⽌⾃给时钟模式,探测到外部晶振停振时复位。

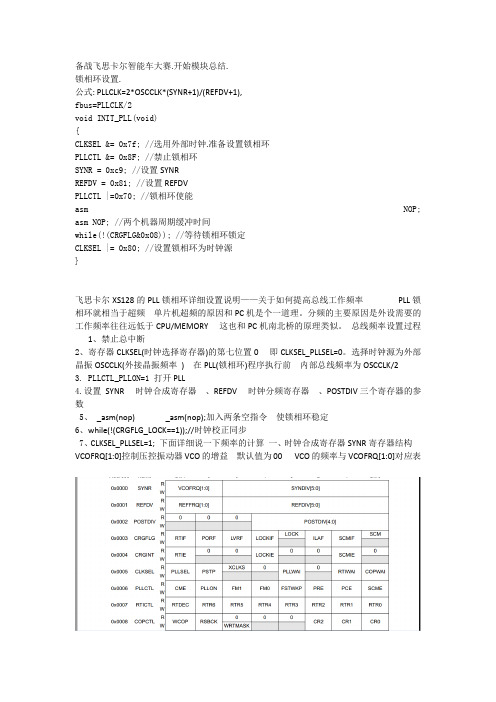

时钟合成寄存器SYNR读写Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0Read 0 0SYN5 SYN4 SYN3 SYN2 SYN1 SYN0 WriteVCOFRQ[1:0](BIT7 BIT6)控制压控振动器VCO的增益,默认值为00,VCO的频率与VCOFRQ[1:0]对应表如下所⽰:读写Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Read/Write REFFRQ1 REFFRQ0 REFDV5 REFDV4 REFDV3 REFDV2 REFDV1 REFDV0 REFFRQ[1:0]默认值为00,表⽰参考时钟频率在1~2MHZ之间,要求的参考时钟频率与REFFRQ[1:0]的设置值如下表如⽰:读写Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0ReadRTIF PORF 0LOCKIFLOCK TRACKSCMIFSCMWriteRTIF:实时中断(RTI)标志位 1 发⽣实时中断0 未发⽣实时中断PROF:上电复位标志位 1 发⽣上电复位0 未发⽣上电复位LOCKIF:锁相环中断标志位1 锁相环锁定位发⽣变化时,产⽣中断请求0 锁相环锁定位未发⽣变化LOCK:锁相环频率锁定标志,为1表⽰时钟频率已稳定,锁相环频率已锁定。

飞思卡尔16位单片机9S12XS128使用收藏最近做一个关于飞思卡尔16位单片机9S12XS128MAA的项目,以前未做过单片机,故做此项目颇有些感触。

现记录下这个艰辛历程。

以前一直是做软件方面的工作,很少接触硬件,感觉搞硬件的人很高深,现在接触了点硬件发现,与其说使用java,C#等语言写程序是搭积木,不如说搞硬件芯片搭接的更像是在搭积木(因为芯片是实实在在拿在手里的东西,而代码不是滴。

还有搞芯片内部电路的不在此列,这个我暂时还不熟悉)。

目前我们在做的这个模块,就是使用现有的很多芯片,然后根据其引脚定义,搭接出我们需要的功能PCB板,然后为其写程序。

废话不多说,进入正题。

单片机简介:9S12XS128MAA单片机是16位的单片机80个引脚,CPU是CPU12X,内部RAM 8KB,EEPROM:2KB,FLASH:128KB,外部晶振16M,通过内部PLL可得40M总线时钟。

9S12XS128MAA单片机拥有:CAN:1个,SCI:2个,SPI:1个,TIM:8个,PIT:4个,A/D:8个,PWM:8个下面介绍下我们项目用到的几个模块给出初始化代码1、时钟模块初始化单片机利用外部16M晶振,通过锁相环电路产生40M的总线时钟(9S12XS128系列标准为40M),初始化代码如下:view plaincopy to clipboardprint?/******************系统时钟初始化****************/void Init_System_Clock(){asm { // 这里采用汇编代码来产生40M的总线LDAB #3STAB REFDVLDAB #4STAB SYNRBRCLR CRGFLG,#$08,*//本句话含义为等待频率稳定然后执行下一条汇编语句,选择此频率作为总线频率BSET CLKSEL,#$80}}/******************系统时钟初始化****************/void Init_System_Clock(){asm { // 这里采用汇编代码来产生40M的总线LDAB #3STAB REFDVLDAB #4STAB SYNRBRCLR CRGFLG,#$08,*//本句话含义为等待频率稳定然后执行下一条汇编语句,选择此频率作为总线频率BSET CLKSEL,#$80}}上面的代码是汇编写的,这个因为汇编代码量比较少,所以用它写了,具体含义注释已经给出,主函数中调用此函数即可完成时钟初始化,总线时钟为40M.2、SCI模块初始化单片机电路做好了当然少不了和PC之间的通信,通信通过单片机串口SCI链接到PC 端的COM口上去。

Freescale Semiconductor, Inc.Document Number: 用户指南 Rev. 0, 09/2014Confidentiality statement, as appropriate to document/part status.___________________________________________________________________飞思卡尔单片机快速上手指南作者:飞思卡尔半导体IMM FAE 团队飞思卡尔半导体是全球领先的单片机供应商,其单片机产品包含多种内核,有数百个系列。

为支持用户使用这些产品,飞思卡尔提供了丰富的网站资源、文档及软硬件工具,另外,我们还有众多的第三方合作伙伴及公共平台的支持。

对于不熟悉飞思卡尔产品和网站的初学者来说,了解和使用这些资源这无疑是一个令人望而生畏的浩瀚工程。

本指南的目的,就是给初学者提供一个指导,让他们不被这些海量信息淹没;用户根据本指导提供的操作步骤,能迅速找到所需的资源,了解如何使用相关的工具。

在本指南中,我们以飞思卡尔的新一代Kinetis 单片机K22系列为例,介绍了如何获取与之相关的资源,如何对其进行软硬件设计和开发。

实际上,这些方法也适用于其它的单片机系列。

当然,对于其它有较多不同之处的产品,我们也会继续推出相应的文档,供广大用户参考。

目录1 如何获取技术资料与支持 ..........................................................2 2 如何选择产品、申请样片及购买少量芯片和开发工具 ........... 93 飞思卡尔单片机的开发环境、开发工具和生态系统 ............. 224 如何阅读飞思卡尔的技术文档 ................................................ 45 5 飞思卡尔单片机硬件设计指南 ................................................ 55 6飞思卡尔单片机软件开发指南 (67)飞思卡尔单片机快速上手指南, Rev. 1, 09/20142Freescale Semiconductor, Inc.1 如何获取技术资料与支持1.1 概述当用户使用飞思卡尔单片机芯片时,如何获取芯片的数据手册(Datasheet )、参考设计(Reference Manual )和官方例程等资源呢?另外当用户遇到了技术问题该如何获得帮助和解答呢?这里以Kinetis 的K22系列芯片为例为大家介绍如何解决这些问题。

备战飞思卡尔智能车大赛.开始模块总结.锁相环设置.公式: PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1),fbus=PLLCLK/2void INIT_PLL(void){CLKSEL &= 0x7f; //选用外部时钟.准备设置锁相环PLLCTL &= 0x8F; //禁止锁相环SYNR = 0xc9; //设置SYNRREFDV = 0x81; //设置REFDVPLLCTL |=0x70; //锁相环使能asm NOP; asm NOP; //两个机器周期缓冲时间while(!(CRGFLG&0x08)); //等待锁相环锁定CLKSEL |= 0x80; //设置锁相环为时钟源}飞思卡尔XS128的PLL锁相环详细设置说明——关于如何提高总线工作频率PLL锁相环就相当于超频单片机超频的原因和PC机是个一道理。

分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY这也和PC机南北桥的原理类似。

总线频率设置过程1、禁止总中断2、寄存器CLKSEL(时钟选择寄存器)的第七位置0即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK(外接晶振频率)在PLL(锁相环)程序执行前内部总线频率为OSCCLK/23. PLLCTL_PLLON=1 打开PLL4.设置SYNR时钟合成寄存器、REFDV时钟分频寄存器、POSTDIV三个寄存器的参数5、_asm(nop) _asm(nop);加入两条空指令使锁相环稳定6、while(!(CRGFLG_LOCK==1));//时钟校正同步7、CLKSEL_PLLSEL=1; 下面详细说一下频率的计算一、时钟合成寄存器SYNR寄存器结构VCOFRQ[1:0]控制压控振动器VCO的增益默认值为00VCO的频率与VCOFRQ[1:0]对应表什么是锁相环呢?MCU的支撑电路一般需要外部时钟来给MCU提供时钟信号,而外部时钟的频率可能偏低,为了使系统更加快速稳定运行,需要提升系统所需要的时钟频率。

飞思卡尔DG128—PE编程入门教程(1)首先打开CodeWarrior 5.0 开发环境,然后在弹出的选项中选择新建工程注释:如果没有弹出这个对话框,可以在下面的File中选择New Project新建一个工程。

(2) 选择开发芯片的型号(这里我们使用的是MC9S12DG128)接着选择TBDML,这个是我们使用在线调试功能的选项。

(3) 选择工程的生成路径,注意:如果我们不使用PE编程功能的话,在这步结束后,可以直接选择完成按钮来完成工程的新建。

(4) (PE编程功能的步骤)下一步,这个对话框我们什么都不用选择,直接点击下一步。

(5)选择下面这个选项来启动PE编程功能。

(6) 红色边框中选项的功能为是否启动浮点数据的使用,默认第一个是不启用;第二个是启用,float数据为32位,double为32位;第三个是启用,float 数据为32位,double数据为64位。

(7)最后一步什么都不要设置,直接点击完成。

(8) 以上步骤我们完成了一个DG128工程的新建步骤。

PE的使用步骤:(1) 新建工程后,会自动弹出个芯片封装型号的选择,选择后点击OK。

(注意:我们学校使用的芯片是112管脚,所以注意选择红线标注的选项)(2) 点击OK后,就会出现我们要编程的环境了。

如下所示:(3)红色标注的地方就是该工程的工作区。

细心的同学就会发现,它生成的文件中没有我们需要写的源文件XXX.c 。

那我们现在就来生成这些文件,找到下图的选项Processor Expert 。

然后点击第二个选项的Generate Code ' XXX .mcp' (这里的XXX 表示该工程名称)。

下面是自动生成的文件。

这时候发现软件为我们自动的生成了一个Project.c (Project 是我这个工程建立的文件命,不同的工程文件名将导致这个名字不同)的文件。

这个就是我们将要编写的源文件了,它里面包含了主函数main()。

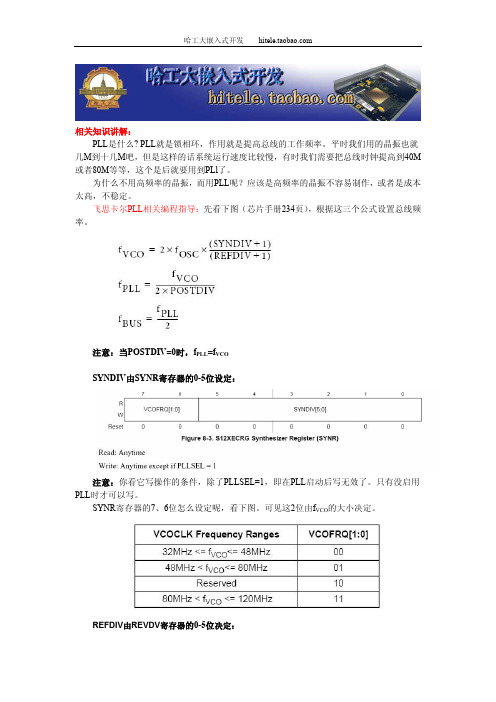

相关知识讲解:PLL是什么? PLL就是锁相环,作用就是提高总线的工作频率。

平时我们用的晶振也就几M到十几M吧,但是这样的话系统运行速度比较慢,有时我们需要把总线时钟提高到40M 或者80M等等,这个是后就要用到PLl了。

为什么不用高频率的晶振,而用PLL呢?应该是高频率的晶振不容易制作,或者是成本太高,不稳定。

飞思卡尔PLL相关编程指导:先看下图(芯片手册234页),根据这三个公式设置总线频率。

注意:当POSTDIV=0时,f PLL=f VCOSYNDIV由SYNR寄存器的0-5位设定:注意:你看它写操作的条件,除了PLLSEL=1,即在PLL启动后写无效了。

只有没启用PLL时才可以写。

SYNR寄存器的7、6位怎么设定呢,看下图。

可见这2位由f VCO的大小决定。

REFDIV由REVDV寄存器的0-5位决定:PLL初始化步骤:1. 设定总线频率由外部晶振频率决定2. 设置PLL相关参数,改变f BUS 值3. 等待PLL稳定4. 设定总线频率由f PLL决定外部晶振我们选用16M,假如设置f BUS=40M,怎么设置呢?假如要设置f BUS=40M,则f PLL=80M,令POSTDIV=0,则f PLL=f VCO=80M,根据下图,VCOFRQ=01, 80M=2*16M*(SYNDIV+1)/(REFDIV+1),即(SYNDIV+1)/(REFDIV+1)=5/2,可以设SYNDIV=4,REFDIV=1.这样系统的时钟就设置成了40M。

实际应用:将系统时钟设置成40M,并根据此设置定时器,每隔400ms led闪烁一次。

CLKSEL=0X00; // 初始化PLL前先使用外部晶振PLLCTL_PLLON=1; // 开启PLLSYNR =0x40 | 0x04; // pllclock=2*osc*(1+SYNR)/(1+REFDV)=80MHz;REFDV=0x80 | 0x01;POSTDIV=0x00;_asm(nop); // BUS CLOCK=40M_asm(nop);while(!(CRGFLG_LOCK==1)); //等待PLL稳定CLKSEL_PLLSEL =1; //fBUS采用根据PLL频率设定这样就设定了总线时钟为40M,定时器设置参见实验2-定时器.。

M=2.一、关键点1、MC 模块驱动电机的PWM 波频率在20K 左右时效果比较好。

DITH 位等于0时,计算方法如下:DITH=1时,其中,左对齐和有对齐方式下 M=1,中间对齐是2、MC 模块定时计数器的中断最好禁止,如果开启,在相应的中断服务程序中至少要添加一条“清楚中断标志位”的指令。

3、电机控制模块共8个通道,每个通道有2个Pin 脚组成。

4、Fast 位控制精度,7位或者11位。

5、给周期寄存器写入数值,可启动 MC 计数器,写0关闭所有通道的计数器。

6、MCAM[1:0]写入0x00可关闭某个channel ,写入非零值不是启动MC 计数器,而是控制对齐方式。

为了精确周期寄存器的值应尽量大,Ftc 应尽量小。

二、寄存器寄存器讲解讲解讲解::1 MCCTL0 (Motor Controller Control Register 0)第7位保留;第6、5位是MCPRE[1:0]控制电机控制器定时计数器时钟f TC 预分频系数。

如下:第4位 MCSWAI 置1,等待模式中电机控制器正常运行,清0,在等待模式中电机控制模块时钟关闭。

第3位,FAST ,清0,电机控制器PWM 模块占空比寄存器分辨率设置为11位,置1,电机控制器PWM 模块占空比寄存器分辨率设置为7位。

第2位,DITH ,清零,电机控制器dith 特性禁止,置1电机控制器dith 特性使能。

第1位保留;第0位MCTOIF ,为1表示,电机控制模块定时计数器溢出;为0,表示自上次复位或清零以来,电机控制模块定时计数器没有发生溢出。

2 MCCTL1 (Motor Controller Control Register 1)第7位,RECIRC控制PWM波极性。

0表示—,1表示+ ;第6到第1位系统保留;第0位,MCTOIE,为0表示Motor Controller Timer Counter Overflow Interrupt禁止,为1标志使能。

飞思卡尔初学之PWM调试笔记M9S12XS128 单片机有8 个独立的PWM 输出通道,其中每相邻的两个可以级联成一个通道。

本文着重应用实践,理论性的东西少谈为妙,因为理论的东西资料上都有。

想借此平台记录下调试心得以免日后遗忘,因本人也是初学该款单片机,难免有错误之处,还希望达人指点。

PWM 应用步骤:一、PLL 初始化,这一步应该说不算PWM 设置的内容,但是又必须设置,因为这关系着PWM 周期值的计算。

从开发板上的晶振来看是16M,但是总线时钟却并不是16M,S12 单片机里面有个锁相环设置,要设置好了才准确。

具体这个PLL 函数我还没去了解。

现在是现成套用。

void PLL_Init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1){ //锁相环时钟=2*16*(2+1)/(1+1)=48MHzCLKSEL=0X00;PLLCTL=0XE1;REFDV = 1; //总线时钟=48/2=24MHzSYNR = 2;_asm(nop); // BUS CLOCK=24M_asm(nop);while (!(CRGFLG & 0x08)) ;CLKSEL = 0x80; //选定锁相环时钟}用了这个PLL 初始化函数以后,总线时钟就是24M 了。

二、PWM 相关设置1、禁止PWM。

PWME2、选择时钟源。

PWMPRCLK, PWMSCLA, PWMSCLB ,PWMCLK。

其中通道0 、1、4、5 可以选择ClockA ClockSA。

通道2、3、6、7 可以选择ClockB ClockSB其中值得说明的是ClockA 或ClockB 是通过总线时钟预分频获得的。

ClockSA 或ClockB 是分别对ClockA ClockB 再次进行分频获得的。

分频系数的设置都有相应的寄存器进行设置。

后面会提到。

飞思卡尔XS128的PLL锁相环详细设置说明——关于如何提高总线工作频率PLL锁相环就相当于超频,单片机超频的原因和PC机是个一道理。

分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY,这也和PC机南北桥的原理类似。

总线频率设置过程:1、禁止总中断2、寄存器CLKSEL(时钟选择寄存器)的第七位置0,即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK(外接晶振频率),在PLL(锁相环)程序执行前,内部总线频率为OSCCLK/23. PLLCTL_PLLON=1 打开PLL4.设置SYNR(时钟合成寄存器)、REFDV(时钟分频寄存器)、POSTDIV三个寄存器的参数5、_asm(nop)_asm(nop);加入两条空指令,使锁相环稳定6、while(!(CRGFLG_LOCK==1));//时钟校正同步7、CLKSEL_PLLSEL=1;下面详细说一下频率的计算一、时钟合成寄存器SYNR寄存器结构:VCOFRQ[1:0]控制压控振动器VCO的增益,默认值为00,VCO的频率与VCOFRQ[1:0]对应表如下所示:SYNDIV[5:0]为频率合成因子,值为0~63。

二、时钟分频寄存器REFDV:REFFRQ[1:0]默认值为00,表示参考时钟频率在1~2MHZ之间,要求的参考时钟频率与REFFRQ[1:0]的设置值如下表如示:REFDIV[5:0]为分频因子REFDV的值,有效值为0~63。

三、POSTDIV寄存器公式1:Fvco=2*osc*(1+SYNDIV)/(1+REFDIV)公式2:Fpll=Fvco/(2*POSTDIV) 如果POSTDIV=0时Fpll=Fvco公式3:BUSCLOCK=Fpll/2下面是一段产生80MHz总线频率的代码://PLL锁相环void SetbusCLK_80M()//设置总线时钟{CLKSEL=0x00;//释放PLL到系统PLLCTL_PLLON=1;//打开PLLSYNR=0xc0|0x09;//参数1REFDV=0x80|0x01;//参数2POSTDIV=0x00;//参数3//Fvco=2*osc*(1+SYNDIV)/(1+REFDIV) 2*16*(1+9)/(1+1)=160MHz //Fpll=Fvco/(2*POSTDIV) 如果POSTDIV=0时Fpll=Fvco=160MHz //BUSCLOCK=Fpll/2=80MHz//以下指令可以使PLL稳定_asm(nop);//空指令,使锁相环稳定_asm(nop);while(!(CRGFLG_LOCK==1));//时钟校正同步CLKSEL_PLLSEL=1;。