数字电子技术基础(数字电路)第五章触发器

- 格式:ppt

- 大小:2.50 MB

- 文档页数:57

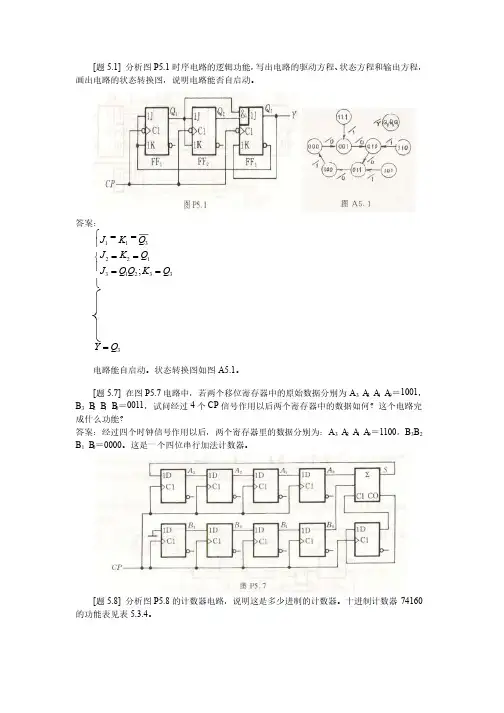

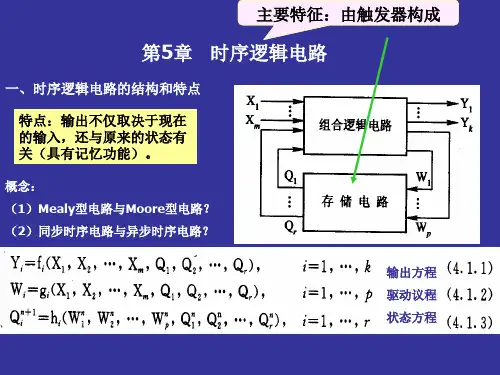

[题5.1] 分析图P5.1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

画出电路的状态转换图,说明电路能否自启动。

答案:答案:11322131233;J K QJ K Q J Q Q K Q ì==ï==íï==î3Y Q =电路能自启动。

状态转换图如图A5.1。

[题5.7] 在图P5.7电路中,若两个移位寄存器中的原始数据分别为A 3 A 2 A 1 A 0=1001,B 3 B 2 B 1 B 0=0011,试问经过4个CP 信号作用以后两个寄存器中的数据如何?这个电路完成什么功能?成什么功能?答案:经过四个时钟信号作用以后,两个寄存器里的数据分别为:A 3 A 2 A 1 A 0=1100,B 3B 2B 1 B 0=0000。

这是一个四位串行加法计数器。

这是一个四位串行加法计数器。

[题5.8] 分析图P5.8的计数器电路,说明这是多少进制的计数器。

十进制计数器74160的功能表见表5.3.4。

答案:答案:电路为七进制计数器。

图P5.8电路为七进制计数器。

[题5.9] 分析图P5.9的计数器电路,画出电路的状态转换图,说明这是多少进制的计数器。

十六进制计数器74LS161的功能表见表5.3.4。

答案:答案:。

这是一个十进制计数器。

电路的状态转换图如图A5.9。

这是一个十进制计数器。

[题5.10] 试用4位同步二进制计数器74LS161接成十二进制计数器,标出输入、输出端。

可以附加必要的门电路。

74LS161的功能表见表5.3.4。

答案:答案:见图A5.10 [题5.11] 试分析图P5.11的计数器在M=1和M=0时各为几进制。

74160的功能表见表5.3.4。

答案:答案:M=1时为六进制计数器,M=0时为八进制计数器。

时为八进制计数器。

[题5.16] 图P5.16电路是由两片同步十进制计数器74160组成的计数器,试分析这是多少进制的计数器,两片之间是几进制。

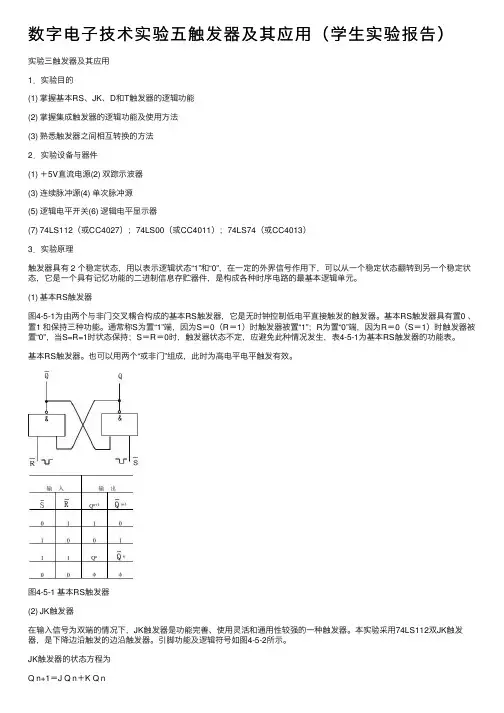

数字电⼦技术实验五触发器及其应⽤(学⽣实验报告)实验三触发器及其应⽤1.实验⽬的(1) 掌握基本RS、JK、D和T触发器的逻辑功能(2) 掌握集成触发器的逻辑功能及使⽤⽅法(3) 熟悉触发器之间相互转换的⽅法2.实验设备与器件(1) +5V直流电源(2) 双踪⽰波器(3) 连续脉冲源(4) 单次脉冲源(5) 逻辑电平开关(6) 逻辑电平显⽰器(7) 74LS112(或CC4027);74LS00(或CC4011);74LS74(或CC4013)3.实验原理触发器具有 2 个稳定状态,⽤以表⽰逻辑状态“1”和“0”,在⼀定的外界信号作⽤下,可以从⼀个稳定状态翻转到另⼀个稳定状态,它是⼀个具有记忆功能的⼆进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。

(1) 基本RS触发器图4-5-1为由两个与⾮门交叉耦合构成的基本RS触发器,它是⽆时钟控制低电平直接触发的触发器。

基本RS触发器具有置0 、置1 和保持三种功能。

通常称S为置“1”端,因为S=0(R=1)时触发器被置“1”;R为置“0”端,因为R=0(S=1)时触发器被置“0”,当S=R=1时状态保持;S=R=0时,触发器状态不定,应避免此种情况发⽣,表4-5-1为基本RS触发器的功能表。

基本RS触发器。

也可以⽤两个“或⾮门”组成,此时为⾼电平电平触发有效。

图4-5-1 基本RS触发器(2) JK触发器在输⼊信号为双端的情况下,JK触发器是功能完善、使⽤灵活和通⽤性较强的⼀种触发器。

本实验采⽤74LS112双JK触发器,是下降边沿触发的边沿触发器。

引脚功能及逻辑符号如图4-5-2所⽰。

JK触发器的状态⽅程为Q n+1=J Q n+K Q nJ和K是数据输⼊端,是触发器状态更新的依据,若J、K有两个或两个以上输⼊端时,组成“与”的关系。

Q与Q为两个互补输出端。

通常把 Q=0、Q=1的状态定为触发器0 状态;⽽把Q=1,Q=0定为 1 状态。

图4-5-2 74LS112双JK触发器引脚排列及逻辑符号下降沿触发JK触发器的功能如表4-5-2注:×— 任意态↓— ⾼到低电平跳变↑— 低到⾼电平跳变Q n (Q n )— 现态 Q n+1(Q n+1)— 次态φ— 不定态JK 触发器常被⽤作缓冲存储器,移位寄存器和计数器。

第5章 触发器一、选择题1.为了使钟控RS触发器的次态为1,RS的取值应为()。

[成都理工大学2006 研]A.RS=0B.RS=01C.RS=10D.RS=11【答案】B【解析】当S=l,R=0时,Q=1 、Q'=O 。

在SD=1;当S=0,R=1 时,Q=0,Q'=l;当S=R=0时,电路维持原来的状态不变。

2.设计一“00001111”串行序列发生器,最少需要触发器个数是()。

[电子科技大学2006 研]【答案】B【解析】设有三个不同的变量Q2Q1Q0,前三个状态可以确定下一个状态,比如Q2Q1Q0=000确定输出状态为1,001的时候为1,依次类推,八个输出需要计数器至少有8个不同的状态。

3.(多选)下列所示的电路中,能完成逻辑功能的电路有()。

[北京邮电大学2010研]A B C D【答案】ACD【解析】D 触发器特性方程为=;JK 触发器的特性方程为1n QD +=n Q ;T 触发器特性方程为=;n+1n n Q J Q KQ =+0=n n n Q Q Q Q=+n+1Q TQ TQ =+Q n+11⋅=+=n n nQ Q Q Q Q 二、填空题1.对于D 触发器,欲使则输入D =______。

[成都理工大学2006研]【答案】【解析】根据D 触发器的特性方程,可得2.施密特触发器输入端加正弦波信号,则输出为同频率的______。

[北京工业大学2008研]【答案】矩形脉冲【解析】施密特触发器状态转换过程中的正反馈作用,可以将边沿变化缓慢的周期性信号变换为边沿很陡的矩形脉冲信号3.图5-1为某触发器状态图,该触发器为______触发器。

[北京工业大学2008研]图5-1【答案】D【解析】该触发器只有保持和翻转功能,没有置数功能,所以肯定不是RS 触发器,而JK 触发器需要两个不同变量的输入,图中的变量数只有一个,所以应该是T 触发器或者D 触发器,T 触发器特性方程为,当Q =1时,输入T =1,应该会得到逻辑电平0,而不是1; D 触n+1Q TQ TQ =+发器特性方程为,符合状态转换图。

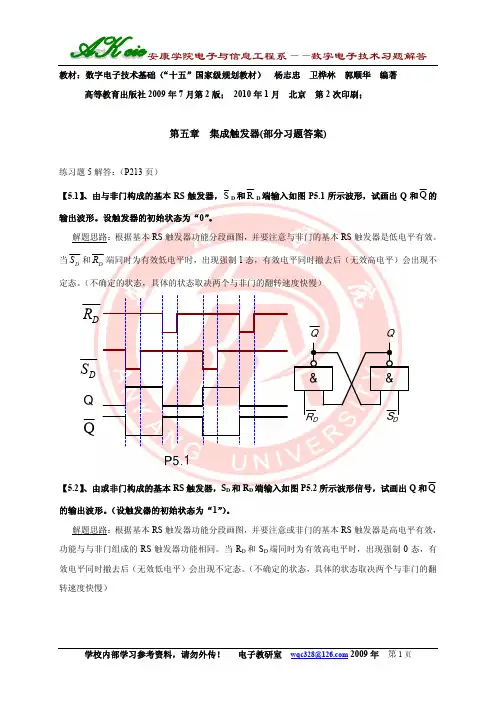

教材:数字电子技术基础(“十五”国家级规划教材) 杨志忠 卫桦林 郭顺华 编著高等教育出版社2009年7月第2版; 2010年1月 北京 第2次印刷;第五章 集成触发器(部分习题答案)练习题5解答:(P213页)【5.1】、由与非门构成的基本RS 触发器,S D 和R D 端输入如图P5.1所示波形,试画出Q 和Q 的输出波形。

设触发器的初始状态为“0”。

解题思路:根据基本RS 触发器功能分段画图,并要注意与非门的基本RS 触发器是低电平有效。

当D S 和D R 端同时为有效低电平时,出现强制1态,有效电平同时撤去后(无效高电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ【5.2】、由或非门构成的基本RS 触发器,S D 和R D 端输入如图P5.2所示波形信号,试画出Q 和Q 的输出波形。

(设触发器的初始状态为“1”)。

解题思路:根据基本RS 触发器功能分段画图,并要注意或非门的基本RS 触发器是高电平有效,功能与与非门组成的RS 触发器功能相同。

当R D 和S D 端同时为有效高电平时,出现强制0态,有效电平同时撤去后(无效低电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ1≥1≥【5.4】、已知同步RS 触发器的输入CP,R 和S 的电压波形如题P5-4图所示的波形,试画出Q 和Q 的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步钟控RS 触发器是电位型触发器(高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,n 1n Q R S Q+=+,约束条件:RS=0,R=S=1时出现1Q Q 1n 1n ==++。

CPSQR【5.5】、已知同步D 触发器CP 和D 端的输入电压波形如P5.5图所示,试画出Q 端的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步式触发器是电位型触发器(假定高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,D Q1n =+。

数字电子技术基础第五版期末知识点总结Company number:【WTUT-WT88Y-W8BBGB-BWYTT-19998】数电课程各章重点第一、二章 逻辑代数基础知识要点各种进制间的转换,逻辑函数的化简。

一、 二进制、十进制、十六进制数之间的转换;二进制数的原码、反码和补码 .8421码二、 逻辑代数的三种基本运算以及5种复合运算的图形符号、表达式和真值表:与、或、非三、 逻辑代数的基本公式和常用公式、基本规则逻辑代数的基本公式逻辑代数常用公式:吸收律:A AB A =+消去律:B A B A A +=+ A B A AB =+多余项定律:C A AB BC C A AB +=++反演定律:B A AB += B A B A •=+基本规则:反演规则和对偶规则,例1-5四、 逻辑函数的三种表示方法及其互相转换逻辑函数的三种表示方法为:真值表、函数式、逻辑图会从这三种中任一种推出其它二种,详见例1-7五、 逻辑函数的最小项表示法:最小项的性质;例1-8六、 逻辑函数的化简:要求按步骤解答1、利用公式法对逻辑函数进行化简2、利用卡诺图对逻辑函数化简3、具有约束条件的逻辑函数化简例1.1 利用公式法化简 BD C D A B A C B A ABCD F ++++=)( 解:BD C D A B A C B A ABCD F ++++=)(例 利用卡诺图化简逻辑函数 ∑=)107653()(、、、、m ABCD Y约束条件为∑8)4210(、、、、m解:函数Y 的卡诺图如下:第三章 门电路知识要点各种门的符号,逻辑功能。

一、三极管开、关状态1、饱和、截止条件:截止:T be V V <, 饱和:βCS BS B I I i =>2、反相器饱和、截止判断二、基本门电路及其逻辑符号与门、或非门、非门、与非门、OC 门、三态门、异或;传输门、OC/OD 门及三态门的应用三、门电路的外特性1、输入端电阻特性:对TTL 门电路而言,输入端通过电阻接地或低电平时,由于输入电流流过该电阻,会在电阻上产生压降,当电阻大于开门电阻时,相当于逻辑高电平。

第5章 触发器5.1 画出图5-1由与非门组成的SR 锁存器输出端Q 、Q′的电压波形,输入端S D ′、R D ′的电压波形如图中所示。

图5-1解:波形图如图5-2所示。

图5-25.2 画出图5-3由或非门组成的SR 锁存器输出端Q 、Q′的电压波形,输入端S D 、R D 的电压波形如图中所示。

图5-3解:波形图如图5-4所示。

图5-45.3 试分析图5-5所示电路的逻辑功能,列出真值表,写出逻辑函数式。

图5-5解:当CLK=0时,S、R的值不能加到或非门,此时Q的状态保持不变。

当CLK=1时,Q的状态随SR的不同而发生变化,真值表如表5-1所示。

表5-1卡诺图如图5-6所示。

图5-6化简得n1+=+Q S R'QSR=。

5.4 图5-7所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通瞬间发生振颤,S D′和R D′的电压波形如图中所示,试画出Q、Q′端对应的电压波形。

图5-7解:Q 、Q′端对应的电压波形如图5-8所示。

图5-85.5 在图5-9所示电路中,若CLK 、S 、R的电压波形如图中所示,试画出Q 和Q′端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图5-9解:当CLK =0时,SR 的值不能加到或非门,此时Q 的状态保持不变。

当CLK =1时,成为与非门组成的SR 触发器。

Q 和Q′端对应的电压波形如图5-10所示。

图5-105.6 若将电平触发SR 触发器的Q 与R 、Q′与S 相连,如图5-11所示,试画出在CLK 信号作用下Q 和Q′端的电压波形。

已知CLK 信号的宽度t W =4t pd 。

t pd 为门电路的平均传输延迟时间,假定t pd ≈t PHL≈t PLH 。

设触发器的初始状态为Q =0。

图5-11解:当CLK =0时,触发器输出保持不变;当CLK =1时,输出随SR 触发器变化。

脉冲的上升沿到来时,S =1,经过G 1门和G 3门的时延,Q 被置1;同时,经过G 2门的时延,G 2门输出为1。

第5章 触发器一、选择题1.为了使钟控RS触发器的次态为1,RS的取值应为()。

A.RS=0B.RS=01C.RS=10D.RS=11【答案】B【解析】当S=l,R=0时,Q=1、Q'=O。

在SD=1;当S=0,R=1时,Q=0,Q'=l;当S=R=0时,电路维持原来的状态不变。

2.4级移位寄存器,现态为0111,经右移一位后其次态为()。

A.0011或1011B.1111或1110C.1011或1110D.0011或1111【答案】B【解析】实际上移位可以看做小数点做移动,右移相当于小数点右移,应该是前三位为111,最后一位不确定,在阎石教科书中所举的例子从左到右是低位到高位进行的变换。

3.用n个触发器构成计数器,可得到的最大计数长度为()。

A.nB.2nC.n3D.2n【答案】D【解析】每个触发器可以计数为0或1两个不同的状态,这些状态彼此独立,最大计数长度为2n。

4.设计一“00001111”串行序列发生器,最少需要触发器个数是()A.4个B.3个C.5个D.8个【答案】B【解析】设有三个不同的变量Q2Q1Q0,前三个状态可以确定下一个状态,比如Q2Q1Q0=000确定输出状态为1,001的时候为1,依次类推,八个输出需要计数器至少有8个不同的状态。

5.图5-1所示电路是()。

A.无稳态触发器B.单稳态触发器C .双稳态触发器D .多谐振荡器图5-1【答案】B【解析】首先该电路有输入端,一定不会是多谐振荡器。

若以555定时器的V I2端作为触发信号的输入端,并将由T D 和R 组成的反相器输出电压v OD 接至V I1端,同时在V I1对地接入电容C ,则构成单稳态触发器。

6.为将D 触发器转换为T 触发器,图5-2所示电路的虚线框内应是( )。

A .或非门B .与非门C .异或门D .同或门图5-2【答案】D【解析】由T 触发器和D 触发器的触发方程可得:Q n +1=D ;Q n +1=T ’Q n +TQ n ’,需要令输入D =T ’Q n +TQ n ’,与Q n ’作同或运算,与Q n 作异或运算。