pads logic off

- 格式:docx

- 大小:2.53 MB

- 文档页数:38

PADS中英⽂对照表⼯作区(Working Area库(Library)元件(Part)连线(Connection)、总线(Bus)、使⽤页间连接符号(Off-Page)移动(Move)、拷贝(Copy)、删除(Delete)查询/修改(Query/Modify)和编辑(Edit)等操作⽅式(Mode)参阅在线帮助(On-line Help) 管脚符号(Pin Symbols 逻辑符号(LogicSymbols)元件类型编辑器(Part Type Editor添加端点(Add TerminalX 镜像(X Mirror⽹表(Netlist)和SPICE 格式⽹络表⼯程设计更改(Engineering Change Orders (ECO))。

嵌⼊(OLE) 设置栅格(Grids)使⽤取景( Pan)缩放(Zoom)下拉菜单(Pull-down)菜单(Menu)菜单/ 命令(Menu/Command)⽂件/打开(File/Open)弹出菜单(Pop-up Menus)Filter…⾃⾏选择配置过滤项⽬⼯具条(Toolbars)⼯具盒(Toolboxes)设计(Design)⼯具盒选择(Selection)⼯具盒图标(Icons)⽆模命令(Modeless Commands)快捷键(Shortcut Keys)选择取消(Cancel)光标(Cursor)状态条(Status Bar)设置栅格(Grids) 设计栅格(Design Grid)PADS Logic 有两类栅格(Grid):设计栅格(Design Grid)和显⽰栅格(Display Grid)。

连线(Connections)多边形(Polygons)、不封闭图形(Paths)、圆(Circles)和矩形(Rectangles)。

⼯具/选项(Tools/Options)命令显⽰栅格(Display Grid)全局(Global)标签栅格练习(Grid Exercise)选项(Options)命令放⼤(Zoom in)或缩⼩(Zoom out)取景(Pan)和缩放(Using Pan and Zoom)。

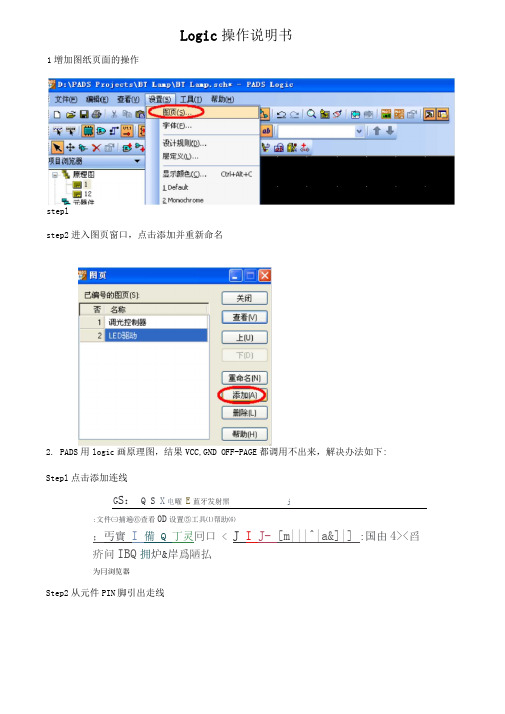

Logic操作说明书1增加图纸页面的操作steplstep2进入图页窗口,点击添加并重新命名2. PADS用logic画原理图,结果VCC,GND OFF-PAGE都调用不出来,解决办法如下:Stepl点击添加连线G S: Q S X电曜E蓝牙发射黑j:文件㈢捕遍⑥查看0D设置⑤工具⑴帮助⑹;丐實I 備 Q 丁灵冋口< J I J- [m|||^|a&]|] :国由4><舀疥问IBQ拥炉&岸爲陋払为冃浏览器Step2从元件PIN脚引出走线29 20U3 ATMEGA328-AU PCB(F;ESET)PB6(XTAL1)PB7{XTAL2)AF1EFStep3VCC1VCC2AVCCPDD(RXD)PD 1(7X0)PD2(INT0)Fun.^/IlK l"TiY4FTa303?32F亀度页间连接待接地电源二)结束显于PG名称取消<Bflck5pace>Alt-i-<5pece>Citrl+<5pace>5hift-l-<5pace>U3 ATMEGA32B-AU29PCG(RESET)PB6(XTAL1)8PB7(XTAL2)AR.EFVCC1VCC2AVCCPDO(RXD)PD1CTXD)PD2(INT0)出现如下图3)删除电气连线方法必须右键选择选择连线1830 31 32 6HE4) 元件和封装关联起来的设置5) 删除元件的方法至社辿说鱼③工理啦T )lilial:^4(& 1 WI ■處J50Ll.^ s ^:\: .J F 苓弋r k l -s -TQFP*Free : aii&' 1 吓「託二日2K3T-32I 妃丫韵怕I社遏申辽|U丁6右 #1 I牛 QATK :A129-Ar矿亓:件的否件伎耳旨归 屉性D玛冲恂1?L 41E営JW 裁tri_ 區用oJ]Z1'1-7呕戸具育33 單 用弭醫啲雌(S )对朿袖方戶m■:未少配屈6)PADS^拉线怎么隐藏在DISPLAY COLOR里在connect的颜色还一下,估计预拉线是背景色所以看不见就消失了,如果是将其更换为与背景色不一样的颜色7)默认需要将语言更改为如下常規□徵严保持视旳摄小显示宽度俏):20样式⑸:村字y □斜交(D)栅格(G)设计(D): 血0 标签和文本0L):10显示删格(P) :J 000 叼捕茯至册格(S)OLE对象叼显示OLE对彖0重画时更新(U)回绘(B)文本译码CT) Vestem European v自动备份间隔◎钟)(1): (5 _____ 备份数QO: [5□在备份文件名中便用设计名称□在设计目录下创淫备份文件确定(0) Arabi c Baltic Central :Chinese : Chinese' Cyrillic Greek Hebrew Japanese Korean (Johab) Korean (Wansung)ThaiTurkish ---- ----EuropeanSimpli fi edTraditional。

PADS2007系列教程――PADS Logic(原PowerLogic)比思电子有限公司HK +852-******** SZ 755-88859921 SH 21-51087906 BJ 10-51665105PADS Logic教程简介欢迎使用PADS Logic教程。

本教程由比思电子有限公司(KGS Technology Ltd.)编写,本公司是Mentor (以前的 Innoveda-PADS) PADS(以前的PowerPCB)产品、APLAC 的射频和微波仿真工具、DpS 的电气图CAD系统PCschematic 在中国的授权代理商。

KGS公司自1989年开始,一直致力于PADS软件产品的销售和支持。

公司提供电子产品在原理样机设计开发阶段全面的解决方案。

包括相关的CAE/CAD/CAM等EDA软件、提供PCB设计服务、PCB样板加工制造、快速PCB加工设备、PCB元器件装配。

所有技术人员都具有十年以上的PCB设计领域从业经历。

本教程描述了PADS Logic的各种功能和特点、以及使用方法。

这些功能包括:·如何在PADS Logic中使用工作区(Working Area)。

·如何在PADS Logic的元件库中定义目标库(Library)。

·如何从库中搜索有关的元件(Part)。

·如何添加连线(Connection)、总线(Bus)、使用页间连接符号(Off-Page)。

·移动(Move)、拷贝(Copy)、删除(Delete)和编辑(Edit)等操作方式(Mode)。

·在设计数据编辑时使用查询/修改(Query/Modify)命令。

·如何定义设计规则(Design Rules)。

·如何建立网表(Netlist)和SPICE格式网络表以及材料清单(BOM)报告和生成智能PDF文档。

·如何输入中英文文本和输入变量数值。

padslogic⽆模式命令PADS⽆模式命令1.PADS2007⽆模命令与快捷键表⽰坐标。

表⽰⽂体。

表⽰数字。

1.[C]显⽰平⾯的焊盘和热焊盘(Thermal)。

2.[D]显⽰当前层。

3.[DO]通孔外形显⽰切换。

4.[E]循环显⽰⾛线的末端与via(过孔)的连接⽅式。

#End no via:⾛线的末端什么也不连接。

#End via :⾛线的末端连接到via(过孔)。

#End Test point:⾛线的末端连接到⼀个作为测试眯的确via(过孔)。

5.[I]数据库完整性测试。

6.[L]改变当前层到n层。

7.[N]增加当前层的⾼亮显⽰的⽹络,表⽰当前⾼亮显⽰的⽹络。

8.[N-]逐个取消⾼亮显⽰,取消⽅式与N命令增加的⽅式反向。

9.[N]去除所有⾼亮显⽰。

10.[O]⽤边框显⽰焊盘和⾛线。

11.[PO]覆铜浇灌边框显⽰。

12.[Q]快速测量命令,可以选择是否捕捉栅格点。

13.[QL]快速测量长度,⾸先选择线段、⽹络或者管脚对。

14.[R]减少显⽰的宽度到n, 例如R50。

15.[RV]输出使⽤⽂件Reuse⽂件时,⽤于改换参数设定。

16.[SPD]显⽰分割/混合层数据,此命令控制Option中的split/mixed选项卡中mixed plane display 下⾯的⼀个参数。

17.[SPI]显⽰平⾯的Thermal(热焊盘),此命令控制Option中的split/mixed选项卡中mixed plane display下⾯的⼀个参数。

18.[SPO]显⽰分割/混合平⾯的多边形边框,此命令控制Option中的split/mixed选项卡中mixed plane display下⾯的⼀个参数。

19.[T]透明显⽰切换。

20.[UM]更改设计单位为mil。

21.[UMM]更改设计单位为MM(毫⽶)。

22.[UI]更改设计单位为英⼨。

23.[X]⽂字外形线显⽰切换。

24.[W]改变线宽到n,例如w5。

PADSLOGIC中文教程PADSLOGIC是一款功能强大的PCB设计软件,广泛应用于电子设计行业。

其用户界面友好,操作简单,功能丰富,能够满足用户对于PCB设计的各种需求。

本文将为大家介绍PADSLOGIC的基本操作和常用功能,希望能够帮助大家更好地使用这款软件。

一、PADSLOGIC的基本操作1.新建工程打开PADSLOGIC软件,点击“File”菜单中的“New”选项,选择“Project”新建一个工程。

在弹出的对话框中输入工程名称和保存路径,点击“OK”按钮确定。

2.添加元件在左侧的工具栏中选择“Place Part”工具,然后在画布上单击鼠标左键即可放置元件。

可以通过“Library”菜单选择需要的元件库,也可以使用“Search”功能查找特定元件。

3.连接元件使用“Place Wire”工具进行连接元件,单击鼠标左键从一个引脚拖动到另一个引脚即可连线。

可以使用“Change Line Width”工具更改连线的宽度。

4.设定电源和接地使用“Place Power Port”工具添加电源和接地,然后连接到元件的对应引脚。

可以在元件属性中调整电源和接地的设置。

5.设定信号线使用“Place Signal”工具添加信号线,可以在元件之间连接各种信号。

可以使用“Change Line Style”工具更改信号线的样式。

6.设定网络在PADSLOGIC中,网络是指一组连接在一起的元件和信号线,可以使用“Create Net”工具设定网络。

可以在属性选项中设置网络的名称和属性。

7.设定封装库在PADSLOGIC中,封装库是用来存储元件的封装信息的,可以使用“Place Library Reference”工具添加封装库。

可以在元件属性中选择需要的封装库。

8.保存工程在工程操作完成后,一定要及时保存工程,可以点击“File”菜单中的“Save”选项保存工程。

也可以使用“Save As”功能保存工程的副本。

决PADS 9.5中文语言下修改零件标号提示“发生严重的运行时错误”并退出的问题1、用Ultraedit打开安装目录下“\9.5PADS\SDD_HOME\Programs\chs”文件夹下的“powerpcb.mdb”文件2、查找"End ICDB Integration",不包含双引号,最终只会找一个结果,而且后面跟着一串星号。

3、把星号后面的“参考编号”修改成英文的“Ref.Des.”,保存再重新运行Pads Layout就可以了。

在此文发表的时候,听说Pads 9.5 update 1也是这两天发布了,不知道有没有修正这个问题。

pads logic off-page 新建及编辑符号2011-07-14 16:59:30| 分类:电子技术| 标签:|举报|字号大中小订阅首先tools-->part editor,file-->open弹出对话框如下:选择右边的off-page,OK。

默认情况下,你可以看到两种off-page符号:refin和refout 。

我们再添加一个输入输出的双向符号。

edit-->part type editor弹出对话框,左侧add,浏览lib,寻找合适的符号系统自带的connect lib中有一个双向箭头,我们可以直接选择它。

完成后OK退出。

可以看到多出来了一个叫CON_IO的符号。

保存退出。

即可。

需要注意的是,这个更新不能在原有之前的sheet上反映出来,需要新建sheet才能够使用。

祝你顺利!如下图所示:2、PADS中层类型简介:所有平面层中包括非特殊层(非平面层NO PLANE,通常为走线ROUTING层)和特殊层(包括CAM平面层及SPLIT分割混合层).a. No plane:通常指走线层,如Top Bottom,以及中间走线层,以正片的形式输出。

b. CAM plane:以负片的形式输出,层分割以2D线来实现,不用铺铜,通常用于电源层跟地层,且占用的数据量要小得多,但有一个缺点就是不会检查设计规则,即分配到这层的网络,就不会再检查安全间距及连接性等,因此,分割层需要自已保证无误。

PADS2007PADS LogicPowerLogicPADS LogicPADS Logic(KGS TechnologyLtd.)Mentor (Innoveda-PADS) PADS PowerPCBAPLACDpS CAD PCschematicKGS1989PADSCAE/CAD/CAM EDAPCB PCBPCB PCBPCBPADS LogicPADS Logic(Working Area)PADS Logic(Library)(Part)(Connection)(Bus)(Off-Page)(Move)(Copy)(Delete)(Edit)(Mode)/(Query/Modify)(Design Rules)(Netlist)SPICE(BOM)PDF(OLE)(Engineering Change Orders (ECO))PADS Logic(On-lineHelp)PADS LogicPADS LogicPADS LogicWindows 2000WindowsXP//Mentor Graphics SDD/PADS2007/System DesignPADS LogicPADS Logicsupport@–(GUI)–PADS(Library)–(Parts)–(Connections)–(Buses)––(Design Rules)–PDF–Add Field–PADS Logic OLE(Engineering Change Orders (ECO))–(GUI)PADS Logic PADS LogicPADSPADS Logic(Grids)( Pan)(Zoom)PADS LogicPADS Logic Windows(Menu)(Pop-up Menus)(Shortcut Keys)(Toolbars)(Toolboxes)(Pull-down)/(Menu/Command)/(File/Open)(Icons)(Toolbars)(Menu Bar)(Modeless Commands)(Modeless Commands)(Shortcut Keys)Windows Alt-F PADS Logic(Help)ModelessCommandsEsc(Pop-up Menu)(Cancel)PADS Logic56x 56(0,0)B11x 17C17x 22(Cursor)X/Y(Status Bar)1. 0,0(Status Bar)2. X/Y(Grids)PADS Logic(Grid)(Design Grid)(DisplayGrid)(Design Grid)(Parts)(Connections)(Polygons)(Paths)(Circles)(Rectangles)2 mils/(Tools/Options)(Design)(Design Grid)(Display Grid)(Design Grids)(Design Grids)/(Tools/Options)(Global)(Display Grid)(Display Grid)(Display Grid)10(Zoom)(Grid Exercise)(Tools Menu)(Options)(Modeless)(Modeless)(Design Grid)(Display Grids)1. (Display Grid)GD(Modeless)GD2.500(Enter)(Zoom in)(Zoom out)(Grid)(Grid)(Grid)(Using Pan and Zoom)G500(Enter)(Design Grid)(Grid)(Zooming in)(Zooming out)(Using Pan and Zoom)”(Modeless)(V alue)(Space)/(Setup/Preferences)(Pan)(Mouse)(Mouse)(Zoom)1./(File/Open)PADS Logic(Pop-up menu)No2.(File Open)preview.sch(Practice Zoom)(Zoom)1. (Toolbar)(Zoom)(Mouse)2. (Zoom in)3. (Zoom out)(Zoom)(Zoom)52.(Pan)(Zoom in)(Pan)(Zoom out)3.(Zoom)(Panning)(Mouse)(Mouse)(Zoom)(Pan)Tools Options(Options)Global1Display Display MinimumdisplayDisplay Grid2Automatic backups PADSInterval(Number of)Backup File3Style Samll cross,Large cross Full crossDiagonal Diagonal4Text EncodingChinese SimplifyDesign1Grids2(Parameters)Tie DotBus Angle Preserve Ref Des on pasteAllow Floating Connection3Sheet Size Sheet4Show Off-page Sheet NumberSeparators Numbers per LineTextLine Widths–PADSPADS Logic(Part Editor)(Part Type)PADS(Part Type)PADS Logic(Part Editor)(PinDecal)PADS Logic(Part Editor)CAE(CAEDecal)(Part Editor)(PartType)previewstart.schpreviewstart.sch1(Toolbar)(Open)PADS Logic CAE(CAE Decal)PADS-LayoutPCB(PCB Decal)(Pin Decal)(2D line )(Pin Decal Editor)1. /(Tools/Part Editor)(PartEditor)2(Part Editor),/(File/New)3.(Select Type of Editing Item)(PinDecal)OK(Pin Decal Editor)(Pin Decal)(Pin Decal)CAE(CAE Decal)(Pin Decal)PNAME A00D01VCCNETNAME#ETYP SWP(Pin Type)(Gate SwapV alues)4.G20(Design Grid)205. (Status Bar)X Y6.7. X160Y0 ((Status Bar))8.(Circle)9.S 180 010.(Design Grid) (20 mils)11. (Move Mode)(Pin Decal)1./(File/Save As)(Save CAE Decal toLibrary)2. \libraries\preview3. (Name of Item)pinnot New_Pin4. OKPADS Logic(Pin Decal)PINNOT(Pin Decal)(Pin Decal)(Pin Decal)(Part Editor)/(File/Exit Part Editor)CAE(CAE Decal)CAE(CAE Decal)(2D Line)CAE(CAE Decal Wizard)87C256(Part Type)CAD(CAE Decal Editor)1. /(Tools/Part Editor)PADS Logic(Part Editor)2(Part Editor)/(File/New)3CAD(CAE Decal)OKCAD(CAE Decal Editor)CAE(CAE Decal)CAE(Decal)CAE(CAE Decal)CAE(CAEDecal)REF(Reference Designation)PART_TYPE(Part Type)(740474LS74)Free Label 1(Part Type)Free Label 2(Part Type)CAE CAE(CAE Decals)1. (Toolbar)Decal Editing4WizardHorizontal200,V ertical200Pin Spacing Horizontal100,V ertical100Box Parameters2002005PIN(Pin Decal)Left pins10Right pins10,Upper pins0Lower pins0PADS Logic6OK CAD(CAE Decal)CAE(CAE Decal)(LogicSymbols)(Pin Symbols)(Terminal)((Pin Decal)X)CAE(CAE Decal)(On-line Help)(Terminal)(Pin Symbols)2.(Pins)PIN(Pin Decal)OK3.X(X Mirror)X4.(Step)(Repeat)(Terminals)PADS Logic(Step and Repeat)1.(Step and Repeat)2.(Direction)(Down)7(Distance)100(Preview)3.OK(Step and Repeat)4.(Add Terminal)(Terminals)CAE(CAE Decal)15311.(Change Pin Decal)(#16)Yes#16CAE(CAE Decal)CAE(CAE Decal)1. /(File/Save As)(Save CAE Decal toLibrary)2. Libraries\preview3. (File Name)87C256(New_Decal)4. OKPADS Logic CAE(CAE Decal)87C256CAE(CAE Decal)CAE(CAE Decal)87C256(Part Type)CAE(CAE Decal)/(File/Exit Part Editor)CAE Decal ()CAE Decal 7404CAE Decal7404CAE Decal1.4.Modify 2D LineItem)2. (Part Type)3. OK(Select type of editing item)4.(Toolbar)(Edit Electrical)7.(…)\Libraries\preview CAE(CAE Decal) 8. \Libraries\preview9. (Filter)87*(Apply)87C256(Decal)(Unassigned Decals)10.(Unassigned Decals)87C256(Decal)(Assign)87C256(Decal)(Part Type)A(gate A)(Decal)(Assigned Decals)11. OKCAE (CAE Decal)(On-line Help)PCBPCB (PCB Decal)CAE (CAE Decal)(Pin Numbers)(Names)1.PCB (PCB Decals)2. \Librares\common3. 26(Pin Count)26(Apply)4.SOJ26S(Decal)(Assign)(Decal)(Power)(Ground)(PADS)1. (Pins)2. Pin Group ()Number ()143. (Unused Pins)Signal Pin()4. Name()GND5. (Pin)26Signal Pin, Names ()VCC(Attributes)(Part Type Attributes)1. (Attributes)(Add)2. (Attributes)PART DESC Tab(Attribute V alue)32K X 8 BIT CMOS EPROM/LATCH3. (Add)(Attributes)(V alues)(Attributes) (V alues)$: (leave blank)PART NUMBER: 87C256MFG #1: SIGNETICSMFG #2: (leave blank)PADS Logic(On-line Help)4. OK(Part Type)(Electrical Parameters)(Gates)(Pin Numbers)(Pin Names)(Part Type)CAE(Pin Numbers)(Pin Names)(Pin Numbers)(Pin Names)1.(Edit Gate Decal)3. (Set Pin Name)5. (Output Pins)(PinName)Q1Q76. (Set Pin Name)ALE/ \CE(Pin Name)2. OK3. A14(Input Pin)4. (Set Pin Name)VPP8. OK9.(Input Pin)(Pin Name)(Pin Numbers)1. (Set Pin Number)(Part Type)1. /(File/Return to Part)(Gate)2.Yes(Gate)(Part Editor)3./(File/Save As)(Save Part and GateDecals as)4. \Libraries\preview5. (File Name)87C2566. OKPADS Logic(Part Type)87C256(PartType)(Part Type)87C256(Part Type)/(File/Exit Part Editor)(Part Editor)(Schematic Editor)PADS Logic(Part Type)–(Parts)previewstart1. (Toolbar)(Open)b. X6200Y8200c. “5”2.a. (Design)PADS LogicU8U9(Reference Designator)5. AM100415(Cancel)ESC(Part)AM1004151. (Toolbar)(Delete)(Delete)1./(File/Save As)(File Save As)2. (File Name)previewpart.sch3. (Save)PADS Logic previewpart.sch– (Connections)(Power)(Ground)Floating1. (Toolbar)(Open)(Part)(U3)(Zoomed in)1.(Design Toolbox)(Add Connection)2.U31U5B 6U315(Move)3. 154. U1U3PADS Logic(highlights)5. Esc(Add Connection)(Move)(Delete)U3U315“(Adding Connections to Power and Ground)”(Power)(Power)(Ground)(Ground)(Power)(Power)U3U3U315+12V1. U32.(Design)(Add Connection)(Alternate)Alt+Tab+12V(Status Bar)6.(Ground)(Power)R5R21. S R5R52. (Add Connection)R523.(Ground)R54. S R2R25. (Add Connection)R226.PG(Display PG Name)7. R2.28.(Alternate)Ctrl+Tab+5V9. R2+5V(Off-page)(netlist)PADS Logic(Off-page)1. (Design)(Add Connection)6. U7(Off-page)(Add Connection)7.24MHZ OKFloatingPADS2005PADS20051/(Tools/Options)DesignParameters Allow Floating Connection2PartPADS2007PADS Logicpreviewpart U7U8CtrlU7U829U71219U8U8U8U71. /(File/Save As)(File Save As)2. (File Name)previewconnect.sch3. (Save)PADS Logic previewconnect.sch–(Busses)(Busses)(Bus)(Bus)1. (Toolbar)(Open)2. (Toolbar)(Add Bus)(Bus)1. (Add Connection)(Connections)PADS Logic1.(Toolbar)(Copy Mode)–(Design Data)(Placement)(Properties)(Parts)(Parts)(Part)1. (Toolbar)(Open)2.24MHz(Off-page)/(Query/Modify Netname)3. /(Query/Modify Netname)XXXOK4. 24MHzNet 24MHZ already exists - OKto combine nets? Yes1.S R500R500(Enter)PADS Logic(Logic)(Power)2. (Zoom in)3. (Properties)9. (Reference Designator)C10OK10.(Close)(Part Properties)Swap Ref.Des(Swap pins)Pin U5-A1Pin2Pin1Pin2PinU5-A1Pin3Pin(Part)(Capacitor) C10R500(Mirror)C101. (Toolbar)(Move Mode)3. (Pop-up menu)Y(Mirror)4. C10(Capacitors)(Part)1. (Properties)。

PADS无模式命令1.PADS2007无模命令与快捷键<x.y>表示坐标。

<s>表示文体。

<n>表示数字。

1.[C]显示平面的焊盘和热焊盘(Thermal)。

2.[D]显示当前层。

3.[DO]通孔外形显示切换。

4.[E]循环显示走线的末端与via(过孔)的连接方式。

#End no via:走线的末端什么也不连接。

#End via :走线的末端连接到via(过孔)。

#End Test point:走线的末端连接到一个作为测试眯的确via(过孔)。

5.[I]数据库完整性测试。

6.[L<n>]改变当前层到n层。

7.[N<s>]增加当前层的高亮显示的网络,<s>表示当前高亮显示的网络。

8.[N-]逐个取消高亮显示,取消方式与N<s>命令增加的方式反向。

9.[N]去除所有高亮显示。

10.[O<r>]用边框显示焊盘和走线。

11.[PO]覆铜浇灌边框显示。

12.[Q]快速测量命令,可以选择是否捕捉栅格点。

13.[QL]快速测量长度,首先选择线段、网络或者管脚对。

14.[R<n>]减少显示的宽度到n, 例如R50。

15.[RV]输出使用文件Reuse文件时,用于改换参数设定。

16.[SPD]显示分割/混合层数据,此命令控制Option中的split/mixed选项卡中mixed plane display 下面的一个参数。

17.[SPI]显示平面的Thermal(热焊盘),此命令控制Option中的split/mixed选项卡中mixed plane display下面的一个参数。

18.[SPO]显示分割/混合平面的多边形边框,此命令控制Option中的split/mixed选项卡中mixed plane display下面的一个参数。

19.[T]透明显示切换。

20.[UM]更改设计单位为mil。

21.[UMM]更改设计单位为MM(毫米)。

决PADS 9.5中文语言下修改零件标号提示“发生严重的运行时错误”并退出的问题1、用Ultraedit打开安装目录下“\9.5PADS\SDD_HOME\Programs\chs”文件夹下的“powerpcb.mdb”文件2、查找"End ICDB Integration",不包含双引号,最终只会找一个结果,而且后面跟着一串星号。

3、把星号后面的“参考编号”修改成英文的“Ref.Des.”,保存再重新运行Pads Layout就可以了。

在此文发表的时候,听说Pads 9.5 update 1也是这两天发布了,不知道有没有修正这个问题。

pads logic off-page 新建及编辑符号2011-07-14 16:59:30| 分类:电子技术| 标签:|举报|字号大中小订阅首先tools-->part editor,file-->open弹出对话框如下:选择右边的off-page,OK。

默认情况下,你可以看到两种off-page符号:refin和refout 。

我们再添加一个输入输出的双向符号。

edit-->part type editor弹出对话框,左侧add,浏览lib,寻找合适的符号系统自带的connect lib中有一个双向箭头,我们可以直接选择它。

完成后OK退出。

可以看到多出来了一个叫CON_IO的符号。

保存退出。

即可。

需要注意的是,这个更新不能在原有之前的sheet上反映出来,需要新建sheet才能够使用。

祝你顺利!如下图所示:2、PADS中层类型简介:所有平面层中包括非特殊层(非平面层NO PLANE,通常为走线ROUTING层)和特殊层(包括CAM平面层及SPLIT分割混合层).a. No plane:通常指走线层,如Top Bottom,以及中间走线层,以正片的形式输出。

b. CAM plane:以负片的形式输出,层分割以2D线来实现,不用铺铜,通常用于电源层跟地层,且占用的数据量要小得多,但有一个缺点就是不会检查设计规则,即分配到这层的网络,就不会再检查安全间距及连接性等,因此,分割层需要自已保证无误。

如果将电源和地设置成CAM 平面层,输出GERBER 文件时,是以负片形式输出.此时在本层的网络会自动产生花孔,不需要再通过走宽线或者铺铜来将它们连接.然后再拿到PCB板厂做时,就会把整个网络用铜片代替,而在板子设计时铺不铺铜已经是个形式而已了.当然,你要是设置成NO PLANE 则必须要铺得.步骤就是画好铺铜区域,把该区域网络设定为POWER OR GND ,然后FLOOD ALL即可!c. Split/Mixed plane:混合层,以正片的形式输出,需要铺铜,但其铺铜与No plane不同,可以选择分割块按块铺,统一操作是在tool/pour manager的plane connect页中操作,该层在进行规则校验时会检查规则。

分割混合层SPLIT 同样也是用来处理电源或GND 的,但是它是输出正片,那么分到该层的POWER & GND都必须靠铺铜来连接,铺时,系统自动分割两个部分而且没有任何连接关系,也可以在本层再走线.建议不要这样设置.使用Mixed plane做电源层或地层时,层分割过程可能会出层某一块铜皮被另一块铜皮全包围,或有重叠的情况,进行pour 操作后,经常出现被覆盖的现象,在这种情况下,需要设置分割块的优先级别(flood priority),级别越低,越优先铺铜,即重叠部分划归优先级别低的.3、Hatch和Flood的区别解释如下:我们知道PowerPCB里的覆铜区域的边界是由弧线和折线等构成的,这个边界描述了需要覆铜区域的范围。

Flood是根据现有的设计规则进行覆铜,软件会根据设计规则重新计算并确定覆铜区域的边界。

Hatch呢,就是简单地在已有覆铜区域边界的覆铜区域内覆铜,或简单理解为”覆铜区域内的覆铜可视化“,经常新打开一个曾经覆铜的板子需要做这个操作。

形象一点,Flood字面是洪水的意思,水流冲过,一切都要更新了,所有的边界也要重新界定了,当然,自然的洪水要遵循自然规律,覆铜的flood则会遵循设计规则。

Hatch,字面意思是孵化的意思,孵化是在一个壳里孵化长大,这个“壳”就是覆铜区域的边界了,铜在里面…孵化长大直到填满。

有时候,我们会做一个比较大的设计,这是文件会很大,而且,操作时间也很长,这样如果有一点误操作,很可能就把powerpcb的数据库破坏,经常会强制关闭设计或造成无法同步,甚至不能输出*.asc文件。

因此,在你的一个设计时间比较长时,最好,先导出一个*.asc文件,再把这个文件导入生成新的*.pcb这样数据库能整理一次,能避免上面提到的错误发生。

改板时,也推荐大家,先这样做一遍,能省掉你以后不少麻烦!4、PowerPCB gerber out时*.rep,*.pho,*.drl,*.lst各表示什么意思,在制板时哪些文件是制板商所需要的?*.pho GERBER数据文件*.rep D码文件(线,焊盘的尺寸,必不可少的)*.drl 钻孔文件*.lst 各种钻孔的坐标以上文件都是制板商所需要的。

5、PowerPCB的25层有何用处?POWERPCB的25层存储为电源、地的信息。

如果做多层板,设置为CAM PLANE就需要25层的内容。

设置焊盘时25层要比其它层大20MIL,如果为定位孔,要再大些。

6、PADS Router中移动元器件后已布好的线消失问题的解决办法:打开tools->options->Placement选项卡,在Reroute traces框中选择during move 或after move,不要选no rerouting 即可。

7、器件封装中过孔或焊盘的绘制问题:有些插件元件封装需要过孔(pad stack),过孔的设置除了默认的三层:mounted side、inner layers、opposite side需要设置焊盘大小和孔径外,还需要添加第四层:layer 25。

打开过孔的pad stack,如下图所示:点击Add添加新的层,在层选择中选择layer_25添加,第25层的设置为:焊盘大小比其他层大20mil或0.6mm,孔径一样。

如果过孔没有添加第25层的属性,则在PCB中该孔会与接地平面的铜箔相连,孔周围没有隔离圈。

第25层的数据就是关于地平面的电气属性,一般在地平面设置为CAM Plane 时使用。

8、BGA引脚批量打孔的方法:BGA 引脚有几百个,若是挨个打孔,不仅费时费力,而且不容易对齐,孔与焊盘之间的间距也不好控制。

可以使用自动布线器PADS Router的扇出功能自动打孔。

选定BGA器件,右键点击属性,如下图所示:在VIA Biasing 中选择合适的孔,在routing中选择合适的走线宽度,并合理设置clearance,然后就可以进行批量打孔了。

设置好规则后选择BGA器件,右键中点击fanout选项打孔,然后再进行微调就可以了。

9、元器件布局的时候栅格一般设置为20mil。

10、使系统互连噪声最小的原则:1. 要求严格的信号网路要布设在同一个信号层,并保持导线尽可能短,应避免改变信号网路的布设层,层间信号的传递会引起反射并降低线路阻抗。

2. 是相邻信号层的路径彼此成直角(相互垂直)。

3. 各信号层间通过地线层或电源层彼此隔离。

4. 平行信号线的布设应该尽量拉开距离。

5. 差分导线对的长度必须一致。

6. 尽量减少通孔。

7. 尽量使用同一走线宽度进行走线。

8. 尽可能使用最宽的路线以减少直流电阻。

12、去耦电容的放置问题:去耦电容的电源端与IC的电源插针享用同一个焊盘,使得IC和去耦电容之间形成的间隔距离最小。

OV平面应该设置在于安装元器件的PCB表面层直接相邻的层次上,并且所有的元器件都应该使用最短、最宽的线条与他相连接,即使用直接最近接地。

如果存在某种原因去耦电容必须移至原理IC电源插针而无法享用同一个焊盘的场合,最好是在IC和去耦电容之间采用小面积的铜质面(一个小面积的电源平面)来代替线条,以使去耦电容的互连电感最小化。

并联去耦电容的布局问题:使用若干个并联去耦电容是降低他们ESL影响的一种方法。

但是用这种做法来减少ESL 影响时,只有在去耦电容的互连接电感远小于单个去耦电容的ESL条件下才会有明显的整体效果。

这是由于让多余一个的去耦电容来与IC的一个电源插针享用同一个焊盘是有困难的。

所以经常采用的是一个小面积的电源平面的布局方式。

一般情况下,当将N个去耦电容并联使用时,它们所形成的总阻抗就会降低。

虽然理论上将他们的并联阻抗为1/N乘以单个去耦电容的阻抗,但在实际应用中,降低的程度则还取决于他们相互之间布局的位置,只有在布局合理的条件下,可获得的阻抗才会为单个去耦电容阻抗的1/10.设计多个去耦电容布局的最为显见的方式就是把它们一个一个的排成一排,而且把所有的0V连接都设计在同一端。

但是这样的布局不会产生所要求的阻抗降低效果。

这不仅是因为他们的电流流动是处于同一个流向,而且器件之间的如此靠近又会形成相当大的互电感。

因此这样的布局所形成的阻抗降低的整体效果不会达到1/10的水平。

所以在采用这种布局时,通常都会把器件的间距拉开一点,以尽量降低他们之间的互感,并以此达到将整体阻抗降低至最低。

然而,假如器件能被设置的使得由流经它们的电流所形成的磁通相互抵消的话,那么器件也就可以被安置的相互紧靠在一起。

如下图的放置方式:(戴尔专利:6337798)采用这种放置方式的一个例子就是BGA封装的CPU的有些电源供电引脚上需要接好几个去耦电容的情况。

下图的放置方式是起不到并联去耦的效果:有关去耦电容放置的其他情况如下所示:在PCB中必须注意。

13、20H规则:20H规则的采用是指要确保电源平面的边缘要比0V平面边缘至少缩入相当于两个平面间层距的20倍。

这个规则经常被要求用来作为降低来自0V/电源平面结构的侧边射击发射技术。

但是,20H规则仅仅在某些特定条件下才会提供明显的效果。

这些特定的条件包括有:(1)、在电源总线中电流波动的上升/下降时间要小于1ns.(2)、电源平面要处于PCB的内部层面上,并且与它相邻的上下两个层面都为0V平面。

这两个0V平面向外延伸的距离至少要相当于它们各自与电源平面间层距的20倍。

(3)、在所关心的任何频率上,电源总线结构不会产生谐振。

(4)、PCB的总层数至少为8层或更多。

14、有关地平面的阻焊盘的问题:在地平面上,任何缝隙和孔洞的存在对于EMC来讲都是有害的,因为它们的存在必然会增加阻抗和阻止RF返回电流的自由流通。

由于在每个通孔周围要求有净空孔(阻焊盘)存在,在改善EMC性能,而又不会严重影响产品产量的前提下,阻焊盘应该设计的尽可能的小。