数字逻辑与数字系统练习题

- 格式:docx

- 大小:172.75 KB

- 文档页数:18

()1、数字电路又称为开关电路、逻辑电路。

答案:正确()2、二极管、三极管、场效应管是常用的开关元件。

答案:正确()3、最基本的逻辑关系是:与、或、非。

答案:正确()4、高电平用0表示,低电平用1表示,称为正逻辑。

答案:错误()5、TTL型门电路比CMS型门电路开关速度快。

答案:正确()6、逻辑表达式是逻辑函数常用的表示方法。

答案:正确()7、用真值表表示逻辑函数,缺乏直观性。

答案:错误()8、逻辑图是最接近实际的电路图。

答案:正确()9、由真值表得到的逻辑函数一般都要经过化简。

答案:正确()10、组合电路的特点是:任意时刻的输出与电路的原状态有关。

答案:错误()11、1+A=1答案:正确()12、AB+A=A()13、将实际问题转换成逻辑问题第一步是要先写出逻辑函数表达式。

答案:错误14、异或函数与同或函数在逻辑上互为反函数。

(对)每个最小项都是各变量相“与”构成的,即n个变量的最小项含有n个因子。

(对)15、因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立。

(错)16、逻辑函数F=A B+A B+B C+B C已是最简与或表达式。

(错)17、利用约束项化简时,将全部约束项都画入卡诺图,可得到函数的最简形式。

(错)18、卡诺图中为1的方格均表示逻辑函数的一个最小项。

(对)19、在逻辑运算中,“与”逻辑的符号级别最高。

(错)20、标准与或式和最简与或式的概念相同。

(对)21、数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

(对)22、格雷码具有任何相邻码只有一位码元不同的特性。

(对)23、所有的集成逻辑门,其输入端子均为两个或两个以上。

(错)24、根据逻辑功能可知,异或门的反是同或门。

(对)25、逻辑门电路是数字逻辑电路中的最基本单元。

(对)26、TTL和CMOS两种集成电路与非门,其闲置输入端都可以悬空处理。

(错)27、74LS系列产品是TTL集成电路的主流,应用最为广泛。

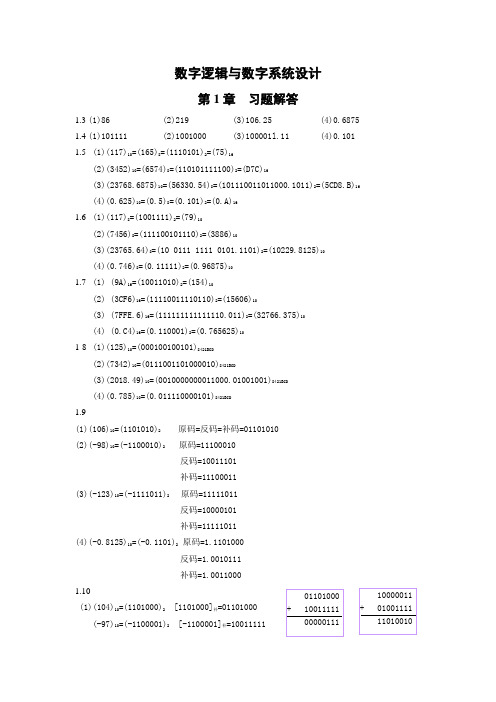

/cugFirst/fig_logic/exercise/xiti/T3%EF%BC%8D3.htm1 由或非门构成的触发器电路如图3.25所示,请写出触发器输出Q的次态方程。

图中已给出输入信号a、b、c的波形。

设触发器的初始状态为1,画出输出口的波形。

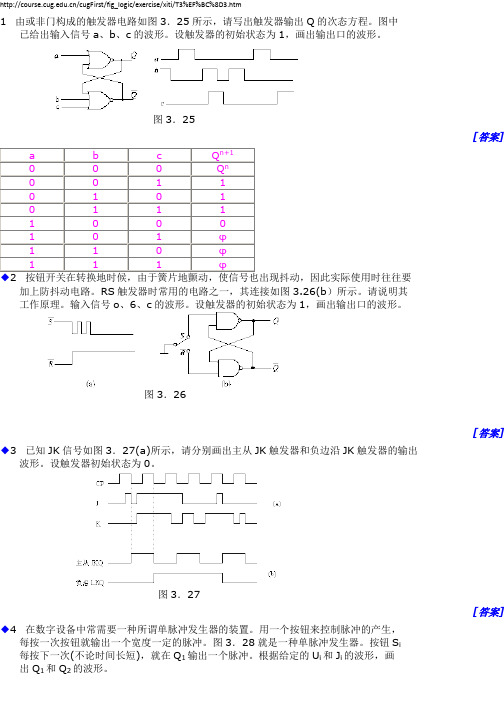

图3.25[答案] a b c Q n+1000Q n0011010101111000101φ110φ111φ◆2 按钮开关在转换地时候,由于簧片地颤动,使信号也出现抖动,因此实际使用时往往要加上防抖动电路。

RS触发器时常用的电路之一,其连接如图3.26(b)所示。

请说明其工作原理。

输入信号o、6、c的波形。

设触发器的初始状态为1,画出输出口的波形。

图3.26[答案]◆3 已知JK信号如图3.27(a)所示,请分别画出主从JK触发器和负边沿JK触发器的输出波形。

设触发器初始状态为0。

图3.27[答案]◆4 在数字设备中常需要一种所谓单脉冲发生器的装置。

用一个按钮来控制脉冲的产生,每按一次按钮就输出一个宽度一定的脉冲。

图3.28就是一种单脉冲发生器。

按钮S i 每按下一次(不论时间长短),就在Q1输出一个脉冲。

根据给定的U i和J i的波形,画出Q1和Q2的波形。

图3.28[答案]◆5 写出图3.29中各个触发器的次态方程,并按照所给的CP信号,画出各个触发器的输出波形(设初始态为0)。

图3.29[答案]◆6 带有与或输入门电路的JK触发器的逻辑示意如图3.30所示,图中标明了外加输入信号的连接。

请写出图中触发器的次态方程,并根据所给的输入波形,画出输出波形。

图3.30[答案]◆7 图3.31(a)是一种两拍工作寄存器的逻辑图,即每次在存人数据之前必须先加人置0 信号,然后“接收”信号有效,数据存人寄存器。

(1)若不按两拍工作方式来工作,即置0信号始终无效,则当输人数据为D2D1D0=000--001---010时,输出数据Q2Q1Q0将如何变化?(2)为使电路正常工作,置0信号和接收信号应如何配合?画出这两种信号的正确时间关系。

2021—2022学年春季学期

课程名称:数字逻辑与数字系统

一.(10分)逻辑电路如图1-1所示。

试回答如下问题: (1) 在图1-1中的74161实现的是几进制计数器? (2) 已知输入波形CP ,Q 2Q 1Q 0初始值为000,

在图1-2中画出Q 2、Q 1、Q 0、以及输出F 波形; (3) 说明图1-1逻辑电路的功能?

F

图1-1

图1-2

二.(8分)逻辑电路的状态转换图如图2所示。

试回答如下问题: (1) 说明该电路的功能;

(2) 用74160和必要的逻辑门实现该电路。

图2

三.(15分)逻辑电路的状态转换图如图3所示。

试回答如下问题:

(1)说明该电路的功能;

(2)用3个上升沿有效的D触发器和必要的逻辑门实现该电路,要求写出状态方

程、输出方程和驱动方程,判断能否自启动。

图3

四.(15分)时序逻辑电路如图4所示,写出驱动方程、输出方程,状态方程,列状态转换表,画出状态转换图,说明电路功能。

X

图4

五.(13分)逻辑电路的状态转换图如图5-1所示,其中X为输入,Z为输出,Q2Q1Q0为状态。

试回答如下问题:

(1)说明该电路的功能;

(2)根据图5-1状态转换图,以及给出的Verilog源程序,填写图5-2中a1~a10、

b1~b2、c1~c3的Verilog源程序;

(3)已知输入波形,如图5-3所示,画出Q2、Q1、Q0、Z波形。

图5-1

图5-2

图5-3

六.(9分)时序逻辑电路如图6所示,X为输入,F为输出;写出输出方程,状态方程,列状态转换表,画出状态转换图,说明逻辑电路功能。

图6。

山东工商学院2020学年第一学期数字逻辑与数字系统课程试题 A卷(考试时间:120分钟,满分100分)特别提醒:1、所有答案均须填写在960数字加起来827参考答案207上,写在试题纸上无效。

2、每份答卷上均须准确填写函授站、专业、年级、学号、姓名、课程名称。

一单选题 (共10题,总分值20分 )1. 一个8选一数据选择器的数据输入端有个。

(2 分)A. 1B. 2C. 3D. 4E. 82. 8位移位寄存器,串行输入时经__________个脉冲后,8位数码全部移入寄存器中。

(2 分)A. 1B. 2C. 4D. 83. 将一个时间上连续变化的模拟量转换为时间上断续(离散)的模拟量的过程称为_________。

(2 分)A. 采样B. 量化C. 保持D. 编码4. 若RAM的地址码有8位,行、列地址译码器的输入端都为4个,则它们的输出线(即字线+位线)共有________________条。

(2 分)A. 8B. 16C. 32D. 2565. 将幅值上、时间上离散的阶梯电平统一归并到最邻近的指定电平的过程称为_________。

(2 分)A. 采样B. 量化C. 保持D. 编码6. 在下列逻辑电路中,不是组合逻辑电路的有。

(2 分)A. 译码器B. 编码器C. 全加器D. 寄存器7. 同步计数器和异步计数器比较,同步计数器的显著优点是__________ 。

(2 分)A. 工作速度高B. 触发器利用率高C. 电路简单D. 不受时钟CP控制。

8. 某移位寄存器的时钟脉冲频率为100KHZ,欲将存放在该寄存器中的数左移8位,完成该操作需要__________ 时间。

(2 分)A. 10μSB. 80μSC. 100μSD. 800ms9. 一个16选1的数据选择器,其地址输入(选择控制输入)端有个。

(2 分)A. 1B. 2C. 4D. 1610. 一个无符号8位数字量输入的DAC,其分辨率为_________位。

北京邮电大学2008——2009学年第一学期《数字逻辑与数字系统》期末考试试题(A )考试注意事项一、学生参加考试须带学生证或学院证明,未带者不准进入考场。

学生必须按照监考教师指定座位就坐。

二、书本、参考资料、书包等物品一律放到考场指定位置。

三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有考场违纪或作弊行为者,按相应规定严肃处理。

四、学生必须将答题内容做在试题答卷上,做在草稿纸上一律无效。

五、学生的姓名、班级、学号、班内序号等信息由教材中心统一印制。

考试 课程 数字逻辑与数字系统 考试时间 2009年1月13日 题号 一 二 三 四 五 六 七 八 总分满分 10 20 10 10 10 12 14 14 得分 阅卷 教师一、选择题(每小题1分,共10分。

)1. )D C B (B )B A (A F ++++==( )A .B B . A+BC . 1D .AB2.同步时序电路和异步时序电路比较,其差异在于后者( ) A . 没有稳定状态 B . 没有统一的时钟脉冲控制 C . 输入数据是异步的 D . 输出数据是异步的 3.(10000011)8421BCD 的二进制码为( )。

A .( 10000011)2B .(10100100)2C . (1010011)2D . (11001011)24. 74LS85为四位二进制数据比较器。

如果只进行4位数据比较,那么三个级联输入端a<b 、a>b 、a=b 应为( )。

A . a<b 接地,a>b 接地,a=b 接地B . a<b 接高电平,a>b 接高电平,a=b 接高电平C . a<b 接高电平,a>b 接高电平,a=b 接地5. N 个触发器可以构成能寄存( )位二进制数码的寄存器。

A. NB. 2NC. 2ND. N 26.时序电路中对于自启动能力的描述是( )。

A . 无效状态自动进入有效循环,称为具有自启动能力。

数字逻辑与数字系统智慧树知到课后章节答案2023年下天津大学天津大学第一章测试1.十进制数(119)10转换为八进制数是答案:1672.十六进制数(1C4)16转换成十进制数是答案:4523.n个变量可以构成()个最大项或最小项答案:4.负二进制数的补码等于答案:反码加15.已知输入A、B和输出Y的波形如图所示,能实现此波形的门电路是()答案:同或门6.补码由原码按位取反加1答案:错7.增加位宽的方法有零扩展和符号扩展两种答案:对8.相同功能的逻辑门中扇入数越多,逻辑门越复杂答案:对9.两输入的逻辑门包括答案:或门;异或门;与门10.关于二进制的相关说法正确的是答案:零扩展的负数会变化;用补码实现原码的减法;原码不能计算负数加法第二章测试1.下列逻辑等式中不成立的是答案:2.布尔代数的与或非,运算优先级是 ( )答案:非>与>或3.关于无关项X,说法错误的是()答案:所有无关项X一定出现在最简表达式的圈中4.布尔代数就是二值数学运算()答案:错5.组合逻辑电路是无记忆的 ( )答案:对6.卡诺图的编码采用格雷码 ( )答案:对7.译码器具有N个输入和2N个输出,且输出具有独热性( )答案:对8.关于组合逻辑电路说法正确的是()答案:组合逻辑电路的输出仅仅取决于当前输入;大的组合逻辑电路可以由小的组合逻辑电路构成;组合逻辑电路是无记忆的;组合逻辑电路不包含回路9.下列表达式成立的是()答案:AB = BA;B(B+C) = B;A+B=B+A10.卡诺图的画圈原则中,说法正确的是( )答案:质主蕴含项一定出现在最简解中;最简表达式一定含有最少的圆圈数目;质主蕴含项一定是能圈的最大圈;最简表达式中有时都是非质主蕴含项第三章测试1.64位行波进位加法器的延迟为()。

假设全加器的延迟是450ps。

答案:28.8ns2.在SystemVerilog模块中定义一个端口必须指明哪些要素()。

答案:方向;名字3.logic类型的变量会被综合为()电路。

第一部分:1.在二进制系统中,下列哪种运算符表示逻辑与操作?A) amp;B) |C) ^D) ~解析:正确答案是 A。

在二进制系统中,amp; 表示逻辑与操作,它仅在两个位都为1时返回1。

2.在数字逻辑中,Karnaugh 地图通常用于简化哪种类型的逻辑表达式?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是B。

Karnaugh 地图通常用于简化或门的逻辑表达式,以减少门电路的复杂性。

3.一个全加器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 C。

一个全加器有三个输入:两个加数位和一个进位位。

4.下列哪种逻辑门可以实现 NOT 操作?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 D。

与非门可以实现 NOT 操作,当且仅当输入为0时输出为1,输入为1时输出为0。

5.在数字逻辑中,Mux 是指什么?A) 多路复用器B) 解码器C) 编码器D) 多路分配器解析:正确答案是 A。

Mux 是指多路复用器,它可以选择输入中的一个,并将其发送到输出。

6.在二进制加法中,下列哪个条件表示进位?A) 0 + 0B) 0 + 1C) 1 + 0D) 1 + 1解析:正确答案是 D。

在二进制加法中,当两个位都为1时,会产生进位。

7.在数字逻辑中,一个 JK 触发器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 B。

一个 JK 触发器有两个输入:J 和 K。

8.下列哪种逻辑门具有两个输入,且输出为两个输入的逻辑与?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 A。

与门具有两个输入,只有当两个输入都为1时,输出才为1。

9.在数字逻辑中,下列哪种元件可用于存储单个位?A) 寄存器B) 计数器C) 锁存器D) 可编程逻辑门阵列解析:正确答案是 C。

锁存器可用于存储单个位,它可以保持输入信号的状态。

10.一个带有三个输入的逻辑门,每个输入可以是0或1,一共有多少种可能的输入组合?A) 3B) 6C) 8D) 12解析:正确答案是 C。

数字逻辑与数字系统模拟试题2一、填空题(每空一分)1、位置计数法三个要素是、和。

2、数字信号的特点是在上和上都是断续变化的,其高电平和低电平常用和来表示。

3、( 35.4)8 =()2 =( )10=( )164、单稳态触发器特点之一是:有一个和一个。

5、描述脉冲波形的主要参数有、、、、、、。

6、TTL OC门(集电极开路门)的输出端可以直接相连,实现。

二、判断题(正确打√,错误的打×;每题2分)1、十进制数具有两个特点:计数基数为10,逢“十”进位。

2、与逻辑关系是指只有当决定一件事情的全部条件具备之后,结果才能发生。

3、实现两个二进制数相加的电路称为半加。

4、单稳态触发器一般用于定时、整形和产生方波。

5、将模拟量转换为数字量的过程称为数/模转换。

三、选择题(在给定的四个答案中选择一个正确答案,每题2分)1、在何种输入情况下,“与非”运算的结果是逻辑0。

A.全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是12、以下电路中常用于总线应用的有 A 。

A.三态门B.O C门C.漏极开路门D.C M O S与非门3、N个触发器可以构成二进制寄存器的位数为。

A.N-1位B.N位C.N+1位D.2N位4、多谐振荡器可产生。

A.正弦波B.矩形脉冲C.三角波D.锯齿波5、石英晶体多谐振荡器的突出优点是。

A.速度高B.电路简单C.振荡频率稳定D.输出波形边沿陡峭6、以下各电路中,可以产生延时的电路是。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.石英晶体多谐振荡器7、若在编码器中有50个编码对象,则要求输出二进制代码位数至少应为 位。

A.5 B.6 C.10 D.508、一个16选一的数据选择器,其地址输入端有 个。

A.1B.2C.4D.169、一个16选一的数据选择器,其数据输入端有 个。

A.1B.2C.4D.1610、用RAM2114(1024×4位)构成4096×8位RAM ,需A 、4片;B 、8片;C 、24片;D 、12片四、按要求解答下列问题(每题10分)1、试用公式化简法化简逻辑函数为最简与或表达式。

1.一位十六进制数可以用 C 位二进制数来表示。

2.十进制数25用8421BCD 码表示为 B 。

3. 以下表达式中符合逻辑运算法则的是 D 。

A . 1B . 2C . 4D . 16 A .10 101 B .0010 0101 C .100101 D .10101 A .C ·C =C 2 B .1+1=10 C .0<1 D .A +1=14. 当逻辑函数有n 个变量时,共有 D 个变量取值组合? 5.A+BC= C 。

6.在何种输入情况下,“与非”运算的结果是逻辑0。

DA. nB. 2nC. n 2D. 2n A .A +B B.A +C C.(A +B )(A +C ) D.B +C A .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是17. 以下电路中可以实现“线与”功能的有 C 。

8.以下电路中常用于总线应用的有 A 。

A .与非门B .三态输出门C .集电极开路门D . C M O S 与非门 A .T S L 门 B .O C 门 C . 漏极开路门D .C M O S 与非门9.若在编码器中有50个编码对象,则要求输出二进制代码位数为 B 位。

10.一个16选一的数据选择器,其地址输入(选择控制输入)端有 C 个。

A .5B .6C .10D .50 A .1 B .2 C .4 D .1611.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = A 。

A .3X A A X A A X A A X A A 01201101001+++B .001X A AC .101X A AD .3X A A 0112.一个8选一数据选择器的数据输入端有 E 个。

A .1B .2C .3D .4E .813.在下列逻辑电路中,不是组合逻辑电路的有 D 。

A .译码器B .编码器C .全加器D .寄存器14.八路数据分配器,其地址输入端有 c 个。

由或非门构成的触发器电路如图3.25所示,请写出触发器输出Q的次态方程。

图中已给出输入信号a、b、c的波形。

设触发器的初始状态为1,画出输出口的波形。

图3.25[答案]a b c Q n+1000Q n0011010101111000101φ110φ111φ◆2 按钮开关在转换地时候,由于簧片地颤动,使信号也出现抖动,因此实际使用时往往要加上防抖动电路。

RS触发器时常用的电路之一,其连接如图(b)所示。

请说明其工作原理。

输入信号o、6、c的波形。

设触发器的初始状态为1,画出输出口的波形。

图3.26[答案]◆3 已知JK信号如图3.27(a)所示,请分别画出主从JK触发器和负边沿JK触发器的输出波形。

设触发器初始状态为0。

图3.27[答案]◆4 在数字设备中常需要一种所谓单脉冲发生器的装置。

用一个按钮来控制脉冲的产生,每按一次按钮就输出一个宽度一定的脉冲。

图3.28就是一种单脉冲发生器。

按钮S i每按下一次(不论时间长短),就在Q1输出一个脉冲。

根据给定的U i和J i的波形,画出Q1和Q2的波形。

图3.28[答案]◆5 写出图3.29中各个触发器的次态方程,并按照所给的CP信号,画出各个触发器的输出波形(设初始态为0)。

图3.29[答案]◆6 带有与或输入门电路的JK触发器的逻辑示意如图3.30所示,图中标明了外加输入信号的连接。

请写出图中触发器的次态方程,并根据所给的输入波形,画出输出波形。

图3.30[答案]◆7 图3.31(a)是一种两拍工作寄存器的逻辑图,即每次在存人数据之前必须先加人置0信号,然后“接收”信号有效,数据存人寄存器。

(1)若不按两拍工作方式来工作,即置0信号始终无效,则当输人数据为D2D1D0=000--001---010时,输出数据Q2Q1Q0将如何变化?(2)为使电路正常工作,置0信号和接收信号应如何配合?画出这两种信号的正确时间关系。

(3)若采用单拍方式工作,请提出一种改进方案。

图3.31[答案]图3.31◆8 分析图3.32(a)所示同步计数电路,作出状态转移表和状态图。

计数器是几进制计数器?能否自启动?并画出在时钟作用下的各触发器输出波形。

图3.32[答案]QQ3n Q2n Q1nQ2n+1Q1n+13n+1000001001011010100011111100001101010110100111110◆9 图3.33(a)所示为序列信号发生器逻辑图,作出状态转移表和状态图,确定其输出序列。

图3.33[答案]Q 3nQ2nQ1nD1000100110110110010000001010010101110◆10 图3.34(a)是一种序列信号发生器电路,它由一个计数器和一个四选一数据选择器构成。

分析计数器的工作原理,确定其模值和状态转换关系;确定在计数器输出控制下,数据选择器的输出序列。

图3.34(a)[答案] PS NSQ 3nQ2nQ1nQ3n+1Q2n+1Q1n+1000001 001010010011011100100101101000110111111000Q3n Q2n Q1n Y0000 Y=D0=Q3n001 1 Y=D1=Q3n0100 Y=D2011 1 Y=D3100 1 Y=D01010 Y=D1◆11 分析图3.35(a)所示的同步时序电路,作出状态转移表和状态图,说明这个电路能对何种输入序列进行检测。

图3.35[答案] Q1n Q2n010 000/010/00 100/111/01 100/111/01 000/011/0◆12 分析图3.36(a)所示的同步时序电路,作出状态转移表和状态图,说明它是摩尔型电路还是米里型电路。

当X=1和x=0时,电路分别完成什么功能?图3.36[答案] ______Z=Q1n Q2nQ1n QX=0X=1Z2n0 1 1 1 11 00 01110 0 1 0011 00 111◆13 分析图3.37(a)所示的同步时序电路,作出状态转移表和状态图。

当输入序列x为01011010时,画出相应的输出序列(设初始状态为000)。

图3.37[答案] Q1n+1=T1Q1n+T1Q1n=XQ1n+XQ1nQ2n+1=Q1n Q2n+Q1n Q2n_______Q3n+1=XQ1n Q2n Q3n+XQ1n Q2n Q2nZ=Q1n Q3nPS NSQ3n Q2nQ1n X=0X=10000 00 010010 110 10110 011 00100 10 111101 11 11111 1 0 0 0101011 111 111001 01 01设计题◆1 采用JK触发器设计具有自启动特性的同步五进制计数器。

已知状态转移过程的编码是110→011→100→001→100→110,请画出计数器的逻辑图。

[答案] Q2n+1=Q2n+Q0n Q2nQ1n+1=Q0n Q2n Q1n+Q1n Q2nQ0n+1=Q0n+Q2n Q1n Q0n_________J2=1, K2=Q0n ,J1=Q0n Q2n,K1=Q2n J0=1,K0= Q2nQ2n图3.38(A)图3.38(b)◆2 用D触发器设计按循环码规律工作的六进制同步计数器。

其编码为000→001→011→111→101→100→000[答案]____ D2=Q2n+1=Q1n+Q2n Q0n=Q0n(Q1n+Q2n)=Q0n Q1n Q2n D1=Q1n+1=Q2n Q1n____D0=Q0n+1=Q2n+n Q1n=Q2n Q1PS NSQ2n Q1n Q0nQ2n+1Q1n+1Q0n+1000001001011011111111101101100100000图3.39◆3 用JK触发器设计具有以下特点的计数器:(1)计数器具有两个控制输入C1和C2,C1用以控制计数器的模数,C2用以控制计数器的增减;(2)若C1=0,计数器的M=3;如果C1=1,则计数器为M=4;(3)若C1=0,则为加法计数;若C2=1,则为减法计数。

画出计数器逻辑图。

[答案]图3.40◆4 利用D触发器构成的移位寄存器和门电路,设计产生图3.41(a)所示的脉冲序列信号发生器。

图3.41[答案]_____ _____D0=Q2n Q1n+Q2n Q0n=Q2n Q1n Q2n Q0nQ 2Q1QD1010 0100 1001 0011 0110 1101◆5 利用移位寄存器构成的序列信号发生器产生序列0100101。

(1)需要几个触发器?(2)作出状态转移表。

[答案]◆6 采用D触发器及异或门构成的计数型序列信号发生器来产生0110011序列信号。

画出相应的逻辑图。

[答案]_____ _____D2=Q2n+1=Q1n Q2n=Q2n Q1n·Q0n Q1n_____ _____D1=Q1n+1=Q0n Q1n+Q2n Q0nQ1n=Q2n Q1n·Q1n Q0n·Q1n Q0n_____D0=Q0n+1=(Q2n+Q1n)Q0n=Q2n Q1n·Q0n状态转移真值表输出序列真值表Q 2nQ1nQ0nQ2n+1Q1n+1Q0n+1Q2Q1Q0F00000100000010100011010*******0111000110100101100010111010111100001101图3.42◆7 采用D触发器及同或门构成的计数型序列信号发生器来产生如图3.41(a)所示的101001序列信号。

画出相应的逻辑图。

[答案]状态转移表输出序列真值表Q 2nQ1nQ0nQ2n+1Q1n+1Q0n+1Q2Q1QF00000100010010100010010*******011100011010010110001010001011图3.43◆8 采用图3.44(a)所示的电路来构成五路脉冲分配器,为此需要具体设计其中的译码电路。

用与门电路及741S138译码器来构成这个译码器。

(a)(b)图3.44[答案] PS NSQ 3nQ2nQ1nQ3n+1Q2n+1Q1n+1000011 001111011111010001110101111110101010100011◆9 741390异步十进制计数器除了作为二、五、十进制计数器外,可以在不加门电路的情况下构成从2—10的各种模值的计数器,而且有多种方案。

若构成模值为6,7的各种计数器时,采用复0方案,如何连接才能实现?画出相应的连接图。

[答案]图3.45(a)图3.45(b)◆10 条件同9题,采用复9方案,请画出相应的连接图。

[答案]图3.46(a)图3.46(b)◆11 异步中规模计数器741392的示意图和符号如图3.47(a)所示。

其内部有一个模2计数器和一个模6计数器(从000----101),有两个置0端,当R01=R02=1时,DCBA=0000。

(1)采用该计数器连接成M=5的计数器,画出连接图。

(2)采用该计数器连接成M=11的计数器,使用尽可能少的外接门电路,画出连接图。

图3.47[答案]图3.47◆12 74U561是一种功能较为齐全的同步计数器。

其内部是四位二进制计数器。

功能表如下所示(Q D为高位输出)。

其中丽为输出控制端,OOC是与时钟同步的进位输出。

(1)说明这个计数器的清零和预置有几种方式。

(2)若要用这个计数器来构成十进制计数器,有几种连接方式?画出连接图。

O CSLOADALOADSCLRACLRCPD C BAQ D D C Q BQ A1X X X X X X X XX高阻00111↑d c bad c ba0X011X d c bad c ba0X X01↑X X XX0 0 00X X X0X X X XX0 0 001111↑X X XX加法计数[答案](a)预置法(b)复位法图3.48◆13 图3.49是一种中规模计数器的连接方式,改变预置值,也能改变级联计数器的模值。

(1)说明图3.49所示是几进制计数器,说明理由。

(2)若要两个计数器级联后的M二55,预置值应如何确定?图3.49[答案]◆14 用一片同步计数器741S169和一片八选一数据选择器,设计一个输出序列为0的序列信号发生器,画出逻辑图。

[答案]图3.50◆15 作“101”序列信号检测器的状态表,凡收到输入序列101时,输出就为1,并规定检测的序列101不重叠,即:X=0 Z=000100001。