第二十二讲 移位寄存器和计数器

- 格式:ppt

- 大小:1.92 MB

- 文档页数:24

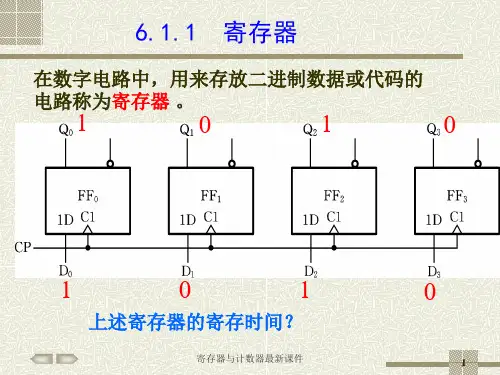

移位寄存器及算术运算应用作者:梁伟来源:《电子技术与软件工程》2018年第01期寄存器被广泛应用于数字电路和计算机中,是由具有存储功能的触发器构成的,移位寄存器在移位脉冲作用下依次逐位右移或左移,通过proteus模拟软件进行直观分析移位寄存器移位功能,移位功能可应用于CPU内部寄存器进行算术运算。

【关键词】移位寄存器 CPU算术运算1 移位寄存器寄存器被广泛应用于数字电路和计算机中,是由具有存储功能的触发器构成的。

移位寄存器具有代码寄存和移位两个功能,在移位脉冲的作用下,数码如向左移一位,则称为左移,反之称为右移。

移位寄存器具有单向移位功能的称为单向移位寄存器,即可向左移也可向右移的称为双向移位寄存器。

2 移位寄存器的算术运算如图1所示为由D触发器组成的4位串行输入-并行输出左移位寄存器,图中各触发器的CP接在一起作为移位脉冲控制端(CP脉冲同步控制),数据从最低位触发器D输入,前一触发器输出端和后一触发器D端连接。

由于CP接在一起作为脉冲控制端,当第1个CP脉冲上升沿到来时,D1触发器输出Q1是根据输入数据D改变,D2触发器Q2输出是根据Q1数据改变,D3触发器Q3输出是根据Q2数据改变,D4触发器Q4输出是根据Q3的数据改变。

单向右移寄存器移位过程如下:(1)清零,只要=0,触发器直接置0。

(2)接收数据,当=1时,第1个CP脉冲后,输入信号d4d3d2d1=1101左移1位,寄存器状态从高位到低位为Q4Q3Q2Q1=0001。

(3)第2个CP脉冲后,输入信号d4d3d2d1=1101在移2位,寄存器状态为Q4Q3Q2Q1=0011。

(4)第3个CP脉冲后,输入信号d4d3d2d1=1101在移3位,寄存器状态为Q4Q3Q2Q1=0110。

(5)第4个CP脉冲后,输入信号d4d3d2d1=1101在移4位,寄存器状态为Q4Q3Q2Q1=1101。

即在四个CP脉冲作用后,数码d4d3d2d1=1101恰好全部左移位串行输入寄存器,寄存器输出状态从高位到低位为Q4Q3Q2Q1=1101从四个触发器的输出端并行输出,完成串行输入--并行输出。

移位寄存器讲解1. 什么是移位寄存器?移位寄存器是一种基本的数字电路元件,用于将数据按位进行移位操作。

它由多个触发器(或者称为存储器元件)组成,可以在时钟的控制下,实现数据的输入、输出和移位操作。

2. 移位寄存器的分类根据移位方向和数据输入方式的不同,移位寄存器可以分为以下几种类型:2.1 串行输入的移位寄存器串行输入的移位寄存器每次只能输入一位数据,数据位依次串行输入到寄存器中。

这种类型的移位寄存器常用于串行数据通信和数据处理中。

2.2 并行输入的移位寄存器并行输入的移位寄存器可以同时输入多位数据,每位数据对应寄存器中的一个存储单元。

这种类型的移位寄存器常用于并行数据传输和存储器操作中。

2.3 串行输出的移位寄存器串行输出的移位寄存器每次只能输出一位数据,数据位依次串行输出到外部设备。

这种类型的移位寄存器常用于串行数据通信和数据处理中。

2.4 并行输出的移位寄存器并行输出的移位寄存器可以同时输出多位数据,每位数据对应寄存器中的一个存储单元。

这种类型的移位寄存器常用于并行数据传输和存储器操作中。

3. 移位寄存器的工作原理移位寄存器的工作原理可以分为两个方面:数据输入和数据移位。

3.1 数据输入对于串行输入的移位寄存器,数据从一个输入端口依次输入到寄存器中的各个存储单元。

每当时钟信号到来时,数据在存储单元之间进行移位操作,新的数据通过输入端口进入寄存器。

对于并行输入的移位寄存器,数据同时从多个输入端口输入到寄存器中的各个存储单元。

时钟信号到来时,数据保持不变,不进行移位操作。

3.2 数据移位无论是串行输入还是并行输入的移位寄存器,当时钟信号到来时,数据都会在存储单元之间进行移位操作。

移位的方向可以是向左移位(左移)或向右移位(右移),具体方向由控制信号决定。

移位寄存器的移位操作可以分为以下几种方式:3.2.1 逻辑右移逻辑右移是指将数据向右移位,最右边的位被丢弃,最左边的位用0填充。

3.2.2 逻辑左移逻辑左移是指将数据向左移位,最左边的位被丢弃,最右边的位用0填充。

单片机移位寄存器1. 什么是单片机移位寄存器单片机移位寄存器(Shift Register)是一种具有移位功能的寄存器,在数字电子电路中被广泛应用。

它由一组触发器(Flip-Flop)组成,可以将数据按照特定的方式进行移位操作。

2. 移位寄存器的工作原理移位寄存器通常由串行输入、串行输出、并行输入和并行输出四个主要部分组成。

其工作原理如下:•串行输入:数据输入信号逐位地经过寄存器,通过串行输入端口输入。

每当输入一个新的数据位时,原有的数据位将向左移位,腾出位置存放新的数据位。

•串行输出:从移位寄存器的串行输出端口输出数据。

当整个移位寄存器被移位后,最右边的数据位将从串行输出端口输出,同时,原有数据位向右移位填充空出的位置。

•并行输入:通过并行输入端口将整个数据一次性输入到移位寄存器中,不进行移位操作。

•并行输出:通过并行输出端口将整个移位寄存器的内容一次性输出。

3. 移位寄存器的应用场景移位寄存器在数字电子电路中具有广泛的应用,例如:3.1. 数据传输与存储移位寄存器可以用于将数据从一个地方传输到另一个地方,实现数据的序列化和反序列化。

在通信系统中,可以使用移位寄存器将并行数据转换为串行数据进行传输,或者将串行数据转换为并行数据进行处理。

3.2. 并行输入/输出扩展通过移位寄存器,可以将单片机的并行输入/输出引脚扩展为更多的输入/输出引脚。

通过将多个移位寄存器级联,可以实现更多的输入/输出引脚扩展。

3.3. 状态存储移位寄存器可以用于存储状态信息,例如程序计数器(Program Counter)和状态寄存器(Status Register)等。

4. 移位寄存器的类型根据移位寄存器的工作方式和结构特点,常见的移位寄存器包括以下几种类型:4.1. 并行入/串行出移位寄存器(PISO)并行入/串行出移位寄存器有多个并行输入引脚和一个串行输出引脚。

多个并行输入信号可以一次性并行输入到寄存器中,然后按位进行移位,输出到串行输出引脚上。

数电实验之移位寄存器移位寄存器一实验目的1.学习用D触发器构成移位寄存器(环行计数器)2.掌握中规模集成电路双向移位寄存器逻辑功能及使用方法二实验原理1、用4个D触发器组成4位移位寄存器,将每位即各D触发器的输出Q1、Q2、Q3、Q4分别接到四个0—1指示器(LED)将最后一位输出Q4反馈接到第一位D触发器的输入端,则构成一简单的四位移位环行计数器。

2、移位寄存器具有移位功能,是指寄存器中所存的代码能够在时钟脉冲的作用下依次左移或右移。

对于即能左移又能右移的寄存器称为双向移位寄存器。

只需要改变左移、右移的控制信号便可实现双向移位的要求。

根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

本实验选用的4位双向移位寄存器,型号为74LS194A(或CD40194),两者功能相同,其引脚分布图如下图18.1所示:其中A、B、C、D为并行输入端,A为高位依次排列;QA、QB、QC、QD为并行输出端;SR为右移串行输入端;SL为左移串行输入端;S1、S0为操作模式控制端;CLR为异步清零端;低电平有效;CLK为CP时钟脉冲输入端。

74LS194A有5种工作模式:并行输入,右移(QD→QA),左移(QD←QA),保持和清零。

74LS194功能表如表18.1所示:表18.1三实验器件数字实验箱集成电路芯片:74LS74×2 (CD4013×2);74LS75 ;74LS76 ;74LS194A(CD40194)。

图18.1四实验内容1.用74LS74组成移位寄存器,使第一个输出端点亮LED并使其右移循环。

顺序是FF1、FF2、FF3、FF4。

A) 1. 用两个74LS74按图18.2连接:图18.21. CP时钟输入先不接到电路中(单步脉冲源或连续脉冲源);1. 连接线路完毕,检查无误后加+5V电源;2. 观察4个输出端的LED应该是不亮的,如果有亮的话,应按清零端的逻辑开关,(给出一个低电平信号清零后,再将开关置于高电平)即将4个D触发器输出端的LED清零。

移位寄存器工作原理移位寄存器是数字电路中常见的一种元件,它在数字系统中扮演着非常重要的角色。

它可以实现数据的移位操作,常用于串行数据传输、数字信号处理、以及各种控制系统中。

在本文中,我们将深入探讨移位寄存器的工作原理,包括其结构、功能和应用。

移位寄存器通常由多个触发器组成,每个触发器都有一个时钟输入和一个数据输入。

当时钟触发时,数据会从一个触发器传输到下一个触发器,从而实现数据的移位操作。

根据时钟触发的方式,移位寄存器可以分为同步移位寄存器和异步移位寄存器两种类型。

同步移位寄存器的各个触发器都是由同一个时钟信号控制,而异步移位寄存器的触发器则可以独立地进行移位操作。

移位寄存器有多种工作模式,包括串行输入、并行输入、串行输出和并行输出等。

在串行输入模式下,数据按位输入到移位寄存器中,然后通过时钟触发逐位移位;在并行输入模式下,所有数据同时输入到寄存器中,然后通过时钟触发同时移位。

类似地,串行输出模式下,数据按位输出,而并行输出模式下,所有数据同时输出。

移位寄存器还可以实现各种功能,如数据的存储、数据的平移、数据的旋转等。

在数字信号处理中,移位寄存器常用于实现数字滤波器、乘法器、除法器等算法;在通信系统中,移位寄存器则用于实现数据的调制、解调、编码、解码等功能。

除此之外,移位寄存器还有许多应用。

在微处理器中,移位寄存器常用于实现逻辑运算、移位运算、乘法运算、除法运算等指令;在控制系统中,移位寄存器则用于实现状态机、计数器、定时器等功能。

总之,移位寄存器在数字系统中有着广泛的应用,是数字电路中不可或缺的重要元件。

综上所述,移位寄存器是数字系统中非常重要的元件,它通过触发器的移位操作实现数据的移位,具有多种工作模式和功能。

在各种应用领域中,移位寄存器都发挥着重要的作用,为数字系统的设计和应用提供了强大的支持。

希望本文能够对读者对移位寄存器的工作原理有所帮助,也希望读者能够进一步深入学习和应用移位寄存器的知识。

山东省考研电子信息科学与技术复习资料数字电路重要概念解析数字电路是电子信息科学与技术领域的重要基础学科之一,也是考研电子信息科学与技术复习中的关键内容。

掌握数字电路的重要概念对于理解和应用电子信息技术具有重要意义。

本文将对数字电路的重要概念进行解析和讲解,帮助考研学生更好地复习和掌握该知识点。

1. 逻辑门逻辑门是数字电路的基本构建单元,根据输入和输出的逻辑关系来实现特定的逻辑功能。

常见的逻辑门包括与门、或门、非门、异或门等。

其中,与门(AND gate)的输出仅在所有输入为1时为1,其余情况输出为0;或门(OR gate)的输出仅在所有输入为0时为0,其余情况输出为1;非门(NOT gate)的输出是输入信号的反相;异或门(XOR gate)的输出仅在输入中的1的数量为奇数时为1,偶数时为0。

2. 码制在数字电路中,为了能够用离散的信号表示各种信息,需要用不同的码制进行编码。

常见的码制有二进制码、BCD码、格雷码等。

其中,二进制码采用0和1表示信息;BCD码(二进制编码的十进制码)用4位二进制码表示一个十进制数;格雷码是一种反映连续数值变化的编码方式,相邻两个数值仅有一位的差异。

3. 各种时序触发器时序触发器是数字电路中常用的存储装置,用于存储和传递信号。

常见的时序触发器包括RS触发器、D触发器、JK触发器和T触发器等。

其中,RS触发器是最基本的触发器,通过置位和复位信号来控制输出状态;D触发器由RS触发器演化而来,通过时钟信号来控制输出状态;JK触发器是一种比较通用的触发器,可以实现其他触发器的功能;T触发器是一种特殊的JK触发器,内部反馈线路简化成单个输入。

4. 各种组合逻辑电路组合逻辑电路是由逻辑门组成的电路,根据输入信号直接输出结果。

常见的组合逻辑电路有加法器、减法器、译码器、编码器、多路选择器等。

在数字电路设计中,组合逻辑电路常用于实现各种逻辑函数和运算。

5. 计数器和移位寄存器计数器和移位寄存器是数字电路中常用的计数和移位操作的电路。