8421BCD码与余三码的相互转换

- 格式:docx

- 大小:320.69 KB

- 文档页数:13

一、写出二进制数1110001.11对应的八进制、十进制、十六进制和8421BCD 码形式的数值。

(1110001.11)2 = (161.6)8= (113.75)10 = (71.C)16=(0001 0001 0011.01110101)8421BCD(6C.8)16=(1101100.1)2= (154.4)8= (108.5)10=(0001 0000 1000. 0101)8421BCD(10011000)8421BCD =(1100010 )2=( 98 )10=( 62 )16。

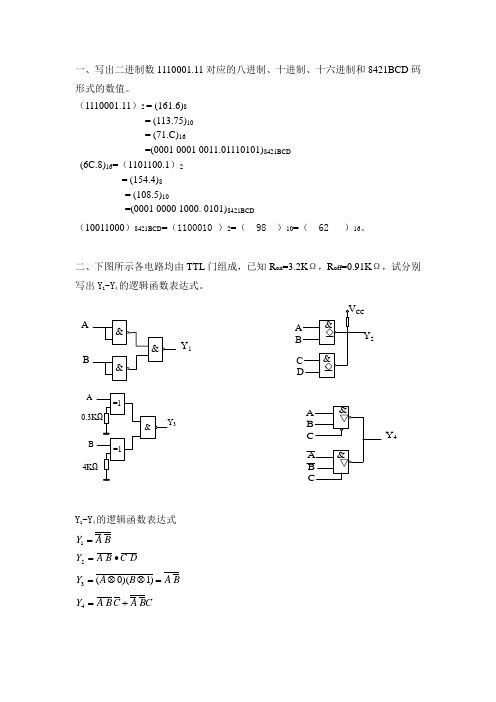

二、下图所示各电路均由TTL 门组成,已知R on =3.2K Ω,R off =0.91K Ω,试分别写出Y 1-Y 4的逻辑函数表达式。

A BY 12A B 4K 3Y 4Y 1-Y 4的逻辑函数表达式BA Y =1D C B A Y ∙=2B A B A Y =⊗⊗=)1)(0(3C B A C B A Y +=4Y 1Y 2A B 39KY 4Y 1-Y 4的逻辑函数表达式B A 1=Y DC B A Y ∙=20)1()0(3=+++=BA YC C 4B A B A Y +=AB11 B A + AA B A BAA B1AB B A 1三、1.要将一D 触发器转换为JK 触发器,则应令D= n n Q K Q J +2.上升沿触发的JK 触发器输入端波形(D R 为异步清0端,D S 为异步置数端)如下图所示,试画出输出端Q 的工作波形。

CP QS D R D J K↑∙+=+CP Q K Q J Q n n n )(1CP QS D R D J K3.上升沿触发的D 触发器输入端波形(D R 为异步清0端,D S 为异步置数端)如下图所示,试画出输出端Q 的工作波形。

↑∙=+CP Q n D 1CP QD S DR D4.上升沿触发的D 触发器输入端波形(D R 为异步清0端,D S 为异步置数端)如下图所示,试画出输出端Q 的工作波形。

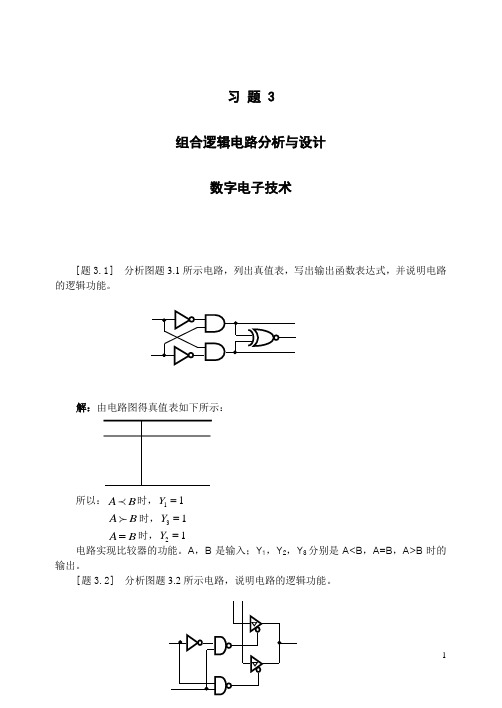

1习 题 3组合逻辑电路分析与设计数字电子技术[题3.1] 分析图题3.1所示电路,列出真值表,写出输出函数表达式,并说明电路的逻辑功能。

解:由电路图得真值表如下所示:所以:AB 时,11Y = A B 时,31Y = A B =时,21Y =电路实现比较器的功能。

A ,B 是输入;Y 1,Y 2,Y 3分别是A<B ,A=B ,A>B 时的输出。

[题3.2] 分析图题3.2所示电路,说明电路的逻辑功能。

2解:电路的逻辑函数表达式为:(10Y S EN A S EN B EN Y EN ⎧=⋅⋅+⋅⋅=⎪⎨=⎪⎩时);输出高阻态(时)电路的逻辑功能是:在使能条件EN=1且S=0时,输出A ;在使能条件EN=1且S=1时,输出B ;使能条件EN=0时,输出高阻态。

电路实现数据选择器的功能。

[题3.3] 图题3.3是一个密码锁控制电路。

开锁条件是必须将开锁开关闭合,且要拨对密码。

如果以上两个条件都得到满足,开锁信号为1,报警信号为0,即锁打开而不报警。

否则,开锁信号为0,报警信号为1。

试分析该电路的密码是多少。

解:1Y S ABCD =⋅2Y S ABCD =⋅分析电路可知:电路的密码是1001。

[题3.4] 图题3.4所示电路由4位二进制比较器7485和4位二选一数据选择器74157组成。

其中74157控制端B A /的控制作用为:B A /=0时,Y i =A i ,否则,Y i =B i 。

试分析图示电路的逻辑功能。

3解:当A B ≤时,输出A ;当A B 时,输出B ;所以电路的功能是输出A ,B 中较小的数。

[题3.5] 某建筑物的自动电梯系统有五个电梯,其中三个是主电梯(设为A 、B 、C ),两个备用电梯。

当上下人员拥挤,主电梯全被占用时,才允许使用备用电梯。

现需设计一个监控主电梯的逻辑电路,当任何两个主电梯运行时,产生一个信号(Y 1),通知备用电梯准备运行;当三个主电梯都在运行时,则产生另一个信号(Y 2),使备用电梯主电源接通,处于可运行状态。

学号:课程设计题目余3码转换成8421 BCD 码学院计算机科学与技术专业计算机科学与技术班级姓名指导教师2010 年06 月24 日课程设计任务书学生姓名拉巴珠久学生专业班级计算机0806指导教师黄靖学院名称计算机科学与技术学院一、题目:余3码转换成8421 BCD 码原始条件:使用“与”门( 74 LS 08 )、“或”门( 74 LS 32 )、非门( 74 LS 04 ),设计余3码转换成8421 BCD 码。

二、要求完成设计的主要任务如下:1.能够运用数字逻辑的理论和方法,把时序逻辑电路设计和组合逻辑电路设计相结合,设计一个有实际应用的数字逻辑电路。

2.使用同步时序逻辑电路的设计方法,设计余3码转换成8421 BCD 码。

写出设计中的三个过程。

画出课程设计图。

3.根据74 LS 08、74 LS 32、74 LS 04集成电路引脚号,在设计好的余3码转换成8421 BCD 码电路图中标上引脚号。

4.在试验设备上,使用74 LS 08、74 LS 32、74 LS 04集成电路连接、调试和测试余3码转换成8421 BCD 码电路。

指导教师签名:20 年月日系主任(责任教师)签名:20 年月日1设计目的1.掌握组合逻辑电路的基本概念与结构。

2.认识基本门电路74LS08、74LS32、74LS04的各端口,能够正确的使用。

3.了解余3码转换成8421BCD码的工作原理,调试及故障排除方法。

2设计要求1.能够运用数字逻辑的理论和方法,把时序逻辑电路设计和组合逻辑电路设计相结合,设计一个有实际应用的数字逻辑电路。

2.使用同步时序逻辑电路的设计方法,设计余3码转换成8421 BCD 码。

写出设计中的三个过程。

画出课程设计图。

3.根据74 LS 08、74 LS 32、74 LS 04集成电路引脚号,在设计好的余3码转换成8421 BCD 码电路图中标上引脚号。

4.在试验设备上,使用74 LS 08、74 LS 32、74 LS 04集成电路连接、调试和测试余3码转换成8421 BCD 码电路。

3.4 X 、Y 均为四位二进制数,它们分别是一个逻辑电路的输入和输出。

设: 当 0≤X≤ 4时, Y=X+1 ;当 5≤X≤9 时,Y=X -1,且X 不大于9。

(1) 试列出该逻辑电路完整的真值表; (2) 用与非门实现该逻辑电路。

解:(1) 按题意要求列真值表如下:0 0 0 0x 3x 2x 1x 0y 3y 2y 1y 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 10 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 0x x x x x x x x x x x x x x x x x x x x x x x xX X Y 033=x 3X X X X X Y 031022++=x 3X XX X X X X X X X X X Y 0132121231+++=x 3X Y 00=01001110000111101x 3x 2x 1x 01111(2) 把与或表达式转换为与非表达式,以便用与非门实现该逻辑电路。

X X X X Y 03033==X X X X X X X X X X Y 0310*******=++=X X X X X X X X X X X X X X X X X X X X X X X X Y 0132012012030132012012031=+++= X Y 00=作图如下:x 3x 2x 1x 0y 3y 2y 1y 03.5 设计一交通灯监测电路。

红、绿、黄三只灯正常工作时只能一只灯亮,否则,将会发出检修信号,用两输入与非门设计逻辑电路,并给出所用74系列的型号。

解:设A 、B 、C 分别表示红、绿、黄三只灯,且亮为1,灭为0;检修信号用L 表示,L 为1表示需要检修。

8421bcd转换为余三码的方法在计算机语言中,8421BCD是一种常用的数字编码方式,但在一些场合下,也需要将它转换为余三码的形式。

余三码已被广泛应用于数字电路的设计和计算机组成原理中。

下面,我们将分步骤介绍如何将8421BCD转换为余三码。

第一步:将8421BCD拆分成4位二进制数8421BCD指的是使用四个数码位来表示一个十进制数的一种编码方式。

8、4、2、1分别代表二进制数的8、4、2、1位。

将一个8421BCD数拆分成4位二进制数,是将每个数码位的数值转换成二进制数。

例如,将BCD码“0110 1001”拆分成4位二进制数就是“0110 1001”,因为每个数码位数值的8421BCD编码都可以直接转换成二进制数。

第二步:将每个二进制数转换为余数将二进制数转换为余数可以使用模三运算。

模三运算是指将一个数除以三后的余数。

对于一个二进制数,如果它的末位是1,则除以3后余1;如果末位是0,则除以3的余数为0。

例如,二进制数“1101”除以3的余数等于2,因为它的末位是1,“110”除以3的余数为0。

所以,“0110 1001”转换成余数的结果就是“010 010 101”。

第三步:将余数按倒序连接将余数按倒序连接就可以得到余三码。

这是因为在余三码中,高位和低位的顺序和二进制数是相反的。

例如,在二进制数中一个数的低位是在右边,而在余三码中,它的低位是在左边。

因此,在将多个余数连接在一起时,需要按倒序连接,才能得到正确的结果。

综上所述,将8421BCD转换为余三码需要完成三个步骤。

第一步是将8421BCD拆分成4位二进制数,第二步是将二进制数转换为余数,第三步是将余数按倒序连接。

这种转换方法可以帮助我们在数字电路设计和计算机组成原理中更好地应用余三码。

VHDL程序并行语句的应用一、实训目的1.巩固编译、仿真VHDL文件的方法。

2.掌握VHDL程序并行语句的应用。

二、实训器材计算机与Qu artusⅡ工具软件。

三、实训指导(一)实训原理8421BC D-余3码转换电路的真值表如表3-1所示。

表3-1 8421BC D-余3码转换电路的真值表输入输出a3 a2 a1 a0 y3 y2 y1 y00 0 0 0 0 0 1 10 0 0 1 0 1 0 00 0 1 0 0 1 0 10 0 1 1 0 1 1 00 1 0 0 0 1 1 10 1 0 1 1 0 0 00 1 1 0 1 0 0 10 1 1 1 1 0 1 01 0 0 0 1 0 1 11 0 0 1 1 1 0 0(二)实训步骤1.设计输入VH DL文件(1)建立工程项目。

(2)建立VHDL文件。

(3)用条件信号赋语句或选择信号赋值语句等并行语句设计VH DL文件。

VHDL代码如下:LIBRAR Y ieee;USE ieee.std_lo gic_1164.ALL;ENTITY ysmzhISPORT(a:IN STD_LO GIC_V ECTOR(3 DOWNTO 0);y:OUT STD_LO GIC_V ECTOR(3 DOWNTO 0));END ysmzh;ARCHIT ECTUR E a OF ysmzhISBEGINPROCES S(a)BEGINCASE a ISWHEN "0000"=>y<="0011";WHEN "0001"=>y<="0100";WHEN "0010"=>y<="0101";WHEN "0011"=>y<="0110";WHEN "0100"=>y<="0111";WHEN "0101"=>y<="1000";WHEN "0110"=>y<="1001";WHEN "0111"=>y<="1010";WHEN "1000"=>y<="1011";WHEN "1001"=>y<="1100";WHEN OTHERS=>NULL;END CASE;END PROCES S;END a;2.编译仿真VH DL文件(1)编译VHDL文件。

数字逻辑电路》课程设计

报告书

题目名称:余三码和8421BCD码相互转化的逻辑电路

学院:专业:机电工程学院电子信息工程

班级:2016 级 1 班学号:

1X01131XXX 姓名:XXX

指导教师:XXX

2018 年 6 月

课程设计报告书

1. 掌握组合逻辑电路的基本概念与结构。

2. 认识基本门电路 74LS08、74LS32、 74LS04、74LS48、 74LS27、74LS86

的各端口,并能够正确的使用。

3. 了解 8421BCD 码转换成余 3 码及余 3码转换成 8421BCD 码的工作原理, 调

试及故障排除方法。

4. 掌握芯片间的逻辑关系,准确的进行连线。

设计内容:

使用“与”门( 74LS08)、“或”门( 74LS32)、非门( 74LS04)、 七段数码管译码器驱动器( 74LS48)、三输入“或”门 74LS27、“异或门”

74LS86,设计 8421BCD 码转换成余 3 码及余 3 码转换成 8421BCD 码。

根据题意,要将 8421BCD 码转换成余 3 码及余 3码转换成 8421BCD 码 就必须得根据转换的规则来实现。

其中 8421BCD 码转换成余三码时, 8421BCD 码有

0000—0110七种输入,另外有 1101—1111是 3 种输入,这三 种输入转换成余三

码后用单个数码管无法进行显示; 余 3 码转换成 8421BCD 码时,余三码有

0011—1111十三种输入,另外有 0000—0010 是三种输入单 一数码管无法显示

的, 因此我们可以用这些无关小项来化简逻辑函数, 从而 得到优化的逻辑电路,正确的完成设计的要求。

功能说明:设 计 目 的

设计 内容 及

功能 说明

集成电路名称及引脚符号

74LS08 与门 74LS32 或门

74LS27 三输入“或”

74LS04 非门

门

设计

内容

及

功能

说明

74LS48 七段数码管译码器驱动器

8421BCD码转余3 码”

设

计

步

骤余3 码转8421BCD

码”

根据卡诺图,逻辑函数化简结果如下所示

8421BCD码转余3 码”

O3(A,B,C, D) A BD BC O2( A,B,C, D) BC BCD

BD O1( A,B,C, D) CD CD O0( A,B,C,D) D “余

3 码转8421BCD码” Y3(A,B,C, D) AB ACD

Y2(A,B,C, D) BC BCD BCD Y1(A, B,C,D) CD

CD Y0(A, B,C,D) D 4. 画出组合逻辑电路

设

计

步

骤

5. 调试

从 A,B,C,D 端输入 8421BCD 码得到的 O3,O2,O1,O0和输入余 3 码得到的

Y3,Y2,Y1,Y0如图所示,与预期结果相同。

输入

输出

A B C D O3 O2 O1 A0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 0 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 0 0 1 1 1 0 1 0 1 1 0 0 0 0

1

1

1

1

设 计 步 骤

设

计

步

骤

输入输出

A B C D Y3 Y2 Y1 Y0

0 0 1 1 0 0 0 0

0 1 0 0 0 0 0 1

0 1 0 1 0 0 1 0

0 1 1 0 0 0 1 1

0 1 1 1 0 1 0 0

1 0 0 0 0 1 0 1

1 0 0 1 0 1 1 0

1 0 1 0 0 1 1 1

1 0 1 1 1 0 0 0

1 1 0 0 1 0 0 1

余3 码转8421BCD

码

仿真电路

该仿真电路可以实现8421 码制和余三码的相互转化

设计小

结

s m n S ∙-J

≡M S

0⅛

H

E

™ i A n W

≡

=Ln 3Ul

QsOsl r 1511 115∣1 13 (阖冋

^^ ~~h

∣Λ⅛A∣A∣。