FPGA AXI4接口介绍

- 格式:pdf

- 大小:190.33 KB

- 文档页数:4

05AXI4总线axi-stream(AXI4总线实战)软件版本:vitis2020.2(vivado2020.2)操作系统:WIN10 64bit硬件平台:适⽤XILINX A7/K7/Z7/ZU/KU系列FPGA(⽶联客(milianke)MZU07A-EG硬件开发平台)登录"⽶联客"FPGA社区-视频课程、答疑解惑!5.1概述AXI4-Stream去掉了地址,允许⽆限制的数据突发传输规模,AXI4-Stream接⼝在数据流传输中应⽤⾮常⽅便,本来⾸先介绍了AXI4-Stream协议的型号定义,并且给出了⼀些Stream接⼝的时序⽅案图。

之后通过VIVADO⾃带的AXI4模板,创建axi-stream-master和axi-stream-slave ip。

通过图形设计连线,添加仿真激励完成验证。

本⽂实验⽬的:1:掌握基于VIVADO⼯具产⽣AXI协议模板2:掌握通过VIVADO⼯具产⽣AXI-Stream代码3:掌握通过VIVADO封装AXI-Stream图形化IP4:通过仿真验证AXI-Stream IP的⼯作是否正常。

5.2AXI4-Stream协议介绍5.2.1信号定义信号源描述ACLK时钟源信号在ACLK信号上升沿采样ARESETn复位源复位信号,ARESETn低电平有效TVALID master TVALID代表主设备数据有效,当TVALID和TREADY同时有效完成数据收发TREADY slave TREADY表⽰从设备准备可以,主设备可以发送数据,当TVALID和TREADY同时有效完成数据收发TDATA[(8n-1):0]master TDATA axi-stream的数据TSTRB[(n-1):0]master TSTRB[n-1:0]对应的bit位为1代表对应的字节有效,否则⽆效,但是会占⽤这个数据位。

TKEEP[(n-1):0]master KEEP[n-1:0]对应的bit位为1代表对应的字节有效,否则为空,可以丢掉。

技术交流DOI:10.3969/j.issn.1006-6403.2023.05.016基于FPGA 的JESD204B 接口设计[吴震霖]针对传统的ADC 数据传输方式存在的问题,提出了基于FPGA 的JESD204B 接口设计方法。

该方法利用FPGA 内部的高速串行接口以及IP 核实现JESD204B 协议的物理层和数据链路层的功能。

硬件测试结果表明,该方法使用FPGA 实现JESD204B 接口,满足FPGA 与高速ADC 芯片之间通过JESD204B 链路进行数据传输的需求,提高了数据传输的稳定性。

吴震霖硕士研究生,中国电子科技集团公司第三十四研究所,研究方向为高速数据采集与传输技术。

关键词:JESD204B 协议 高速串行接口 ADC FPGA摘要1 引言随着软件无线电技术的发展,高速ADC 的应用范围越来越广泛[1]。

数字中频技术使用高速ADC 对模拟中频信号进行采样,将模拟信号转换为适合FPGA 处理的数据流,对中频信号的采样通常要求ADC 具有高采样率的特点,因此,FPGA 与高速ADC 芯片之间的数据传输量巨大[2]。

传统的FPGA 与ADC 芯片之间通过并行的LVDS 接口进行传输,存在通道间串扰大、同步难的缺点[3]。

JESD204B 协议采用串行数据链路,减少了FPGA 与ADC 芯片之间互连的管脚数量,更少的走线布线,简化了系统设计,同时,可以实现更高的采样率,可以实现确定性时延,数据传输更加稳定可靠[4]。

介绍了JESD204B 协议的分层结构,并提出了基于FPGA 的JESD204B 接口设计方法,说明了该方法的时钟结构、发送器结构、接收器结构和AXI4-Lite 管理接口。

最后,将设计的JESD204B 接口在硬件平台上进行测试验证。

2 JESD204B 协议分层JESD204B 协议的分层结构如图1所示,包括应用层、传输层、数据链路层、物理层[5]。

发送端与接收端通过高速串行接口连接,从发送端到接收端可实现确定性延迟。

AXI4的PL与PS联合设计AXI4(Advanced eXtensible Interface 4)是一种用于高性能处理器之间和外设之间通信的标准总线接口。

在FPGA(Field-Programmable Gate Array)中使用AXI4接口可以实现PL(Programmable Logic)与PS (Processing System)的联合设计。

PL是FPGA中的可编程逻辑部分,可以根据用户的需求灵活地实现各种功能。

而PS是处理系统,包括处理器、内存和外设等,用于执行各种软件任务。

PL和PS的联合设计可以充分发挥二者的优势,提高系统的性能和灵活性。

在AXI4中,数据传输是通过总线事务实现的。

AXI4总线事务包括读取(Read)和写入(Write)操作。

在PL与PS之间进行通信时,可以使用AXI4总线事务来进行数据的传输。

首先,PL可以通过AXI4总线向PS发送读取请求。

PS接收到读取请求后,可以将数据从内存中读取出来,并通过AXI4总线返回给PL。

这样,PL就可以获取到来自PS的数据。

另外,PL也可以通过AXI4总线向PS发送写入请求。

PS接收到写入请求后,可以将数据写入到内存中。

这样,PL就可以将数据传输给PS,供PS进行后续处理。

除了数据传输外,PL和PS之间还可以通过AXI4总线传输控制信号。

比如,PL可以向PS发送中断请求信号,PS接收到后可以执行相应的处理。

此外,PL还可以通过AXI4总线向PS发送配置信息,以便PS对PL进行配置和控制。

在PL与PS联合设计中,AXI4总线可以起到连接二者的桥梁作用。

PL和PS通过AXI4总线进行数据传输和控制信号传递,实现了二者之间的高速通信。

这种设计可以将PL中的硬件加速器与PS中的软件进行有效结合,提高系统的性能和灵活性。

例如,可以将图像处理算法实现为PL中的硬件加速器,通过AXI4总线将待处理的图像数据传递给PL,然后PL对图像进行处理,再通过AXI4总线将处理结果传递给PS进行显示或存储。

AMBA AXI Protocol Version:2.0序言面向的读者:这是AMBA (高速微控制器总线结构)AXI(高速可扩展接口)协议的说明书。

主要面向想熟悉AMBA、或是想去设计与AMBA AXI协议相兼容的系统和模块的读者。

说明书的内容安排:第一章绪论阅读本章,你会了解到AXI协议的结构、该协议中定义的基本的交易过程。

第二章信号描述本章主要介绍AXI一些信号的定义,如:写地址通道、读数据通道、写反应通道、读地址通道、读数据通道、以及低功耗接口等所用到信号。

第三章通道握手介绍通道握手的整个过程第四章地址选择主要讲AXI猝发类型、如何去计算地址、在一次猝发中使用字节通道传输的过程。

第五章附加的控制信息本章主要讲怎样让AXI协议支持系统级缓存和保护单元。

第六章自动访问本章主要讲互斥访问和锁定访问第七章反应信号主要讲AXI从模块的四种交易反应。

第八章模式调整主要讲AXI协议如何使用ID 标签去进行无序传输。

第九章数据总线主要讲在AXI读和写数据线上,如何处理交易大小可变的数据,以及如何用字节固定端的方式去处理混合端类型数据。

第十章非对齐传输主要讲如何使用AXI协议处理非对齐传输。

第十一章时钟和复字节主要讲述AXI时钟和复字节信号的时序。

第十二章低功耗接口主要讲如何使用AXI时钟控制接口,进入或者跳出一种低功耗的模式。

第十三章AXI4主要描述AXI协议中AXI3版本和AXI4版本技术上的不同。

第十四章AXI4-Lite主要讲述AXI4-Lite接口,它是一种简单控制寄存器类型的接口,在不需要AXI4全部功能的时候使用。

说明书中的约定如下:●印刷字体的类型●第四页的时序图●第四页中的信号印刷字体的类型:斜体此类型的字体用于突出显示重要的注释,介绍专用术语,指出文中所用到的参照和引用。

加粗字体此类型的字体用于突出显示接口包含的成分,如:菜单名。

指示出信号的名字。

在描述列表的适当之处,也可用来表示术语。

理解AXIQuadSerialPeripheralInterface(SPI)IP核在使用MicroBlaze过程中,调用了此IP,所以有必须仔细学习下;名词:XIP:eXecute In PlaceMotorola M68HC11支持特性:*可配置的AXI4接口*支持对DRR/DTR FIFO的突发操作;*支持可配置的XIP模式操作;*支持AXI4-Lite或者AXI4接口连接的32bit Slave;*支持可配置的SPI模式:标准、双、四模式;*可编程的SPI时钟相位和极性;*可配置的FIFO深度,16、256深度;对XIP模式只支持64深度;*Configurable slave Memories in dual and quad modes are: Mixed,Micro,Winbond,and Spansion;*AXI 接口选项:XIP 模式:使能AXI4 和AXI4-Lite接口,地址模式可以选择24bit和32bit;Performance 模式:使能AXI4接口;使用AXI4接口可以在核的发送和接收FIFO地址处启用突发功能。

当不使能performance模式时,AXI4-Lite将被使用。

*SPI 选项模式可以选择:standard/dual/quadTransacton Width: 8/16/32频率比率:2~2048,代表了SPI的sck = ext_spi_clk/ratio ;NO. of Slave: 代表了slave的个数;1~32;*寄存器:AXI4-Lite写访问寄存器由32位AXI写数据(* _wdata)信号更新,不受AXI写数据选通(* _wstrb)信号的影响。

对于写入,AXI写地址有效(* _awvalid)和AXI写数据有效(* _wvalid)信号需要同时有效。

表2-3显示了适用的寄存器集,无论是否使能Performance Mode,或禁止XIP模式。

AXI4功能AXI4协议基于猝发式传输机制。

在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。

在主设备和从设备之间所传输的数据分别使用到从设备的写数据通道和到主设备的读数据通道。

在从主设备到从设备的写数据交易中,AXI有一个额外的写响应通道,从设备通过该通道向主设备发出信号表示完成写交易。

所有的AXI4包含了5个不同的通道:λ读地址通道(Read address channel, AR);写地址通道(Write address channel, AW);λλ读数据通道(Read data channel, R);写数据通道(Write data channel, W);λ写响应通道(Writeλ response channel, B);每个通道由一个信号集构成,并且使用双向的V ALID和READY握手信号机制。

信息源使用V ALID信号,表示在通道上存在可用的有效数据或者控制信息;而信息接收源使用READY信号,表示可以接收数据。

读数据通道和写数据通道也包含LAST信号,该信号用来表示在一个交易发生时,最后一个传输的数据项。

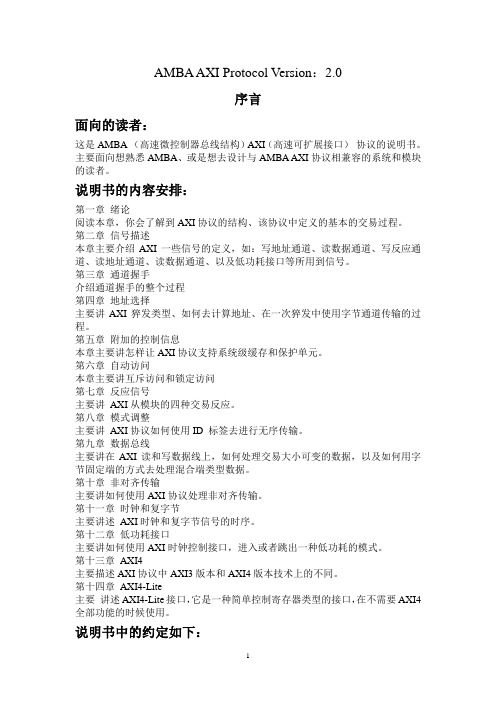

图2.1给出了AXI4使用读地址和读数据通道的读交易。

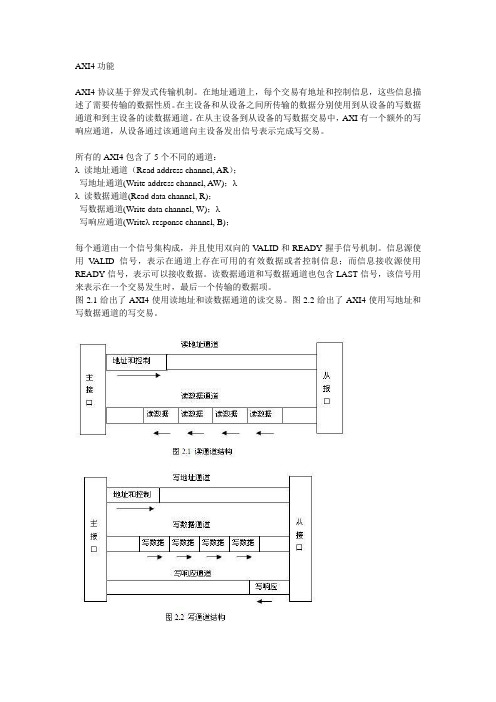

图2.2给出了AXI4使用写地址和写数据通道的写交易。

2.2.1 AXI4全局信号表2.1给出了AXI4的全局信号。

2.2.2 低功耗接口信号表2.2给出了AXI4的低功耗接口信号。

2.2.3 AXI4通道及信号读和写交易有各自的地址通道。

地址通道上给出交易所要求的地址和控制信息。

AXI4读和写地址通道包括下面的机制:λ可变长度的猝发操作,每次猝发操作包含1-256数据;提供服务质量(QoS)信号λ支持多个区域接口;λλ猝发传输不能超过4k边界;包裹、递增和非递增猝发;λ使用互斥和锁的原子操作;λ系统级缓存和缓冲控制;λλ安全和特权访问。

1.读和写地址通道读和写交易有各自的地址通道。

地址通道加载交易所有要求的地址和控制信息,表2.3给出了写地址通道信号及信号定义。

FPGAAXI4接⼝介绍FPGA AXI4总线简介——整理⾃CSDN,新浪博客,eefocus等by绿⽌冰崖2018.1⼀、AXI总线简介AXI是ARM1996年提出的微控制器总线家族AMBA(Advanced Microcontroller Bus Architecture)协议中的⼀部分,是⼀种⾯向⾼性能,⾼带宽,低延迟的⽚内总线。

通过统⼀的AXI接⼝,开发者为开发ip core只需要学习⼀种协议即可。

AXI的第⼀个版本出现在AMBA3.0,发布于2003年。

当前的最新的版本发布于2010年。

NetFPGA10G采⽤了AXI4系列总线架构,⽽Xilinx从Virtex6,Spartan6才开始⽀持AXI4。

如需AXI4整体总线通信模式,请参看ARM AXI4Specification,XilinxUG761AXI Reference Guide。

AXI4-Llite和AXI4-Stream接⼝是AXI4接⼝的⼦集,他们的主要区别及各⾃的优势如下:AXI4:主要⾯向⾼性能地址映射通信的需求,允许最⼤256轮的数据突发传输; AXI4-Lite:简称为AXI,是⼀个轻量级的地址映射单次传输接⼝,占⽤很少的逻辑单元,是⼀个简单地吞吐量地址映射性通信总线,⽤于CPU与IP core之间的通信,从架构层⾯来说,AXI主要负责控制层⾯;AXI4-Stream:简称为AXIS,去掉了地址项,允许⽆限制的数据突发传输规模,⾯向⾼速流数据传输,⽤于各IP core之间进⾏⾼速数据传输,AXIS主要负责数据层⾯。

⼆、AXI4⼯作过程AXI4所采⽤的是⼀种READY,VALID握⼿通信机制,即主从模块进⾏数据通信前,根据操作先后对各所⽤到的地址、数据通道进⾏握⼿。

⼯作过程简单来说,就是传输发起⽅A等到传输接收⽅B的READY信号后,A将数据或地址与VALID信号同时发送给B。

2.1AXI⼯作过程AXI握⼿,传送信息的时序如图1所⽰。

基于FPGA的AXI4总线时序设计与实现

马飞;刘琦;包斌

【期刊名称】《电子技术应用》

【年(卷),期】2015(41)6

【摘要】针对AXI4总线设备之间的高速数据传输需求,根据AXI4总线协议,设计实现了一种基于FPGA的AXI4总线读写时序控制方法.以FPGA为核心,采用VHDL语言,完成了满足AXI4总线协议的读猝发方式数据传输和写猝发方式数据传输时序控制模块的设计.利用FPGA内部嵌入式系统提供的高性能数据传输接口完成AXI4时序控制模块的功能验证.实际应用表明,依据提出的设计方法实现的读写时序控制模块能够满足AXI4总线协议规定的时序关系,实现数据的高速正确传输,总线数据传输速率能够达到1.09 GB/s.

【总页数】4页(P13-15,19)

【作者】马飞;刘琦;包斌

【作者单位】北京空间机电研究所,北京100094;北京空间机电研究所,北京100094;北京空间机电研究所,北京100094

【正文语种】中文

【中图分类】TP336

【相关文献】

1.一种基于FPGA的ISA总线转CAN总线设计与实现 [J], 董文华;赵倩;程志华

2.基于SPI总线FLASH时序控制的FPGA实现 [J], 薛宏亮

3.基于FPGA的SAR数据源时序测试设计与实现 [J], 赵君;张宇坤;郭建奇

4.基于FPGA与ARM的多路时序控制系统设计与实现 [J], 王鹏;吕志刚;杜卫东

5.基于FPGA的SAR数据源时序测试设计与实现 [J], 赵君;蔡晓乐;张宇坤;郭建奇因版权原因,仅展示原文概要,查看原文内容请购买。

AXI4协议规范引言:AXI4(Advanced eXtensible Interface 4)是一种基于总线的互联标准,用于在现代计算机系统中连接多个IP核(Intellectual Property)。

它是由ARM公司开发的,旨在提供高性能、低功耗、可扩展的接口标准,方便IP核之间的通信和数据交换。

本文将详细介绍AXI4协议规范及其应用。

1. AXI4基本概念AXI4是AXI(Advanced eXtensible Interface)总线的第四个版本,相较于之前版本,它具有更加完善的功能和灵活性。

AXI4协议规范定义了一套一致的接口和通信机制,包括地址传输、数据传输、读写控制等。

它的设计目标是在高性能、高效能和低功耗之间取得平衡。

2. AXI4协议规范的主要特点2.1 高性能:AXI4使用了多种优化技术,例如乱序访问、多通道传输和同步等,以提供高性能的数据传输能力。

同时,它还支持全双工传输,能够同时进行读写操作,增强了系统的并行处理能力。

2.2 低功耗:AXI4在设计时考虑了功耗优化,采用了多种策略来减小功耗,例如自适应时钟门控、低功耗模式以及数据压缩等。

这些策略能够有效降低系统的功耗消耗。

2.3 可扩展性:AXI4协议规范支持多种方式的互连配置,包括单一主控模式、多主控模式和多从控模式等。

这在设计复杂的系统中具有重要的作用,能够方便地进行资源共享和IP核的扩展。

2.4 支持AMBA标准:AXI4兼容AMBA(Advanced Microcontroller Bus Architecture)标准,这使得它能够与其他AMBA协议兼容的IP核无缝集成,提高了系统的通用性和可拓展性。

3. AXI4的传输机制3.1 地址传输:AXI4使用32位或64位的地址总线进行地址传输,并支持4KB对齐的地址范围。

地址传输阶段包括有效地址和保留地址等信息。

3.2 数据传输:AXI4支持多种数据传输方式,包括单个传输、突发传输和无效传输等。

基于AXI4-Stream总线的数字视频接口IP核设计郑建立;漆荣辉;张璐【摘要】针对数字视频IP核间高速流数据传输,设计并实现了一种基于AXI4-Stream总线的数字视频接口IP核,对外部输入ITU601格式的数字视频信号,将其格式转化为符合AXI4-Stream总线协议的信号,并通过IP核的主端口输出到下一级IP核的从端口.采用Xilinx ISE Design Suite 14.6软件综合设计实现,结合ISE 自带ISim软件完成功能仿真,通过实际硬件电路验证了设计的正确性及可行性.【期刊名称】《电子科技》【年(卷),期】2016(029)009【总页数】5页(P161-165)【关键词】AXI4-Stream;数字视频信号;IP核【作者】郑建立;漆荣辉;张璐【作者单位】上海理工大学医疗器械与食品学院,上海200093;上海理工大学医疗器械与食品学院,上海200093;上海理工大学医疗器械与食品学院,上海200093【正文语种】中文【中图分类】TN943;TP336在SOC系统设计中,高级微控制器总线结构(Advanced Microcontroller Bus Architecture,AMBA)被广泛采用,已经迅速成为SOC结构和IP核开发的标准[1]。

AXI4、AXI4-Lite、AXI4-Stream这3种总线标准是AMBA第4版的重要组成部分。

AXI4总线有助于最大化性能和能效;AXI4-Lite总线和AXI4-Stream总线是FPGA实现的理想选择。

AMBA4.0总线是标准接口规范,由多家企业共同为行业而设定,包括业界领先的OEM厂商、半导体及EDA供应商等[2],可确保不同IP 核的兼容,加快SOC设计效率。

本文在深入分析和研究AXI4-Stream总线协议的基础上,通过VHDL硬件描述语言实现了对ITU601格式的数字视频输入信号转化为符合AXI4-Stream协议的视频输出信号,并通过ISim软件仿真及在基于Xilinx Zynq7000芯片设计的内窥镜视频处理系统电路上得到验证。

FPGA AXI4总线简介

——整理自CSDN,新浪博客,eefocus等

by绿止冰崖2018.1

一、AXI总线简介

AXI是ARM1996年提出的微控制器总线家族AMBA(Advanced Microcontroller Bus Architecture)协议中的一部分,是一种面向高性能,高带宽,低延迟的片内总线。

通过统一的AXI接口,开发者为开发ip core只需要学习一种协议即可。

AXI的第一个版本出现在AMBA3.0,发布于2003年。

当前的最新的版本发布于2010年。

NetFPGA10G采用了AXI4系列总线架构,而Xilinx从Virtex6,Spartan6才开始支持AXI4。

如需AXI4整体总线通信模式,请参看ARM AXI4Specification,Xilinx UG761AXI Reference Guide。

AXI4-Llite和AXI4-Stream接口是AXI4接口的子集,他们的主要区别及各自的优势如下:

AXI4:主要面向高性能地址映射通信的需求,允许最大256轮的数据突发传输; AXI4-Lite:简称为AXI,是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元,是一个简单地吞吐量地址映射性通信总线,用于CPU与IP core之间的通信,从架构层面来说,AXI主要负责控制层面;

AXI4-Stream:简称为AXIS,去掉了地址项,允许无限制的数据突发传输规模,面向高速流数据传输,用于各IP core之间进行高速数据传输,AXIS主要负责数据层面。

二、AXI4工作过程

AXI4所采用的是一种READY,VALID握手通信机制,即主从模块进行数据通信前,根据操作先后对各所用到的地址、数据通道进行握手。

工作过程简单来说,就是传输发起方A等到传输接收方B的READY信号后,A将数据或地址与VALID信号同时发送给B。

2.1AXI工作过程

AXI握手,传送信息的时序如图1所示。

图1AXI总线通讯时序简图

AXI总线主要分为五个通道:

读地址通道,包含ARVALID,ARREADY,ARADDR信号,ARVALID,ARREADY 是读地址通道的握手信号,ARADDR是读地址信号,32bit位宽;

写地址通道,包含AWVALID,AWREADY,AWADDR信号,AWVALID,AWREADY 是写地址通道的握手信号,AWADDR是写地址信号,32bit位宽;

读数据通道,包含RVALID,RREADY,RDATA,RRESP信号,RVALID,RREADY 是读数据通道的握手信号,RDATA是读数据信号,32bit位宽,RRESP为读回应信号,2bit位宽;

写数据通道,包含WVALID,WREADY,WDATA,WSTRB信号,WVALID, WREADY是写数据通道握手信号,WDATA为写数据信号,32bit位宽,WSTRB的每一位代表写数据中为1的字节,32/8=4bit位宽;

写应答通道,包含BVALID,BREADY,BRESP信号,BVALID,BREADY为写应答通道握手信号,BRESP为写回应信号,与RRESP一样,00代表成功,其它为错误,2bit位宽;

系统通道,包含:ACLK,ARESETN信号,ACLK为AXI总线时钟,ARESETN 是AXI总线复位信号,低电平有效。

2.1.1读操作流程

工作过程为主与从进行读地址通道握手并传输地址内容,然后在读数据通道握手并传输所读内容以及读取操作的回应,时钟上升沿有效,如图2所示。

图2AXI读操作流程图

2.1.2写操作流程

工作过程为主与从进行写地址通道握手并传输地址内容,然后在写数据通道握手并传输所读内容,最后再写回应通道握手,并传输写回应数据,时钟上升沿有效,如图3所示。

图3AXI写操作流程图

2.2AXIS工作过程

Axis简化了通讯过程,省去了地址操作,它的信号主要包括:

tready信号:从告诉主做好传输准备;

tvalid信号:主告诉从数据传输有效;

tlast信号:主告诉从该次传输为突发传输结尾;

tdata信号:数据,可选宽度32,64,128,256bit;

tstrb信号:为1的bit为对应tdata有效字节,宽度为tdata/8

tuser信号:用户定义信号,宽度为128bit

aclk信号:总线时钟,上升沿有效;

aresetn信号:总线复位,低电平有效;

通信时序如图4所示。

图4AXIS通讯时序

2.3小结

axi与axis是AXI4总线中通信复杂度较低的两条总线,最大开发难度存在于axi的控制平面向axis的数据平面下发参数时,由于axi与axis时钟频率不同而产生的跨时钟域数据传输问题。