第7章 数字逻辑电路

- 格式:ppt

- 大小:932.00 KB

- 文档页数:67

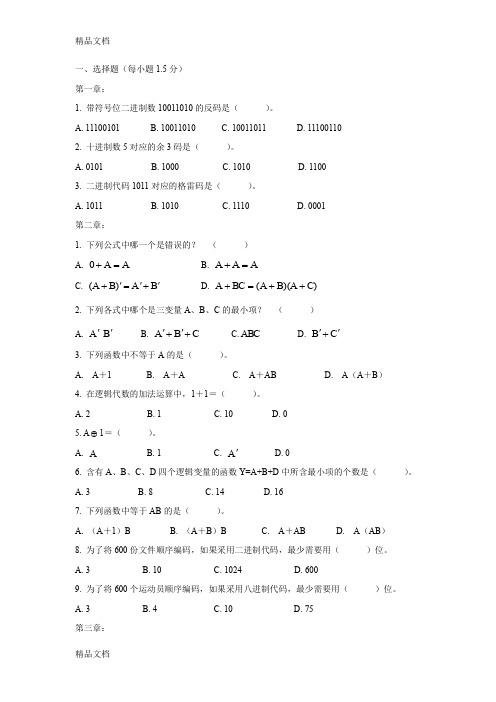

一、选择题(每小题1.5分)第一章:1. 带符号位二进制数10011010的反码是( )。

A. 11100101B. 10011010C. 10011011D. 111001102. 十进制数5对应的余3码是( )。

A. 0101B. 1000C. 1010D. 11003. 二进制代码1011对应的格雷码是( )。

A. 1011B. 1010C. 1110D. 0001第二章:1. 下列公式中哪一个是错误的? ( )A. A A 0=+B. A A A =+C. B A )B A ('+'='+D. )C A )(B A (BC A ++=+2. 下列各式中哪个是三变量A 、B 、C 的最小项? ( )A. B A ''B. C B A +'+'C.ABCD. C B '+'3. 下列函数中不等于A 的是( )。

A. A +1B. A +AC. A +ABD. A (A +B )4. 在逻辑代数的加法运算中,1+1=( )。

A. 2B. 1C. 10D. 05. A ⊕1=( )。

A. AB. 1C. A 'D. 06. 含有A 、B 、C 、D 四个逻辑变量的函数Y=A+B+D 中所含最小项的个数是()。

A. 3 B. 8 C. 14 D. 167. 下列函数中等于AB 的是( )。

A. (A +1)BB. (A +B )BC. A +ABD. A (AB )8. 为了将600份文件顺序编码,如果采用二进制代码,最少需要用( )位。

A. 3B. 10C. 1024D. 6009. 为了将600个运动员顺序编码,如果采用八进制代码,最少需要用( )位。

A. 3B. 4C. 10D. 75第三章:1. 采用漏极开路输出门电路(OD 门)主要解决了( )。

A. CMOS 门不能相“与”的问题B. CMOS 门的输出端不能“线与”的问题C. CMOS 门的输出端不能相“或”的问题2. 下列哪个特点不属于CMOS 传输门?( )A. CMOS 传输门属于双向器件。

第一章逻辑门电路§1-1 基本门电路一、填空题1.与逻辑;Y=A·B2.或逻辑;Y=A+B3.非逻辑;Y=4.与;或;非二、选择题1. A2. C3. D三、综合题1.2.真值表逻辑函数式Y=ABC§1-2 复合门电路一、填空题1.输入逻辑变量的各种可能取值;相应的函数值排列在一起2.两输入信号在它们;异或门电路3.并;外接电阻R;线与;线与;电平4.高电平;低电平;高阻态二、选择题1. C2. B3. C4. D5. B三、综合题1.2.真值表逻辑表达式Y1=ABY2=Y3==A+B 逻辑符号3.第二章组合逻辑电路§2-1 组合逻辑电路的分析和设计一、填空题1.代数;卡诺图2.n;n;原变量;反变量;一;一3.与或式;1;04.组合逻辑电路;组合电路;时序逻辑电路;时序电路5.该时刻的输入信号;先前的状态二、选择题1. D2. C3. C4. A5. A三、判断题1. ×2. √3. √4. √5. ×6. √四、综合题1.略2.(1)Y=A+B(2)Y=A B+A B(3) Y=ABC+A+B+C+D=A+B+C+D3. (1) Y=A B C+A B C+ A B C + ABC=A C+AC(2) Y=A CD+A B D+AB D+AC D(3) Y=C+A B+ A B4. (a)逻辑函数式Y= Y=AB+A B真值表逻辑功能:相同出1,不同出0 (b)逻辑函数式Y=AB+BC+AC真值表逻辑功能:三人表决器5.状态表逻辑功能:相同出1,不同出0逻辑图1. 6.Y=A ABC+B ABC+C ABC判不一致电路,输入不同,输出为1,;输入相同,输出为0。

§2-2 加法器一、填空题1.加数与被加数;低位产生的进位2.加数与被加数;低位产生的进位3.加法运算二、选择题1. A2. C三、综合题1.略2.略3.§2-3 编码器与比较器一、填空题1. 编码2. 101011;010000113. 十;二;八;十六4. 0;1;逢二进一;10;逢十进一5. 二进制编码器;二—十进制编码器6. 两个数大小或相等7. 高位二、选择题1. A2. B3. C4. B三、综合题1.略2.(1)10111;00100011(2)00011001;19(3)583. (1)三位二进制(2)1,1,0(3)1,1,14.§2-4 译码器与显示器一、填空题1. 编码器;特定含意的二进制代码按其原意;输出信号;电位;解码器2. 二进制译码器;二—十进制译码器;显示译码器3. LED数字显示器;液晶显示器;荧光数码管显示器4. 1.5~3;10mA/段左右5. 共阴极显示译码器;共阳极显示译码器;液晶显示译码器二、选择题1. A;D2. A三、判断题1.√2.×3.×4.√5.√四、综合题七段显示译码器真值表f=D C B A +D C B A +D C B A+D CB A +D C B A +D C B A =D+B A +C A +C B =DB AC AC B§2-5 数据选择器与分配器一、填空题1.多路调制器;一只单刀多掷选择开关;地址输入;数字信息;输出端2.从四路数据中,选择一路进行传输的数据选择器3.地址选择;输出端二、选择题1. D2. A;C三、判断题1. √2. ×四、综合题1.略2. Y=A B D0+A BD1+A B D2+ABD3第三章触发器§3-1 基本RS触发器与同步RS触发器一、填空题1.两个;已转换的稳定状态2.R S+RSQ n;R+S=13. R S Q n+ R S;RS=04.置0;置15.相同;低电平;高电平6.时钟信号CP7.D触发器8.空翻二、选择题1.D2.B3.A4.B5.B6.D三、判断题1. ×2. ×3. √4. ×5. ×6. ×四、综合题1.略2.3.4.5.略§3-2主从触发器与边沿触发器一、填空题1.空翻2.置0、置1、保持、翻转3.D、J Q n+K Q n4.保持、置1、清0、翻转5.电平、主从6.一次变化7.边沿触发器8.不同、做成9.置0、置1、时钟脉冲二、选择题1.A2.A3.D4.B5.A6.C7.D8.B9.A10.D三、判断题1. √2. ×3. ×4. ×5. √6. ×7. √8. √四、综合题1.2.3.4.略5.略6.§3-3触发器的分类与转换一、填空题1.T、T'2. T Q n+ T Q n、Q n3.1、04. Q n、Q n5. 16. T'7. T8. T'二、选择题1.D2.D3.D4.B5.B三、判断题1. ×2. ×3. ×4. ×四、分析解答题1.2.3.略4.略5.略第四章时序逻辑电路§4-1 寄存器一、填空题1.输入信号;锁存信号2.接收;暂存;传递;数码;移位二、选择题1. C2. B;A三、判断题1. √2. ×3. √四、综合题1.JK触发器构成D触发器,即Q n+1= D。

习 题 七1. 用4位二进制并行加法器设计一个实现8421码对9求补的逻辑电路。

解答设8421码为B 8B 4B 2B 1 ,其对9的补数为C 8C 4C 2C 1 ,关系如下:相应逻辑电路图如图1所示。

图 12. 用两个4位二进制并行加法器实现2位十进制数8421码到二进制码解答设两位十进制数的8421码为D 80D 40D 20D 10D 8D 4D 2D 1 ,相应二进制数为B 6B 5B 4B 3B 2B 1B 0,则应有B 6B 5B 4B 3B 2B 1B 0 = D 80D 40D 20D 10×1010+D 8D 4D 2D 1,运算如下:× D 80 1D 40 0 D 20 1 D 10 0 + D 80 D 40 D 80 D 20D 40 D 10 D 8D 20D 4 D 10D 2 D 1B 6B 5B 4 B 3B 2B 1B 0据此,可得到实现预定功能的逻辑电路如图2所示。

图 23. 用4位二进制并行加法器设计一个用8421码表示的1位十进制加法解答分析:由于十进制数采用8421码,因此,二进制并行加法器输入被加数和加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的范围为0000~10011(0~19,19=9+9+最低位的进位)。

因为题目要求运算的结果也是D 8 D 10D 2D 10 D 18421码,因此需要将二进制并行加法器输出的二进制数修正为8421码。

设输出的二进制数为FC 4 F 4 F 3 F 2 F 1,修正后的结果为'1'2'3'4'4F F F F FC ,可列出修正函数真值表如表1所示。

根据表1写出控制函数表达式,经简化后可得:据此,可画出逻辑电路图如图3所示。

图34. 用一片3-8线译码器和必要的逻辑门实现下列逻辑函数表达式。

解答假定采用T4138和与非门实现给定函数功能,可将逻辑表达式变换如下:逻辑电路图如图4所示。

199 第7章存储器和可编程逻辑器件图7.2 ROM的结构框图由图7.2可知,ROM 是由地址译码器、存储矩阵、读出电路(输出缓冲器)以及芯片选择逻辑等组成。

其中A 0~A n -1为地址输入线,共n 根,其代码是按二进制数进行编码,称为地址码。

通过地址译码器译出相应地址码的字线为W 0~W m -1共计m 根,字线的下标对应地址译码器输出的十进制数,字线与地址码的关系是m =2n 。

位线上的数据输出是被选中存储单元的数据。

2.各部分的功能(1)地址译码器地址译码器的功能是根据输入的地址代码,从n 条地址线中选择一条字线,以确定与该字线地址相对应的一组存储单元的位置。

选择哪一条字线,取决于输入的是哪一个地址代码。

任何时...刻,只能....有一条字线被选中........。

于是,被选中的那条字线对应的一组存储单元中的各位数码,经位线传送到数据线上输出。

n 条地址输入线可得到N =2n 个可能的地址。

(2)存储矩阵存储矩阵是ROM 的核心部件和主体,内部含有大量的存储单元电路。

存储矩阵中的数据和指令都是用一定位数的二进制数表示的。

存储器中存储1位二值代码(0或1)的点称为存储单元,存储器中的总存储单元数即为ROM 的存储容量。

例如,在图7.2所示的ROM 中,假设通过译码器输出的字线数m =210=1 024根,因为位线=8,所以,总的存储量应是1 024×8=8 192个存储单元,简称8KB 。

(3)读/写控制电路读/写控制电路也称为输出缓冲器,它是为了增加ROM 的带负载能力,同时提供三态控制,将被选中的M 位数据输出至位上,以便和系统的总线相连。

7.2.2 ROM的工作原理1.二极管ROM 电路的工作原理以图7.3所示的二极管ROM 电路为例说明其工作原理。

图7.3中的存储矩阵有4条字线W 0~W 3和4条位线D 0~D 3,共有16个交叉点,每个交叉点都可看作是一个存储单元。

交叉点处接有二极管时,相当于存入1,没有接二极管时相当于存入0。

第一章测试1.数字系统中,采用()可以将减法运算转化为加法运算。

A:补码B:原码C:ASCII码D:BCD码答案:A2.下列四个数中最大的数是()。

A:二进制数(10100000)B:十进制数(198)C:16进制数(AF)D:8421BCD码(001010000010)答案:D3.已知十进制数(10.4),下列结果与之相等的是()。

A:二进制数(1010.1)B:八进制数(12.4)C:五进制数(20.2)D:十六进制数(A.8)答案:C4.有一数码10010011,()。

A:作为2421BCD码时,它相当于十进制数93B:作为自然二进制数时,它相当于十进制数93C:作为余3码时,它相当于十进制数60答案:C5.将8421BCD码10000011转换成二进制数为()。

A:000100110001B:01000011C:01010011D:10000011答案:C6.二进制数(01100111)对应的格雷码是()。

A:01010100B:01100111C:00110001D:01101000答案:A7.格雷码(01100111)对应的二进制数码为()。

A:01010101B:01111010C:01010100D:01111110答案:C8.8421BCD码(01100001)对应的2421BCD码为()。

A:00011110B:00110001C:11001110D:11000001答案:D9.十进制数(35.72)对应的余3码为()。

A:01101000.10100101B:00110101.01110010C:00110101.11010010D:00111010.11010010答案:A第二章测试1.在变量A和B取值相异时,其逻辑函数值为1,相同时为0,称为异或运算。

()A:错B:对答案:B2.约束项在函数化简时可以当作1,是因为在实际电路中,这种输入组合根本不可能会让其发生。

()A:对B:错答案:A3.下列关于异或运算的式子中,不正确的是()。