第6章输入输出和中断技术

- 格式:ppt

- 大小:824.00 KB

- 文档页数:8

微机原理与接口技术复习题(本)第1章概论1. 什么是程序和指令?2. 洪。

诺依曼计算机的核心原理是什么?3. 存储程序的概念是什么?4. CPU由那三部分组成?主机由那几部分组成?5. CPU对内存有那两种操作?6. 325.625D=- B= H234D= BCD7. 已知X=-1110011B,试求[X]原、[X]反、[X]补。

8. 已知X=-1110111B ,Y=+1011010B,求[X+Y]补。

9. 已知X=-1101001B ,Y=-1010110B 计算X-Y。

第2章微型计算机基础1. 微处理器内部由那三部分组成?2. 控制器有那些功能?3. 8086由那两部分组成?其功能是什么?4. 熟悉8088最小模式下的主要引脚功能。

5. 指令队列有什么功能?6. 8088的8个通用寄存器是什么?4个段寄存器是什么?两个控制寄存器是什么?7. 什么是逻辑地址和物理地址,有什么关系什么?8. 4个段寄存器中那一个段寄存器用户程序不用设置。

9. 什么是总线?10. 总线周期中,什么情况下要插入TW等待周期?11. 8088CPU中标志寄存器包含那些标志位什么?第3 章、第4章8088指令系统与汇编语言程序设计1. 什么是寻址方式? 8088CPU有那些寻址方式?2. 试说明MOV SI ,[BX ] 与LEA SI , [BX]两条指令的区别。

3. 设DS=212AH ,CS=0200H ,IP=1200H, BX=0500H , DATA=40H,[217A0H]=2300H, [217E0H]=0400H ,[217E2H]=9000H ,试确定下列指令的转移地址:(1) JMP BX(2) JMP WORD PTR [BX](3) JMP DWORD PTR [BX]4. 设SP=2300H ,AX=50ABH ,BX=1234H ,执行PUSH AX 后SP=?在执行PUSH BX ,POP AX后SP=?,AX=?,BX=?.5. 已知AL=7BH ,BL=38H ,试问执行ADD AL ,BL 后的6个状态标志是什么?6. 试判断下列程序执行后AX中的内容是什么。

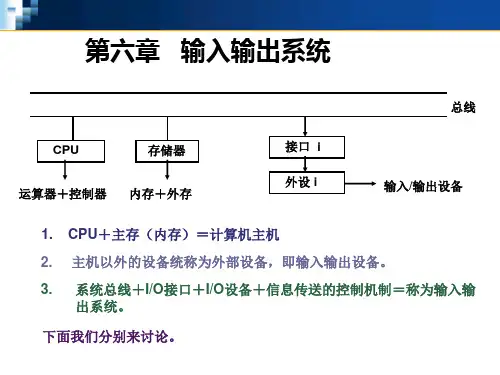

第六章输入输出系统1、通过硬件和软件的功能扩充,把原来独占的设备改造成若干用户共享的设备,这种设备称为()。

A、存储设备B、系统设备C、虚拟设备D、用户设备2、CPU输出数据的速度远远高于打印机的打印速度,为解决这一矛盾,可采用()。

A、并行技术 B.通道技术C、缓冲技术D、虚存技术3、为了使多个进程能有效的同时处理I/O,最好使用()结构的缓冲技术。

A、缓冲池B、单缓冲区C、双缓冲区D、循环缓冲区4、磁盘属于①(),信息的存取是以②()单位进行的,磁盘的I/O控制主要采取③()方式,打印机的I/O控制主要采取③()方式。

①A、字符设备 B、独占设备 C、块设备D、虚存设备②A、位(bit) B、字节C、桢D、固定数据块③A、循环测试 B、程序中断 C、DMA D、SPOOLing5、下面关于设备属性的论述中正确的为()。

A、字符设备的一个基本特征是不可寻址的,即能指定输入时的源地址和输出时的目标地址B、共享设备必须是可寻址的和可随机访问的设备C、共享设备是指在同一时刻内,允许多个进程同时访问的设备D、在分配共享设备和独占设备时,都可能引起进程死锁6、下面关于虚拟设备的论述中,正确的是()。

A、虚拟设备是指允许用户使用比系统中具有的物理设备更多的设备B、虚拟设备是指把一个物理设备变成多个对应的逻辑设备C、虚拟设备是指允许用户以标准化方式来使用物理设备D、虚拟设备是指允许用户程序不必全部装入内存便可使用系统中的设备7、通道是一种特殊①(),具有②()能力,它用于实现③()之间的信息传输。

①A、I/O设备B、设备控制器C、处理机D、I/O控制器②A、执行I/O指令集 B、执行CPU指令集C、传输I/O指令D、运行I/O进程③A、内存与外设B、CPU与外设C、内存与外存D、CPU与外存8、为实现设备分配,应为每类设备设置一张①(),在系统中配置一张①(),为实现设备的独立性,系统中应设置一张②()。

①A、设备控制表B、控制器控制表C、系统设备表D、设备分配表②A、设备开关表B、I/O请求表C、系统设备表D、逻辑设备表9、下面不适合于磁盘调度算法的是()。

《微型计算机原理及应用》(吴宁著)课后习题答案下载《微型计算机原理及应用》(吴宁著)内容提要目录第1章计算机基础1.1 数据、信息、媒体和多媒体1.2 计算机中数值数据信息的表示1.2.1 机器数和真值1.2.2 数的表示方法——原码、反码和补码1.2.3 补码的运算1.2.4 定点数与浮点数1.2.5 BCD码及其十进制调整1.3 计算机中非数值数据的信息表示1.3.1 西文信息的表示1.3.2 中文信息的表示1.3.3 计算机中图、声、像信息的表示1.4 微型计算机基本工作原理1.4.1 微型计算机硬件系统组成1.4.2 微型计算机软件系统1.4.3 微型计算机中指令执行的基本过程 1.5 评估计算机性能的主要技术指标1.5.1 CPU字长1.5.2 内存储器与高速缓存1.5.3 CPU指令执行时间1.5.4 系统总线的传输速率1.5.5 iP指数1.5.6 优化的内部结构1.5.7 I/O设备配备情况1.5.8 软件配备情况习题1第2章 80x86/Pentium微处理器2.1 80x86/Pentium微处理器的内部结构 2.1.1 8086/8088微处理器的基本结构2.1.2 80386CPU内部结构2.1.3 80x87数学协处理器2.1.4 Pentium CPU内部结构2.2 微处理器的主要引脚及功能2.2.1 8086/8088 CPU引脚功能2.2.2 80386 CPU引脚功能2.2.3 Pentium CPU引脚功能2.3 系统总线与典型时序2.3.1 CPU系统总线及其操作2.3.2 基本总线操作时序2.3.3 特殊总线操作时序2.4 典型CPU应用系统2.4.1 8086/8088支持芯片2.4.2 8086/8088单CPU(最小模式)系统 2.4.3 8086/8088多CPU(最大模式)系统 2.5 CPU的工作模式2.5.1 实地址模式2.5.2 保护模式2.5.3 虚拟8086模式2.5.4 系统管理模式2.6 指令流水线与高速缓存2.6.1 指令流水线和动态分支预测2.6.2 片内高速缓存2.7 64位CPU与多核微处理器习题2第3章 80x86/Pentium指令系统3.1 80x86/Pentium指令格式3.2 80x86/Pentium寻址方式3.2.1 寻址方式与有效地址EA的概念 3.2.2 各种寻址方式3.2.3 存储器寻址时的段约定3.3 8086/8088 CPU指令系统3.3.1 数据传送类指令3.3.2 算术运算类指令3.3.3 逻辑运算与移位指令3.3.4 串操作指令3.3.5 控制转移类指令3.3.6 处理器控制类指令3.4 80x86/Pentium CPU指令系统3.4.1 80286 CPU的增强与增加指令 3.4.2 80386 CPU的增强与增加指令 3.4.3 80486 CPU增加的指令3.4.4 Pentium系列CPU增加的指令 3.5 80x87浮点运算指令3.5.1 80x87的数据类型与格式3.5.2 浮点寄存器3.5.3 80x87指令简介习题3第4章汇编语言程序设计4.1 程序设计语言概述4.2 汇编语言的程序结构与语句格式 4.2.1 汇编语言源程序的框架结构4.2.2 汇编语言的语句4.3 汇编语言的伪指令4.3.1 基本伪指令语句4.3.2 80x86/Pentium CPU扩展伪指令 4.4 汇编语言程序设计方法4.4.1 程序设计的基本过程4.4.2 顺序结构程序设计4.4.3 分支结构程序设计4.4.4 循环结构程序设计4.4.5 子程序设计与调用技术4.5 模块化程序设计技术4.5.1 模块化程序设计的特点与规范4.5.2 程序中模块间的关系4.5.3 模块化程序设计举例4.6 综合应用程序设计举例4.6.1 16位实模式程序设计4.6.2 基于32位指令的实模式程序设计 4.6.3 基于多媒体指令的实模式程序设计 4.6.4 保护模式程序设计4.6.5 浮点指令程序设计4.7 汇编语言与C/C 语言混合编程4.7.1 内嵌模块方法4.7.2 多模块混合编程习题4第5章半导体存储器5.1 概述5.1.1 半导体存储器的分类5.1.2 存储原理与地址译码5.1.3 主要性能指标5.2 随机存取存储器(RAM)5.2.1 静态RAM(SRAM)5.2.2 动态RAM(DRAM)5.2.3 随机存取存储器RAM的应用5.3 只读存储器(ROM)5.3.1 掩膜ROM和PROM5.3.2 EPROM(可擦除的PROM)5.4 存储器连接与扩充应用5.4.1 存储器芯片选择5.4.2 存储器容量扩充5.4.3 RAM存储模块5.5 CPU与存储器的典型连接5.5.1 8086/8088 CPU的'典型存储器连接5.5.2 80386/Pentium CPU的典型存储器连接 5.6 微机系统的内存结构5.6.1 分级存储结构5.6.2 高速缓存Cache5.6.3 虚拟存储器与段页结构习题5第6章输入/输出和中断6.1 输入/输出及接口6.1.1 I/O信息的组成6.1.2 I/O接口概述6.1.3 I/O端口的编址6.1.4 简单的I/O接口6.2 输入/输出的传送方式6.2.1 程序控制的输入/输出6.2.2 中断控制的输入/输出6.2.3 直接数据通道传送6.3 中断技术6.3.1 中断的基本概念6.3.2 中断优先权6.4 80x86/Pentium中断系统6.4.1 中断结构6.4.2 中断向量表6.4.2 中断响应过程6.4.3 80386/80486/Pentium CPU中断系统6.5 8259A可编程中断控制器6.5.1 8259A芯片的内部结构与引脚6.5.2 8259A芯片的工作过程及工作方式 6.5.3 8259A命令字6.5.4 8259A芯片应用举例6.6 82380可编程中断控制器6.6.1 控制器功能概述6.6.2 控制器主要接口信号6.7 中断程序设计6.7.1 设计方法6.7.2 中断程序设计举例习题6第7章微型机接口技术7.1 概述7.2 可编程定时/计数器7.2.1 概述7.2.2 可编程定时/计数器82537.2.3 可编程定时/计数器82547.3 可编程并行接口7.3.1 可编程并行接口芯片8255A7.3.2 并行打印机接口应用7.3.3 键盘和显示器接口7.4 串行接口与串行通信7.4.1 串行通信的基本概念7.4.3 可编程串行通信接口8251A7.4.3 可编程异步通信接口INS82507.4.4 通用串行总线USB7.4.5 I2C与SPI串行总线7.5 DMA控制器接口7.5.1 8237A芯片的基本功能和引脚特性 7.5.2 8237A芯片内部寄存器与编程7.5.3 8237A应用与编程7.6 模拟量输入/输出接口7.6.1 概述7.6.2 并行和串行D/A转换器7.6.3 并行和串行A/D转换器习题7第8章微型计算机系统的发展8.1.1 IBM PC/AT微机系统8.1.2 80386、80486微机系统8.1.3 Pentium及以上微机系统8.2 系统外部总线8.2.1 ISA总线8.2.2 PCI局部总线8.2.3 AGP总线8.2.4 PCI Express总线8.3 网络接口与网络协议8.3.1 网络基本知识8.3.2 计算机网络层次结构8.3.3 网络适配器8.3.4 802.3协议8.4 80x86的多任务保护8.4.1 保护机制与保护检查8.4.2 任务管理的概念8.4.3 控制转移8.4.4 虚拟8086模式与保护模式之间的切换 8.4.5 多任务切换程序设计举例习题8参考文献《微型计算机原理及应用》(吴宁著)目录本书是普通高等教育“十一五”国家级规划教材和国家精品课程建设成果,以教育部高等学校非计算机专业计算机基础课程“基本要求V4.0”精神为指导,力求做到“基础性、系统性、实用性和先进性”的统一。

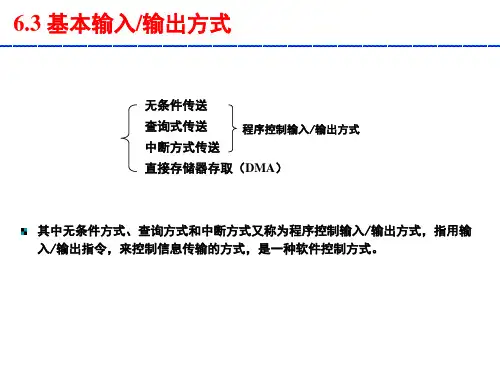

第六章输入/输出方式与接口芯片第一节输入/输出方式第二节中断第三节可编程定时/计数器8254及其应用第四节可编程并行I/O接口芯片8255A及其应用第五节可编程中断控制器8259及其应用第一节输入/输出方式●教学目标介绍I/O 接口的基本概念介绍I/O端口的编址方式介绍CPU与外设间的数据传送关系●学习要求掌握I/O接口的基本功能,了解接口的一般结构熟悉I/O端口的编址方式,了解IN/OUT指令的执行过程掌握微机与外设的各种传送方式,了解DMA传送过程一、I/O接口1)I/O接口的基本概念I/O接口是连接CPU与外设的逻辑控制部件,它主要在CPU与外设间起着传输状态与命令信息,实现数据的缓冲、数据格式转换等作用。

它的主要功能有:选择外设对外设进行控制和监视进行数据寄存和缓冲进行数据格式转换进行信号电平转换I/O接口的分类并行I/O接口和串行I/O接口可编程接口和不可编程接口专用接口和通用接口2)I/O接口的基本结构主要包含有数据端口、状态端口和控制端口数据端口用于存放数据信息,包括数据输入寄存器和数据输出寄存器,主要作用是协调CPU和外设之间的数据传输速度。

控制端口用于存放控制信息,控制信息是CPU通过接口传送给外设的,其主要作用是控制外设工作,如控制输入输出装置的启/停等。

状态端口用于存放状态信息,即反映外设当前工作的状态信息,CPU可通过读取这些信息,了解外设当前的工作情况。

3)I/O端口的寻址方式在一个微机系统中既有存储单元地址又有I/O端口地址,根据两者地址的不同安排可分为以下两种寻址方式。

存储器统一编址在这种方式中,把I/O端口作为存储器的一个单元来对待,即每个端口占用一个存储单元地址。

此时,对I/O端口操作可以使用全部的存储器指令,而不必另设专门的I/O指令。

由于该方式是将I/O地址映射到了存储器地址空间,所以也称为存储器映像方式。

I/O端口独立编址在这种方式下,I/O端口与存储器各自独立编址,这样存储器地址和I/O端口地址可以重叠。

《计算机接口技术》部分习题参考解答第4章 PC机的总线结构和时序4-1 答:总线周期是指CPU从存储器端口或I/O端口存取一个字节所需的时间。

8088/8086基本总线周期由4个时钟周期组成。

IBM PC/XT/A T中,CPU时钟频率是4.77MHz,时钟周期是210ns。

XT机的一个基本总线周期是4个时钟周期,一个输入或输出周期是5个时钟周期。

4-2 答:在T1状态下,8088/8086CPU数据/地址线上是地址信息。

用ALE信号可将地址信息锁存起来。

数据信息在T2开始以后送出。

XT机的AD7~AD0在ALE下降沿控制锁存后送系统地址总线A7~A0。

A19/S6~A16/S3经ALE下降沿控制锁存后送系统地址总线A15~A8;CPU的AD7~AD0在8288发出的DT/!R(数据收发控制信号)和DEN(数据允许)信号控制下,经双向总线驱动器连接到系统数据总线D7~D0,这样,实现了地址和数据及状态信号的分离,使地址信号和数据信号同时分别出现在系统地址总线和数据总线上。

(注意:这里用符号“!”表示逻辑非,对于信号则表示低电平有效,下同。

)4-3 答:PC/XT机中8088的MN/!MX引脚接地,因此工作在最大模式。

8088最大模式系统由8088CPU、8284时钟信号发生器和8288总线控制器组成。

总线控制器发出一些存储器和输出控制信号,接入系统总线后的名称为!IOW、!IOR、!MEMW、!MEMR、ALE信号,此外它还发出中断响应信号!INTA、DT/!R和DEN 等信号。

这些信号是由CPU连接8288的S2、S1、S0三线的电平决定的。

4-4 答:8284时钟发生器的作用是将晶振信号分频,向8088及计算机系统提供符号定时要求的各种时钟信号,并产生准备好和系统复位信号。

CLK信号:4.77MHz,提供XT机时钟频率。

PCLK信号:2.38MHz,分频后供8253使用。

OSC信号:14.31818MHz,供显示器使用。