主从触发器与边沿触发器的比较与应用研究

- 格式:docx

- 大小:37.26 KB

- 文档页数:3

边沿D 触发器电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

英文全称为data flip-flop或delay flip-flop。

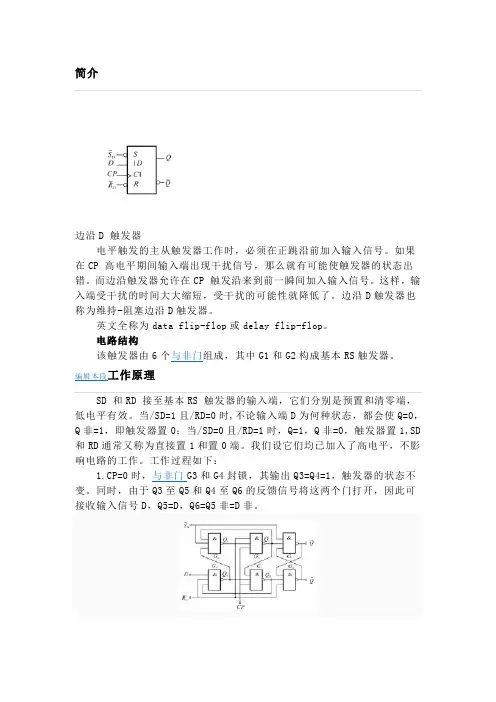

电路结构该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

编辑本段工作原理SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当/SD=1且/RD=0时,不论输入端D为何种状态,都会使Q=0,Q非=1,即触发器置0;当/SD=0且/RD=1时,Q=1,Q非=0,触发器置1,SD 和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5非=D非。

D触发器原理2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5非=D非,Q4=Q6非=D。

由基本RS触发器的逻辑功能可知,Q=Q3非=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

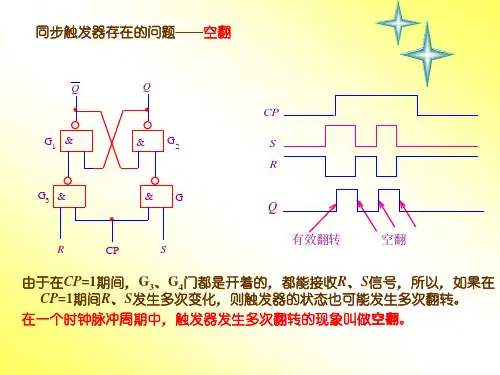

第23卷2009年3月甘肃联合大学学报(自然科学版)Jour nal of G ansu Lianhe U niver sity (N atural Sciences)Vo l.23M ar.2009收稿日期:2008-01-10.作者简介:吴凤凰(1977-),女,河南郑州人,南京农业大学讲师,硕士,主要从事智能控制方面的研究.文章编号:1672-691X(2009)03-0010-03触发器三种触发方式的分析与比较吴凤凰1,赵 静2(1.南京农业大学理学院,江苏南京210095;2.中州大学工程技术学院河南郑州450044)摘 要:分析与比较了触发器三种触发方式:电平触发、脉冲触发、边沿触发.在不同的触发方式下,当触发信号到达时,触发器的状态转换过程具有不同的动作特点.特别是时钟信号在有效电平时,输入端信号发生变化,主从结构的S R 触发器的多次翻转,而主从结构的J K 触发器发生 一次翻转 的情况.掌握这些动作特点对于正确使用触发器是非常必要的.关键词:触发器;边沿触发;SR 触发器;J K 触发器中图分类号:T N 783 文献标识码:A触发器作为能够存储1位二值信号的基本单元电路,对其内容的理解程度直接影响后面时序逻辑电路的学习.根据电路结构的不同,触发器的触发方式分为电平触发,脉冲触发和边沿触发.不同的电路结构在输入状态发生变化过程中具有不同的动作特点.掌握这些动作特点对正确使用触发器是十分必要的.1 S R 触发器的电平触发及脉冲触发的比较SR 触发器的结构如图1所示,主从SR 触发器的结构如图2所示.如果输入端(CL K 、S 、R )的信号如图3所示,对于电平触发的SR 触发器,输出端(Q 、Q )的波形图如图3所示.主从SR 触发器输出(Q 、Q )波形图如图4所示.由图可见,电平触发SR 触发器和主从SR 触发器在输入端(CL K 、S 、R)信号相同的情况下,前者在CL K =1期间,输出端按照SR 触发器特性表变化.前5个脉冲,由于S R 在图3 电平触发SR 触发器CLK =1期间未改变,故输出在CL K =1期间保持,第6个脉冲CL K =1期间,S 由1 0,R 由0 1,故输出端在CL K =1期间由1 0.主从SR触发器的主触发器结构与SR 触发器相同,故输出相同,见图3中的Q 和图4中的Q m ,而从触发器的输出是在CL K 下降沿随着主触发器而变.可见,如果在有效电平,输入端有干扰出现,这两种触发方式都会产生误动作.图4 主从SR 触发器2 主从S R 触发器和主从J K 触发器的比较主从S R 触发器的结构如图2所示,主从J K 触发器的结构如图5所示.图5 主从J K 触发器结构比较图5和图6,图5中的输入端(CL K 、S 、R)信号与图6中的输入端信号(CL K 、J 、K )相同,前5个脉冲,主从SR 触发器和主从J K 触发器的输出端都是按照SR 和J K 触发器的特性表在下降沿发生变化.第6个脉冲期间,输入信号发生对于主从SR 触发器,主触发器输出随着输入发生多次翻转:0 1 0,而对于主从JK 触发器的主触发器只发生一次翻转:0 1.这一特点是教学中的重点也是难点.3 主从J K 触发器和边沿触发J K触发器的比较以下降沿触发的J K 触发器为例.J 、K 输入端输入相同的信号,从图6和图7可以看出,第1到第5个脉冲,在时钟信号高电平期间输入端信号没有发生变化,两触发器的输出相同;而第6个图6 主从JK 触发器波形图信号,在时钟信号高电平期间输入端信号发生变化,两触发器的输出不同.对于主从J K 触发器,发生了一次翻转,Q 端输出由0变1,而边沿触发J K 触发器,因为不受在时钟信号高电平期间输入端信号变化的影响,所以只需观察第6个脉冲下降沿到来时J K 的状态,便可确定输出.图7 边沿触发J K 触发器波形图通过对SR 触发器、主从SR 触发器、主从J K 触发器、边沿J K 触发器的分析与比较,可以总结出以下方法去分析各触发器输出波形:判别触发方式,由符号或语言描述. 分析在CL K =1或CL K =0期间输入端有无状态变化.套用方法:利用触发器结构图分析法或者套用特性表分析.(下转第14页)11吴凤凰等:触发器三种触发方式的分析与比较大规模更新设备的状况,又能够采用新技术改善现有的电力传输水平及电力系统的安全可靠运行,具有理论和实际意义.参考文献:[1]李浩昱,李霄燕,张福恩.具有能量缓冲的统一潮流控制器及其控制的研究[J].中国电机工程学报,2001,21(7):9-13[2]武守远,周孝信.灵活交流输电系统研究 统一潮流控制器的分析与仿真[J].电网技术,1995,19(4):1-7.[3]何大愚.柔性交流输电技术和用户电力技术的新发展.电力系统自动化[J].1999,23(6):8-13.The Application of Technology on FlexibleTransmission in Controlling Tidal CurrentL I Rong1,YAN G Bei2,YAN G Bin3(1.Department of Elect ron and Electr ic Eng ineering,L anzhou V ocatio nal College o f Pr etor-Chemistr y,L anzho u,730060,China;2.T he Quality T echnolog y Bur eau o f Lanzho u,L anzhou730040,China;3.Department of Industr y,City Colleg e of L anzhou,L anzhou730070,China)Abstract:The techno logy of flexible transmission is one of the new est technolog y,it can control elec-tricity system tide so as to ex er t the potential of the present electricity system.UPFC is the mo st com prehensiv e control up to now,it can contr ol tr ansm issio n param eters like vo ltag e,impedance, phase,w att and var pow er etc.The compare of theo ry analysis and calculation indicates that the tide control ability of flex ible transmissio n device not only lies on the types of device but also has the rela-tion w ith or ig inal natur al po w er.Key words:flex ible transmission;contro lling tidal current(上接第11页)不同触发方式的触发器在有效电平期间,输入端发生状态变化,是学习触发器的重点和难点,通过这种方式进行分析比较,可以加深学生对它的理解,从而掌握各触发器的特点.对后续时序逻辑电路的学习打下了坚实的基础.参考文献:[1]清华大学电子学教研组.数字电子技术基础[M].北京:高等教育出版社,2006.[2]华中科技大学电子技术课程组.电子技术基础[M].北京:高等教育出版社,2006.[3]李云,许柯.数字电路逻辑设计[M].北京:机械工业出版社,2007.[4]董艳峰,田海峰.主从触发器的动作特点及波形分析.甘肃联合大学学报[J].2008,(22)2:50-52.Analysis and Compare for Three Triggered Ways of the Flip-flopW U F eng-huang1,ZH A O J ing2(1.Colleg e o f Science,Nanjing A gr iculture U niv ersity,N anjing210095,China;2.Co llege o f Eng ineer ing T echnolog y,Zheng zhou U niver sity,Zheng zho u450044,China)Abstract:Three trigg ered w ays of the flip-flop w hich are master-slave flip-flop,pulse flip-flo p,edge-tr ig gered flip-flop,is analy zed and co mpared in the paper.When the clock pulse is arriving,the state of the flip-flop has different characteristic.Especially w hen the clock pulse is in the effectual v oltag e, if the input sig nal chang ed m aster-slav e SR flip-flop w ould flip time after time,w hile master-slave JK flip-flop w ould flip o nly o nce.It s necessar y to be master o f the characteristic.Key words:flip-flop;edge-tr ig gered flip-flop;SR flip-flop;JK flip-flop14 甘肃联合大学学报(自然科学版) 第23卷。

一、触发器概述1.基本性质:它有两个稳定的工作状态,一个是“0”态,即输出Q=0,=1;另一个是“1”态,即输出Q=1,=0。

当无外界信号作用时,触发器状态维持不变。

在一定的外界信号作用时,触发器可以从一个稳态翻转到另一个稳态,当外界信号消失后,能保持更新后的状态。

总之,触发器是一种能记忆一位二进制数的存储单元。

由它可以构造计数器、寄存器、移位寄存器等时序逻辑电路。

按结构形式可以分为没有钟控的基本触发器和有钟控的时钟触发器。

按逻辑功能还可以分为RS触发器、D触发器、JK触发器和T触发器。

2.基本RS触发器由两个与非门交叉耦合构成。

逻辑图如图4-1(a)所示,惯用符号如图4-1(b)所示。

工作原理:==1时,不管初态如何,触发器状态将保持不变。

=0,=1时,不管初态如何,门2的输出=1,使门1的输出Q=0,即此时触发器维持“0”态,称为直接置“0”端。

=1,=0时,不管初态如何,门1的输出Q=1,使门2的输出=0,即此时触发器维持“1”态,称为直接置“1”端。

==0时,不管初态如何,两与非门的输出均为“1”,此时的状态称非法状态。

之后,如、变为“1”时,由于翻转速度的差异,触发器的最终状态是无法确定的。

正常工作时不允许出现这种情况。

3.触发器逻辑功能的描述方法通常有功能真值表、特性方程、激励表、状态图及时序图等方法。

功能真值表:以表格的形式反映触发器从初态(接收输入信号前的状态,用表示)向次态(接收输入信号后的状态,用表示)转移的规律,也称状态转移真值表。

特性方程:以表达式的形式反映触发器在输入信号作用下,次态与输入信号初态之间的逻辑关系,它可由真值表推得。

激励表:又称驱动表,用表格的形式反映触发器从一个状态转到另一个状态,所需的输入条件。

可由真值表转换得到,也是真值表的逆关系。

状态图:又称状态转移图。

它是一种以图形的方式描述触发器状态转移与输入信号之间的关系。

它用圆圈表示时序电路的各种状态,用带箭头的直线表示状态转移方向,直线上方表示状态转移的条件。

边沿D触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态岀错。

而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

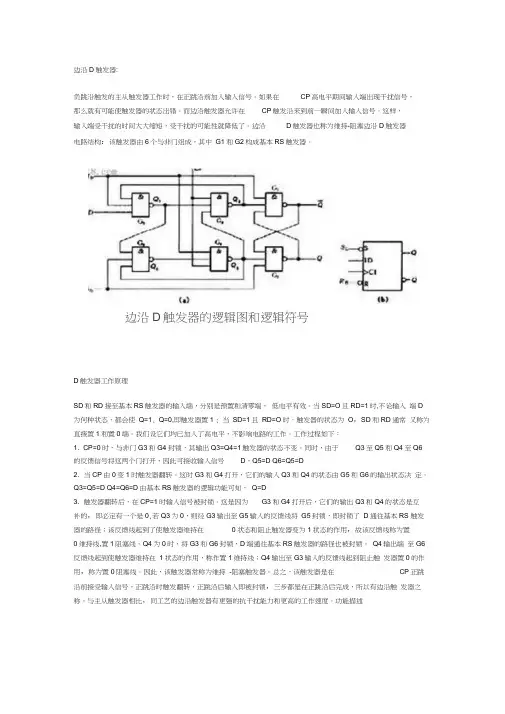

边沿D触发器也称为维持-阻塞边沿D触发器电路结构:该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

边沿D触发器的逻辑图和逻辑符号D触发器工作原理SD和RD接至基本RS触发器的输入端,分别是预置和清零端,低电平有效。

当SD=O且RD=1时,不论输入端D 为何种状态,都会使Q=1, Q=0,即触发器置1 ; 当SD=1且RD=O时,触发器的状态为O,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1. CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D Q6=Q5=D2. 当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D Q4=Q6=D由基本RS触发器的逻辑功能可知,Q=D3. 触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输岀至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

主从触发器与边沿触发器的比较与应用研究触发器是数字电路中常见的重要组件,用于存储和传递信号。

在数

字系统设计中,触发器扮演着重要的角色。

主从触发器和边沿触发器

是两种常见的触发器类型。

本文将对这两种触发器进行比较与应用研究。

一、主从触发器(Master-Slave Flip-Flop)

主从触发器是一种常见的触发器类型,由两个触发器组成:主触发

器(Master Flip-Flop)和从触发器(Slave Flip-Flop)。

主触发器接受

所需的输入信号,从触发器复制主触发器的状态并输出。

主从触发器

通过时钟信号进行同步操作。

1.1 主从触发器的工作原理

主从触发器的工作原理基于时钟信号。

当时钟信号为0时,主触发

器锁定输入信号,并将其传递给从触发器。

而当时钟信号为1时,从

触发器锁定主触发器的状态,并将其输出。

1.2 主从触发器的优点和应用

主从触发器具有以下优点:

- 简单可靠:主从触发器的结构相对简单,易于设计和实现。

- 逻辑精确:主从触发器能够在时钟上升沿或下降沿稳定地改变状态。

- 应用广泛:主从触发器常用于存储器和计数器等数字电路组件中。

二、边沿触发器(Edge-Triggered Flip-Flop)

边沿触发器是另一种常见的触发器类型。

边沿触发器与时钟信号的变化边沿(上升沿或下降沿)相关联。

只有在时钟信号变化边沿到来时,边沿触发器才会读取和存储输入信号。

2.1 边沿触发器的工作原理

边沿触发器的工作原理基于时钟信号的边沿。

当时钟信号发生变化的边沿到来时,边沿触发器读取输入信号并将其状态存储起来。

边沿触发器的状态只在时钟信号边沿到来时发生改变。

2.2 边沿触发器的优点和应用

边沿触发器具有以下优点:

- 灵活性高:边沿触发器能够在时钟信号的任意边沿发生变化时捕获输入信号。

- 无中间状态:边沿触发器的状态仅在时钟信号边沿到来时改变,避免了产生中间状态。

- 应用广泛:边沿触发器常用于处理时序电路和高速存储器等应用中。

三、主从触发器与边沿触发器的比较与应用研究

3.1 响应时间

主从触发器和边沿触发器的响应时间存在差异。

主从触发器需要等待整个时钟周期才能锁定输入信号,而边沿触发器只需要等待时钟信

号变化边沿的到来。

因此,在高速电路设计中,边沿触发器通常更受青睐,因为它的响应速度更快。

3.2 中间状态

主从触发器在时钟信号发生变化时,主触发器和从触发器之间会存在中间状态,可能会导致不稳定的输出结果。

而边沿触发器通过时钟信号变化边沿来触发状态转换,不会产生中间状态,输出更为稳定。

3.3 应用场景

主从触发器常用于需要精确控制信号状态的场景,如计数器和状态机。

边沿触发器适用于高速电路和时序电路设计,如存储器和通信接口。

综上所述,主从触发器和边沿触发器都在数字系统设计中扮演着重要的角色。

主从触发器用于需要控制信号状态的场景,而边沿触发器适用于高速和时序要求较高的电路设计。

在实际应用中,根据具体需求和设计要求,选择合适的触发器类型能够更好地满足设计目标。