主从型RS触发器

- 格式:doc

- 大小:39.50 KB

- 文档页数:3

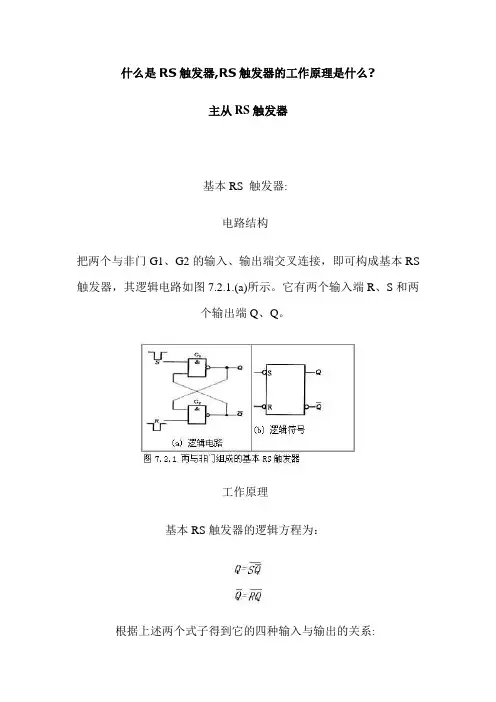

什么是RS触发器,RS触发器的工作原理是什么?主从RS触发器基本RS 触发器:电路结构把两个与非门G1、G2的输入、输出端交叉连接,即可构成基本RS 触发器,其逻辑电路如图7.2.1.(a)所示。

它有两个输入端R、S和两个输出端Q、Q。

工作原理基本RS触发器的逻辑方程为:根据上述两个式子得到它的四种输入与输出的关系:1.当R=1、S=0时,则Q=0,Q=1,触发器置1。

2.当R=0、S=1时,则Q=1,Q=0,触发器置0。

如上所述,当触发器的两个输入端加入不同逻辑电平时,它的两个输出端Q和Q有两种互补的稳定状态。

一般规定触发器Q端的状态作为触发器的状态。

通常称触发器处于某种状态,实际是指它的Q端的状态。

Q=1、Q=0时,称触发器处于1态,反之触发器处于0态。

S=0,R=1使触发器置1,或称置位。

因置位的决定条件是S=0,故称S 端为置1端。

R=0,S=1时,使触发器置0,或称复位。

同理,称R端为置0端或复位端。

若触发器原来为1态,欲使之变为0态,必须令R端的电平由1变0,S端的电平由0变1。

这里所加的输入信号(低电平)称为触发信号,由它们导致的转换过程称为翻转。

由于这里的触发信号是电平,因此这种触发器称为电平控制触发器。

从功能方面看,它只能在S和R的作用下置0和置1,所以又称为置0置1触发器,或称为置位复位触发器。

其逻辑符号如图7.2. 1(b)所示。

由于置0或置1都是触发信号低电平有效,因此,S端和R端都画有小圆圈。

3.当R=S=1时,触发器状态保持不变。

触发器保持状态时,输入端都加非有效电平(高电平),需要触发翻转时,要求在某一输入端加一负脉冲,例如在S端加负脉冲使触发器置1,该脉冲信号回到高电平后,触发器仍维持1状态不变,相当于把S端某一时刻的电平信号存储起来,这体现了触发器具有记忆功能。

4.当R=S=0时,触发器状态不确定在此条件下,两个与非门的输出端Q和Q全为1,在两个输入信号都同时撤去(回到1)后,由于两个与非门的延迟时间无法确定,触发器的状态不能确定是1还是0,因此称这种情况为不定状态,这种情况应当避免。

主从RS触发器

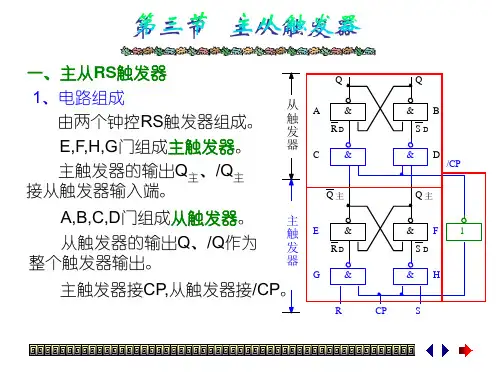

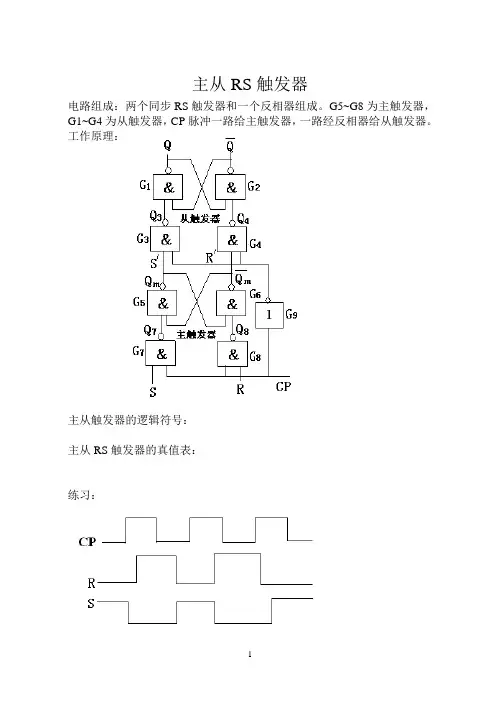

电路组成:两个同步RS触发器和一个反相器组成。

G5~G8为主触发器,G1~G4为从触发器,CP脉冲一路给主触发器,一路经反相器给从触发器。

工作原理:

主从触发器的逻辑符号:

主从RS触发器的真值表:

练习:

主从JK触发器

电路组成:将主从RS触发器的Q端和Q端反馈到G7、G8的输入端,并将S端改称为J端,R端改为K端,即构成主从JK触发器。

工作原理:

JK触发器的符号:

JK触发器真值表:

练习:图为JK触发器的逻辑图,请根据CP、J、K的波形,画出输出波形。

设初始状态为0.

请根据下图波形,画出下降沿有效和上升沿有效时的输出波形

D触发器

1、D触发器的逻辑符号

2、逻辑功能

3、真值表

4、时序图(设下降沿有效)

如果上升沿有效。

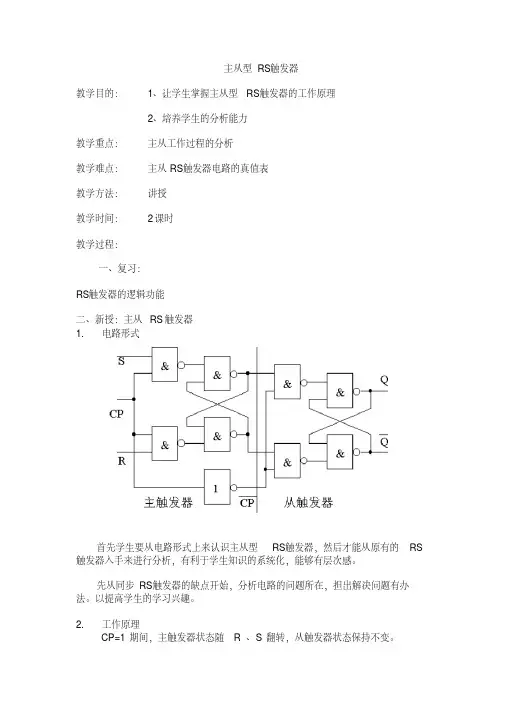

主从型RS触发器教学目的:1、让学生掌握主从型RS触发器的工作原理2、培养学生的分析能力教学重点:主从工作过程的分析教学难点:主从RS触发器电路的真值表教学方法:讲授教学时间:2课时教学过程:一、复习:RS触发器的逻辑功能二、新授:主从RS触发器1. 电路形式首先学生要从电路形式上来认识主从型RS触发器,然后才能从原有的RS 触发器入手来进行分析,有利于学生知识的系统化,能够有层次感。

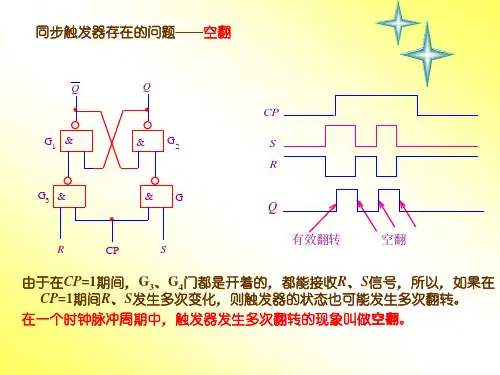

先从同步RS触发器的缺点开始,分析电路的问题所在,担出解决问题有办法。

以提高学生的学习兴趣。

2. 工作原理CP=1期间,主触发器状态随R 、S翻转,从触发器状态保持不变。

CP从1变成0时,从触发器的状态随此时主触发器状态翻转。

CP=0期间,主触发器和从触发器状态均保持不变。

因此,主从RS触发器是一个边沿触发器然后由工作原理推出真值表。

以利于学生有序的掌握知识。

由于电路的结构比较复杂,学生在平时使用的过程在中会有较多的不便,故引出主从型RS触发器的逻辑符号,以便在平时画图时使用。

3. 功能表、表达式和逻辑符号真值表不能够死记硬背,要讲究机巧,这里要引用RS触发器的规则,这里是输入高电平有效,只有当输入有一个为1时,输出才可能发生变化,当RS为00时则输出不变。

当两个现时有效时则输出不能确定。

由于R像0则当RS为10时则输出为0,又由于S像1,则当RS输入为01时,则输出为1。

这样学生就会较深的记住主从型RS触发器的真值表了。

又能够让学生区分同步RS触发器的逻辑功能。

4. 波形图主从RS触发器的状态只在时钟信号的下降沿翻转,抗干扰能力较强!克服了同步RS触发器发生空翻的缺点。

作业:1、画出主从型RS触发器的逻辑电路与逻辑符号。

2、分析主从型RS触发器的工作原理。

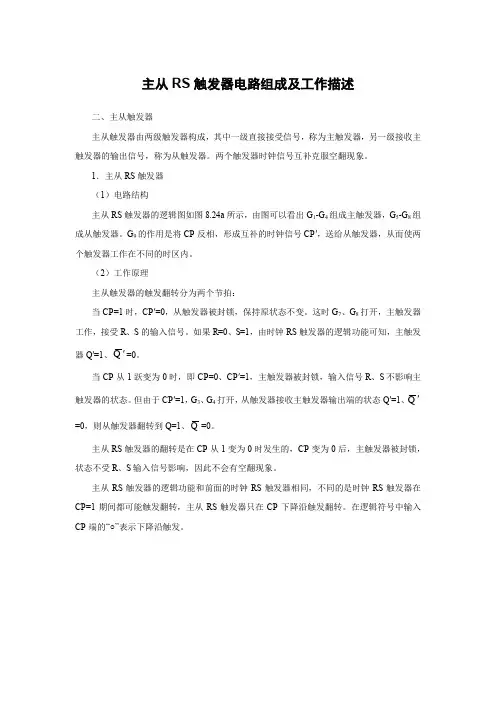

主从RS触发器电路组成及工作描述二、主从触发器主从触发器由两级触发器构成,其中一级直接接受信号,称为主触发器,另一级接收主触发器的输出信号,称为从触发器。

两个触发器时钟信号互补克服空翻现象。

1.主从RS触发器(1)电路结构主从RS触发器的逻辑图如图8.24a所示,由图可以看出G1-G4组成主触发器,G5-G8组成从触发器。

G9的作用是将CP反相,形成互补的时钟信号CP′,送给从触发器,从而使两个触发器工作在不同的时区内。

(2)工作原理主从触发器的触发翻转分为两个节拍:当CP=1时,CP′=0,从触发器被封锁,保持原状态不变。

这时G7、G8打开,主触发器工作,接受R、S的输入信号。

如果R=0、S=1,由时钟RS触发器的逻辑功能可知,主触发器Q′=1、Q'=0。

当CP从1跃变为0时,即CP=0、CP′=1,主触发器被封锁,输入信号R、S不影响主触发器的状态。

但由于CP′=1,G3、G4打开,从触发器接收主触发器输出端的状态Q′=1、Q' =0,则从触发器翻转到Q=1、Q=0。

主从RS触发器的翻转是在CP从1变为0时发生的,CP变为0后,主触发器被封锁,状态不受R、S输入信号影响,因此不会有空翻现象。

主从RS触发器的逻辑功能和前面的时钟RS触发器相同,不同的是时钟RS触发器在CP=1期间都可能触发翻转,主从RS触发器只在CP下降沿触发翻转。

在逻辑符号中输入CP端的“○”表示下降沿触发。

Q9(a)电路结构(b)逻辑符号图8.24 主从RS触发器2.主从JK触发器(1)电路结构主从JK触发器电路是在主从RS触发器基础上引两条反馈线:Q反馈到R端,Q反馈到S端,外加信号从J、K输入。

如图8.25a所示。

(2)工作原理当CP=1时,CP′=0,从触发器被封锁,保持原状态不变。

主触发器的状态由输入端J、K的信号和从触发器状态来决定。

当CP从1跃变为0时,即CP=0,主触发器被封锁,但由于CP′=1,从触发器接收主触发器输出端的状态。

rs主从触发器原理RS主从触发器原理引言:RS主从触发器是一种基本的数字电路元件,常用于时序电路中。

它在计算机内存中起着重要的作用,用于存储和传输数据。

本文将介绍RS主从触发器的原理及其工作方式。

一、什么是RS主从触发器RS主从触发器是由两个互补反馈的逻辑门组成的电路元件。

它由两个触发器构成,一个是主触发器,一个是从触发器。

主触发器用于存储输入信号,从触发器用于传输输出信号。

RS主从触发器可以存储一位二进制数据,并在时钟信号的控制下进行数据传输。

二、RS主从触发器的原理RS主从触发器的原理基于逻辑门的工作原理。

它由两个与非门(NOR)组成。

其中,一个与非门的输出连接到另一个与非门的输入,形成互相反馈的电路。

这种反馈机制使得RS主从触发器可以存储和传输数据。

三、RS主从触发器的工作方式1. 重置状态(Reset):当RS主从触发器的R(Reset)输入为1,S (Set)输入为0时,主触发器的输出Q为0,从触发器的输出Q'为1。

这种状态下,RS主从触发器被重置,输出为逻辑低电平。

2. 设置状态(Set):当RS主从触发器的R输入为0,S输入为1时,主触发器的输出Q为1,从触发器的输出Q'为0。

这种状态下,RS 主从触发器被设置,输出为逻辑高电平。

3. 禁用状态(Hold):当RS主从触发器的R和S输入都为0时,主触发器和从触发器的状态不变,保持之前存储的数据。

4. 非法状态(Illegal):当RS主从触发器的R和S输入都为1时,主触发器和从触发器的状态将无法确定,处于非法状态。

四、RS主从触发器的应用RS主从触发器常用于时序电路中,用于存储和传输数据。

它可以作为计数器、寄存器、状态机等电路的关键组成部分。

在计算机内存中,RS主从触发器被广泛应用,用于存储和读取数据。

五、RS主从触发器的优缺点1. 优点:RS主从触发器结构简单,易于设计和实现;可以存储一位二进制数据,并在时钟信号的控制下进行数据传输。

课程设计任务书学生姓名:王志强专业班级:电子1101班指导教师:刘金根工作单位:信息工程学院题目: 主从RS触发器电路设计初始条件:计算机、ORCAD软件、L-EDIT软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:2周2、技术要求:(1)学习ORCAD软件、L-EDIT软件。

(2)设计一个CMOS四输入与非门电路。

(3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.28-12.5对主从RS触发器电路进行设计仿真工作,完成课设报告的撰写。

2013.12.6 提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日摘要 (1)1 绪论 (2)2 设计内容及要求 (3)2.1 设计的目的及主要任务 (3)2.2 设计思想 (3)3软件介绍 (4)3.1 OrCAD简介 (4)3.2 L-Edit简介 (5)4 主从RS触发器电路介绍 (6)4.1 主从RS触发器的组成 (6)4.2 主从RS触发器电路真值表 (7)5 Cadence中主从RS触发器电路的设计 (8)5.1 主从RS电路原理图的绘制 (8)5.2 主从RS触发器电路的仿真 (9)6 L-EDIT中主从RS触发器电路版图的设计 (11)6.1 版图设计的基本知识 (11)6.2 与非门的绘制 (12)6.3主从RS触发器版图设计 (14)7课程设计总结 (15)参考文献 (16)主从RS触发器由两个同样的同步RS触发器组成,本文详细介绍了主从RS触发器电路设计仿真及版图布局设计验证。

课程设计任务书学生姓名:王志强专业班级:电子1101班指导教师:刘金根工作单位:信息工程学院题目: 主从RS触发器电路设计初始条件:计算机、ORCAD软件、L-EDIT软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:2周2、技术要求:(1)学习ORCAD软件、L-EDIT软件。

(2)设计一个CMOS四输入与非门电路。

(3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.28-12.5对主从RS触发器电路进行设计仿真工作,完成课设报告的撰写。

2013.12.6 提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日摘要 (1)1 绪论 (2)2 设计内容及要求 (3)2.1 设计的目的及主要任务 (3)2.2 设计思想 (3)3软件介绍 (4)3.1 OrCAD简介 (4)3.2 L-Edit简介 (5)4 主从RS触发器电路介绍 (6)4.1 主从RS触发器的组成 (6)4.2 主从RS触发器电路真值表 (7)5 Cadence中主从RS触发器电路的设计 (8)5.1 主从RS电路原理图的绘制 (8)5.2 主从RS触发器电路的仿真 (9)6 L-EDIT中主从RS触发器电路版图的设计 (11)6.1 版图设计的基本知识 (11)6.2 与非门的绘制 (12)6.3主从RS触发器版图设计 (14)7课程设计总结 (15)参考文献 (16)主从RS触发器由两个同样的同步RS触发器组成,本文详细介绍了主从RS触发器电路设计仿真及版图布局设计验证。

主从型RS触发器

教学目的:1、让学生掌握主从型RS触发器的工作原理

2、培养学生的分析能力

教学重点:主从工作过程的分析

教学难点:主从RS触发器电路的真值表

教学方法:讲授

教学时间:2课时

教学过程:

一、复习:

RS触发器的逻辑功能

二、新授:主从RS触发器

1. 电路形式

首先学生要从电路形式上来认识主从型RS触发器,然后才能从原有的RS 触发器入手来进行分析,有利于学生知识的系统化,能够有层次感。

先从同步RS触发器的缺点开始,分析电路的问题所在,担出解决问题有办法。

以提高学生的学习兴趣。

2. 工作原理

CP=1期间,主触发器状态随R 、S翻转,从触发器状态保持不变。

CP从1变成0时,从触发器的状态随此时主触发器状态翻转。

CP=0期间,主触发器和从触发器状态均保持不变。

因此,主从RS触发器是一个边沿触发器

然后由工作原理推出真值表。

以利于学生有序的掌握知识。

由于电路的结构比较复杂,学生在平时使用的过程在中会有较多的不便,故引出主从型RS触发器的逻辑符号,以便在平时画图时使用。

3. 功能表、表达式和逻辑符号

真值表不能够死记硬背,要讲究机巧,这里要引用RS触发器的规则,这里是输入高电平有效,只有当输入有一个为1时,输出才可能发生变化,当RS为00时则输出不变。

当两个现时有效时则输出不能确定。

由于R像0则当RS为10时则输出为0,又由于S像1,则当RS输入为01时,则输出为1。

这样学生就会较深的记住主从型RS触发器的真值表了。

又能够让学生区分同步RS触发器的逻辑功能。

4. 波形图

主从RS触发器的状态只在时钟信号的下降沿翻转,抗干扰能力较强!克服

了同步RS触发器发生空翻的缺点。

作业:

1、画出主从型RS触发器的逻辑电路与逻辑符号。

2、分析主从型RS触发器的工作原理。