D触发器原理-D触发器电路图

- 格式:doc

- 大小:26.50 KB

- 文档页数:4

d触发器逻辑电路介绍d触发器是数字电路中常用的组合逻辑电路。

它具有存储功能,可以通过时钟信号来控制数据的传输和存储。

在本文中,我们将深入探讨d触发器的工作原理和应用场景。

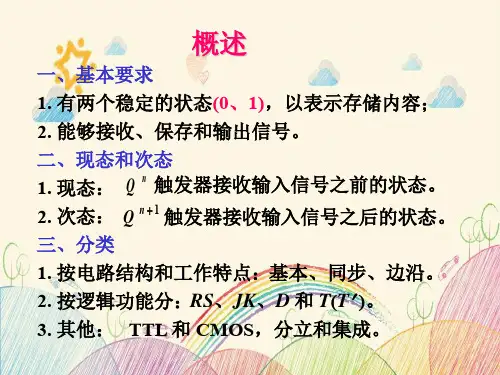

基本原理d触发器是一种双稳态触发器,它可以存储1位的数据。

它由两个与门和两个非门组成。

d触发器有两个输入端:时钟(CLK)和数据(D),以及两个输出端:输出(Q)和非输出(Q’)。

当时钟信号为高电平(正脉冲)时,d触发器的输出Q将根据数据输入D的值进行改变。

如果D为高电平,则Q也为高电平;如果D为低电平,则Q为低电平。

在时钟信号为低电平(负脉冲)时,d触发器的输出将被保持在上一次时钟信号为高电平时的状态。

工作原理下面是d触发器的逻辑电路图:_____D _____| |____ Q| d' |CLK ___|_____|根据上图,我们可以看到当CLK为高电平时,d触发器的输出Q将受到D的值的控制。

具体来说,当CLK为高电平时,两个与门的输出取决于D和d’的值。

如果D 为高电平,d’为低电平,则Q为高电平;如果D为低电平,d’为高电平,则Q为低电平。

当CLK为低电平时,与门的输出被锁存,Q的状态保持不变。

应用场景d触发器在数字电路中有着广泛的应用,特别是在时序电路中。

以下是一些常见的应用场景:1. 时序电路设计d触发器可以用于设计各种时序电路,如计数器、移位寄存器、时钟分频器等。

通过合理使用时钟信号和数据输入D,我们可以实现不同的功能,实现更复杂的计算和控制。

2. 数据存储和同步d触发器可以用作数据存储器件,可以存储和传递数据信号。

通过时钟信号的控制,我们可以实现数据的同步传输,并且确保数据在传输过程中的稳定性。

3. 状态机设计d触发器的状态保持特性使其成为状态机设计中的重要组成部分。

通过合理使用d触发器和其他逻辑门,我们可以实现复杂的状态转换和状态控制逻辑。

4. 内存设计在计算机系统中,d触发器可以被用于构建存储器单元(如SRAM),用于存储和处理数据。

维持阻塞D 触发器电路结构及工作原理描述边沿触发器只是在CP 的某一边沿(上升沿或下降沿)时刻才能对所作用的输入信号产生响应,即只有在CP 边沿时输入信号才有效(输出状态与输入有关),而其他时间触发器都处于保持状态。

可见,这种触发器不会有空翻现象,并且抗干扰能力增强,工作更可靠。

边沿触发器有上升沿触发和下降沿触发两种。

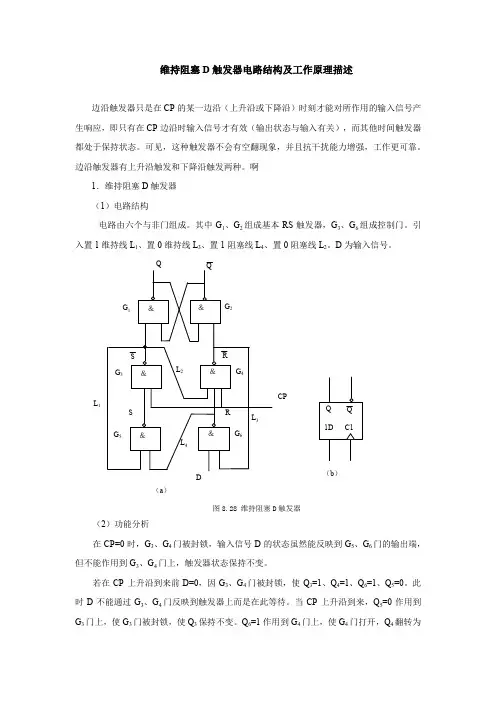

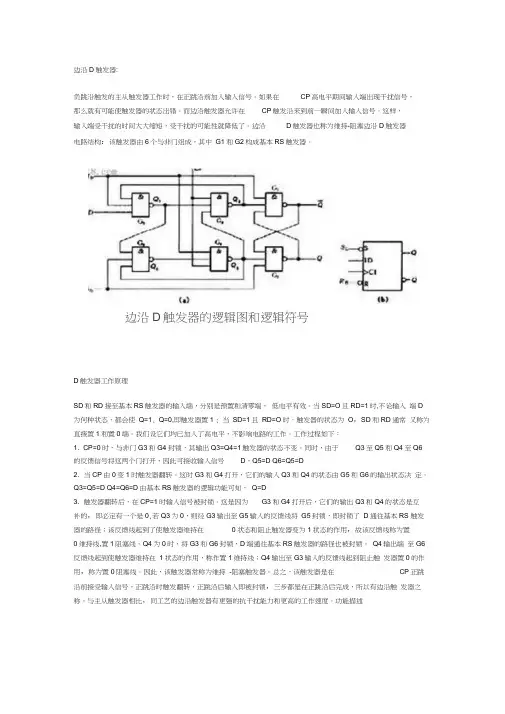

啊1.维持阻塞D 触发器 (1)电路结构电路由六个与非门组成。

其中G 1、G 2组成基本RS 触发器,G 3、G 6组成控制门。

引入置1维持线L 1、置0维持线L 3、置1阻塞线L 4、置0阻塞线L 2。

D 为输入信号。

图8.28 维持阻塞D 触发器(2)功能分析在CP =0时,G 3、G 4门被封锁,输入信号D 的状态虽然能反映到G 5、G 6门的输出端,但不能作用到G 3、G 4门上,触发器状态保持不变。

若在CP 上升沿到来前D =0,因G 3、G 4门被封锁,使Q 3=1、Q 4=1、Q 6=1、Q 5=0。

此时D 不能通过G 3、G 4门反映到触发器上而是在此等待。

当CP 上升沿到来,Q 5=0作用到G 3门上,使G 3门被封锁,使Q 3保持不变。

Q 6=1作用到G 4门上,使G 4门打开,Q 4翻转为QQDCP(a )L 1(b )0,使触发器输出Q=0、Q=1。

无论CP上升沿到来前触发器状态如何,只要D=0,但CP 上升沿到来后,触发器状态变为0。

同时Q4=0通过置0维持线L3反馈到G6门的输入端,将G6门封锁,即在CP=1期间,无论D如何变化,触发器状态保持0不变。

若在CP上升沿到来前D=1,因G3、G4门被封锁,使Q3=1、Q4=1、Q6=0、Q5=1。

此时Q6、Q5的状态不能通过G3、G4门反映到触发器上。

触发器保持原状态。

当CP上升沿到来,Q6、Q5的状态反映到触发器上,Q6=0,G4门被封锁,使Q4保持不变。

Q3翻转为0,使触发器输出Q=1、Q=0。

无论CP上升沿到来前触发器状态如何,只要D=1,CP上升沿到来后,触发器状态变为1。

边沿D 触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

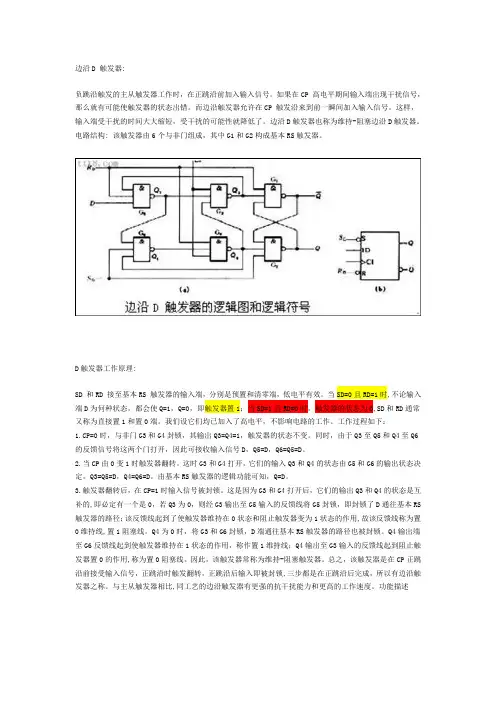

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

D触发器工作原理:SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。

D触发器工作原理引言概述:D触发器是数字电路中常用的一种触发器,它具有简单的结构和稳定的工作性能。

本文将详细介绍D触发器的工作原理,包括其基本概念、内部结构、输入输出特性以及应用领域。

正文内容:1. D触发器的基本概念1.1 D触发器是一种时序电路,它根据时钟信号和输入信号的状态变化来控制输出信号的变化。

1.2 D触发器的输入端包括数据输入端(D)、时钟输入端(CK)和复位输入端(Reset),输出端为输出端(Q)和输出端(Q')。

1.3 D触发器的输出状态取决于时钟信号的上升沿或者下降沿以及输入信号的状态。

2. D触发器的内部结构2.1 D触发器内部包含两个互补的锁存器,分别为正相锁存器和负相锁存器。

2.2 正相锁存器和负相锁存器之间通过与门和非门相连,形成为了D触发器的内部逻辑电路。

2.3 时钟信号通过与门和非门的控制,使得D触发器在时钟信号的上升沿或者下降沿时,将输入信号的状态锁存到输出端。

3. D触发器的输入输出特性3.1 当时钟信号为低电平时,D触发器处于保持状态,即输出端保持原来的状态。

3.2 当时钟信号为上升沿或者下降沿时,D触发器根据输入信号的状态来更新输出状态。

3.3 当时钟信号为高电平时,D触发器处于禁止状态,即不接受输入信号的变化。

4. D触发器的应用领域4.1 D触发器常用于数字系统中的时序电路设计,如计数器、移位寄存器等。

4.2 D触发器也可以用于存储数据,实现数据的暂存和传输。

4.3 在数字通信系统中,D触发器可以用于时钟同步和数据传输控制。

总结:综上所述,D触发器是一种常用的数字电路元件,具有简单的结构和稳定的工作性能。

它通过时钟信号和输入信号的状态变化来控制输出信号的变化。

D触发器的内部结构包括正相锁存器和负相锁存器,通过与门和非门的控制实现输入信号的锁存。

D触发器的应用广泛,常用于时序电路设计和数据存储传输等领域。

通过深入了解D触发器的工作原理,我们可以更好地应用它来解决实际问题。

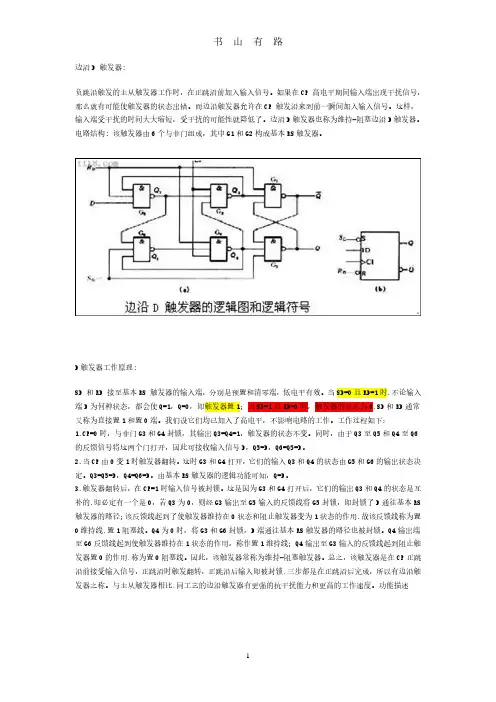

边沿D触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态岀错。

而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器电路结构:该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

边沿D触发器的逻辑图和逻辑符号D触发器工作原理SD和RD接至基本RS触发器的输入端,分别是预置和清零端,低电平有效。

当SD=O且RD=1时,不论输入端D 为何种状态,都会使Q=1, Q=0,即触发器置1 ; 当SD=1且RD=O时,触发器的状态为O,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1. CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D Q6=Q5=D2. 当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D Q4=Q6=D由基本RS触发器的逻辑功能可知,Q=D3. 触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输岀至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

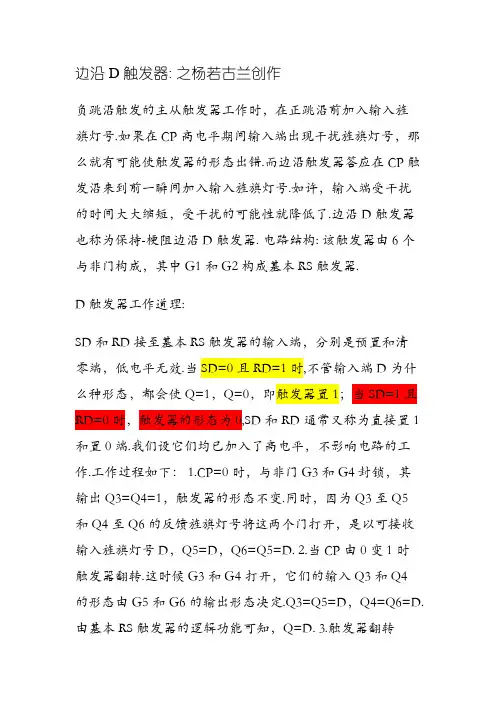

边沿D 触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

D触发器工作原理:SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。

边沿D 触发器: 之杨若古兰创作负跳沿触发的主从触发器工作时,在正跳沿前加入输入旌旗灯号.如果在CP 高电平期间输入端出现干扰旌旗灯号,那么就有可能使触发器的形态出错.而边沿触发器答应在CP 触发沿来到前一瞬间加入输入旌旗灯号.如许,输入端受干扰的时间大大缩短,受干扰的可能性就降低了.边沿D触发器也称为保持-梗阻边沿D触发器. 电路结构: 该触发器由6个与非门构成,其中G1和G2构成基本RS触发器.D触发器工作道理:SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平无效.当SD=0且RD=1时,不管输入端D为什么种形态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的形态为0,SD和RD通常又称为直接置1和置0端.我们设它们均已加入了高电平,不影响电路的工作.工作过程如下: 1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的形态不变.同时,因为Q3至Q5和Q4至Q6的反馈旌旗灯号将这两个门打开,是以可接收输入旌旗灯号D,Q5=D,Q6=Q5=D. 2.当CP由0变1时触发器翻转.这时候G3和G4打开,它们的输入Q3和Q4的形态由G5和G6的输出形态决定.Q3=Q5=D,Q4=Q6=D.由基本RS触发器的逻辑功能可知,Q=D. 3.触发器翻转后,在CP=1时输入旌旗灯号被封锁.这是因为G3和G4打开后,它们的输出Q3和Q4的形态是互补的,即肯定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器保持在0形态和禁止触发器变成1形态的感化,故该反馈线称为置0保持线,置1梗阻线.Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁.Q4输出端至G6反馈线起到使触发器保持在1形态的感化,称作置1保持线;Q4输出至G3输入的反馈线起到禁止触发器置0的感化,称为置0梗阻线.是以,该触发器常称为保持-梗阻触发器.总之,该触发器是在CP正跳沿前接受输入旌旗灯号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称.与主从触发器比拟,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度.功能描述2.特征方程 Qn+1=D3形态转移图脉冲特性: 1.建立时间:由下图保持梗阻触发器的电路可见,CP 旌旗灯号是加到门G3和G4上的,因此在CP上升沿到达之前门G5和G6输出端的形态必须波动地建立起来.输入旌旗灯号到达D端当前,要经过一级门电路的传输延迟时间G5的输出形态才干建立起来,而G6的输出形态须要经过两级门电路的传输延迟时间才干建立,是以D端的输入旌旗灯号必须先于CP的上升沿到达,而且建立时间应满足: tset≥2tpd. 2.坚持时间:由下图可知,为实现边沿触发,应包管CP=1期间门G6的输出形态不变,不受D端形态变更的影响.为此,在D=0的情况下,当CP上升沿到达当前还要等门G4输出的低电平返回到门G6的输入端当前,D端的低电平才答应改变.是以输入低电平旌旗灯号的坚持时间为tHL≥tpd.在 D=1的情况下,因为CP上升沿到达后G3的输出将G4封锁,所以不请求输入旌旗灯号继续坚持不变,故输入高电平旌旗灯号的坚持时间tHH=0. 3.传输延迟时间:由图工作波形图不难推算出,从CP上升沿到达时开始计算,输出由高电平变成低电平的传输延迟时间tPHL和由低电平变成高电平的传输延迟时间tPLH分别是:tPHL=3tpd tPLH=2tpd保持和梗阻D触发器的电路和动态波形4.最高时钟频率:为包管由门G1~G4构成的同步RS触发器能可靠地翻转,CP高电平的持续时间应大于 tPHL,时钟旌旗灯号高电平的宽度tWH应大于tPHL.而为了鄙人一个CP上升沿到达之前确保门G5和G6新的输出电平得以波动地建立,CP低电平的持续时间不该小于门G4的传输延迟时间和tset之和,即时钟旌旗灯号低电平的宽度tWL≥tset+tpd,是以得到:在实际集成触发器中,每个门传输时间是分歧的,而且作了分歧方式的简化,是以上面讨论的结果只是一些定性的物理概念.其真实参数由实验测定. 综上所述,对边沿D触发器归纳为以下几点: 1.边沿D触发器具有接收并记忆旌旗灯号的功能,又称为锁存器;2.边沿D触发器属于脉冲触发方式;3.边沿D触发器不存在束缚条件和一次变更景象,抗干扰功能好,工作速度快。

d触发器作业原理及脉冲特性作业原理批改SD和RD接至底子RS触发器的输入端,它们别离是预置和清零端,低电平有用。

当SD=1且RD=0时(SD的非为0,RD的非为1,即在两个操控端口别离从外部输入的电平值,要素是低电平有用),不管输入端D为何种状况,都会使Q=0,Q非=1,即触发器置0;当SD=0且RD=1(SD的非为1,RD的非为0)时,Q=1,Q非=0,触发器置1,SD和RD一般又称为直接置1和置0端。

咱们设它们均已参加了高电平,不影响电路的作业。

作业进程如下:1.CP=0时,与非门G3和G4封闭,其输出Q3=Q4=1,触发器的状况不变。

一同,因为Q3至Q5和Q4至Q6的反响信号将这两个门翻开,因而可接纳输入信号D,Q5=D,Q6=Q5非=D非。

2.当CP 由0变1时触发器翻转。

这时G3和G4翻开,它们的输入Q3和Q4的状况由G5和G6的输出状况抉择。

Q3=Q5非=D非,Q4=Q6非=D。

由底子RS触发器的逻辑功用可知,Q=Q3非=D触发器原理D。

3.触发器翻转后,在CP=1时输入信号被封闭。

这是因为G3和G4翻开后,它们的输出Q3和Q4的状况是互补的,即一定有一个是0,若Q3为0,则经G3输出至G5输入的反响线将G5封闭,即封闭了D通往底子RS触发器的途径;该反响线起到了使触发器坚持在1状况和阻遏触发器变为0状况的效果,故该反响线称为置1坚持线,置0堵塞线。

Q4为0时,将G3和G6封闭,D端通往底子RS触发器的途径也被封闭。

Q4输出端至G6反响线起到使触发器坚持在0状况的效果,称作置0坚持线;Q4输出至G3输入的反响线起到阻遏触发器置1的效果,称为置1堵塞线。

因而,该触发器常称为坚持-堵塞触发器。

总归,该触发器是在CP正跳沿前承受输入信号,正跳沿时触发翻转,正跳沿后输入即被封闭,三步都是在正跳沿后结束,所以有边际触发器之称。

与主从触发器比照,同技能的边际触发器有更强的抗搅扰才干和更高的作业速度。

d触发器的原理简述和应用1. d触发器的原理简述d触发器是数字电路中常用的触发器类型之一,它是一种单稳态触发器,可以在时钟信号的上升或下降沿触发的情况下,根据数据输入信号的状态来改变输出的状态。

1.1 d触发器的基本结构d触发器由两个输入端(数据输入端d和时钟输入端clk)和两个输出端(输出端q和反相输出端q’)组成。

其基本结构如下:_________| |--|d |--| |--| q |----| |--| clk |--| |--| q' |--|_________|1.2 d触发器的工作原理当时钟信号clk变化时,根据d端的输入信号确定q端和q’端的输出状态。

具体的状态转换规则如下:•当时钟信号clk的边沿(上升沿或下降沿)到来时,若d端输入为低电平(0),则q端输出为低电平(0),q’端输出为高电平(1)。

•当时钟信号clk的边沿到来时,若d端输入为高电平(1),则q端输出为高电平(1),q’端输出为低电平(0)。

2. d触发器的应用d触发器由于其特性和性能优势,在数字电路设计中得到广泛应用。

以下是d 触发器常见的应用场景:2.1 同步时序电路d触发器可以用于同步时序电路中,实现数据的暂存和延时功能。

通过将数据输入信号与时钟信号相接,当时钟信号到来时,输入信号的状态被暂存到d触发器中,随后输出到后续电路中。

这种设计方式可以有效解决时序电路中的数据竞争和冲突问题,提高电路的稳定性和可靠性。

2.2 计数器d触发器还可以组成计数器电路。

通过将多个d触发器串联连接,并将上一个触发器的输出连接到下一个触发器的时钟输入端,就可以实现一个多位二进制计数器。

在计数器电路中,每个触发器的输出与时钟信号相连,当时钟信号边沿到来时,触发器按照一定的规律进行状态转换,从而实现计数功能。

2.3 状态机d触发器还可以用于实现状态机。

状态机是一种非常常见的逻辑电路,可以按照预定的状态序列完成特定的功能。

通过适当地设置和连接多个d触发器,可以实现复杂的状态转换,从而实现更高级的功能。

D触发器工作原理D触发器是数字电路中常用的一种触发器,用于存储和传输数字信号。

它由两个互补反相的输出端和一个输入端组成。

D触发器的工作原理是根据输入信号的变化来改变输出信号的状态。

D触发器有两种常见的类型:D型正沿触发器和D型负沿触发器。

这两种类型的触发器在输入信号的边沿上触发输出信号的变化。

D型正沿触发器在输入信号的上升沿触发输出信号的变化,而D型负沿触发器在输入信号的下降沿触发输出信号的变化。

D触发器的工作原理可以简单描述如下:1. D触发器的输入端被连接到输入信号源,该信号源可以是一个逻辑门、一个计数器或者其他数字电路的输出端。

2. 当输入信号发生变化时,D触发器会根据触发器的类型,在输入信号的边沿上触发输出信号的变化。

3. 当输入信号发生变化时,D触发器的输出端会根据触发器的类型和输入信号的变化,改变其输出状态。

4. D触发器的输出状态可以保持不变,直到下一个输入信号的边沿触发输出信号的变化。

D触发器的工作原理可以通过以下示意图来说明:```_______D ----| || D |----- QCLK ---| 触 || 发 |----- Q'| 器 ||_______|```在上述示意图中,D表示输入信号,CLK表示时钟信号,Q表示输出信号,Q'表示输出信号的补码。

D触发器的工作原理可以进一步解释如下:- 当时钟信号CLK的边沿触发D触发器时,如果D触发器为D型正沿触发器,则在CLK的上升沿时,D触发器会将输入信号D的值传递到输出信号Q上,并将Q'的值设置为Q的补码。

- 当时钟信号CLK的边沿触发D触发器时,如果D触发器为D型负沿触发器,则在CLK的下降沿时,D触发器会将输入信号D的值传递到输出信号Q上,并将Q'的值设置为Q的补码。

D触发器的工作原理使得它在数字电路中具有重要的应用。

例如,D触发器可以用于存储和传输数据,实现计数器和寄存器等功能。

此外,D触发器还可以用于时序电路中,用于控制和同步数字信号的传输和处理。

同步D 触发器电路结构、功能表述分析

同步RS 触发器的R 经过一个非门与S 相接,形成了只有一个输入端的D 触发器。

其电路构成如图8.13所示,它只有一个触发输入端D 和一个时钟CP 输入端。

时钟D 触发器有效解决了时钟RS 触发器R 、S 之间的约束问题。

D CP

(a)同步D 触发器电路 (b )逻辑符号

图8.13 同步D 触发器

1.功能分析

当CP =0时,D 触发器保持原状态不变。

当CP =1时,如果D =0,无论原状态为0或为1,D 触发器均输出0;如果D =1,无论原状态为0或为1,D 触发器均输出1。

2.功能表示方法 (1)功能表

D 触发器的功能表如表8.4。

表8.4 D 触发器的功能表

(2)特征方程

由功能表可得到D 触发器在CP =1时的特征方程:

Q

G

Q

G 3

G4

D Q n =+1

(3)状态转换图

D 触发器状态转换图如图8.14所示。

图8.14 D 触发器状态转换图

(4)波形图

如果已知CP 和D 的波形,则可画出D 触发器的波形图,图8.15为D 触发器的波形图。

设触发器初始状态为0。

图8.15 D 触发器的波形图

CP D

Q

1

1。

基于 CMOS 的 D 触发器的设计一、设计目的:1、进一步熟悉cadence软件的使用;2、掌握cadence的原理图编辑及修改方法;3、掌握cadence前仿的参数设置和方法;4、掌握D触发器的功耗、截止频率和瞬态仿真。

二、设计和原理:触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元。

D触发器在CLK 有效电平期间将D的状态输出。

用CMOS 做器件是集成电路的发展方向。

本次实验设计是用MOS 器件设计一个D触发器。

通过D触发器的功能设计电路图,再转换为MOS 器件的电路。

设计主要是根据D触发器的特性来设计的。

根据它的特性表画原理图D触发器的功能表如下;当CLK = 1 时触发器的Q*=D;当CLK = 0,触发器将保持不变,即Q*=Q。

D触发器的原理图:和主要参数:三、设计仿真:1、瞬态仿真①放参数设置②仿真结果2、功耗仿真①电流波形②平均电流值③功耗 P=U*I=1.8V*1.2094E-4=0.217692mW. 3.最高截止频率仿真Fmax=1/340p=2.94E8hz通过仿真验证,电路设计符合逻辑关系,完全正确的四、版图设计:五、实验总结;通过本次设计训练,使我对集成设计的基本流程有了进一步的了解,操作、动手能力方面也得到了很大的提高,熟悉并掌握了cadence的基本操作;但是在布线的时候出了问题,没能做出后面的工序,很是遗憾啊!希望在以后的学习中我能做到更好!由于MOS 器件内部有电容存在,所以信号的传输会有延时,而且各个器件的延时会进行叠加,这对输出的特性有很大的影响,有时会造成致命的错误,这对器件的使用范围会有制约,这是所不允许的。

通过电路原理图的调整可以解决一定的问题。

这个问题没有办法完全的解决。

这是因为器件的制造工艺的约束。

MOS 管的宽长比对MOS 电路的性能起着非常重要的作用。

因此在每个管子的选择都需要慎重。

对于怎样选择各个管子的参数目前还不知道有什么有效的简便的方法。

边缘D 触发器: 之迟辟智美创作

负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号.如果在CP 高电平期间输入端呈现干扰信号,那么就有可能使触发器的状态犯错.而边缘触发器允许在CP 触发沿来到前一瞬间加入输入信号.这样,输入端受干扰的时间年夜年夜缩短,受干扰的可能性就降低了.边缘D触发器也称为维持-阻塞边缘D触发器. 电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器.

D触发器工作原理:

SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平有效.当SD=0且RD=1时,不论输入端D为何种状态,城市使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端.我们设它们均已加入了高电平,不影响电路的工作.工作过程如下: 1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变.同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门翻开,因此可接收输入信号D,Q5=D,Q6=Q5=D. 2.当CP由0变1时触发器翻转.这时G3和G4翻开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定.Q3=Q5=D,Q4=Q6=D.由基本RS触发器的逻辑功能可知,Q=D. 3.触发器翻转后,在CP=1时输入信

号被封锁.这是因为G3和G4翻开后,它们的输出Q3和Q4的状态是互补的,即肯定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器酿成1状态的作用,故该反馈线称为置0维持线,置1阻塞线.Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁.Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线.因此,该触发器常称为维持-阻塞触发器.总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边缘触发器之称.与主从触发器相比,同工艺的边缘触发器有更强的抗干扰能力和更高的工作速度.功能描述

2.特征方程 Qn+1=D

3状态转移图

脉冲特性: 1.建立时间:由下图维持阻塞触发器的电路可

见,CP信号是加到门G3和G4上的,因而在CP上升沿达到之前门G5和G6输出真个状态必需稳定地建立起来.输入信号达到D端以后,要经过一级门电路的传输延迟时间G5的输出状态才华建立起来,而G6的输出状态需要经过两级门电路

的传输延迟时间才华建立,因此D真个输入信号必需先于CP 的上升沿达到,而且建立时间应满足: tset≥2tpd. 2.坚持时间:由下图可知,为实现边缘触发,应保证CP=1期间门G6的输出状态不变,不受D端状态变动的影响.为此,在D=0的情况下,当CP上升沿达到以后还要等门G4输出的低电平返回到门G6的输入端以后,D真个低电平才允许改变.因此输入低电平信号的坚持时间为tHL≥tpd.在 D=1的情况下,由于CP上升沿达到后G3的输出将G4封锁,所以不要求输入信号继续坚持不变,故输入高电平信号的坚持时间

tHH=0. 3.传输延迟时间:由图工作波形图不难推算出,从CP上升沿达到时开始计算,输出由高电平酿成低电平的传输延迟时间tPHL和由低电平酿成高电平的传输延迟时间tPLH分别是:tPHL=3tpd tPLH=2tpd

维持和阻塞D触发器的电路和静态波形

4.最高时钟频率:为保证由门G1~G4组成的同步RS触发器能可靠地翻转,CP高电平的继续时间应年夜于 tPHL,时

钟信号高电平的宽度tWH应年夜于tPHL.而为了在下一个CP上升沿达到之前确保门G5和G6新的输出电平得以稳定地建立,CP低电平的继续时间不应小于门G4的传输延迟时间和tset之和,即时钟信号低电平的宽度tWL≥

tset+tpd,因此获得:

在实际集成触发器中,每个门传输时间是分歧的,而且作了分歧形式的简化,因此上面讨论的结果只是一些定性的物理概念.其真实参数由实验测定. 综上所述,对边缘D触发器归纳为以下几点: 1.边缘D触发器具有接收并记忆信号的功能,又称为锁存器;2.边缘D触发器属于脉冲触发方式;3.边缘D触发器不存在约束条件和一次变动现象,抗干扰性能好,工作速度快。