第5章组合逻辑电路

- 格式:ppt

- 大小:1.96 MB

- 文档页数:83

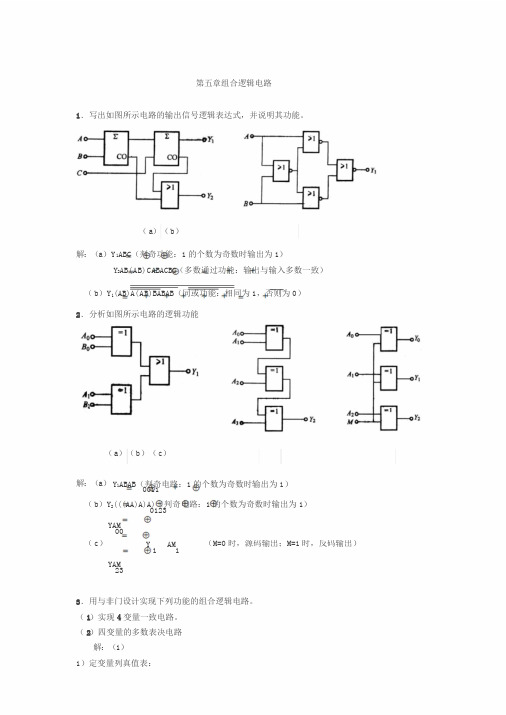

第五章组合逻辑电路1.写出如图所示电路的输出信号逻辑表达式,并说明其功能。

(a)(b)解:(a)Y1ABC(判奇功能:1的个数为奇数时输出为1)Y2AB(AB)CABACBC(多数通过功能:输出与输入多数一致)(b)Y1(AB)A(AB)BABAB(同或功能:相同为1,否则为0)2.分析如图所示电路的逻辑功能(a)(b)(c)解:(a)Y1ABAB(判奇电路:1的个数为奇数时输出为1)0011(b)Y2(((AA)A)A)(判奇电路:1的个数为奇数时输出为1)0123YAM00(c)Y1 A M1(M=0时,源码输出;M=1时,反码输出)YAM233.用与非门设计实现下列功能的组合逻辑电路。

(1)实现4变量一致电路。

(2)四变量的多数表决电路解:(1)1)定变量列真值表:ABCDYABCDY0000110000000101001000100101000011010110010*******010*******011001110001110111112)列函数表达式:YABCDABC D ABCDABCD3)用与非门组电路(2)输入变量A、B、C、D,有3个或3个以上为1时输出为1,输人为其他状态时输出为0。

1)列真值表2)些表达式3)用与非门组电路4.有一水箱由大、小两台水泵ML和Ms供水,如图所示。

水箱中设置了3个水位检测元件A、B、C,如图(a)所示。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C点时水泵停止工作;水位低于C点而高于B点时Ms单独工作;水位低于B点而高于A点时ML单独工作;水位低于A点时ML和Ms同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

解:(1)根据要求列真值表(b)(b)(a)(2)真值表中×对应的输入项为约束项,利用卡诺图化简(c)(d)(c)(d)(e)得:MABCsMBL(ML、M S的1状态表示工作,0状态表示停止)(3)画逻辑图(e)5.某医院有—、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。

第五章 组合逻辑电路典型例题分析第一部分:例题剖析例1.求以下电路的输出表达式:解:例2.由3线-8线译码器T4138构成的电路如图所示,请写出输出函数式.解:Y = AC BC ABC= AC +BC + ABC = C(AB) +CAB = C (AB) T4138的功能表&&Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7“1”T4138A B CA 2A 1A 0YaYbS 1 S 2 S 30 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1S 1S 2S 31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0A 2A 1A 0Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 70 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 0例3.分析如图电路,写出输出函数Z的表达式。

CC4512为八选一数据选择器。

解:例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。

(表中未出现的输入变量状态组合可作为约束项)CC4512的功能表A ⨯DIS INH 2A 1A 0Y1 ⨯0 10 00 00 00 00 00 00 00 0⨯⨯⨯⨯⨯0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1高阻态 0D 0D 1D 2D 3D 4D 5D 6D 7ZCC4512A 0A 1A 2D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7DIS INHD1DA B C D Y 0 0 0 0 10 0 0 1 00 0 1 0 10 0 1 1 00 1 0 0 0CD AB 00 01 11 1000 1 0 0 101 0 1 0 1 11 ××××10 0 1 ××AB第一步画卡诺图第三步画逻辑电路图例5.写出下面组合电路的输出表达式,分析逻辑功能。

思考题与习题题解5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与电路原来所处的状态无关;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与信号作用前电路原来所处的状态有关。

(2)构成一异步2n进制加法计数器需要n 个触发器,一般将每个触发器接成计数或T’型触发器。

计数脉冲输入端相连,高位触发器的CP端与邻低位Q端相连。

(3)一个4位移位寄存器,经过 4 个时钟脉冲CP后,4位串行输入数码全部存入寄存器;再经过4个时钟脉冲CP后可串行输出4位数码。

(4)要组成模15计数器,至少需要采用 4 个触发器。

5-2判断题(1)异步时序电路的各级触发器类型不同。

(×)(2)把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。

(×)(3)具有N个独立的状态,计满N个计数脉冲后,状态能进入循环的时序电路,称之模N计数器。

(√)(4)计数器的模是指构成计数器的触发器的个数。

(×)5-3单项选择题(1)下列电路中,不属于组合逻辑电路的是(D)。

A.编码器B.译码器C.数据选择器D.计数器(2)同步时序电路和异步时序电路比较,其差异在于后者( B)。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关(3)在下列逻辑电路中,不是组合逻辑电路的有( D)。

A.译码器B.编码器C.全加器D.寄存器(4)某移位寄存器的时钟脉冲频率为完成该操作需要(B)时间。

100KHz,欲将存放在该寄存器中的数左移8位,A.10μSB.80μSC.100μSD.800ms(5)用二进制异步计数器从0做加法,计到十进制数178,则最少需要(C )个触发器。

A.6B.7C.8D.10(6)某数字钟需要一个分频器将32768Hz的脉冲转换为1HZ的脉冲,欲构成此分频器至少需要(B)个触发器。

A.10B.15C.32D.32768(7)一位8421BCD 码计数器至少需要(B)个触发器。