第4章 组合逻辑电路习题解答

- 格式:doc

- 大小:1.42 MB

- 文档页数:17

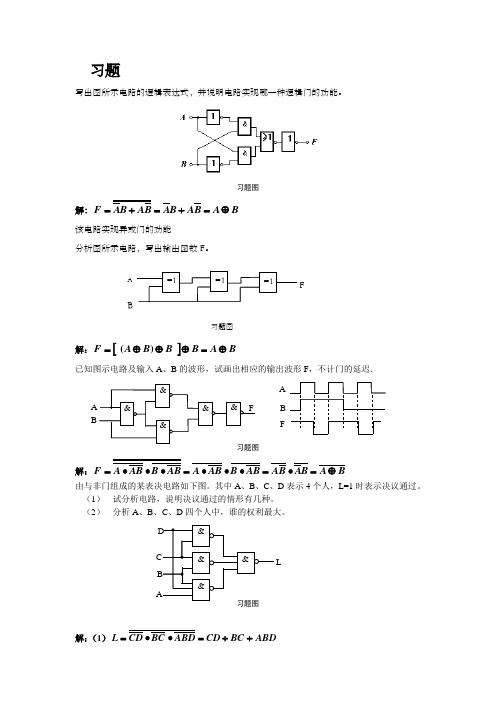

习题写出图所示电路的逻辑表达式,并说明电路实现哪一种逻辑门的功能。

习题图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能分析图所示电路,写出输出函数F 。

习题图 解:[]B A B BB A F ⊕=⊕⊕⊕=)(已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=由与非门组成的某表决电路如下图。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情形有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题图B AC & && & D L BA =1=1=1FF A B & && & & F B A(3)依照真值表可知,四个人当中C 的权利最大。

分析图所示逻辑电路,已知S 1﹑S 0为功能操纵输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)试分析图所示电路的逻辑功能。

习题图解:(1)ABC C B A F )(++=10电路逻辑功能为:“判输入ABC 是不是相同”电路。

已知某组合电路的输入A 、B 、C 和输出F 的波形如以下图所示,试写出F 的最简与或表达式。

习题图 解:(1)依照波形图取得真值表:(2)由真值表取得逻辑表达式为C AB BC A C B A F ++=、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方式,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

FCB ACB A DC BD A D C B C B A D C B D A D C B C B A D C B D A D C B F •••=+++=+++=依照最简与非式画出用与非门实现的最简逻辑电路:电路略。

数字电路与逻辑设计习题_4第四章组合逻辑电路剖析第四章组合逻辑电路一、选择题1.下列表达式中不存在竞争冒险的有。

A.Y=B +A BB.Y=A B+B CC.Y =A B C +ABD.Y =(A+B )A D 2.若在编码器中有50个编码对象,则要求输出二进制代码位数为位。

A.5B.6C.10D.503.一个16选一的数据选择器,其地址输入(选择控制输入)端有个。

A.1B.2C.4D.16 4.下列各函数等式中无冒险现象的函数式有。

A.B A AC C B F ++= B.B A BC C A F ++=C.B A B A BC C A F +++=D.C A B A BC B A AC C B F +++++=E.B A B A AC C B F +++= 5.函数C B AB C A F ++=,当变量的取值为时,将出现冒险现象。

A.B=C=1B.B =C=0C.A =1,C=0D.A =0,B=0 6.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = 。

A.3X A A X A A X A A X A A 01201101001+++B.001X A AC.101X A AD.3X A A 017.一个8选一数据选择器的数据输入端有个。

A.1 B.2 C.3 D.4 E.8 8.在下列逻辑电路中,不是组合逻辑电路的有。

A.译码器B.编码器C.全加器 D.寄存器9.八路数据分配器,其地址输入端有个。

A.1B.2C.3D.4E.8 10.组合逻辑电路消除竞争冒险的方法有。

A. 修改逻辑设计B.在输出端接入滤波电容C.后级加缓冲电路D.屏蔽输入信号的尖峰干扰 11.101键盘的编码器输出位二进制代码。

A.2B.6C.7D.812.用三线-八线译码器74LS 138实现原码输出的8路数据分配器,应。

A.A ST =1,B ST =D ,C ST =0 B. A ST =1,B ST =D ,C ST =D C.A ST =1,BST =0,CST =D D.A ST =D ,BST =0,CST =013.以下电路中,加以适当辅助门电路,适于实现单输出组合逻辑电路。

第四章 组合逻辑电路4.1 分析题图4.1所示的电路,写出Y 的逻辑表达式。

题图4.1解:在图中标出各级输出变量,有12314234,,,T A T B T T B AB T T A BA Y T T ABBA AB BA A B=========+=⊕4.2 求题图4.2所示电路中F 的逻辑表达式,化简成最简与或式,列出真值表,分析其逻辑功能,设计出全部改用与非门实现这一逻辑功能的电路。

题图4.2解:在图中标出各级输出变量,有12341252345,,(),()T AC T B T A CT T T AC B A C B T T T B A C F T T A B C ABC===+=+=+=+==+=⊕=+ 真值表如下:A B CF0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 11 0 0 0 0 0 0 1显然,此电路可实现三人一致功能。

F A B C ABC A B C ABC =+=所以,其与非门逻辑电路如下4.3 分析题图4.3所示电路。

题图4.3解:在图中标出各级输出变量,有1232425121362746157,,T T ABT T C ABC T T C AB C T T C ABC F TT ABC T F ABCT T T ABC AC BCF T T ABC AC BC ABC AB C=====+=+========++=+=+++=+4.4 分析题图4.4所示电路,求输出F 的逻辑函数表达式并化简,用最少的或非门实现。

题图4.4解:在图中标出各级输出变量,有123123,T A B C T A B T B T T F T A B=++=+=++==+其或门形式如下:4.5 分析题图4.5所示电路,说明其逻辑功能。

题图4.5解:在图中标出各级输出变量,有10020031141152301001200123111245111111,,T A B T A B T A B T A B T T T S T A B C T A B S T T A B C C T T A B A C B C =⊕==⊕====⊕===⊕=⊕⊕=+=++此图可实现二位全加器的功能。

第四章 组合逻辑门电路4.2 试分析图中所示电路的逻辑功能。

解:Y AB AB AB AB A B ==+=⊕可知,图中所示电路为异或门电路。

4.3 试分析图中所示电路是否合理,并写出其最简与-或表达式。

A CB DB C D图4.3解:(1)由图写出逻辑表达式:Y AC B BD BC BC D =(2)化为与-或表达式:()()()Y AC B BD BC BC DAC B BD BC BC D AC B BD BC B C D ABCD ABC BC BD CD==+=++++=++++(3)由与-或表达式作出图示卡诺图:(4)由卡诺图得出最简逻辑表达式: Y A C B C D =++ 可见,图示电路不合理。

4.7 路灯由安装在三个不同地方的开关A 、B 、C 控制。

当总电源开关闭合时,三个开关可控制路灯的点亮和熄灭,这时,一个开关动作时灯亮,另一个开关动作时灯熄灭。

当总电源开关S 断开时,路灯不会亮。

试用与非门设计该路灯控制电路。

解:(1)分析设计要求并列出真值表:设总电源开关S 闭合时为1,断开时为0;路灯控制开关A 、B 、C 动作时为1,不动作时为0; 灯用Y 表示,灯灭为0,灯亮为1。

由此可列出真值表,如表题4.7所示:(2)求出最简与-或表达式 由真值表作出卡诺图,如图题4.7(a)所示。

由图可知,该逻辑函数已不能进一步化简。

因此,可直接写出逻辑表达式: Y A BC AB C A B C AB C =+++ 由真值表可知,S=0,Y=0;S=1时,Y 受A 、B 、C 的控制。

因此,符合题意要求的逻辑表达式应为:()Y S ABC ABC ABC ABC =+++ 将上式变换为与-非表达式:Y S ABC SABC SABC SABC = (3)画出逻辑图:如图题4.7(b)所示。

图题4.7C S(a )(b )4.8 由与非门设计一个数值范围判别电路。

设电路输入A 、B 、C 、D 为表示1位十进制数X 的8421BCD 码,当X 符合下列条件时,输出Y=1,否则输出为0。

第四章组合逻辑电路一、填空题1、根据逻辑功能的不同特点,可将数字电路分成两大类:一类称为组合逻辑电路,另一类称为电路。

2、分析组合逻辑电路时,一般根据图写出逻辑函数表达式。

3、用门电路设计组合逻辑电路时,通常根据设计要求列出,再写出输出逻辑函数表达式。

4、组合逻辑电路的特点是输出状态只与,与电路原来的状态,其基本单元电路是。

5、译码器按功能的不同分为三种,,。

6、是编码的逆过程。

7、数据选择器是在的作用下,从中选择作为输出的组合逻辑电路。

8、2n选1数据选择器有位地址码。

9、8选1数据选择器在所有输入数据都为1时,其输出标准与-或表达式共有个最小项。

如所有输入数据都为0时,则输出为。

10、全加器有3个输入端,它们分别为,,和;输出端有2个,分别为、。

11、半导体数码显示器的内部接法有两种形式:共接法和共接法。

12、BCD-七段译码器/驱动器输出高电平有效时,用来驱动极数码管;如输出低电平有效时,用来驱动极数码管。

13、数据选择器只能用来实现输出逻辑函数,而二进制译码器不但可用来实现输出逻辑函数,而且还可用来实现输出逻辑函数。

14、在组合逻辑电路中,消除竞争冒险现象的主要方法有,,,。

二、判断题()1、模拟量是连续的,数字量是离散的,所以模拟电路的精度要高于数字电路。

()2、数据选择器是将一个输入数据分配到多个指定输出端的电路。

()3、数值比较器是用于比较两组二进制数大小或相等的电路。

()4、优先编码器只对多个输入编码信号中优先权最高的信号进行编码。

()5、加法器是用于对两组二进制数进行比较的电路。

()6、具有记忆功能的电路不是组合逻辑电路。

()7、译码器的作用就是将输入的二进制代码译成特定的信号输出。

()8、全加器只用于对两个一位二进制数相加。

()9、数据选择器根据地址码的不同从多路输入数据中选择其中一路输出。

()10、在任何时刻,电路的输出状态只取决于该时刻的输入,而与该时刻之前的电路状态无关的逻辑电路,称为组合逻辑电路。

教材:数字电子技术基础(“十五”国家级规划教材) 杨志忠 卫桦林 郭顺华 编著高等教育出版社2009年7月第2版; 2010年1月 北京 第2次印刷;第四章 组合逻辑电路(部分练习题答案)练习题P172【4.1】、试分析图P4.1所示电路的逻辑功能。

解题思路:根据逻辑图依次写出函数表达式、化简表达式、列写真值表、分析逻辑功能。

(b )、Y AB AB A B =+=:;(同或功能) 真值表略; 【4.2】、试分析图P4.2所示电路的逻辑功能。

解题思路:根据逻辑图依次写出函数表达式、化简表达式、列写真值表、分析逻辑功能。

(a )、Y AB AB AB AB A B =⋅=+=⊕;(异或功能) 真值表略; 【4.3】、试分析图P4.3所示电路的逻辑功能。

解题思路:根据逻辑图从输入到输出逐级依次写出函数表达式、化简表达式、列写真值表、分析逻辑功能。

(a )、()Y ABC A ABC B ABC C ABC A B C ABC ABC =⋅+⋅+⋅=⋅++=+; 真值表略; 【4.4】、试分析图P4.4所示电路的逻辑功能。

解题思路:根据逻辑图从输入到输出逐级依次写出函数表达式、化简表达式、列写真值表、分析逻辑功能。

解:12 Y A B C Y AB A B C AB A B C =⊕⊕=⋅⊕⋅=+⊕⋅;该逻辑电路实现一位全加运算。

Y1表示本位和数,Y2是进位输出。

mi A B C Y1 Y2 0 0 0 0 0 0 1 0 0 1 1 02 0 1 0 1 03 0 1 1 0 14 1 0 0 1 05 1 0 1 0 16 1 1 0 0 17 1 1 1 1 1【4.6】、写出图P4.6所示电路的逻辑函数表达式,并且把它化成最简与或表达式。

解题思路:变量译码器实现逻辑函数是把逻辑变量输入译码器地址码,译码器输出i i m Y =,再用与非门(输出低电平有效)变换就可以得到所需的逻辑函数,输出函数具有下列的表达形式:(,,)0356m(0,3,5,6)A B C F Y Y Y Y ==∑。

第四章习题答案4-1(a)100A A F ⊕=,211A A F ⊕=,322A A F ⊕=,33A F =(b) 000B A C =,011111)()(C B A B A C ⊕+=,000B A S ⊕=,0111)(C B A S ⊕⊕= (c) B A AB F +=(同或)(d) B A AC F +=1,B A BC F +=2,C A BC F+=3, 4-2,F ,F ,F∑=)9,8,7,6,5(3m F ,∑=)9,4(2m F ,∑=)8,7,3,2(1m F ,∑=)8,6,3,1(0m F卡诺图化简D F =3,AD D C B F +=2,D A C B CD F ++=1,D B A D A F +=0,F ,F ,F∑=)9,8,7,6,5(3m Y ,∑=)9,4,3,2,1(2m Y , ∑=)8,7,4,3,0(1m Y ,∑=)8,6,4,2,0(0m Y用4-16线译码器实现987653F F F F F Y =,943212F F F F F Y =,874301F F F F F Y =,864200F F F F F Y =4-3将四片138译码器级联,ST 接高电平,ST 接低电平,ST 由译码控制3442A A ST =,3432A A ST =,3432A A ST =,3432A A ST =4-4113471347(1,3,4,7)F m m m m m F F F F ===∑ 2046046(0,4,6)F m m m m F F F ===∑4-51)一片8选1,输入A 、B 、C 分别接8选1的地址A 2,A 1,A 00,,1,17563420========D D D D D D D D D D2)两片8选1,输入A 、B 、C ,D 分别接4选1的地址012,,,A A A E1,01413121197651151084320================D D D D D D D D D D D D D D D D4-6A S SB A S S B A S S AB S S F 01010101)()(+⊕+++= A S S B A S S B A S S B S S A S S AB S S F 010*********+++++=将A S S ,,01分别接8选1的地址012,,A A A ,则输入端分别是0,1,,70635421========D D D D B D B D D D4-71) 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3B 2B 1B 0=0011,CI=0 2) 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3B 2B 1B 0=1101,CI=04-8假设四位被加数为ABCD ,加数为EFGH 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3,B 2,B 1,B 0如下:M CI M H B M G B M F B M E B =⊕=⊕=⊕=⊕=,,,,01234-9真值表∑=)15,14,13,11,7(m F1)8选1数据选择器,将B A M ,,分别接8选1的地址012,,A A A ,则输入端分别是0,1,42107653========D D D D D C D D D2)用3-8译码器151413117151413117F F F F F m m m m m F ==4-10设三个开关分别为A,B,C ,开关的关闭为1,打开为0;灯的输出为F ,灯的亮为1,灭为0真值表C B A F =输入ABCD 分别接4-16译码器的地址段A 3,A 2,A 1,A 0 1) a 端:0158421=====D D D D D , 其余数据端接1 2) b 端:所有数据端均接1,1150=D D3) c 端:012109653======D D D D D D ,其余数据端接1 4) d 端:0158421=====D D D D D ,其余数据端接15) e 端:01514131187421=========D D D D D D D D D ,其余数据端接1 6) f 端:1150==D D ,其余数据端接07) g 端:08421====D D D D ,其余数据端接1设输出灯亮为1,灭为0真值表如下:1)4-16输入ABCD 分别接4-16译码器的地址段A 3,A 2,A 1,A 0(1) F 1端:143210=====D D D D D , 其余数据端接0 (2) F 2端:198765=====D D D D D , 其余数据端接0 (3) F3端:1151413121110======D D D D D D , 其余数据端接0 2)4位数据比较器实现用两片数据选择器,输入端ABCD 分别接两个比较器的A 3A 2A 1A 0,第一片比较器的B 3B 2B 1B 0=0101,第二片的B 3B 2B 1B 0=1001,两片的级联端0,1===<>=B A B A B A I I I ,则:B A I F <=11,B A I F >=23,212F F F =用4-16输入A 1A 0B 1B 0分别接4-16译码器的地址段A 3,A 2,A 1,A 0 (1) F 0端:1151375====D D D D , 其余数据端接0(2) F 1端:1141311976======D D D D D D , 其余数据端接0 (3) F 2端:1141110===D D D , 其余数据端接0 (4) F 3端:115=D , 其余数据端接04-141)只要把两片的B A I =直接相连就可以判断三个输入数据是否相等,假定输入为ABCD 四门课程,及格为1,不及格为0;输出F 为能否毕业,能够毕业为1,不能毕业为0。

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

(基本题属于4.1节)习题4.1图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能4.2分析图所示电路,写出输出函数F 。

(基本题属于4.1节)习题4.2图 解:[]B A B BB A F ⊕=⊕⊕⊕=)(4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.(基本题属于4.1节)图解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(基本题属于4.1节)(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

B AC&& && DLB A =1 =1 =1FFA B&&&&&FB A习题4.4图解:(1)ABD BC CD ABD BC CD L ++=••= (2)(3)4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

(基本题属于4.1节)习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)(3)当S 1S 0=00和S 1S 0=11时,该电路实现两输入或门,当S 1S 0=01时,该电路实现两输入或非门,当S 1S 0=10时,该电路实现两输入与非门。

4.6试分析图所示电路的逻辑功能,并用最少的与非门实现。

(综合题属于4.1、4.2节)10习题4.6图解:(1)DC AD B AD D C A D B AD D C A D B AD A D C D B AD L ••=++=++=+++•=)((2)(3)4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

(基本题属于4.2节)习题4.7图 解:(1)根据波形图得到真值表:FC B ALC AB BC A C B A F ++=4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

(基本题属于4.2节)解:1)(1)将逻辑函数化成最简与或式并转换成最简与非与非式。

D C B D A D C BD A D C B F ••=+=(2)根据最简与非与非式画出用与非门实现的最简逻辑电路。

2)(1) 将逻辑函数的反函数化成最简与或式。

ACDBC A BD D A C B A F ++++=F L(2) 利用反演规则将逻辑函数化成最简或与式并转换成最简或非或非式。

DC A C B AD B D A C B A D C A C B A D B D A C B A D C A C B A D B D A C B A F ++++++++++++=++++++++=++++++++=))()()()(())()()()(((3)根据最简或非或非式画出用或非门实现的最简逻辑电路。

(图略) 3)(1)由上步可知逻辑函数的反函数化成最简与或式。

ACD BC A BD D A C B A F ++++=(2)则逻辑函数的最简与或非式为。

ACD BC A BD D A C B A F ++++=(3)根据最简与或非式画出用与或非门实现的最简逻辑电路。

(图略)4.9、设计一个由三个输入端、一个输出端组成的判奇电路,其逻辑功能为:当奇数个输入信号为高电平时,输出为高电平,否则为低电平。

要求画出真值表和电路图。

(基本题属于4.2节) 解:(1)根据题意,设输入逻辑变量为A 、B 、C ,输出逻辑变量为F ,列出真值表为:(2)由真值表得到逻辑函数表达式为:C B A ABC C B A C B A C B A F ⊕⊕=+++=(3)画出逻辑电路图F4.10、试设计一个8421BCD 码的检码电路。

要求当输入量ABCD ≤4,或≥8时,电路输出L 为高电平,否则为低电平。

用与非门设计该电路。

(基本题属于4.2节) 解:(1)根据题意列出真值表为:(2)由真值表可得到输出逻辑函数表达式为:)15,14,13,12,11,10()9,8,4,3,2,1,0()(0123m m D D D D L ∑+∑=(3)将输出逻辑函数表达式化简并转换为与非与非式为:0120120123)(D D D D D D D D D D L •=+=(4)画出逻辑电路图4.11、一个组合逻辑电路有两个功能选择输入信号C 1、C 0,A 、B 作为其两个输入变量,F 为电路的输出。

当C 1C 0取不同组合时,电路实现如下功能:1.C 1C 0=00时,F=A 2.C 1C 0=01时,F= A ⊕B 3.C 1C 0=10时,F=AB 4.C 1C 0=11时,F=A+B 试用门电路设计符合上述要求的逻辑电路。

(基本题属于4.2节) 解:(1)根据题意,列出真值表(2)由真值表列出逻辑函数表达式为:B AC AB C B A C A C C m B A C C F 0100101)15,14,13,11,6,5,1,0(),,,(+++=∑=(3)根据逻辑函数表达式画出逻辑电路图。

B A =1 =1C FD L4.12、用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。

列出控制电路真值表,并选用合适的集成电路来实现。

(基本题属于4.2节)解:(1)根据题意,列出真值表由题意可知,令输入为A 、B 、C 表示三台设备的工作情况,“1”表示正常,“0”表示不正常,令输出为R ,Y ,G 表示红、黄、绿三个批示灯的 状态,“1”表示亮,“0”表示灭。

F(2)由真值表列出逻辑函数表达式为:∑=)6,5,3,0(),,(m C B A R ∑=)4,2,1,0(),,(m C B A Y7),,(m C B A G =(3)根据逻辑函数表达式,选用译码器和与非门实现,画出逻辑电路图。

4.13、 8-3线优先编码器74LS148在下列输入情况下,确定芯片输出端的状态。

(1) 6=0,3=0,其余为1; (2) EI=0,6=0,其余为1;(3) EI=0,6=0,7=0,其余为1; (4) EI=0,0~7全为0;(5) EI=0,0~7全为1。

(基本题属于4.3节)解:(1)74LS148在输入6=0,3=0,其余为1时,输出所有端均为1。

(2)74LS148在输入EI=0,6=0,其余为1时,输出A 2 A 1 A 0 =001,CS=0,EO=1。

(3)74LS148在输入EI=0,6=0,7=0,其余为1时,输出A 2 A 1 A 0 =000,CS=0,EO=1。

(4)74LS148在输入EI=0,0~7全为0时,输出A 2 A 1 A 0 =000,CS=0,EO=1。

(5)74LS148在输入EI=0,0~7全为1时,输出A 2 A 1 A 0 =111,CS=1,EO=0。

4.14、试用8-3线优先编码器74LS148连成32-5线的优先编码器。

(基本题属于4.3节) 解:4.15、4-16线译码器74LS154接成如习题4.15图所示电路。

图中S 0、S 1为选通输入端,芯片译码时,S 0、S 1同时为0,芯片才被选通,实现译码操作。

芯片输出端为低电平有效。

(1) 写出电路的输出函数F 1(A,B,C,D)和F 2(A,B,C,D)的表达式,当ABCD 为何种取值时,函数F 1=F 2=1;(2) 若要用74LS154芯片实现两个二位二进制数A 1A 0,B 1B 0的大小比较电路,即A >B时,F 1=1;A <B 时,F 2=1。

试画出其接线图。

(综合题属于4.4节)习题4.15图 解:(1)∑=)14,13,9,7,4,0(),,,(1m D C B A F∑=)15,13,9,8,7,5(),,,(2m D C B A F当ABCD=0111或ABCD=1001或ABCD=1101时,F 1=F 2=1。

(2)由题意得到真值表如下:∑=)14,13,12,9,8,4(),,,(1m D C B A F ∑=)11,7,6,3,2,1(),,,(2m D C B A F画出逻辑电路图为:4、16用74LS138译码器构成如习题4.16图所示电路,写出输出F 的逻辑表达式,列出真值表并说明电路功能。

(基本题属于4.4节)习题4.16图解:(1)由题可得逻辑函数表达式为:∑=)5,421(),,(,,m C B A F(2)列出真值表如下:4、17试用74LS138译码器和最少的与非门实现逻辑函数(基本题属于4.4节)1)∑=)7,6,2,0(C)B,(A,F 1m2)F 2(A,B,C)=A ⊙B ⊙C 解:(1)A B C F 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 10 1 1 0 1 1 0 0(2)F 2(A,B,C)=A ⊙B ⊙C ∑=)7,4,2,1(m4.18、试用3线-8线译码器74LS138设计一个能对32个地址进行译码的译码器。

(综合题属于4.4节)解:用3线-8线译码器74LS138设计一个能对32个地址进行译码的译码器如图所示。

4.19、已知8421BCD 可用7段译码器,驱动日字LED 管,显示出十进制数字。

指出下列变换真值表中哪一行是正确的。

(注:逻辑“1”表示灯亮)D C B A a b c d e f g * 00 0 0 0 0 0 0 0 0 0 0 4 0 1 0 0 0 1 1 0 0 1 1 71111111C B A G 1 G 2A G 2BY 0 Y 7 ~74LS138 C B A 0 G 1 G 2A G 2BY 0 Y 7 ~74LS138 Y 16~Y 23 Y 24~Y 31 C B A G 1 G 2A G 2B Y 0 Y 7 ~74LS138 C B A G 1G 2A G 2B Y 0Y 7 ~74LS138 A 1 A 2 A 0 A 1 Y 0~Y 7 Y 8~Y 15 A1解:第二行4的显示是正确的。

4.20、已知某仪器面板有10只LED 构成的条式显示器。

它受8421BCD 码驱动,经译码而点亮,如图所示。