高速PCB设计验证经典案例

- 格式:pdf

- 大小:2.46 MB

- 文档页数:32

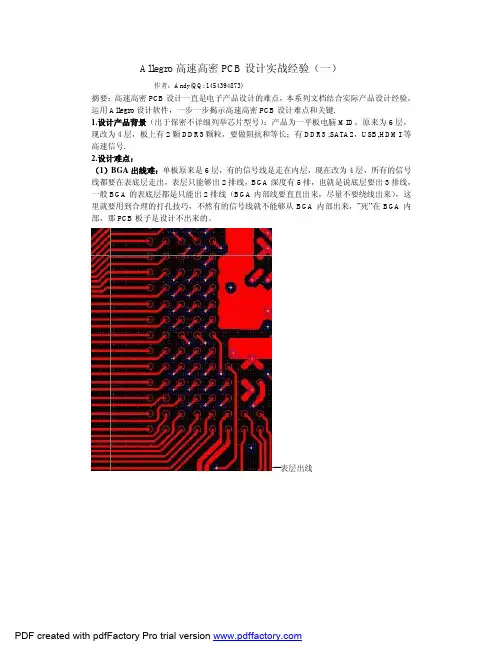

Allegro高速高密PCB设计实战经验(一)作者:Andy(QQ: 1454394873)摘要:高速高密PCB设计一直是电子产品设计的难点,本系列文档结合实际产品设计经验,运用Allegro设计软件,一步一步揭示高速高密PCB设计难点和关键.1.设计产品背景(出于保密不详细列举芯片型号):产品为一平板电脑MID,原来为6层,现改为4层,板上有2颗DDR3颗粒,要做阻抗和等长;有DDR3 ,SA TA2,USB,HDMI等高速信号.2.设计难点:(1)BGA出线难:单板原来是6层,有的信号线是走在内层,现在改为4层,所有的信号线都要在表底层走出,表层只能够出2排线,BGA深度有5排,也就是说底层要出3排线,一般BGA的表底层都是只能出2排线(BGA内部线要直直出来,尽量不要绕线出来),这里就要用到合理的打孔技巧,不然有的信号线就不能够从BGA内部出来,”死”在BGA内部,那PCB板子是设计不出来的。

---表层出线底层出线注意到没有,这里的fanout是交错开来,原来2个过孔间只能过一根线,现在打孔交错开来,间距就变为2倍,就是原来的1.4倍,这样就可以出2根线了,通过这种方法可以出更多的线.(2)DDR3高速处理:对于DDR高速信号线处理要非常仔细,等长,过孔数量相等,参考平面完整,这些都是要注意的地方.注意到上图DDR的同组信号在打孔换层处都是集中打孔,这样可以减少由于过孔产生的阻抗不连续,高频效应等.DDR底下的参考平面要尽量的完整,底下电源为1.5V的电源层,注意信号线不要离分割线太近,大于20MIL比较好3.其他高速信号线处理:按照一般严格设计Sata2HDMI 欢迎学习交流,请加Allegro高速高密PCB设计QQ群211497609原创,如需转载请注明来自Allegro高速高密PCB设计QQ群211497609Allegro高速高密PCB设计实战经验(一)作者:Andy(QQ: 1454394873)摘要:高速高密PCB设计一直是电子产品设计的难点,本系列文档结合实际产品设计经验,运用Allegro设计软件,一步一步揭示高速高密PCB设计难点和关键.1.设计产品背景(出于保密不详细列举芯片型号):产品为一平板电脑MID,原来为6层,现改为4层,板上有2颗DDR3颗粒,要做阻抗和等长;有DDR3 ,SA TA2,USB,HDMI等高速信号.2.设计难点:(1)BGA出线难:单板原来是6层,有的信号线是走在内层,现在改为4层,所有的信号线都要在表底层走出,表层只能够出2排线,BGA深度有5排,也就是说底层要出3排线,一般BGA的表底层都是只能出2排线(BGA内部线要直直出来,尽量不要绕线出来),这里就要用到合理的打孔技巧,不然有的信号线就不能够从BGA内部出来,”死”在BGA内部,那PCB板子是设计不出来的。

东南大学硕士学位论文环境的污染和无线电频谱资源的影响,世界各国制定了相关的电磁兼容标准、法律法规来限制产品的电磁辐射问题,不符合标准要求的产品不允许在市场中销售,即电磁兼容认证,这也逐渐成了限制别国产品进入本国市场的技术贸易壁垒。

欧盟于1989年5月3日颁布了电磁兼容性指令(89/336/EEc)。

指令严格规定,凡不符合指令要求的产品,一律禁止进入欧盟市场或投入使用。

1991年4月、1992年4月和1993年7月,欧盟又先后三次对该指令进行修改。

最近,欧盟在89/336/EEC及其修改件的基础上对电磁兼容技术法规内容再一次作了较大幅度的修改和调整,并于2004年12月31日重新颁布了新的电磁兼容性指令(2004/108/F_贮),该指令将逐步取代89/336/EEC。

指令所有电子产品必须通过电磁发射测试和电磁抗扰度测试并按要求加贴CE标志才可以欧盟市场中销售,没有CE标志的,不得上市销售,已加贴CE标志进入市场的产品,发现不符合安全要求的,要责令从市场收回,持续违反指令有关CE标志规定的,将被限制或禁止进入欧盟市场或被迫退出市场。

欧盟电磁兼容标准的执行及过渡时间如下表所示:图1-3欧洲电磁兼容标准执行情况西方一些发达的国家如美国、加拿大、日本等国也提出实施EMC指令的要求,并且实施这一指令的要求也正在向世界各国延伸,将成为世界各国的共同要求。

所以不通过电磁兼容性能试验的设备、产品是无法进入国际市场,它是电子设备进入国际市场的通行证。

我国也于2003年开始实施强制性的产品认证,在认证规定之内的产品必须在指定测试机构通过相应电磁兼容和安全标准的测试并在产品上贴加“CCC”标识,方可在市场中销售。

且近年来全球电磁兼容认证的要求也不断变化,世界各国都逐渐采用IEC及CISPR出版制定的EMC的标准来要求市场上的电子产品,如下表所示12】:电磁兼容要求的扩大199219931994199519961997199819992000200120022003.2006FCCFCCFCCFCCFCCFCC∞CFCCDOCFCCDOCFCCDOCFCCDOCFCCDoCFCCDoCTWTuvTWTUvTWTWTWTWTWTUVTWTWNEMKONEMKONEMKONEMKONEMKONEMKONEMKONEMKONEMKONEMKONEMKONEMKoVDEVDEVDEfCECECECECECECECEC£CEMPR¨.MPR¨。

一板成功——高速电路研发与设计典型故障案例解析高速电路研发和设计是现代通信产业发展的重要组成部分,具有很高的技术含量和难度。

然而,在实际应用中,由于各种因素(如材料、电磁干扰等),很容易出现故障。

今天,我们将针对一板成功——高速电路研发与设计典型故障案例进行分析和解析。

故障现象:在进行高速电路研发和设计时,出现了一种故障现象:板子上部分器件在工作时明显变热,甚至部分器件直接烧毁。

而这种现象只出现在一些进行投产的板子上,而对于样品板则没有出现这种故障现象。

故障原因:经过系统的分析和研究,最终确定了故障的原因是电路板设计中功率计算不足。

具体来说,方案设计中提出的功率并不能满足实际需要,因此在高负荷的运转条件下,电路板所产生的过热等问题就愈发凸显。

解决方法:为了解决故障问题,需要尽快修复板子并对其进行更加准确的设计。

具体来说,可以采取以下措施:1、补充设计方案:对于原来不足的功率计算,我们需要重新对方案进行分析,对于需要的额外功率进行补充计算,从而确保功率的合理性。

2、电路板材料升级:合理的材料组合可以很好的抵御高速电路研发和设计中发生的干扰和噪声,从而更好的保证电路板的稳定性。

3、测试验证:在设计高速电路研发和设计中,我们需要大量的测试和验证,以确保设计的可靠性和稳定性。

这是一种必要的步骤,需要给予足够的重视。

总结:在高速电路研发和设计中,出现问题是常有的事情。

重要的是,在出现问题的时候及时的识别和排除问题,并尽快地采取行动,找到解决问题的方法。

希望通过对高速电路研发和设计中的典型故障案例解析,能够对广大电路工作者提供帮助,提升电路板设计的质量和稳定性。

标题:PCB设计优秀工作案例:从失败到成功的启示在我们的公司,PCB设计部门一直是我们业务的核心部分。

最近,我分享一个我在PCB设计部门工作的优秀案例,这个案例是一个从失败到成功的旅程,它展示了如何通过不断的努力和正确的策略,将一个看似失败的项目转化为一个成功的商业案例。

这个案例涉及到的是一个为移动设备制造商设计的PCB项目。

项目开始时,我们遇到了许多挑战。

设计之初,我们没有考虑到生产效率、成本和可靠性的关键因素,导致我们的PCB 设计在生产过程中出现了许多问题。

面对这些问题,我们立即采取了行动。

首先,我们重新评估了我们的设计流程,认识到我们需要更全面地考虑生产效率。

其次,我们开始与生产部门密切合作,以确保我们的设计符合他们的生产要求。

我们还对材料选择和生产工艺进行了优化,以提高PCB的可靠性。

通过这些改进,我们成功地解决了生产中的问题,并获得了积极的反馈。

我们的PCB产品在市场上表现出色,得到了制造商的高度评价。

此外,我们的产品也赢得了客户的信任,为公司带来了更多的业务机会。

这个案例的教训是,成功的设计不仅仅是关于技术能力,还包括与生产部门和客户的紧密合作。

我们需要不断地调整和优化我们的设计流程,以确保我们的产品能够满足生产效率和可靠性的要求。

同时,我们需要倾听客户的需求,了解他们的期望,并努力满足这些期望。

此外,这个案例还强调了持续改进的重要性。

当我们遇到问题时,不要轻易放弃,而应该积极寻找解决方案。

通过不断的尝试和改进,我们可以不断提高我们的设计质量,从而赢得更多的市场份额和客户的信任。

这个案例告诉我们,通过持续的努力和改进,我们可以将看似失败的项目转化为成功的商业案例。

在这个过程中,我们不仅可以提高自己的技能和知识,还可以为公司的业务发展做出贡献。

这个案例展示了PCB设计部门如何通过团队合作、持续改进和客户需求导向,实现了从失败到成功的飞跃。

这为我们所有人树立了榜样,提醒我们在追求卓越的过程中,永远不要放弃。

高速数字电路的PCB设计随着科技的发展,高速数字电路在各个领域中的应用越来越广泛。

高速数字电路的性能和稳定性很大程度上依赖于PCB(Printed Circuit Board)的设计。

本文将介绍高速数字电路的PCB设计原则和技巧。

一、PCB设计原则高速数字电路的PCB设计需要遵循以下原则:1. 信号完整性:在高速信号传输中,信号完整性是至关重要的。

为保证信号的稳定性和减少信号干扰,应采取合适的布局和层叠设计,减少信号走线长度和阻抗不匹配。

2. EMI抑制:高速数字电路的设计容易产生电磁干扰(EMI),对周围设备和系统造成不良影响。

应采用地线分离、屏蔽、滤波等方法来抑制EMI,并遵循EMC(Electromagnetic Compatibility)标准。

3. 热管理:高速数字电路的工作频率高,容易产生较大的功耗和热量。

应合理布局散热器、添加散热片等热管理措施,防止芯片过热从而影响电路性能。

4. 容易维修:在设计PCB时,应考虑到信号线的维修和替换。

通过采用模块化设计和合理布局,可以减少维修难度和成本。

二、PCB设计技巧高速数字电路的PCB设计应遵循以下技巧:1. PCB层次布局:将电路板分为不同的层次,包括信号层、地层和电源层。

信号层应采用临近地层和电源层的布局,以降低信号传输时的阻抗。

2. 差分传输线设计:差分传输线可以减少信号间的干扰,提高信号完整性。

差分传输线的设计应注意保证两根信号线的长度和走线路径相等,并保持合适的差模阻抗匹配。

3. 地线设计:地线是保证信号完整性和抑制干扰的关键。

应该采用广泛的地面平面,减少信号回路的面积。

同时,要避免信号线和地线相交,以减少耦合噪声。

4. 综合布线:在综合布线时,要尽量缩短信号线和电源线的长度,减少信号路径中的损耗和时延,提高电路的性能。

5. 细节考虑:在PCB设计过程中,应考虑到引脚的分配、电源供应、电容和电感的布局等细节。

合理安排元件和电路的布置,可以减少干扰和噪声,提高电路的可靠性。

一、斯卡鲁帕尔马尼的“春之韵”系列斯卡鲁帕尔马尼是一位在艺术领域备受瞩目的艺术家,他的“春之韵”系列作品中,使用了Cadence Allegro软件进行了精准的电路设计,实现了艺术与科技的完美结合。

通过Cadence Allegro的卓越性能和稳定性,斯卡鲁帕尔马尼成功地实现了作品中的电路元件的精确布局和优化,让作品在内部结构上更加完美。

这一系列作品的成功,不仅展现了艺术家对科技的巧妙运用,也向人们展示了Cadence Allegro在电路设计中的优秀表现。

二、华为5G基站天线设计作为全球领先的通信技术企业,华为公司在5G领域的发展备受瞩目。

在5G基站天线设计中,Cadence Allegro发挥了关键作用。

通过Cadence Allegro的高度灵活性和智能设计工具,华为公司工程师们实现了天线的快速设计、仿真和验证,大大加快了产品上市时间,提高了5G基站的性能和可靠性。

华为的成功案例再次证明了Cadence Allegro在电路设计领域的卓越性能和广泛应用价值。

三、尼康相机电路设计尼康是全球知名的相机制造商,其产品质量和性能一直备受推崇。

在尼康相机的电路设计中,Cadence Allegro为设计师们提供了强大的支持和工具,帮助他们实现了电路的高度集成和优化,从而使得尼康相机在成像质量、稳定性和实用性上获得了极大的提升。

尼康相机的成功案例充分显示了Cadence Allegro在消费电子产品领域的重要作用,也证明了Cadence Allegro在实际应用中的稳定性和可靠性。

四、特斯拉电动汽车电池管理系统设计特斯拉作为电动汽车领域的领先者,其产品一直以高性能和创新著称。

在特斯拉电动汽车的电池管理系统设计中,Cadence Allegro发挥了关键作用。

通过Cadence Allegro提供的强大电路设计和仿真工具,特斯拉工程师们成功地实现了电池管理系统的高效设计和验证,保证了汽车电池的安全性和性能稳定性。

TMS320C6201高速电路PCB及电磁兼容性设计印刷电路板(PCB)是电子产品中电路元器件的支撑件,它提供电路元器件之间的电气连接. 随着电子技术的飞速发展,目前高速集成电路的信号切换时间已经小于1ns,时钟频率已达到几百MHz,PCB的密度也越来越高。

PCB设计的好坏对整个系统的抗干扰性能影响很大,直接关系到系统的稳定性和可靠性。

因此,在PCB设计时,应遵守相应的设计规则,符合电磁兼容性的要求。

TMS320C6201是TI公司的DSP芯片,200MHz时钟的C6201峰值性能可以达到2400Mops。

如此高的时钟频率,对PCB的电磁兼容性设计提出了很高的要求。

电磁兼容性与电磁干扰电磁兼容性( EMC)是指电子设备在预期的电磁环境中能够协调、有效地进行工作的能力. 其目的是使电子设备既能抑制各种外来的干扰,又能减少其本身对其他电子设备的电磁干扰。

电磁干扰( EMI) 的来源主要有本电子设备内部形成的干扰以及外界耦合到本电子设备形成的干扰。

针对电子设备内部的干扰,主要通过合理的PCB电磁兼容性设计加以防止和抑制;而针对外界干扰,则可通过电磁屏蔽措施切断其耦合途径加以解决。

本文主要对前者加以阐述。

PCB 及电磁兼容性设计外形与布局从生产工艺考虑,印刷电路板一般采用长宽比不太悬殊的矩形。

PCB尺寸不宜过大,否则导线过长易引起电磁干扰。

导线或器件离PCB板边缘距离不小于2mm。

TI6000系列DSP功耗比较大,电源稳压块应布置在离通风口较近的板边缘,电源块下铺铜以利于散热,发热较大的还可加散热片。

合理的元器件布局,可减少各单元电路间的相互干扰。

大功率低速电路、模拟电路和数字电路应分块布局。

在各分块内,以该分块内核心元件为中心进行布局,尽量缩短各元器件间的引线连接。

电源与接地电源与接地的正确设计,对于抑制电磁干扰来说至关重要。

电源线和地线尽量宽以减小电阻。

数字电路与模拟电路要分开接地。

数字电路的地可构成闭环以提高抗噪声性能。

第三讲高速PCB设计高速PCB设计是指在电子设备中进行高速信号传输的PCB布线设计。

高速信号的传输速率越高,其频率越高,波形越复杂,对PCB设计的要求也越高。

高速PCB设计的关键在于保证信号完整性、减少信号干扰和噪声,并提高信号的传输效率和可靠性。

首先,保证信号完整性是高速PCB设计的首要目标。

信号完整性是指信号在传输过程中能够保持原有的波形特征和时序关系。

为了实现信号完整性,需要遵循信号传输线的基本原则,如匹配阻抗、控制信号的传输延迟、减小信号的反射和串扰等。

匹配阻抗是指信号传输线的特性阻抗和驱动源的输出阻抗、接收端的输入阻抗之间的匹配。

通常使用差分传输线来提高信号传输的抗干扰能力。

其次,减少信号干扰和噪声也是高速PCB设计的关键。

信号干扰和噪声会导致信号失真、抖动增大以及误码率的提高。

为了减少信号干扰和噪声,可以采取以下措施:布局合理,将高频和低频信号分开布局,并采用屏蔽、隔离和距离阻隔等措施;使用电源和地线的抗干扰设计,采用分析电源和地线的布线方向,减小供电线上的回流环路;使用合适的解耦电容和滤波电容来过滤电源中的噪声。

最后,提高信号的传输效率和可靠性也是高速PCB设计的一项重要任务。

提高信号的传输效率可以通过优化信号的传输线路、增强信号的驱动能力和改善信号的接收灵敏度等方式来实现。

优化信号的传输线路包括减小传输线路的长度和阻抗变化、优化信号传输线的走向等。

增强信号的驱动能力可以采用提高驱动电流和降低输出电阻的方法。

改善信号的接收灵敏度可以通过增大接收电路的增益和降低信号的噪声背景。

总结起来,高速PCB设计需要充分考虑信号完整性、信号干扰和噪声的影响因素,并通过匹配阻抗、减少信号反射和串扰、布局合理、抗干扰设计、合适的解耦电容和滤波电容等措施来保证信号的传输效率和可靠性。

高速PCB设计对于电子设备的性能和稳定性有着重要的影响,是电子工程师需要重视和掌握的技能之一。

Cadence高速电路板设计与仿真第5版是一本针对高速电路板设计和仿真的重要参考书籍。

本书包含了大量实例,通过对这些实例的学习和实操,读者可以更好地掌握高速电路板设计与仿真的核心知识和技术。

接下来,我们将通过对这本书第5版的实例进行深入分析,来探讨其中的一些重要内容。

一、实例一:差分传输线的设计与仿真在本书的第5版中,作者详细介绍了差分传输线的设计与仿真。

通过对这个实例的学习,读者可以学习到差分传输线的基本原理、设计方法以及仿真技术。

本书还通过具体的案例分析,详细解释了如何在实际项目中进行差分传输线的设计与仿真,以及如何应对常见的问题和挑战。

通过对这个实例的学习,读者可以获得丰富的经验和技巧,从而更好地应用到实际工程中去。

二、实例二:串扰分析与抑制技术在高速电路板设计与仿真中,串扰是一个非常重要的问题。

在第5版的实例中,作者对串扰分析与抑制技术进行了深入的讲解。

通过对这个实例的学习,读者可以了解到串扰的产生机理、分析方法以及抑制技术。

本书还介绍了一些常用的抑制技术,并通过实例分析,详细解释了如何在实际项目中应对串扰问题。

通过对这个实例的学习,读者可以获得丰富的实战经验,从而更好地解决实际项目中遇到的串扰问题。

三、实例三:高速电路板布线与阻抗控制高速电路板的布线和阻抗控制是高速信号传输中非常关键的问题。

在第5版的实例中,作者对高速电路板布线与阻抗控制进行了详细的介绍和讲解。

通过对这个实例的学习,读者可以了解到高速电路板布线的基本原理、布线技术以及阻抗控制方法。

本书还通过实例分析,详细解释了在实际项目中如何进行高速电路板布线和阻抗控制,以及如何应对常见的问题和挑战。

通过对这个实例的学习,读者可以获得丰富的经验和技巧,从而更好地应用到实际工程中去。

四、实例四:高速电路板仿真与调试在实际工程中,高速电路板的仿真和调试是非常重要的环节。

在第5版的实例中,作者对高速电路板仿真与调试进行了深入的讲解。

通过对这个实例的学习,读者可以了解到高速电路板仿真的基本原理、仿真工具和调试技术。

ADI的高速PCB设计The World Leader in High Performance Signal Processing SolutionsA Practical Guide toHigh-Speed Printed CircuitBoard LayoutAgendaOverviewSchematicLocation location locationLocation, location, locationPower supply bypassingParasiticsGround and power planesPackagingRF Signal routing and shielding SummaryOverviewPCB layout is one of the last steps in the design process and often one of the most criticalHigh-speed circuit performance is heavily dependant onHigh speed circuit performance is heavily dependant on layoutA high-performance design can be rendered useless due to a poor or sloppy layoutpoor or sloppy layoutToday’s presentation will help:p y pz Improve the layout processz Ensure expected circuit performance is achievedz Reduce design timeL tz Lower costz Lower stress for you and the PCB designerThe World Leader in High Performance Signal Processing SolutionsSchematicSchematicA good layout starts with a good Schematic! Schematic flow and contentInclude as much information as you canInclude as much information as you canWhat should you include?Items to Include on a Schematic N tNotesComponent tolerances and case sizesPart numbers (internal/external/alternative)Board stack upTests or alignment procedurespPower dissipationControlled impedance and line matchingComponent de-ratingThermal requirementsThermal requirementsKeep outsMechanical considerationsCritical component placementCritical component placementWarning flagsWhat ever else you can think of!SchematicThe World Leader in High Performance Signal ProcessingSolutionsLocation, location, location! Location location location!Location, Location, LocationLocation Location LocationJust as in real estate location is everything!Input/output and power connections are typically defined…Everything else is undefinedd fi d E thi l i d fi dz Critical component placementSignal routingz Signal routingz Circuit and component proximityThe World Leader in High Performance Signal Processing SolutionsPower Supply BypassingPower Supply Bypassing Bypassing is essential tohigh speed circuitpperformanceCapacitors right at powersupply pinsCapacitors provide low ACz Capacitors provide low ACimpedance to groundz Provide local charge storagefor fast rising/falling edgesf f t i i/f lli dPower Supply Bypassing Bypassing is essential tohigh speed circuit performance +V S L1pCapacitors right at power supply pins Capacitors provide low ACC10.1μF1μHz Capacitors provide low AC impedance to ground z Provide local charge storage f f t i i /f lli dμfor fast rising/falling edges Keep trace lengths short EQUIVALENT DECOUPLED POWERLINE CIRCUIT RESONATES AT:f =1f =2πLC√f = 500kHzPower Supply BypassingBypassing is essential tohigh speed circuitpperformanceCapacitors right at powersupply pinsCapacitors provide low ACz Capacitors provide low ACimpedance to groundz Provide local charge storagefor fast rising/falling edgesf f t i i/f lli dKeep trace lengths shortPower Supply BypassingBypassing is essential tohigh speed circuitpperformanceCapacitors right at powersupply pinsCapacitors provide low ACz Capacitors provide low ACimpedance to groundz Provide local charge storagefor fast rising/falling edgesf f t i i/f lli dKeep trace lengths shortClose to load returnClose to load returnz Helps minimize transientcurrents in the ground planePower Supply BypassingB i i ti l tBypassing is essential to high speed circuit performanceC i i hCapacitors right at power supply pinsz Capacitors provide low ACi d t dimpedance to groundz Provide local charge storage for fast rising/falling edges K t l th h tKeep trace lengths short Close to load returnz Helps minimize transient pcurrents in the ground planeValuesz Individual circuit performance d dua c cu t pe o a cePower Supply Bypassing B i i ti l tBypassing is essential tohigh speed circuitperformanceC i i hCapacitors right at powersupply pinsz Capacitors provide low ACimpedance to groundz Provide local charge storage for fast rising/falling edgesKeep trace lengths shortKeep trace lengths shortClose to load returnz Helps minimize transient currents in the ground planein the ground planeValuesz Individual circuit performance Maintains low AC impedancez Maintains low AC impedancePower Supply Bypassing B i i ti l t Bypassing is essential tohigh speed circuitperformanceCapacitors right at power Capacitors right at powersupply pinsz Capacitors provide low ACP id l l h t fz Provide local charge storage forfast rising/falling edgesKeep trace lengths shortClose to load returnClose to load returnz Helps minimize transient currentsin the ground planeValuesz Individual circuit performancez Maintains low AC impedancez Multiple resonancesPower Supply Bypassing B i i ti l t hi hBypassing is essential to high speed circuit performance Capacitors right at powersupply pinssupply pinsz Capacitors provide lowimpedance AC returnProvide local charge storage forz Provide local charge storage forfast rising/falling edgesKeep trace lengths shortClose to load returnz Helps minimize transient currentsin the ground planeValuesz Individual circuit performancez Maintains low AC impedancez Multiple resonancesFerrite beadsThe World Leader in High Performance Signal Processing SolutionsParasitics。