微电子工艺(3)----第三章外延

- 格式:ppt

- 大小:3.23 MB

- 文档页数:74

毕业论文简介外延抑制自掺杂技术研究应用物理2班 08510233 伏瑜指导老师:王青 ( 教授) 杜金生 (工程师)摘要外延层杂质浓度是影响电学性能的重要参数,外延掺杂存在有意识掺杂和无意识掺杂(即自掺杂),自掺杂影响外延生长。

自掺杂降低了衬底/外延界面过渡区的陡峭程度,同时也增加了外延淀积过程中的本底浓度。

不但对外延层的电阻率控制带来相当大的困难,使外延层界面处杂质分布梯度变缓,外延层有效厚度减薄,PN结击穿电压的显著降低,晶体管的大电流特性变坏,特别不利于要求薄而界面处杂质分布陡的外延层的微波器件的制造。

而且一些有害杂质的存在,还会使噪声增加等。

本文对外延淀积过程中自掺杂的产生进行了分析,提出了在外延淀积过程中可以通过改变压力、温度、及采用HCl腐蚀抛光技术、背封技术、H2烘烤赶气技术、二步外延技术等方法来解决外延自掺杂,从而改善器件的特性参数。

关键词:外延淀积自掺杂AbstractThe impurity concentration is a key parameter which has an effect on the electrical performance of the device in the epitaxy, the doping of epitaxy exists conscious and unconscious doping (i.e, self-doping), the growth of epitaxy is influenced by self-doping. Since the self-doping reduced the steep degree of substrate and the epitaxy interface of transition region, also increased background concentration in the process of the extension. It makes the control of the epitaxy,s resistivity difficult, the epitaxy of the interface between layer impurities distribution gradient slow, the epitaxy of effective thickness thin, the breakdown voltage of PN junction significantly reduce, and the current characteristics of transistor change bad, especially to the disadvantage of manufacturing microwave devices ,which were required thin and the distribution of the impurities were steep in the interface. And the existence of some harmful impurities, still can make noise up, etc.This paper analised the generation of self-doping during the epitaxial deposition , some techniques such as altering press, temperature,HCl rot, back-seal, H2expel,and two-step epitaxy, are proposed to improve the electrical charateristics of the device by reducing self-doping effect during epitaxial deposition.Key words:Epitaxy; Deposition;Self-doping;第一章外延技术概述1、概念所谓外延就是在一定的条件下,在单晶衬底上,沿原来的结晶方向生长一层导电类型、电阻率、厚度和晶格结构、完整性等都符合要求的新单晶层的工艺过程。

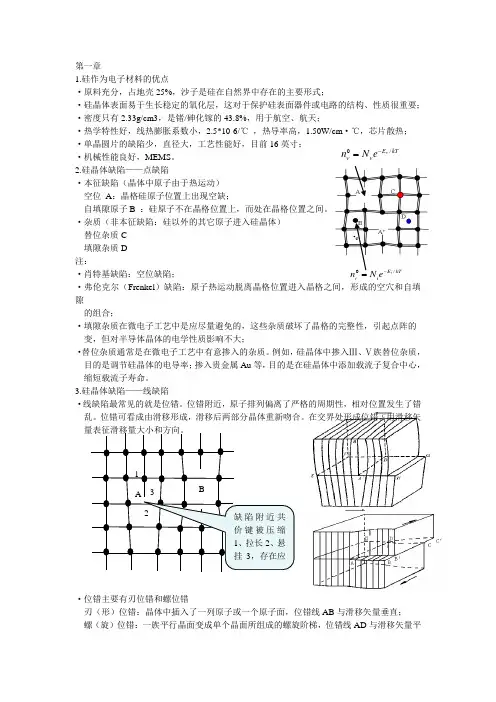

1.硅作为电子材料的优点·原料充分,占地壳25%,沙子是硅在自然界中存在的主要形式;·硅晶体表面易于生长稳定的氧化层,这对于保护硅表面器件或电路的结构、性质很重要; ·密度只有2.33g/cm3,是锗/砷化镓的43.8%,用于航空、航天;·热学特性好,线热膨胀系数小,2.5*10-6/℃ ,热导率高,1.50W/cm ·℃,芯片散热; ·单晶圆片的缺陷少,直径大,工艺性能好,目前16英寸;·机械性能良好,MEMS 。

2.硅晶体缺陷——点缺陷·本征缺陷(晶体中原子由于热运动) 空位 A :晶格硅原子位置上出现空缺;自填隙原子B :硅原子不在晶格位置上,而处在晶格位置之间。

·杂质(非本征缺陷:硅以外的其它原子进入硅晶体) 替位杂质C 填隙杂质D 注:·肖特基缺陷:空位缺陷; ·弗伦克尔(Frenkel )缺陷:原子热运动脱离晶格位置进入晶格之间,形成的空穴和自填隙的组合;·填隙杂质在微电子工艺中是应尽量避免的,这些杂质破坏了晶格的完整性,引起点阵的 变,但对半导体晶体的电学性质影响不大; ·替位杂质通常是在微电子工艺中有意掺入的杂质。

例如,硅晶体中掺入Ⅲ、Ⅴ族替位杂质, 目的是调节硅晶体的电导率;掺入贵金属Au 等,目的是在硅晶体中添加载流子复合中心, 缩短载流子寿命。

3.硅晶体缺陷——线缺陷·线缺陷最常见的就是位错。

位错附近,原子排列偏离了严格的周期性,相对位置发生了错 乱。

位错可看成由滑移形成,滑移后两部分晶体重新吻合。

在交界处形成位错。

用滑移矢量表征滑移量大小和方向。

·位错主要有刃位错和螺位错刃(形)位错:晶体中插入了一列原子或一个原子面,位错线AB与滑移矢量垂直; 螺(旋)位错:一族平行晶面变成单个晶面所组成的螺旋阶梯,位错线AD 与滑移矢量平kT E v v e N n /0-=νkTE i i i e N n /0-=1 23 BA 缺陷附近共价键被压缩1、拉长2、悬挂3,存在应力·刃形位错的两种运动方式:滑移和攀移。

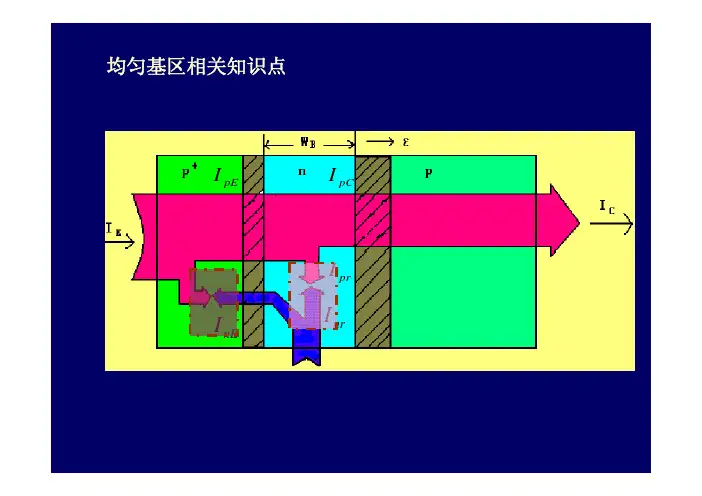

均匀基区相关知识点I pEI pCI prI nEI nr相关公式β∗W B2 τb =1− =1− 2 2 LB τBD EW B N B WBρE γ = 1− D W N = 1− W ρ B E E E B⎛ W B2 α =⎜ ⎜1 − 2 L2 B ⎝2 B 2 BR口E = 1− R口B1⎞⎛ R口E ⎞ W B2 R口E ⎟ ⎟⎜ ⎟ ≈ 1 − 2 L2 − R ⎜1 − R ⎟ 口 B1 ⎠ B 口 B1 ⎠⎝⎛W R口E ⎜ β ≈⎜ + R口B1 ⎝ 2L⎞ ⎟ ⎟ ⎠−1§3-3 缓变基区晶体管的放大系数以NPN 管为例,结电压为 VBE 与 VBC 。

现代晶体管,如双扩散外延平面管 属缓变基区晶体管,由于载流子在 基区主要是以漂移运动在传输,故 它又称为 漂移晶体管。

N+0PN杂质浓度分布图:x jE x jCWB = x jC − x jEN E ( x) N B ( x)NC0x jE x jCx1、基区内建电场的形成与求解 形成的物理机理(以P型基区的Xmb-Xjc段为例)xjE 和xjC为发射结 和集电结结深, xmB为杂质补偿后 基区净杂质浓度 的极值位置杂质浓度高的地方留下不 可移动的电离杂质电荷 (NA-),杂质浓度低的地 方积累多子(空穴)杂质(NA) 浓度梯度杂质电离多子(空 穴) 浓度梯度多子(空 穴) 扩散正负电荷 分离内建电场内建电场的作用 漂移晶体管电场方向:指向发射结 加速场 电场作用: 基区的少子(电子) 向集电结方向漂移运 动,对少子有加速作用 向发射结方向漂移运动, 抵消多子扩散运动 多子电流等于零基区的多子(空穴)xjE到xmB段,将产生一个与EB方向相反的自建电场EB’,它将阻止 基区中少子(电子)流向集电结,称阻滞电场,该部分基区称阻 滞区。

一般情况下,相对与整个基区而言,阻滞区很窄,一般可以忽略。

请从以下几方面总结半导体器件中的内建电场① 掺杂不均匀产生的内建电场 ~ 产生机理? 对多数载流子运动的影响? 对少数载流子运动的影响? ② 大注入产生的内建电场 ~ 产生机理? 对多数载流子运动的影响? 对少数载流子运动的影响 ? ③ p-n结中的内建电场 ~ 产生机理? 势垒区(阻挡层)→阻挡多数载流子还是阻挡少数载流子? 耗尽层近似?→ 耗尽什么种类的载流子?三个内建电场形成机理的比较内建电场种类形成原因 P区与N区刚接触 时冶金结两边存 在自由载流子浓 度差 大注入时中性区 多子具有浓度梯 度分布电荷分离的表现形式 冶金结两边自由载流子扩散,留下不 可移动的电离施主和受主杂质电荷在 空间上分离 多子与少子同时扩散,但由于多子扩 散得不到补充,最终使得靠近耗尽区 少子浓度高于多子浓度,远离耗尽区 边界少子浓度低于多子浓度,最终多 子与少子电荷在空间上分离 多子浓度扩散,使得靠近发射结耗尽 区的电离杂质电荷高于多子,靠近集 电结耗尽区的电离杂质电荷低于多 子,造成电离杂质电荷与多子电荷在 空间上分离作用 载流子的扩散运 动等于漂移运动PN结空间电 荷区内建电 场 大注入PN结 中性区中的 内建电场 (自建场) 缓变基区BJT 中基区内建 电场多子的扩散运动 与漂移运动抵 消,加强少子扩 散运动 多子的扩散运动与 漂移运动抵消,少 子在基区以漂移运 动为主掺杂原子具有浓 度梯度,多子具 有相同的浓度梯 度分布基区内建电场表达式的推导 设基区杂质浓度分布为:NB (0)NB (x)⎛ ηx ⎞ N B ( x ) = N B ( 0 ) exp ⎜ ⎜− W ⎟ ⎟ B ⎠ ⎝ 式中 η 是表征基区内杂质变化程度的一个参数:NB (WB )0WBxN B (W B ) = N B ( 0 ) exp (− η )N B (0) η = ln N B (W B )当 η = 0 时为均匀基区。

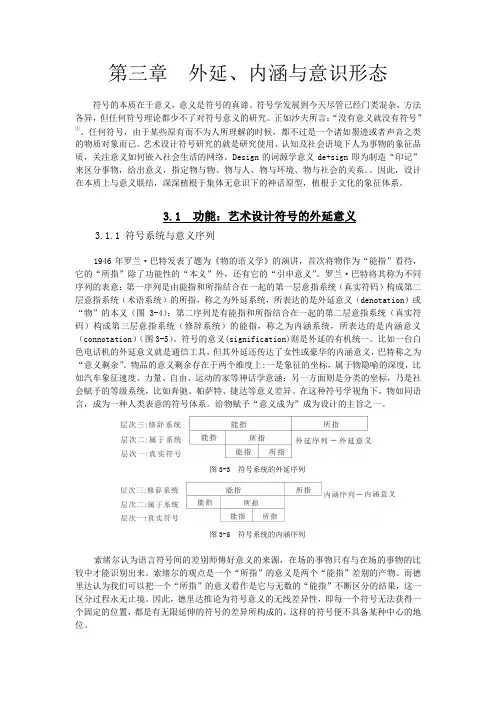

第三章外延、内涵与意识形态符号的本质在于意义,意义是符号的真谛。

符号学发展到今天尽管已经门类混杂,方法各异,但任何符号理论都少不了对符号意义的研究。

正如沙夫所言:“没有意义就没有符号”①。

任何符号,由于某些原有而不为人所理解的时候,都不过是一个诸如墨迹或者声音之类的物质对象而已。

艺术设计符号研究的就是研究使用、认知及社会语境下人为事物的象征品质,关注意义如何嵌入社会生活的网络。

Design的词源学意义de+sign即为制造“印记”来区分事物,给出意义,指定物与物、物与人、物与环境、物与社会的关系。

因此,设计在本质上与意义联结,深深植根于集体无意识下的神话原型,植根于文化的象征体系。

3.1 功能:艺术设计符号的外延意义3.1.1 符号系统与意义序列1946年罗兰·巴特发表了题为《物的语义学》的演讲,首次将物作为“能指”看待,它的“所指”除了功能性的“本义”外,还有它的“引申意义”。

罗兰·巴特将其称为不同序列的表意:第一序列是由能指和所指结合在一起的第一层意指系统(真实符码)构成第二层意指系统(术语系统)的所指,称之为外延系统,所表达的是外延意义(denotation)或“物”的本义(图3-4);第二序列是有能指和所指结合在一起的第二层意指系统(真实符码)构成第三层意指系统(修辞系统)的能指,称之为内涵系统,所表达的是内涵意义(connotation)(图3-5)。

符号的意义(signification)则是外延的有机统一。

比如一台白色电话机的外延意义就是通信工具,但其外延还传达了女性或豪华的内涵意义,巴特称之为“意义剩余”。

物品的意义剩余存在于两个维度上:一是象征的坐标,属于物隐喻的深度,比如汽车象征速度、力量、自由、运动的家等神话学意涵;另一方面则是分类的坐标,乃是社会赋予的等级系统,比如奔驰、帕萨特、捷达等意义差异。

在这种符号学视角下,物如同语言,成为一种人类表意的符号体系。

一、名词解释1.水汽氧氧化:氧化(氧气)中携带一定量的水气,氧化特性介于干氧与湿氧之间。

2.恒定源扩散:在扩散过程中,硅片表面的杂质浓度N s始终保持不变。

例如,基区、发射区的预淀积,箱法扩散。

3.扩散系数:描述粒子扩散快慢的物理量,是微观扩散的宏观描述。

4.外延:一种在单晶或多晶衬底上生长一层单晶或多晶薄膜的技术。

5.分辨率:光刻时所能得到的光刻图形的最小尺寸,用来表征光刻的精度。

二、简述问答题2.微电子器件对接触和互连有什么要求?获得良好欧姆接触的方法有哪几种?答:对接触和互连有的基本要求有:1)能形成良好的欧姆接触;2)互连材料具有低的电阻率和良好的稳定性;3)可被精细刻蚀;4)易淀积成膜;5)粘附性好;6)强的抗电迁移能力;7)便于键合。

获得良好欧姆接触的方法有:1)高掺杂欧姆接触;2)低势垒欧姆接触;3)高复合欧姆接触。

4.简述电子束曝光的特点答:1)优点:分辨率比光学曝光高;无需光刻板;曝光自动化,加工精度高;在真空中进行;可直接观察曝光的质量。

2)缺点:设备复杂,成本高;产量低;存在邻近效应。

5.X光衍射晶体定向的基本原理是什么?答:1)入射角λ应满足:nλ=2dsinθ;2)晶面密勒指数(hkl)应满足:h2+k2+l2=4n-1(n为奇数),以与h2+k2+l2=4n(n为偶数)。

一、名词解释1.Moore定律:集成电路的集成度每3年增长4倍;特征尺寸每3年减小平方根2倍。

2. 分辨率:表征光刻精度,即光刻时所能得到的光刻图形的最小尺寸。

3.结深:pn结的几何位置与扩散层表面的距离。

5.欧姆接触:当金属与半导体的接触电阻小到可忽略不计时,称为欧姆接触。

二、选择与填空题1.在温度相同的情况下,制备相同厚度的氧化层,分别用干氧,湿氧和水汽氧化,哪个需要的时间最长?(A)A.干氧B.湿氧C.水汽氧化2.二氧化硅膜能有效的对扩散杂质起掩蔽作用的基本条件有(B)①杂质在硅中的扩散系数大于在二氧化硅中的扩散系数②杂质在硅中的扩散系数小于在二氧化硅中的扩散系数③二氧化硅的厚度大于杂质在二氧化硅中的扩散深度④二氧化硅的厚度小于杂质在二氧化硅中的扩散深度A.②④ B. ①③C①④ D. ②③3.离子注入与热扩散相比,哪个横向效应小(A )A. 离子注入B. 热扩散4.在LPCVD中由于hG>>kS,质量转移系数远大于表面反应速率常杂质。

第三章外延、内涵与意识形态符号的本质在于意义,意义是符号的真谛。

符号学发展到今天尽管已经门类混杂,方法各异,但任何符号理论都少不了对符号意义的研究。

正如沙夫所言:“没有意义就没有符号”①。

任何符号,由于某些原有而不为人所理解的时候,都不过是一个诸如墨迹或者声音之类的物质对象而已。

艺术设计符号研究的就是研究使用、认知及社会语境下人为事物的象征品质,关注意义如何嵌入社会生活的网络。

Design的词源学意义de+sign即为制造“印记”来区分事物,给出意义,指定物与物、物与人、物与环境、物与社会的关系。

因此,设计在本质上与意义联结,深深植根于集体无意识下的神话原型,植根于文化的象征体系。

3.1 功能:艺术设计符号的外延意义3.1.1 符号系统与意义序列1946年罗兰·巴特发表了题为《物的语义学》的演讲,首次将物作为“能指”看待,它的“所指”除了功能性的“本义”外,还有它的“引申意义”。

罗兰·巴特将其称为不同序列的表意:第一序列是由能指和所指结合在一起的第一层意指系统(真实符码)构成第二层意指系统(术语系统)的所指,称之为外延系统,所表达的是外延意义(denotation)或“物”的本义(图3-4);第二序列是有能指和所指结合在一起的第二层意指系统(真实符码)构成第三层意指系统(修辞系统)的能指,称之为内涵系统,所表达的是内涵意义(connotation)(图3-5)。

符号的意义(signification)则是外延的有机统一。

比如一台白色电话机的外延意义就是通信工具,但其外延还传达了女性或豪华的内涵意义,巴特称之为“意义剩余”。

物品的意义剩余存在于两个维度上:一是象征的坐标,属于物隐喻的深度,比如汽车象征速度、力量、自由、运动的家等神话学意涵;另一方面则是分类的坐标,乃是社会赋予的等级系统,比如奔驰、帕萨特、捷达等意义差异。

在这种符号学视角下,物如同语言,成为一种人类表意的符号体系。

1、分立器件和集成电路的区别分立元件:每个芯片只含有一个器件;集成电路:每个芯片含有多个元件..2、平面工艺的特点平面工艺是由Hoerni于1960年提出的..在这项技术中;整个半导体表面先形成一层氧化层;再借助平板印刷技术;通过刻蚀去除部分氧化层;从而形成一个窗口..P-N结形成的方法:①合金结方法A、接触加热:将一个p型小球放在一个n型半导体上;加热到小球熔融..B、冷却:p型小球以合金的形式掺入半导体底片;冷却后;小球下面形成一个再分布结晶区;这样就得到了一个pn结..合金结的缺点:不能准确控制pn结的位置..②生长结方法半导体单晶是由掺有某种杂质例如P型的半导体熔液中生长出来的..生长结的缺点:不适宜大批量生产..扩散结的形成方式与合金结相似点:表面表露在高浓度相反类型的杂质源之中与合金结区别点:不发生相变;杂质靠固态扩散进入半导体晶体内部扩散结的优点扩散结结深能够精确控制..平面工艺制作二极管的基本流程:衬底制备——氧化——一次光刻刻扩散窗口——硼预沉积——硼再沉积——二次光刻刻引线孔——蒸铝——三次光刻反刻铝电极——P-N结特性测试3、微电子工艺的特点高技术含量设备先进、技术先进..高精度光刻图形的最小线条尺寸在亚微米量级;制备的介质薄膜厚度也在纳米量级;而精度更在上述尺度之上..超纯指工艺材料方面;如衬底材料Si、Ge单晶纯度达11个9..超净环境、操作者、工艺三个方面的超净;如 VLSI在100级超净室10级超净台中制作..大批量、低成本图形转移技术使之得以实现..高温多数关键工艺是在高温下实现; 如:热氧化、扩散、退火 ..4、芯片制造的四个阶段固态器件的制造分为4个大的阶段粗线条:①材料制备②晶体生长/晶圆准备③晶圆制造、芯片生成④封装晶圆制备:1获取多晶2晶体生长----制备出单晶;包含可以掺杂元素掺杂和母金掺杂3硅片制备----制备出空白硅片硅片制备工艺流程从晶棒到空白硅片:晶体准备直径滚磨、晶体定向、导电类型检查和电阻率检查→切片→研磨→化学机械抛光CMP→背处理→双面抛光→边缘倒角→抛光→检验→氧化或外延工艺→打包封装芯片制造的基础工艺增层——光刻——掺杂——热处理5、high-k技术High—K技术是在集成电路上使用高介电常数材料的技术;主要用于降低金属化物半导体MOS晶体管栅极泄漏电流的问题..集成电路技术的发展是伴随着电路的元器件如MOS晶体管结构尺寸持续缩小实现的..随着MOS晶体管结构尺寸的缩小;为了保持棚极对MOS晶体管沟道电流的调控能力;需要在尺寸缩小的同时维持栅极电容的容量;这通常需要通过减小棚极和沟道之间的绝缘介质层厚度来实现;但由此引起的棚极和沟道之间的漏电流问题越来越突出..High—K技术便是解决这一问题的优选技术方案..因为;MOS器件栅极电容类似于一个平板电容;由于MOS器件面积、绝缘介质层厚度和介电常数共同决定;因此MOS器件栅极电容在器件面积减小的前提下;采用了High—K材料后;可以在不减小介质层厚度因此栅极泄漏电流而不增加的前提下;实现维护栅极电容容量不减小的目标.. High—K材料技术已被英特尔和IBM应用到其新开发的45mm 量产技术中..目前业界常用的High—K材料主要是包括HfO在内的Hf基介质材料..26、拉单晶的过程装料——融化——种晶——引晶——放肩——等径——收尾——完成7、外延技术的特点和应用外延特点:生成的晶体结构良好掺入的杂质浓度易控制可形成接近突变pn结的特点外延分类:按工艺分类A 气相外延VPE利用硅的气态化合物或者液态化合物的蒸汽;在加热的硅衬底表面和氢发生反应或自身发生分解还原出硅..B 液相外延LPE衬底在液相中;液相中析出的物质并以单晶形式淀积在衬底表面的过程..此法广泛应用于III-V族化合半导体的生长..原因是化合物在高温下易分解;液相外延可以在较低的温度下完成..C 固相外延SPED 分子束外延MBE在超高真空条件下;利用薄膜组分元素受热蒸发所形成的原子或分子束;以很高的速度直接射到衬底表面;并在其上形成外延层的技术..特点:生长时衬底温度低;外延膜的组分、掺杂浓度以及分布可以实现原子级的精确控制..按导电类型分类n型外延:n/n; n/p外延 p型外延:p/n; p/p外延按材料异同分类同质外延:外延层和衬底为同种材料;例如硅上外延硅..异质外延:外延层和衬底为不同种材料;例如SOI绝缘体上硅是一种特殊的硅片;其结构的主要特点是在有源层和衬底层之间插入绝缘层———埋氧层来隔断有源层和衬底之间的电气连接按电阻率高低分类正外延:低阻衬底上外延高阻层n/n+反外延:高阻衬底上外延低阻层硅的气相外延的原理:在气相外延生长过程中;有两步:质量输运过程--反应剂输运到衬底表面表面反应过程--在衬底表面发生化学反应释放出硅原子掺杂有意掺杂:按器件对外延导电性和电阻率的要求;在外延的同时掺入适量的杂质;这称为有意掺杂..自掺杂:衬底中的杂质因挥发等而进入气流;然后重新返回外延层..杂质外扩散:重掺杂衬底中的杂质通过热扩散进入外延层..外延的应用1、双极型电路:n/n+外延;在n型外延层上制作高频功率晶体管..n/p外延:双极型传统工艺在p衬底上进行n型外延通过简单的p型杂质隔离扩散;实现双极型集成电路元器件的隔离..2、MOS电路:外延膜的主要应用是作为双极型晶体管的集电极..外延膜在MOS集成电路中的较新应用是利用重掺杂外延减小闩锁效应寄生闸流管效应..8、分子束外延MBE的原理及其应用在超高真空下;热分子束由喷射炉喷出;射到衬底表面;外延生长出外延层..9、二氧化硅膜的用途表面钝化:保护器件的表面及内部;禁锢污染物..掺杂阻挡层:作为杂质扩散的掩蔽膜;杂质在二氧化硅中的运行速度低于在硅中的运行速度..绝缘介质:IC器件的隔离和多层布线的电隔离;MOSFET的栅电极;MOS电容的绝缘介质..10、二氧化硅膜的获得方法A:热氧化工艺B:化学气相淀积工艺C:溅射工艺D:阳极氧化工艺11、热氧化机制①线性阶段;②抛物线阶段生长逐渐变慢;直至不可忍受影响氧化速率的因素有:氧化剂、晶向、掺杂类型和浓度、氧化剂的分压..热氧化生长方法:1干氧氧化:干燥氧气;不能有水分;随着氧化层的增厚;氧气扩散时间延长;生长速率减慢;适合/Si界面与硅反应..较薄的氧化层的生长..氧化剂扩散到SiO22水汽氧化:气泡发生器或氢氧合成气源;原理:3湿氧氧化:湿氧氧化的各种性能都是介于干氧氧化和水汽氧化之间;其掩蔽能力和氧化质量都能够满足一般器件的要求..4掺氯氧化:薄的MOS栅极氧化要求非常洁净的膜层;如果在氧化中加入氯;器件的性能和洁净度都会得到改善..减弱二氧化硅中的移动离子主要是钠离子的沾污影响;固定Na+离子;减少硅表面及氧化层的结构缺陷/Si界面特性:12、SiO2/Si界面杂质发生再分热氧化薄膜是由硅表面生长得到的二氧化硅薄膜..高温生长工艺将使SiO2布;与二氧化硅接触的硅界面的电学特性也将发生变化..杂质再分布:有三个因素:①分凝效应② 扩散速率③ 界面移动/Si界面杂质的再分布就远小于干氧氧化;湿氧水汽氧化速率远大于干氧氧化速率;水汽氧化SiO2氧化速率介于水汽、干氧之间;SiO/Si界面杂质的再分布也介于水汽、干氧之间..2/Si界面P-Si的反型层;以二氧化硅层中存在着与制备工艺有关的正电荷;这种正电荷将引起SiO2及MOS器件阈值电压不稳定等现象..可动离子或可动电荷主要是Na+、K+、H+ 等;这些离子在二氧化硅中都是网络修正杂质;为快扩散杂质..其中主要是Na+..在人体与环境中大量存在Na+;热氧化时容易发生Na+沾污..加强工艺卫生方可以避免Na+沾污;也可采用掺氯氧化;固定Na+离子..固定离子或固定电荷主要是氧空位..一般认为:固定电荷与界面一个很薄的约30 过渡区有关;过渡区有过剩的硅离子;过剩的硅在氧化过程中与晶格脱开;但未与氧完全反应..干氧氧化空位最少;水汽氧化氧空位最多..热氧化时;首先采用干氧氧化方法可以减小这一现象..氧化后;高温惰性气体中退火也能降低固定电荷..13、氧化膜厚度的检测劈尖干涉和双光干涉:利用干涉条纹进行测量;因为要制造台阶;所以为破坏性测量..比色法:以一定角度观察SiO2膜;SiO2膜呈现干涉色彩;颜色与厚度存在相应关系..比色法方便迅速;但只是粗略估计..椭圆仪法:入射的椭圆偏振光经氧化膜的多次反射和折射以后;得到了改变椭圆率的反射椭圆偏振光;其改变量和膜厚与折射率相关..高频MOS结构C-V法:测量金属栅极的电容;利用公式测量氧化膜层的厚度..14、化学气相沉积定义化学气相淀积Chemical Vapor Deposition是通过气态物质的化学反应在衬底上淀积薄膜的工艺方法..与之对应的是:PVD蒸发和溅射;它主要应用于导体薄膜..15、淀积技术包括哪两种CVD和PVD16、LPCVD和APCVD的主要区别 LPCVD有何优势APCVD:原料以气相方式被输送到反应器内;原料气体向衬底基片表面扩散;被基片吸附;由于基片的温度高或其它能量提供给原料气体;使其发生表面化学反应;生成物在基片表面形成薄膜;而生成物中的其它物质是气相物质;扩散到气相中被带走..LPCVD:低压情况下;分子自由程较长;薄膜电极的均匀性较高..LPCVD相对APCVD的特点:增加了真空系统;气压在1-10-2Torr之间;压下分子自由程长;可以竖放基片;热系统一般是电阻热壁式..17、PECVD的机理 PECVD有何优势优势:采用等离子体把电能耦合到气体中;促进化学反应进行;由此淀积薄膜;因此该法可以在较低温度下淀积薄膜..PECVD常常是低温和低压的结合..机理:反应器的射频功率使低压气体真空度1-10Torr产生非平衡辉光放电;雪崩电离激发出的高能电子通过碰撞激活气体形成等离子体..衬底基片具有一定温度;约300℃吸附活泼的中性原子团与游离基即高能的等离子体发生化学反应;生成的薄膜物质被衬底吸附、重排进而形成淀积薄膜;衬底温度越高形成的薄膜质量越好..18、多晶硅淀积和外延淀积的主要区别..淀积多晶硅薄膜的方法:主要采用LPCVD的方法..掺杂则采用:离子注入;化学气相淀积;扩散..多晶硅的淀积和外延淀积的主要区别:硅烷的使用19、金属薄膜的用途金属化的作用1在微电子器件与电路中金属薄膜最重要的用途是作为内电极MOS栅极和电容器极板和各元件之间的电连接..2在某些存储电路中作为熔断丝..3 用于晶圆的背面通常是金;提高芯片和封装材料的黏合力..金属化的作用:集成电路中金属化的作用是将有源器件按设计的要求连接起来;形成一个完整的电路与系统..20、说明为什么铝作为通常使用的金属薄膜; 说明铜作为新一代金属薄膜的原因..铝膜:用途: 大多数微电子器件或集成电路是采用铝膜做金属化材料优点:导电性较好;与p-Si;n+-Si>51019 能形成良好的欧姆接触;光刻性好;与二氧化硅黏合性好;易键合..缺点:抗电迁移性差;耐腐蚀性、稳定性差;台阶覆盖性较差..工艺:蒸发;溅射铜膜:用途:新一代的金属化材料;超大规模集成电路的内连线;缺点:与硅的接触电阻高;不能直接使用;铜在硅中是快扩散杂质;能使硅中毒;铜进入硅内改变器件性能;与硅、二氧化硅粘附性差..优点:电阻率低只有铝的40-45% ;导电性较好;抗电迁移性好于铝两个数量级;工艺:溅射21、VLSI对金属化的要求是什么①对n+硅和p+硅或多晶硅形成低阻欧姆接触;即金属/硅接触电阻小②能提供低电阻的互连引线;从而提高电路速度③抗电迁移性能要好④与绝缘体如二氧化硅有良好的附着性⑤耐腐蚀⑥易于淀积和刻蚀⑦易键合;且键合点能经受长期工作⑧层与层之间绝缘要好;不互相渗透和扩散;即要求有一个扩散阻挡层22、Al-Si接触的常见问题及解决办法Al和Si之间不能合成硅化物;但是可以形成合金..Al在Si中溶解度很小;但是相反Si在Al中溶解度很大;这样就形成尖楔现象;从而使P-N结失效..解决尖楔问题:(1)一般采用Al-Si合金代替Al作为Al/Si的接触和互连材料..但是又引入了硅的分凝问题..(2)由于铜的抗电迁移性好;铝-铜0.5-4%或铝-钛0.1-0.5%合金结构防止电迁移;结合Al-Si 合金;在实际应用中人们经常使用既含有铜又含有硅的Al-Si-Cu合金以防止合金化即共熔问题和电迁移问题..(3)Al-掺杂多晶硅双层金属化结构:在多晶硅中掺杂重磷或重砷;构成掺杂多晶的结构..(4)铝-隔离层结构:在Al-Si之间沉积一层薄的金属层;替代磷掺杂多晶硅;成为阻挡层..23、说明难熔金属在金属连线中的作用难熔金属及其硅化物有较低的电阻率和接触电阻..难熔金属的一个广泛应用是在多层金属结构中填充连接孔;这个工序叫作过孔填充;填补好的过孔叫做接线柱..24、金属化的实现方法有几种请论述真空溅射方法金属化的实现主要通过两种方式来实现:①物理淀积A:真空蒸发淀积较早;金属铝线B:真空溅射淀积Al-Si合金或Al-Si-Cu合金错误!LPCVD难熔金属真空蒸发淀积:被蒸物质从凝聚相转化为气相;气相物质在真空系统中的输运;气相分子在衬底上淀积和生长..分为电阻、电子束等蒸发沉积..真空溅射沉积:溅射淀积是用核能离子轰击靶材;使靶材原子从靶表面逸出;淀积在衬底材料上的过程..25、说明金属CVD的优势和主要用途..金属CVD :LPCVD可以应用于制作金属薄膜..优势:不需要昂贵的高真空泵;台阶覆盖性好;生产效率较高..用途:难控制金属;难熔金属;主要是钨..26、什么叫做光刻;光刻有何目的光刻是图形复印与腐蚀作用相结合;在晶片表面薄膜上制备图形的精密表面工艺技术..光刻的目的就是:在介质薄膜、金属薄膜或金属合金薄膜上面刻蚀出与掩膜版完全对应的几何图形;从而实现选择性扩散和金属薄膜布线的目的..27、光刻技术的图形转移分为哪两个阶段图形转移到光刻胶层;图形从光刻胶层转移到晶圆层28、列出光刻工艺的十个步骤;并简述每一步的目的..表面准备:微粒清除;保持衬底的憎水性..涂光刻胶:与衬底薄膜粘附性好;胶膜均匀;是光刻工艺的核心材料..前烘:使胶膜体内的溶剂充分挥发使胶膜干燥;增加胶膜和衬底的粘附性以及胶膜的耐磨性对准和曝光:把所需图形在晶圆表面上定位或对准;通过曝光灯或其他辐射源将图形转移到光刻胶涂层上后烘:减少效应;激发化学增强的PAG产生的酸与光刻胶上的保护发生反应并移除基团使之能溶解于显影液..显影:将掩膜板上的图形显示在光刻胶上..坚膜:除去光刻胶中剩余的溶剂;增强光刻胶对衬底的附着力..刻蚀:把显影后的光刻胶微图形下层材料的裸露部分去掉;将光刻胶图形转移到下层材料上去的工艺叫作刻蚀..去胶:刻蚀完成以后将光刻胶去除掉..29、光刻胶的分类;谈谈正胶和负胶的区别..正胶:胶的曝光区在显影中除去..正胶曝光时发生光分解反应变成可溶的..使用这种光刻胶时;能够得到与掩膜版遮光图案相同的图形;故称之为正胶..负胶:胶的曝光区在显影中保留;用的较多..具体说来负胶在曝光前对某些有机溶剂是可溶的;而曝光后发生光聚合反应变成不可溶的..使用这种光刻胶时;能够得到与掩膜版遮光图案相反的图形;故称之为负胶..30、刻蚀的方法分类;刻蚀常见有哪些问题分类:刻蚀分为湿法刻蚀和干法刻蚀..湿法刻蚀:化学腐蚀;在腐蚀液中通过化学反应去除窗口薄膜;得到薄膜图形..优点:工艺简单;无需复杂设备;选择比高;均匀性好..缺点:各向同性腐蚀;分辨率低;自动化难..干法刻蚀:使用气体和等离子体能量来进行化学反应的化学工艺..常见问题:不完全刻蚀、刻蚀和底切、各向同性刻蚀..优点:刻蚀非常有方向性各向异性;导致良好的小开口区域的精密度..缺点:选择性差..31、掺杂技术实现的两种方式以及掺杂的目的方式:扩散和离子注入目的:在晶圆表面下的特定位置处形成PN结;在晶圆表面下得到所需的掺杂浓度..32、扩散的基本原理、离子注入的基本原理及其比较微电子工艺中的扩散是杂质在晶体内的扩散;因此是一种固相扩散..晶体内扩散有多种形式:填隙式扩散、替位式扩散、填隙-替位式扩散..离子注入技术:离子注入是将含所需杂质的化合物分子如BCl3、BF3电离为杂质离子后;聚集成束用强电场加速;使其成为高能离子束;直接轰击半导体材料;当离子进入其中时;受半导体材料原子阻挡;而停留在其中;成为半导体内的杂质..离子注入时可采用热退火工艺;修复晶格损伤;注入杂质电激活..离子注入技术的优势:①离子注入克服热扩散的几个问题:A 横向扩散;没有侧向扩散B 浅结C 粗略的掺杂控制D 表面污染的阻碍②离子注入引入的额外的优势:A 在接近常温下进行B 使宽范围浓度的掺杂成为可能33、集成电路的形成集成电路的制造工艺与分立器件的制造工艺一样都是在硅平面工艺基础上发展起来的;有很多相同之处;同时又有所不同..相同点:单项工艺相同的方法外延;氧化;光刻;扩散;离子注入;淀积等..不同点:主要有电隔离;电连接;局部氧化;平整化以及吸杂等..电隔离:1PN结隔离:双极型集成电路多采用PN结隔离;是在硅片衬底上通过扩散与外延等工艺制作出隔离岛;元件就做在隔离岛上..2介质隔离:SOS集成电路Silicon on Sapphire 是最早的介质隔离薄膜电路;新材料SOISilicon on Insulator有很大发展;SOI集成电路也是采用介质隔离工艺的电路..电连接:集成电路各元件之间构成电路必须进行电连接;这多是采用淀积金属薄膜;经光刻工艺形成电连接图形;电路复杂的集成电路一般是多层金属布线;构成电连接..局部氧化:分离器件的氧化工艺是在整个硅片表面制备二氧化硅薄膜;而集成电路工艺中的氧化有时是在局部进行;如MOS型电路中以氮化硅作为掩蔽膜的局部氧化技术..平整化:超大规模集成电路的制备经过多次光刻、氧化等工艺;使得硅片表面不平整;台阶高;这样在进行电连接时;台阶处的金属薄膜连线易断裂;因此;有时通过平面化技术来解决这一问题;如在金属布线进行电连接之前;采用在硅片表面涂附聚酰亚胺膜的方法达到平面化的工艺技术..吸杂:硅单晶本身的缺欠以及电路制备工艺中的诱生缺欠;对电路性能影响很大;有源元件附近的缺欠;通过吸杂技术可以消除或减少缺欠;如通过在硅片背面造成机械损伤;喷沙或研磨;这种背损伤可以吸收杂质与缺欠..34、封装的工艺流程底部准备:底部准备通常包括磨薄和镀金..划片:用划片法或锯片法将晶片分离成单个芯片取片和承载:在挑选机上选出良品芯片;放于承载托盘中..粘片:用金硅熔点技术或银浆粘贴材料粘贴在封装体的芯片安装区域..打线:A:芯片上的打线点与封装体引脚的内部端点之间用很细的线连接起来线压焊;B:在芯片的打线点上安装半球型的金属突起物反面球形压焊;C:TAB压焊技术;封装前检查有无污染物;芯片粘贴质量;金属连接点的好坏电镀、切割筋成和印字最终测试35、封装设计金属罐法;双列直插封装;双列直插封装;针形栅格阵列封装球形栅格阵列封装;薄形封装;四面引脚封装;板上芯片COB。