verilog-a 参考手册

- 格式:pdf

- 大小:2.66 MB

- 文档页数:413

veriloga基础语法VerilogA是一种硅谷团队开发的建模语言,它被广泛应用于集成电路(IC)的设计和仿真中。

本文旨在介绍VerilogA的基础语法。

1. 模块声明在VerilogA中,每个模块都需要进行声明。

声明的语法如下:module 模块名(输入端口1,输入端口2,...输入端口n,输出端口1,输出端口2,...输出端口m);<模块定义代码>endmodule其中,模块名可以由字母、数字和下划线组成,不能以数字开头;输入端口和输出端口可以是标量或向量。

2. 参数声明VerilogA允许在模块中声明参数,以便在实例化时进行配置。

语法如下:parameter 参数名 = 值;参数可以通过assign语句进行连接,也可以在实例化时进行配置。

3. 变量声明在VerilogA中,可以使用不同的变量类型进行声明,如实数、整数、布尔值等。

real: 实数类型,用于存储实数值。

integer: 整数类型,用于存储整数值。

boolean: 布尔类型,用于存储真/假值。

语法如下:real 变量名;integer 变量名;boolean 变量名;4. 函数和任务在VerilogA中,可以使用函数和任务来实现特定的功能。

函数是一段可重用的代码,它接收输入参数并返回一个值。

函数的语法如下:function 返回类型函数名(输入参数);<函数定义代码>return 返回值;endfunction任务是一段可重用的代码,不返回值,但可以通过参数进行输入和输出。

任务的语法如下:task 任务名(输入参数);<任务定义代码>endtask5. 运算符VerilogA支持各种常见的数学和逻辑运算符,如加减乘除、取余、与或非等。

加法运算符:+减法运算符:-乘法运算符:*除法运算符:/取余运算符:%与运算符:&&或运算符:||非运算符:!6. 控制结构在VerilogA中,可以使用if-else、for、while等控制结构来实现条件判断和循环。

(完整word版)Verilog-A30分钟快速入门教程.docxVerilog-A 30分钟快速入门教程进入正题,学了几天的Verilog-A,平台是Agilent ADS,主要参考“ Verilog- AMS Language Reference Manual”和ADS的帮助文档。

现在的状态算是入门了,写了个简单的PLL。

总结这几天的学习,觉得效率太低,我以前有一定 Verilog 基础,研一时学过一点 VHDL-AMS ,学到现在这个状态应该半天就够了;入门的话, 30 分钟足矣;跟着这个教程走,你会很快了解和熟悉Verilog-A 。

(前提是有一定的Verilog 基础和电路基础)1、基尔霍夫定律撑起了整个电路学的大厦(当然也可以认为基尔霍夫定律只是麦克斯韦方程的简化版),作为模拟电路描述语言Verilog-A ,同样将基尔霍夫定律作为其基本,最重要的两个概念便是流量(Flow) 和位 (Potential) ,在电学里是电流和电压,在力学里可以是力和距离,在热学里可以是功率和温差,等等。

在Verilog-A中,你可以将电阻电容电感等器件用一个方程式来表述,比如I(out) <+ V(out)/R ,这样就产生了一个电阻,最后 Verilog-A 仿真器会用某种算法( 迭代是最常见的 ) 将 I(out) 和 V(out) 求解出来,然后根据这个解去算下一个时刻的 I 、V 等,当然这仅仅是指时域仿真。

2 、下面讲Verilog-A的语法:begin end //相当于C语言的一对大括号,与Verilog同if ( expression ) true_statement ;[ else false_statement ; ] //与Verilog同case ( expression ) case_item { case_item } endcasefor ( procedural_assignment ; expression;procedural_assignment ) statement//case与for语句都跟Verilog、C语言类似cross( expr [, dir [, time_tol [, expr_tol ]]] );//cross 用来产生一个 event ,如:@(cross(V(sample) -2.0, +1.0))//指 sample 的电压超过 2.0 时触发该事件,将会执行后面的语句,+1.0 表示正向越过, -1.0 则相反ddt( expr )// 求导,如:I(n1,n2) <+ C * ddt(V(n1, n2)); //表示了一个电容idt( expr ,[ ic [, assert [, abstol ]]] ) //积分,如:V(out) <+ gain * idt(V(in) ,0) + gain * V(in);// 比例积分,式中的 0 表示积分的初值transition( expr [, time_delay [, rise_time [, fall_time [, time_tol ]]]] )// 将 expr 的值 delay一下并指定上升下降沿时间,相当于一个传输门laplace_zp( expr ,ζ ,ρ)将expr 进行拉普拉斯变换,具体表达式参看相关文献,还有laplace_zd()等数据类型:integer 、real ,另外就是 discipline ,不知道怎么翻译比较好,比如说它将电压电流这两个nature 类型作为一个discipline ,这些都在disciplines.vams这个头文件里建好了,编程时要`include "disciplines.vams"。

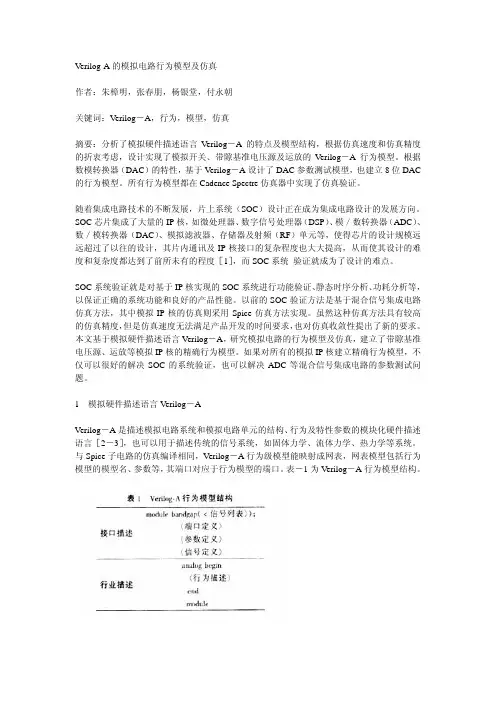

Verilog-A的模拟电路行为模型及仿真作者:朱樟明,张春朋,杨银堂,付永朝关键词:Verilog-A,行为,模型,仿真摘要:分析了模拟硬件描述语言Verilog-A的特点及模型结构,根据仿真速度和仿真精度的折衷考虑,设计实现了模拟开关、带隙基准电压源及运放的Verilog-A行为模型。

根据数模转换器(DAC)的特性,基于Verilog-A设计了DAC参数测试模型,也建立8位DAC 的行为模型。

所有行为模型都在Cadence Spectre仿真器中实现了仿真验证。

随着集成电路技术的不断发展,片上系统(SOC)设计正在成为集成电路设计的发展方向。

SOC芯片集成了大量的IP核,如微处理器、数字信号处理器(DSP)、模/数转换器(ADC)、数/模转换器(DAC)、模拟滤波器、存储器及射频(RF)单元等,使得芯片的设计规模远远超过了以往的设计,其片内通讯及IP核接口的复杂程度也大大提高,从而使其设计的难度和复杂度都达到了前所未有的程度[1],而SOC系统验证就成为了设计的难点。

SOC系统验证就是对基于IP核实现的SOC系统进行功能验证、静态时序分析、功耗分析等,以保证正确的系统功能和良好的产品性能。

以前的SOC验证方法是基于混合信号集成电路仿真方法,其中模拟IP核的仿真则采用Spice仿真方法实现。

虽然这种仿真方法具有较高的仿真精度,但是仿真速度无法满足产品开发的时间要求,也对仿真收敛性提出了新的要求。

本文基于模拟硬件描述语言Verilog-A,研究模拟电路的行为模型及仿真,建立了带隙基准电压源、运放等模拟IP核的精确行为模型。

如果对所有的模拟IP核建立精确行为模型,不仅可以很好的解决SOC的系统验证,也可以解决ADC等混合信号集成电路的参数测试问题。

1模拟硬件描述语言Verilog-AVerilog-A是描述模拟电路系统和模拟电路单元的结构、行为及特性参数的模块化硬件描述语言[2-3],也可以用于描述传统的信号系统,如固体力学、流体力学、热力学等系统。

Verilog-A语法 electrical引言Verilog-A是一种硬件描述语言(HDL),用于模拟和验证电子电路的行为。

它是Verilog的扩展,专门用于模拟模拟电路。

本文将详细介绍Verilog-A的语法和用法,以及其在电气工程中的应用。

Verilog-A简介Verilog-A是一种基于事件驱动的建模语言,用于描述模拟电路的行为和性能。

它是一种高级语言,可以用于描述模拟电路中的信号、电流、电压和功率等。

Verilog-A与Verilog的主要区别在于,Verilog-A更适用于模拟电路设计,而Verilog更适用于数字电路设计。

Verilog-A的语法结构Verilog-A的语法结构包括模块声明、参数声明、端口声明、变量声明、行为描述和函数声明等。

下面将详细介绍这些语法结构。

模块声明Verilog-A中的模块声明用于定义一个模块,模块是Verilog-A代码的基本单元。

模块声明的语法如下:module module_name (input input_name, output output_name);// 模块内部代码endmodule模块声明包括模块名称和端口声明。

参数声明Verilog-A中的参数声明用于定义模块的参数,参数可以在模块实例化时传递。

参数声明的语法如下:parameter parameter_name = value;参数可以是整数、实数或字符串等类型。

端口声明Verilog-A中的端口声明用于定义模块的输入和输出端口。

端口声明的语法如下:input input_name;output output_name;端口可以是输入或输出类型。

变量声明Verilog-A中的变量声明用于定义模块内部的变量。

变量声明的语法如下:integer variable_name;real variable_name;变量可以是整数或实数类型。

行为描述Verilog-A中的行为描述用于描述模块内部的行为和逻辑。

•Verilog-A 30分钟快速入门教程进入正题,学了几天的Verilog-A,平台是Agilent ADS,主要参考“Verilog-AMS Language Reference Manual”和ADS的帮助文档。

现在的状态算是入门了,写了个简单的PLL。

总结这几天的学习,觉得效率太低,我以前有一定Verilog基础,研一时学过一点VHDL-AMS,学到现在这个状态应该半天就够了;入门的话,30分钟足矣;跟着这个教程走,你会很快了解和熟悉Verilog-A。

(前提是有一定的Verilog基础和电路基础)1、基尔霍夫定律撑起了整个电路学的大厦(当然也可以认为基尔霍夫定律只是麦克斯韦方程的简化版),作为模拟电路描述语言Verilog-A,同样将基尔霍夫定律作为其基本,最重要的两个概念便是流量(Flow)和位(Potential),在电学里是电流和电压,在力学里可以是力和距离,在热学里可以是功率和温差,等等。

在Verilog-A中,你可以将电阻电容电感等器件用一个方程式来表述,比如I(out) <+ V(out)/R,这样就产生了一个电阻,最后Verilog-A仿真器会用某种算法(迭代是最常见的)将I(out)和V(out)求解出来,然后根据这个解去算下一个时刻的I、V等,当然这仅仅是指时域仿真。

2、下面讲Verilog-A的语法:begin end //相当于C语言的一对大括号,与Verilog同if ( expression ) true_statement ;[ else false_statement ; ] //与Verilog同case ( expression ) case_item { case_item } endcasefor ( procedural_assignment ; expression;procedural_assignment ) statement//case与for语句都跟Verilog、C语言类似cross( expr [, dir [, time_tol [, expr_tol ]]] );//cross用来产生一个event,如:@(cross(V(sample) -2.0, +1.0))//指sample的电压超过2.0时触发该事件,将会执行后面的语句,+1.0表示正向越过,-1.0则相反ddt( expr ) //求导,如:I(n1,n2) <+ C * ddt(V(n1, n2)); //表示了一个电容idt( expr ,[ ic [, assert [, abstol ]]] ) //积分,如:V(out) <+ gain * idt(V(in) ,0) + gain * V(in);//比例积分,式中的0表示积分的初值transition( expr [, time_delay [, rise_time [, fall_time [, time_tol ]]]] ) //将expr的值delay一下并指定上升下降沿时间,相当于一个传输门laplace_zp( expr ,ζ,ρ)将expr进行拉普拉斯变换,具体表达式参看相关文献,还有laplace_zd()等数据类型:integer、real,另外就是discipline,不知道怎么翻译比较好,比如说它将电压电流这两个nature类型作为一个discipline,这些都在disciplines.vams 这个头文件里建好了,编程时要`include "disciplines.vams"。

veriloga语法electrical摘要:一、Veriloga语法简介1.Veriloga的起源与发展2.Veriloga的主要特点二、Veriloga的基本语法1.模块定义2.信号声明3.逻辑表达式4.赋值语句5.条件语句6.循环语句三、Veriloga的高级语法1.参数传递与使用2.函数定义与调用3.任务定义与调用4.结构体与实例化5.生成块与循环块四、Veriloga在电路设计中的应用1.描述数字电路2.描述模拟电路3.混合信号电路设计4.验证与仿真五、Veriloga与其他语言的比较1.Veriloga与Verilog的比较2.Veriloga与VHDL的比较3.Veriloga在实际项目中的应用优势正文:Veriloga是一种基于Verilog的硬件描述语言,它继承了Verilog的优点,并在此基础上进行了改进与拓展。

Veriloga的语法结构清晰,易于学习,被广泛应用于电路设计与验证领域。

一、Veriloga语法简介Veriloga起源于2001年,由Cadence公司推出,以满足日益复杂的电路设计需求。

它具有语法简洁、可读性强、设计效率高等特点,逐渐成为硬件描述语言领域的一股新兴力量。

二、Veriloga的基本语法1.模块定义在Veriloga中,一个设计可以被划分为多个模块。

模块定义的基本格式如下:```module module_name (input wire clk,input wire rst,output reg [7:0] data_out);```其中,`module_name`为模块名称,`clk`和`rst`为时钟和复位信号,`data_out`为输出信号。

1.信号声明信号声明用于定义模块内的信号,包括输入、输出和寄存器。

信号声明的基本格式如下:```input wire clk;input wire rst;output reg [7:0] data_out;```1.逻辑表达式Veriloga支持各种逻辑运算,如与(`&`)、或(`|`)、非(`~`)等。

veriloga语法 electricalVerilog-A语言是一种电气仿真和建模的高级语言,它是从Verilog HDL发展而来的。

Verilog HDL主要用于数字电路设计,而Verilog-A则主要用于模拟和描述模拟电路中的各种物理现象和元件。

Verilog-A语言的语法与Verilog HDL类似,但它更注重对模拟电路中的连续时间和混合信号的建模支持。

Verilog-A语言主要用于描述电感、电容、电阻、晶体管等各种模拟电路中的元件,以及它们之间的相互作用和连接方式。

在Verilog-A语言中,我们可以使用不同的关键字来定义和描述模拟电路中的各种元件和信号。

例如,我们可以使用关键字`parameter`来定义参数,使用关键字`var`来定义变量,使用关键字`analog`来定义模拟输入和输出端口,使用关键字`analog`和`continuous`来定义连续时间的行为模型等。

Verilog-A语言中的模块可以由一个或多个输入和输出端口组成,每个输入和输出端口可以是数字信号、模拟信号或者是模拟电压、电流信号。

可以通过使用关键字`analog`来定义模拟输入和输出信号的类型和属性。

在使用Verilog-A语言描述模拟电路时,我们可以通过使用不同的关键字和运算符来定义和描述不同的元件和其行为。

例如,我们可以使用关键字`resistor`来定义一个电阻元件,使用关键字`capacitor`来定义一个电容元件,使用关键字`inductor`来定义一个电感元件,使用关键字`source`来定义一个电源等。

此外,Verilog-A语言还支持使用不同的运算符来描述模拟电路中的各种信号处理和运算。

例如,我们可以使用`+`、`-`、`*`、`/`等运算符来进行加减乘除运算,使用`<`、`>`、`=`等运算符来比较不同信号的大小和关系,使用`.`运算符来进行信号的连接等。

总之,Verilog-A语言是一种用于模拟和描述模拟电路中各种物理现象和元件的高级语言。

verilog-a vsin用法-回复Verilog-A 是一种建模语言,用于在集成电路设计中描述模拟行为,而Verilog-HDL 则经常用于数字电路的建模和仿真。

两种语言都是Verilog 语言的变体,用于不同的应用场景。

本文将重点讨论Verilog-A 中的一个关键元素,即vsin 函数的用法。

vsin 函数用于生成一个以正弦波形式变化的电压或电流信号。

它的原型如下:`vsin([amplitude], [frequency], [phase], [tdelay], [theta], [vcycle])`参数说明如下:- `amplitude`:正弦波的振幅,可以是一个常数或一个变量。

- `frequency`:正弦波的频率,单位为Hz。

- `phase`:正弦波的初始相位,单位为弧度。

可以是一个常数或一个变量。

- `tdelay`:正弦波的延迟时间,单位为秒。

可以是一个常数或一个变量。

- `theta`:正弦波的相位偏移,单位为弧度。

可以是一个常数或一个变量。

- `vcycle`:正弦波的周期,单位为秒。

可以是一个常数或一个变量。

现在我们来逐步解释每个参数的含义和用法。

# 1. 振幅(Amplitude)振幅参数表示正弦波的最大值或最小值。

可以将其设置为一个常数或一个变量。

如果振幅为负数,则正弦波将在零线以下变化。

例如,如果我们想要生成一个振幅为1 的正弦波,我们可以按以下方式定义vsin 函数:`vsin(1, ...)`# 2. 频率(Frequency)频率参数表示正弦波每秒变化的周期数。

它的单位是Hz。

可以将其设置为一个常数或一个变量。

例如,如果我们想要生成一个频率为1 kHz 的正弦波,我们可以按以下方式定义vsin 函数:`vsin(..., 1000, ...)`# 3. 相位(Phase)相位参数表示正弦波的初始相位。

它的单位是弧度。

可以将其设置为一个常数或一个变量。

例如,如果我们想要将正弦波的初始相位设置为45 度(约为0.785 弧度),我们可以按以下方式定义vsin 函数:`vsin(..., ..., 0.785, ...)`# 4. 延迟时间(Time Delay)延迟时间参数表示正弦波开始变化之前的等待时间。

assign veriloga用法

Verilog-A(也称为Verilog-AMS)是一种用于建模模拟电路行为的语言,它是Verilog的扩展。

在Verilog-A中,`assign`语句通常用于将一个表达式的值分配给一个信号。

这是一个简单的例子:

```verilog

module example_module;

// 定义输入和输出信号

input A;

output B;

// 使用assign语句将A的值赋给B

assign B = A;

endmodule

```

在上面的例子中,`assign B = A;` 语句将输入信号`A` 的值分配给输出信号`B`。

这是一个非常基本的例子,实际上,`assign`语句可以用于复杂的表达式和逻辑,以实现各种电路行为。

你可以在`assign`语句中使用逻辑运算、条件运算符等来定义信号之间的关系。

请注意,`assign`语句通常用于连续赋值,即信号的值在整个仿真过程中都是连续更新的。

这与`always`块不同,后者在特定的敏感信号变化时执行一次。

希望这对你有帮助。

如果你有具体的Verilog-A代码或问题,可以提供更多的信息,我将尽力提供帮助。

Verilog-A语法实用指南Verilog-A语法是描述模拟电路行为的一种编程语言。

它可以用于描述电路的行为和功能,是数字电路设计中常用的一种语言。

本文将从Verilog-A语法的基本特点、常用语法以及示例应用等方面展开介绍,希望可以为初学者提供一些指导和帮助。

一、Verilog-A语法的基本特点1. 语法简洁明了:Verilog-A语法采用了类似C语言的结构,采用了分号作为语句结束符,使得代码具有良好的可读性。

2. 强大的模块化功能:Verilog-A语法支持模块化的设计,可以将电路设计分为多个模块,每个模块完成不同的功能。

3. 丰富的数据类型:Verilog-A语法支持多种数据类型,包括整型、实型、布尔型等,能够适应不同的应用场景。

4. 可扩展性强:Verilog-A语法可以方便地扩展新的功能和特性,使得它在大型项目中也能够得到应用。

二、Verilog-A语法的常用语法1. 模块定义:使用module关键字定义一个模块,模块内包含输入端口、输出端口以及内部逻辑。

2. 参数定义:使用parameter关键字定义参数,可以在模块中使用这些参数。

3. 时序控制:使用initial关键字定义初始条件,使用always关键字定义条件触发的操作。

4. 信号赋值:使用assign关键字完成信号之间的赋值操作。

5. 行为描述:使用initial和always关键字描述电路的行为。

6. 分支结构:使用if...else...语句完成条件判断。

7. 循环结构:使用for和while等关键字完成循环操作。

三、Verilog-A语法的示例应用1. 模拟电路设计:Verilog-A语法可以用于模拟电路的设计和验证,包括数字电路和模拟电路。

2. 信号处理:Verilog-A语法可以用于实现信号的采集、处理和输出。

3. 控制系统:Verilog-A语法可以用于描述控制系统的行为和功能,包括PID控制、状态空间控制等。

4. 通信系统:Verilog-A语法可以用于描述通信系统的行为和功能,包括调制解调、编解码等。

verilog_ieee官方标准手册

Verilog是一种硬件描述语言(HDL),是用于电子设计自动化(EDA)的语言之一。

Verilog从20世纪80年代开始发展,最初由Gateway Design Automation 公司开发,后来被Cadence Design Systems收购。

Verilog被广泛应用于数字电路的设计和仿真。

IEEE标准的全称是IEEE Std 1364,是Verilog的官方标准手册。

这个标准由IEEE Verilog标准工作组制定,其中包含了Verilog语言的语法和语义规范。

这个标准包含了3个部分:

1. Verilog语言参考手册:这个部分包含了Verilog语言的语法和语义规范。

其中包含了Verilog的基本语法、数据类型、运算符、控制结构、模块和端口等方面的内容,对于初学者来说非常重要。

2. Verilog模拟器标准接口:这个部分定义了与Verilog编译器和模拟器交互的标准接口。

如果你想自己实现一个Verilog编译器或模拟器,那么这个部分非常重要。

3. Verilog验证标准接口:这个部分定义了与Verilog验证工具交互的标准接口。

如果你想自己实现一个Verilog验证工具,那么这个部分非常重要。

总的来说,IEEE标准是Verilog语言的权威参考,所有的Verilog编译器和模拟器都应该遵循这个标准。

如果你想深入学习Verilog语言,那么这个标准是不可或缺的。

verilog-a vsin用法Verilog-A是一种用于模拟数字系统的语言,其中包含了许多用于模拟数字信号的函数和操作符。

Vsin是Verilog-A中用于模拟正弦波信号的函数,它可以在模拟数字系统中用于生成正弦波信号。

一、Vsin函数的使用方法Vsin函数的使用方法非常简单,只需要在Verilog-A代码中调用该函数,并指定频率、幅度和相位等参数即可。

以下是一个简单的示例代码,展示了如何使用Vsin函数生成一个正弦波信号:```verilogmodule sine_generator;// 定义输入信号频率和相位parameter FREQUENCY = 100e6; // 频率,Hzparameter PHASE = 0; // 相位,度// 生成正弦波信号reg [7:0] sine_signal;always @(posedge clk) beginsine_signal = Vsin(FREQUENCY, PHASE); // 使用Vsin函数生成正弦波信号endendmodule```在上面的代码中,我们首先定义了输入信号的频率和相位,然后使用Vsin函数生成了一个8位宽度的正弦波信号。

在每次时钟上升沿时,都会更新该信号的值。

二、Vsin函数的参数说明Vsin函数的参数包括频率(FREQUENCY)、幅度(AMPLITUDE)和相位(PHASE)。

其中,频率是指正弦波的周期,单位为Hz;幅度是指正弦波的振幅,单位为数值大小;相位是指正弦波的初始相位,单位为度数。

在上面的示例代码中,我们使用了默认的幅度和相位值,因此可以直接调用Vsin函数。

三、使用Vsin函数的注意事项在使用Vsin函数时,需要注意以下几点:1. Vsin函数只能用于模拟数字系统中,不能用于实际硬件中。

2. Vsin函数的输出是一个连续的模拟信号,而不是一个离散信号。

因此,在使用Vsin函数生成的信号时,需要将其与实际的模拟信号进行匹配。

Verilog是一种硬件描述语言,用于描述数字电路和系统。

以下是Verilog语法规则的一些要点:

标识符:Verilog中的标识符由字母、数字和下划线组成,且第一个字符必须是字母或下划线。

标识符区分大小写。

数据类型:Verilog中有多种数据类型,包括wire、reg、int、parameter等。

wire类型用于表示线网,reg类型用于表示寄存器。

赋值语句:Verilog中的赋值语句使用“=”操作符,例如“a = b”。

运算符:Verilog中有多种运算符,包括算术运算符、逻辑运算符、关系运算符等。

控制结构:Verilog中有条件语句、循环语句等控制结构。

模块:Verilog中的模块是自顶向下的设计方法的核心,用于描述数字电路和系统。

模块的语法包括模块声明、端口声明、内部信号声明、过程块和实例化等部分。

时序控制:Verilog中的时序控制使用非阻塞赋值和延迟表达式。

参数:Verilog中的参数用于在模块之间传递值。

任务和函数:Verilog中的任务和函数用于执行特定的操作。

注释:Verilog中的注释使用“//”或“/* */”进行注释。

这些是Verilog语法规则的一些要点,如果您想了解更多细节,建议参考Verilog的相关书籍或文档。