利用锁相环芯片实现FSK信号的调制与解调电路的设计综述

- 格式:doc

- 大小:1.25 MB

- 文档页数:18

实验三2FSK调制与解调实验一、实验目的1、了解二进制移频键控2FSK 信号的产生过程及电路的实现方法。

2、了解非相干解调器过零检测的工作原理及电路的实现方法。

3、了解相干解调器锁相解调法的工作原理及电路的实现方法。

二、实验内容1、了解相位不连续2FSK 信号的频谱特性。

2、了解2FSK(相位不连续)调制,非相干、相干解调电路的组成及工作理。

3、观察2FSK 调制,非相干、相干解调各点波形。

4、改变f1、f2的频率大小,观察不同调制指数下的调制解调效果。

(选作)5、利用实验模块的电路,设计出其它解调方法,并自行验证。

(选作)三、预习要求1)画出实验电路中2FSK调制器采用的原理框图;2)根据实验指导书的相关资料,说明本实验2FSK调制的载波频率分别是多少?用什么方法产生的?3)本实验2FSK载波是方波还是正弦波?如何实现的?4)用什么方法可以将方波变成正弦波?5)FSK调制器可以用哪两种基本方法实现?本实验用的是哪一种?6)用什么方法实现的FSK信号的相位是连续的?7)实验中,信息的码速率是多少?可以用什么方法测量?8)可以用什么方法来测量2FSK的两个载波频率?9)当用“10101010………”不断重复的信息码进行FSK调制,用计数法测量FSK调制输出信号的频率,测量得到的频率可能是多少?为什么?10)本实验中,2FSK 信号带宽是多少?如何计算的?公式中的各个量代表什么?11)本实验中,2FSK 信号的频谱会是单峰还是双峰?为什么?12)用示波器同时观测FSK调制器的输入数据、FSK调制器输出的已调信号,要能稳定的观测应该用这两个信号中的哪一个作为示波器的触发信号?13)画出2FSK过零检测解调的原理框图;14)实验中,FSK过零检测解调方案采用数字电路如何实现;15)脉冲的宽度相同,有些时刻的脉冲密一些,有些时刻的脉冲少一些,可以用什么具体的方法区分出每一个单位时刻内脉冲是多还是少?16)测试接收端的各点波形,需要与什么波形对比,才能比较好的进行观测?示波器的触发源该选哪一种信号?为什么?17)采用过零检测解调的方法时,将f1和f2倍频的电路是如何设计的?18)采用过零检测解调的方法时,解调电路中哪一点的波形是f1和f2的倍频?19)2FSK 信号经过整形变成方波2FSK 信号,频谱有什么变化?为什么?20)解调时将f1和f2倍频有何好处?如何通过仪器测量来说明?21)2FSK 信号解调时将f1和f2倍频之后,频谱有什么变化?为什么?22)解调电路各点信号的时延是怎么产生的?23)解调出的信码和调制器的绝对码之间的时延是怎么产生的?24)解调的信号为什么要进行再生?25)理论上,能否实现出一个没有时延的解调器?为什么?26)解调的信号是如何实现再生的?27)再生过程中,是什么环节会对解调的输出造成延时?为什么?28)画出2FSK 锁相PLL 解调的原理框图;29)PLL 解调2FSK 信号的原理是什么?30)为什么2FSK 锁相解调可以实现相干解调?31)要实现2FSK 锁相解调,锁相环需要工作在什么跟踪方式?为什么?32)解调电路中T31(放大出)没有信号输出,可能的原因有哪些?33)T19(2FSK 过零检测出)信号异常,如何判断故障点在哪?34)解调输出信号与发送端的数据信号对比,为什么会有延时,是哪些原理造成的?四、实验原理二进制频率调制(2FSK )是数据通信中使用较早的一种通信方式。

FSK调制解调系统设计一、题目FSK调制解调系统设计二、主要技术指标码传输速率1Kb,载波分别为300K和600K三、方案论证与选择FSK调制可以利用锁相环路PLL来实现,其方法有两种,一种方法是仅利用其中的VCD部分,用FSK的高/低电平去控制VCO的频率,采用这种方法的缺点是频率f1、f2的稳定性差,不利于接收解调;另一种方法是用类似频率合成器采用倍频方式,用晶体振荡管产生基准频率,并通过可控分频器的分频比N1、N2,以获得相当于晶体振荡的高精度、高稳定度调制信号频率。

利用锁相环的频率跟踪特性来工作的,具有VCO振荡强,输出功率大,易于集成,体积小等优点。

频率合成法使得FSK调制器的设计具有很多灵活的模式,主要介绍以下情况.当FSK所需的两个频率f1和f2均已产生.则可以利用锁相环获得相位连续的FSK信号,由数字调制信号控制振荡器f1和振荡器f2,以决定其中之一加至锁相环的鉴相输入墙,锁相环VCO的输出频率始终跟踪并锁定在输入信号的频率上,这样,f1或f2两个信号源在数字调制信号的控制下就成为对锁相环VCO输出频率进行调制的FSK信号,因其产生的频偏是由f1和f2确定的.所以当振荡器f1和f2的频稳很高时。

FSK信号的频稳也很高.这也是频率合成法谩计的FSK调制器的优点之一.四、系统组成框图调制框图:解调框图:五、单元电路设计及说明调制原理2FSK信号是用载波频率的变化来表征被传信息的状态的,被调载波的频率随二进制序列0,1状态而变化,即载频为f1时代表传0,载频为f2时代表传1.显然,FSK信号完全可以看成两个分别以f1和f2为载频,以an和an为被传二进制序列的两种2ASK信号的合成.2FSK信号的产生通常有两种方式:(1)频率选择法;(2)载波调频法.频率选择法是在二进制基带脉冲的控制下通过开关电路对两个不同的独立频率源进行选通.实现比较简单,获得了广泛应用.载波调频法是采用模拟调频电路来实现。

实验十六 FSK调制、解调实验1一、实验目的1、了解FSK调制、解调原理。

2、熟悉锁相环芯片CD4046工作原理。

3、掌握FSK调制、解调的电路实现方法。

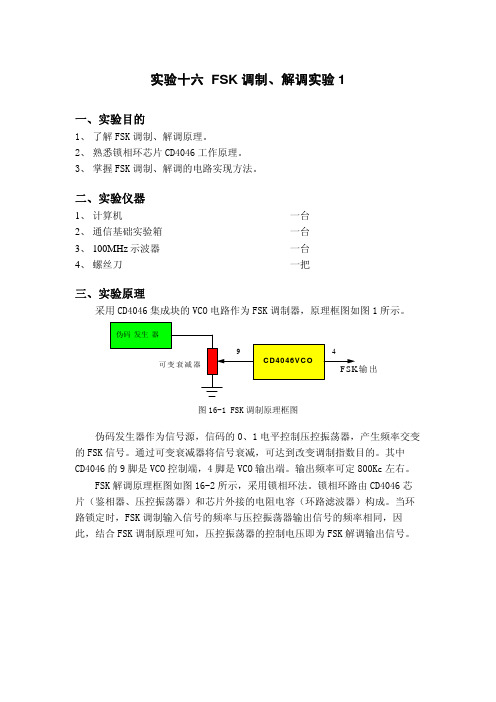

二、实验仪器1、计算机一台2、通信基础实验箱一台3、100MHz示波器一台4、螺丝刀一把三、实验原理采用CD4046集成块的VCO电路作为FSK调制器,原理框图如图1所示。

输出图16-1 FSK调制原理框图伪码发生器作为信号源,信码的0、1电平控制压控振荡器,产生频率交变的FSK信号。

通过可变衰减器将信号衰减,可达到改变调制指数目的。

其中CD4046的9脚是VCO控制端,4脚是VCO输出端。

输出频率可定800Kc左右。

FSK解调原理框图如图16-2所示,采用锁相环法。

锁相环路由CD4046芯片(鉴相器、压控振荡器)和芯片外接的电阻电容(环路滤波器)构成。

当环路锁定时,FSK调制输入信号的频率与压控振荡器输出信号的频率相同,因此,结合FSK调制原理可知,压控振荡器的控制电压即为FSK解调输出信号。

CD4046引脚图:CD4046内部结构图:四、实验内容及步骤1、在MAXPLUSⅡ设计平台下进行电路设计用作FSK 调制的nrz 信号源电路如图16-3所示。

图16-3 FSK 调制nrz 信号源电路FPGA 引脚定义:CLK 83 脚(高频时钟输入16.9344Mc) CLK_OUT 37 脚(分频时钟)NRZ1 39 脚(内部NRZ信号源,用来测试)NRZ2 54 脚(内部NRZ信号源,送到VCO电路)2、实验板设置2.1 FPGA设置(1)接通SW_6(2)K2的“1”脚置“ON”,将16.9344MHz时钟信号送到FPGA的第83脚(全局时钟)2.2FSK调制部分设置(1)用跳线短接J19 1-2,将NRZ码送到可调电阻W4。

(2)调整W4可改变NRZ信号的幅度,即改变调制指数,首先将W4调整到零。

(3)接通SW_15,给CD4046芯片供电。

FSK 信号的调制

一、 实验目的

(1) 了解连续相位2FSK 信号的产生及实现方法

(2) 测量连续相位2FSK 信号的波形及功率谱

(3) 了解用锁相环进行2FSK 信号解调的原理及实现方法

二、 实验原理

FSK 调制原理框图如下:

三、 实验设备

主振荡器、序列码产生器、电压控制振荡器、音频振荡器、加法器、双模开关、可变直流电压、

四、 实验过程

FSK 信号调制连接图

方法一:

(1)相位连续FSK 调制系统中,使VCO 的输出中心频率为5KHz ;

(2)二进制数字序列信号利用主振荡器的2KHz 正弦信号加到序列码产生器的时钟控制端(CLK );

方法二:

(3)相位不连续FSK 调制系统中,可以看作两个ASK 系统相加;

(4)两个信号的频率可分别利用音频振荡器和VCO 的输出频率产生;

(5)数字信号的产生方法可参考ASK 调制信号方法二实现。

(6)最后两路信号经过双模开关实现FSK信号的调制。

五、实验结果

基带信号与调制信号波形

六、实验分析

FSK是利用VCO将其电压信号转化为频率信号,当电压变化时,对应调制信号的频率变化,并且相位连续。

在实验过程中在测试VCO的压控灵敏度时,由于调整那个旋钮时很难控制,遇到了一些问题。

回答问题:在FSK信号调制中,双模开关起什么作用,可由哪个模块代替?

双模开关是通过输入的数字信号来控制载波的输出的选择,可以使用双模开关来产生相位不连续的2FSK信号,实验中用VCO代替双模开关来产生相位连续的2FSK信号。

实验五锁相环用于2FSK的调制与解调仿真(一)实验目的:1)了解和掌握锁相环路在信号的调制与解调中的应用;2)理解2FSK信号的特点与应用;3)掌握MATLAB中通信工具箱相关函数的使用方法,熟悉MATLAB编程过程;(二)实验所用软件:MA TLAB7.1 R14 SP3.(三)实验内容:1)编程实现原始信号的产生;;2)函数hilbert,unwrap,smooth的使用;3)对Matlab中常用画图函数的复习使用;4)用绘图函数画出2FSK信号的调制及解调过程;函数hilbert,unwrap,smooth的使用见MATLAB中help具体示例:% Signal generationt0 = .15; % signal durationts = 0.0005; % sampling intervalfc = 200; % carrier frequencykf = 50; % modulation indexfs = 1/ts; % sampling frequencyt = [0:ts:t0]; % time vectordf = 0.25; % required frequency resolution c = cos(2*pi*fc*t); % carrier signalm =[2*ones(1,t0/(3*ts)),-2*ones(1,t0/(3*ts)),zeros(1,t0/(3*ts)+1)];% Frequency modulationint_m(1) = 0;for (i = 1 : length(t)-1) % integral of m int_m(i+1) = int_m(i) + m(i)*ts;endu = cos(2*pi*fc*t + 2*pi*kf*int_m); % modulated signalfiguresubplot (3,1,1)plot (m(1:300))TITLE ('Modulating Signal')grid on;subplot (3,1,2)plot (c(1:300))TITLE ('Carrier Signal')grid on;subplot (3,1,3)plot (u(1:300))TITLE ('Frequency Modulated Signal')grid on;% Frequency demodulationt = [0:ts:ts*(length(u)-1)]; % finding phase of modulated signalx = hilbert(u);z = x.*exp(-j*2*pi*250*t);phi = angle(z);phi = unwrap(phi); % restoring original phase dem = (1/(2*pi*kf))*(diff(phi)/ts); % demodulated signalfiguresubplot (3,1,1)plot (c(1:300))TITLE ('Carrier Signal')grid on;subplot (3,1,2)plot (u(1:300))TITLE ('Frequency Modulated Signal')grid on;subplot (3,1,3)dem = smooth(dem,7) + 1;plot (dem(1:300))axis ([0 300 -2 2]);TITLE ('De-Modulated Signal') grid on;。

本课程设计主要运用Multisim软件仿真平台设计进行2FSK的调制与解调系统的仿真。

在本次课程设计中先根据2FSK调制与解调原理构建调制解调电路,从Multisim工具箱中招所需各元件,合理设置好参数并运行,其中可以通过不断地修改优化得到需要信号并进行调制,之后经过锁相环解调器进行解调,分析示波器的仿真图形判断2FSK的调制解调系统仿真是否成功。

关键词:Multisim;2FSK ;调制;锁相环解调器前言 (3)一、课程设计及内容 (4)1.1设计任务及主要技术和要求 (4)1.2内容和要求 (4)二、基本原理 (5)2.1 2FSK信号的调制原理 (5)2.2 2FSK信号的解调原理 (6)三、单元电路设计原理及分析 (8)3.1调制单元 (8)3.1.1模拟开关电路 (8)3.1.2振荡电路 (8)3.1.3 2FSK调制电路的整体电路图 (9)3.2 2FSK的解调单元 (10)3.2.1非相干解调 (11)3.2.2 锁相环解调器 (12)四、总结 (14)参考文献 (15)附件1元器件清单 (16)附件2整体仿真电路图 (17)前言数字调频又称移频键控,它是用不同的载波来传送数字信号的。

FSK信号的产生有两种方法:直接调频法和频率键控法。

2FSK信号的产生可利用一个矩形脉冲序列对一个载波进行调频而获得。

这正是频率键控通信方式早期采用的实现方法,也是利用模拟调频法实现数字调频的方法。

2FSK信号的另一产生方法便是采用键控法,即利用受矩形脉冲序列控制的开关电路对两个不同的独立频率源进行选择。

2FSK它是利用载频频率变化来传输数字信息。

数字载频信号又可分为相位离散和相位连续两种情形。

若两个振荡频率分别由不同的独立振荡器提供,它们之间的相位互不相关,这就叫相位离散的数字调频信号;若两个振荡频率由同一振荡信号源提供,是对其中一个载频进行分频,这样产生的两个载波就是相位连续的数字调频信号。

在实际通信系统中,大部分信道不能直接传输基带信号,必须用基带信号对载波波形的参量进行控制,使载波的这些参量随基带信号的变化而变化,即以正弦波作为载波的数字调制系统。

实验二 FSK调制解调实验一. 实验目的1.理解FSK调制的工作原理及电路组成。

2.理解利用锁相环解调FSK的原理和实现方法。

二. 实验电路工作原理数字调频又可称作移频键控FSK,它是利用载频频率变化来传递数字信息。

数字调频信号可以分为相位离散和相位连续两种情形。

本实验电路中,由实验一提供的载频频率经过本实验电路分频而得到的两个不同频率的载频信号,则为相位连续的数字调频信号。

(一) FSK调制电路工作原理=32KHz的载频,另一路输入的基带信号由转换开关K904转接后分成两路,一路控制f1经倒相去控制f=16KHz的载频。

当基带信号为“1”时,模拟开关1打开,模拟开关2关闭,2=32KHz,当基带信号为“0”时,模拟开关1关闭,模拟开关2开通。

此时输出此时输出f1f=16KHz,于是可在输出端得到已调的FSK信号。

2(二) FSK解调电路工作原理FSK集成电路模拟锁相环解调器的工作原理是十分简单的,只要在设计锁相环时,使它锁定在FSK的一个载频f1上,对应输出高电平,而对另一载频f2失锁,对应输出低电平,那末在锁相环路滤波器输出端就可以得到解调的基带信号序列。

三. 实验内容测试FSK调制解调电路TP901~TP909各测量点波形,并作详细分析。

1.按下按键开关: K01、K02、K900。

2.跳线开关设置: K9012–3、K9022–3。

K9041–2、2KHz的伪随机码,码序列为:000011101100101K9042–3、8KHz方波。

做FSK解调实验时,K9041–2、K9031–2。

3.在CA901插上电容,使压控振荡器工作在32KHz,电容在1800Pf 2400Pf之间。

4.观察FSK解调输出TP907~TP909波形,并作记录,并同时观察FSK调制端的基带信号,比较两者波形,观察是否有失真。

四.实验结果TP901:K901的3与2相连TP902:K902的3与2相连TP903:K904的1与2相连,K904的2与3不连,TP906:K905(1与2,3与4)控制。

目录1 锁相环简介 (1)1.1 引言 (1)1.2 锁相环的结构 (1)2 锁相环芯片简介 (2)2.1 NE564介绍 (2)2.2 CD4046介绍 (3)3 FSK简介 (5)3.1 FSK基本概念与特点 (5)3.2 FSK的发展及应用前景 (7)4 利用锁相环芯片实现FSK信号的调制 (7)4.1 FSK信号调制的基本原理 (7)4.2 利用NE564实现FSK信号调制电路的设计 (8)4.3 利用CD4046实现FSK信号调制电路的设计 (8)5 利用锁相环芯片实现FSK信号的解调 (10)6 实验结果分析 (11)6.1 利用锁相环芯片实现FSK信号调制和解调的结果分析 (11)6.2 课题的主要研究工作及意义 (12)参考文献 (14)致谢 (15)利用锁相环芯片实现FSK信号的调制与解调电路的设计摘要:频移键控(FSK)操作方法简单,易于实现;在解调的过程中不须恢复本地载波,也可进行异步传输;并且抗噪声和抗衰落性能也都较强。

因此,频移键控(FSK)的调制与解调技术在通信行业中得到了广泛地应用,且主要适用于低、中速数据的传输。

本文主要介绍锁相环芯片NE564、CD4046和FSK信号的基本特点、工作原理和用途,并详细的阐述了利用锁相环芯片NE564和CD4046实现FSK 信号的调制与解调工作的基本原理和主要设计过程。

在技术方面,主要介绍FSK 调制与解调的相关原理和基本技术。

最后对整个实验设计过程进行总结分析,并深入探讨了课题的主要研究工作及意义,加深了对数字移频键控的调制与解调方法的理解;更加深入的学习了锁相环的设计原理,并加强了对锁相环的应用。

关键词:锁相环;NE564;CD4046;FSK;调制;解调Using PLL Chip to Achieve FSK Signal Modulation andDemodulation Circuit DesignAbstract:Frequency shift keying (FSK) operation method is simple,easy to implement;In the process of demodulation,need not to restore the local carrier can also be used for asynchronous transmission;And anti noise and fading resistance is strong.Therefore,frequency shift keying (FSK) modulation and demodulation technology has been widely used in the communications industry,and is mainly suitable for low and medium speed data transmission.NE564 PLL chip were introduced in this paper,CD4046 and the basic characteristics of FSK signal,the working principle and purpose,and expounds in detail the use of NE564 PLL chip CD4046 and realize the basic principle of FSK signal modulation and demodulation of the work and the main design process.In terms of technology,mainly introduces the FSK modulation and demodulation principle and basic technology.Finally to summarize the whole process of design of experiment is analyzed,and discussed the main research work and significance of topics,deepened the FSK digital modulation and demodulation ways of understanding;More in-depth study,the design principle of phase-locked loop,and strengthen the application of phase-locked loop.Key words:Phase-locked loop;NE564;CD4046;FSK;Modulation;Demodulation1 锁相环简介1.1 引言随着现代社会的不断进步,电子计算机和电子科学技术不断地普及到我们的家庭中。

通信对我们来说也显得越来越至关重要,密不可分。

对于通信技术而言,通信的质量问题也就显的非常的关键。

在保证信息远距离传输正确性这一方面,数字通信系统拥有先天的优势,这也正是数据通信技术快速发展的真正原因。

数字频率调制是数据通信中一种常见的调制方式。

由于频移键控(FSK)的调制和解调原理都相对比较简单,作为数字通信原理的一门入门学科,透彻的理解频移键控(FSK)后可以更好地理解其他较复杂的调制系统,为以后的进一步发展打下坚实基础[1]。

锁相环(PLL)是一种闭环的自动跟踪负反馈系统。

60年代初随着数字通信系统的发展,锁相环的应用也越来越广。

在电子仪器方面,锁相环在频率合成器和相位计等仪器中起了重要作用。

锁相环路之所以能得到如此广泛的应用,是由于其独特的优良性能所决定的。

它具有载波跟踪特性,作为一个窄带跟踪滤波器,可提取淹没在噪声中的信号;用高稳定的参考振荡器锁定,可提供频率高稳定的频率源;可进行高精度的香味与频率测量等等。

它具有调制跟踪特性,可制成高性能的调制器和解调器。

它还具有低门限特性,可大大改善模拟信号和数字信号的解调质量[2]。

对于不同的调制方式,还有其不同的独特的解调方法。

在本实验中主要利用了锁相环的特性,实现了基于锁相环的数字信号移频键控的调制与解调。

1.2 锁相环的结构锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域[3]。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如图1-1所示。

图1-1 锁相环结构图图中的压控振荡器的输出o U 接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压d U 的大小决定。

施加于相位比较器另一个输入端的外部输入信号i U 与来自压控振荡器的输出信号o U 相比较,比较结果产生的误差输出电压ψU 正比于i U 和o U 两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压d U 。

这个平均值电压d U 朝着减小VCO 输出频率和输入频率之差的方向变化,直至VCO 输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

2 锁相环芯片简介2.1 NE564介绍高频模拟锁相环NE564是Philips Semiconductor 公司(荷兰菲利浦公司)的产品,同类国产产品的型号有XD564、L564等。

NE564最高工作频率可达到50MHZ ,采用+5V 单电源供电,特别适用于高速数字通信中FM 调频信号及2FSK 移频键控信号的调制、解调,而无需外接复杂的滤波器。

NE564采用双极性工艺,其外部引脚图和内部组成框图分别如图2-1和图2-2所示。

其中,1A 为限幅器,可抑制FM 调频信号的寄生调幅;相位比较器(鉴相器)PD 的内部含有限幅放大器,以提高对AM 调幅信号的抗干扰能力;外接电容3C 、4C 组成低通滤波器,用来滤出比较器输出的直流误差电压的波纹;改变引脚的输入2电流可改变环路增益;压控振荡器VCO 的内部接有固定电阻R (R=100Ω),只需外接一个定时电容t C 就可产生振荡。

VCO 有两个电压输出端,其中01VCO 输出TTL 电平,02VCO 输出ECL 电平。

后置鉴相器由单位增益跨导放大器3A 和施密特触发器ST 组成。

其中,3A 提供解调FSK 信号时的补偿直流电平及用作线性解调FM 信号时的后置鉴相滤波器;ST 的回差电压可通过引脚16外接直流电压进行调整,以消除输出信号0TTL 的相位抖动[4]。

图2-1 NE564的外部引脚图图2-2 NE564的内部组成框图2.2 CD4046介绍锁相环过去多采用分立元件和模拟电路组成,现在常使用集成电路的锁相环,CD4046便是常用的锁相环集成电路[5]。

CD4046锁相环采用的是RC型压控振荡器,必须外接电容C1和电阻R1作为充放电元件,当PLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。

其特点是电源电压范围宽为3V-18V,输入阻抗高约100M,动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2-3是CD4046的引脚排列,采用16脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

图2-3 CD4046的外部引脚图图2-4 CD4046的内部电原理框图图2-4是CD4046内部电原理框图,它主要由相位比较Ⅰ、相位比较器Ⅱ、压控振荡器(VCO )、源跟随器、线性放大器、整形电路等部分组成。

相位比较器Ⅰ采用异或门结构,当两个输人端信号i U 、o U 的电平状态不同时(即一个高电平,一个为低电平),输出端信号ψU 为高电平;反之,当i U 、o U 的电平状态相同时(即两个均为高,或均为低电平),ψU 输出为低电平。

当i U 、o U 的相位差Δφ变化在0°-180°的范围内时,ψU 的脉冲宽度m 也随之改变,即占空比亦在改变。

从比较器Ⅰ的输入和输出信号的波形(如图2-5所示)可看出,其输出信号的频率是输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°的相位移动。