全数字锁相环毕业设计之开题报告

- 格式:doc

- 大小:86.00 KB

- 文档页数:6

引言锁相的概念是在19世纪30年代提出的,而且很快在电子学和通信领域中获得广泛应用。

尽管基本锁相环的从开始出现几乎保持原样,但是使用不同的技术制作及满足不同的应用要求,锁相环的实现对于特定的设计还是蛮大的挑战。

锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可少的基本部件。

随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。

锁相环技术在众多领域得到了广泛的应用。

如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。

传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的锁相环相比,具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调,易于构建高阶锁相环等优点,并且应用在数字系统中时,不需A/D及D/A转换。

随着通讯技术、集成电路技术的飞速发展和系统芯片(SoC)的深入研究,全数字锁相环必然会在其中得到更为广泛的应用。

因此,对全数字锁相环的研究和应用得到了越来越多的关注。

传统的数字锁相环系统是希望通过采用具有低通特性的环路滤波器,获得稳定的振荡控制数据。

对于高阶全数字锁相环,其数字滤波器常常采用基于DSP 的运算电路。

这种结构的锁相环,当环路带宽很窄时,环路滤波器的实现将需要很大的电路量,这给专用集成电路的应用和片上系统SOC(system on chip)的设计带来一定困难。

另一种类型的全数字锁相环是采用脉冲序列低通滤波计数电路作为环路滤波器,如随机徘徊序列滤波器、先N后M序列滤波器等。

这些电路通过对鉴相模块产生的相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。

由于脉冲序列低通滤波计数方法是一个比较复杂的非线性处理过程,难以进行线性近似,因此,无法采用系统传递函数的分析方法确定锁相环的设计参数。

不能实现对高阶数字锁相环性能指标的解藕控制和分析,无法满足较高的应用需求。

由于数字电子技术的迅速发展,尤其是数字计算和信号处理技术在多媒体、自动化、仪器仪表、通讯等领域的广泛应用,用数字电路处理模拟信号的情况日益普遍。

用于GPS接收机的全集成锁相环设计的开题报告1.背景和意义随着全球定位系统 (GPS)的普及和应用范围的扩大,GPS接收机的需求也不断增加。

锁相环 (PLL) 是GPS接收机中必不可少的关键子系统之一,它可以实现时钟恢复、频率合成、信号解调等功能,对GPS接收机的性能和稳定性有着重要的影响。

目前,市场上主流的GPS接收机产品大都采用了全集成锁相环 (PLL) 设计。

通过对PLL的设计与优化,可以提高GPS接收机的定位精度、灵敏度和鲁棒性。

2.研究现状目前,PLL技术已经在数字领域和模拟领域得到了广泛的应用。

在数字领域,PLL可以完成数字时钟重构、数字频率合成、数字解调等功能。

在模拟领域,PLL可以实现频率锁定、相位锁定、时钟恢复等功能。

针对GPS接收机中PLL的设计,已经有很多研究者进行了相关的研究。

其中,PLL的数字实现方式包括直接数字合成方法、分数数字合成方法和整数-N数字合成方法等。

在PLL的模拟实现方面,主要包括模拟锁相环、混频锁相环、相位锁定环等。

3.研究内容和方法本论文主要研究的内容是GPS接收机中全集成锁相环的设计与优化。

具体内容包括:(1) PLL的理论基础和相关原理研究(2) GPS接收机PLL的技术发展和研究现状分析(3) GPS接收机中全集成锁相环的设计和实现(4) GPS接收机中全集成锁相环性能优化方法的研究(5) GPS接收机中全集成锁相环实验验证与分析本论文主要采用文献研究法、仿真模拟法和实验验证法等方法进行研究。

首先从PLL的基本原理、数字实现方式和模拟实现方式等方面进行深入研究,然后针对GPS接收机中PLL的优化,提出一些有效的优化方法并进行实验验证,最终得出全集成锁相环在GPS接收机中的性能与作用。

4.研究意义和贡献本论文的研究意义和贡献主要包括:(1) 对GPS接收机中PLL的设计和优化进行了深入研究(2) 提出了有效的全集成锁相环优化方法,有利于提高GPS接收机的性能(3) 对GPS接收机的性能和稳定性有着积极的促进作用(4) 为GPS接收机的进一步研发和拓展提供了理论基础和参考依据5.论文结构安排第一章:前言本章主要介绍了全集成锁相环在GPS接收机中的重要性和本文的研究背景及意义。

高速低抖动全数字锁相环的设计研究的开题报告一、研究背景和目的在当前数字信号系统中,低抖动时钟是非常重要的。

低抖动的时钟信号可以提高数据传输的可靠性和稳定性,在数字信号处理、通信系统、雷达、高速采集等领域得到广泛应用。

因此,设计一款高速低抖动全数字锁相环是十分必要的。

本文的研究目的在于设计一种高速低抖动的全数字锁相环,通过对锁相环内部的数字控制电路、数字滤波电路、数字相位频率检测器以及数字控制振荡器等模块的优化设计,从而达到减小整个锁相环系统抖动的目的。

二、研究内容和方法本文的研究内容主要包括以下几个方面:1. 锁相环内部的数字控制电路设计:本文将设计一种数字控制电路,以实现锁相环的数字化控制。

数字控制电路将接收锁相环的参考信号和反馈信号,通过锁相环的数字滤波器、数字相位频率检测器以及数字控制振荡器等模块,控制锁相环的输出信号,以实现锁相环的数字化控制。

2. 数字滤波电路的优化设计:本文将优化数字滤波器的设计,以减小数字滤波电路对时钟信号的抖动。

3. 数字相位频率检测器的设计:本文将设计一种数字相位频率检测器,以实现对参考信号和反馈信号的比较,从而实现对锁相环输出信号相位和频率的数字控制。

4. 数字控制振荡器的设计:本文将设计一种数字控制振荡器,以实现对锁相环输出信号频率的控制。

数字控制振荡器将接收相位差误差信号,通过数字控制电路对其进行数字控制,从而调整输出信号的频率。

本文的研究方法主要包括以下几个方面:1. 软件设计仿真:使用ADS软件进行数字电路仿真,验证各个模块的设计是否合理,并通过仿真分析锁相环系统的抖动性能。

2. 硬件设计实现:采用高速数字集成电路实现本文所设计的锁相环电路,并通过测试和分析验证其抖动性能,测试数据将记录并进行分析。

三、预期成果和意义本文的预期成果为设计实现一种高速低抖动的全数字锁相环,通过对锁相环内部的数字控制电路、数字滤波电路、数字相位频率检测器以及数字控制振荡器等模块的优化设计,实现锁相环系统的低抖动性能与高稳定性,并在数字信号处理、通信系统、雷达、高速采集等领域得到广泛应用。

基于全数字锁相环的时间数字转换器的研究的开题报告一、研究背景及意义时间数字转换器是指将时间信号转换为数字信号的电子设备。

在许多应用场合中,需要对时间信号进行高精度的测量和处理,例如雷达、GPS、通信等领域。

时间数字转换器是这些应用的关键组件之一。

传统的时间数字转换器通常采用基于脉冲计数器的方式实现,但其精度和速度都较低。

因此,研究一种新型的高性能时间数字转换器是十分必要的。

本研究拟采用基于全数字锁相环技术的时间数字转换器,该技术是一种先进的数字信号处理技术,可以实现高精度、高速度的时间数字转换,具有很强的应用价值。

同时,该技术在数字时钟、数字信号处理等领域也有广泛的应用,因此其研究对于提高国内技术水平和推动相关领域的发展具有重要意义。

二、研究目标及内容本研究的主要目标是设计一种基于全数字锁相环的高精度时间数字转换器,并进行实现和验证。

具体而言,研究内容包括:1. 建立全数字锁相环的数学模型和仿真模型,并进行性能分析和优化。

2. 设计和实现基于全数字锁相环的时间数字转换器系统,并对其进行可靠性测试和性能评估。

3. 对实现的时间数字转换器进行误差分析和校准,评估其精度和稳定性。

4. 探索时间数字转换器的应用场景,并对其在雷达、GPS、通信等领域的性能进行测试。

三、研究方法本研究主要采用仿真和实验相结合的方法进行,具体包括:1. 利用MATLAB等工具建立基于全数字锁相环的数学模型和仿真模型,并进行性能评估和优化。

2. 设计和实现基于FPGA(Field Programmable Gate Array)的时间数字转换器原型系统,并进行可靠性测试和性能评估。

3. 对实现的时间数字转换器进行误差分析和校准,评估其精度和稳定性。

4. 在实验室中搭建测试平台,对时间数字转换器在雷达、GPS、通信等领域的性能进行测试和验证。

四、研究成果及预期本研究的最终成果为基于全数字锁相环的高精度时间数字转换器,预期达到以下技术水平:1. 时间分辨率达到纳秒级别,误差小于10 ps。

应用于SoC的全数字锁相环设计的开题报告1. 研究背景随着数字信号处理技术的不断发展,SoC(System on Chip)中集成的数字电路越来越复杂,其内部的时钟分频系统也变得异常重要。

在数字电路系统中,时钟信号的稳定性和精度直接影响数字系统的性能和稳定性。

因此,全数字锁相环(Digital Phase Locked Loop,DPLL)在SoC 中得到了广泛应用。

全数字锁相环是一种数字电路,能够使输入信号与VCO(Voltage-Controlled Oscillator)的频率同步,可以在高达数GHz的速度下实现精确的相位调整。

全数字锁相环没有模拟环路滤波器,具有抗干扰能力强、可调性和调试性好等优点。

因此,在数字电路系统中,全数字锁相环已成为最为常见的时钟同步方案之一。

2. 研究内容本文将深入探讨如何设计一种高性能的全数字锁相环电路,并将其应用于SoC中。

本文的研究内容如下:(1)锁相环的基本原理:介绍锁相环的基本工作原理,包括锁定范围、捕获范围、稳定性等指标的定义与计算。

(2)基本模块设计:详细介绍数字锁相环中的基本模块——相位检测器、数字控制器和VCO,并对每个模块的实现方式进行分析和设计。

(3)噪声分析及抑制:对锁相环中的噪声进行分析和抑制,例如抖动噪声、相位噪声等。

(4)时钟分频及输出:实现数字锁相环的时钟分频功能,并通过分频器输出相应的时钟信号。

(5)仿真分析:利用Cadence仿真工具对所设计的电路进行仿真分析,对电路的性能进行评估。

3. 研究意义本文设计的全数字锁相环电路具有以下特点:(1)采用数字电路实现,具有抗干扰能力强、可调性和调试性好等优点;(2)具有高速、高精度、低杂波等特性,能够满足SoC中对时钟同步的高要求;(3)在电路设计过程中,对噪声进行分析和抑制,提高了电路的稳定性和精度。

本文采用的研究方法为理论研究与实验仿真相结合,能够提高锁相环电路设计的可靠性和优化性。

开题报告专业:电子信息工程全数字锁相环的VHDL设计一、综述本课题国内外研究动态,说明选题的依据和意义锁相技术是一种实现相位自动控制的方法,是专门研究相位的技术。

利用锁相技术得到的锁相环PLL是一个闭环的相位自动控制系统,它的输出信号能够自动跟踪输入信号的相位变化,也可以将之称为一个相位自动跟踪系统,它能够自动跟踪两个信号的相位差,并且靠反馈控制达到自动调节输出信号相位的目的。

锁相环的研究一直是学术界的一个研究重点,由于条件所限,国内对于锁相环的研究主要停留在理论方面,高性能锁相环的产品基本基本依赖进口。

而在国外,锁相环技术则在不断发展,从最初采用分离器件到采用集成电路,从采用双极工艺到使用CMOS 工艺,从需要挂电阻和电容到锁相环完全集成在一块芯片上,并且作为嵌入式IP核应用在大的数字系统中。

随着ASIC芯片电源电压下降,使得电源电压与核心薄氧化器件的阈值电压相比裕量有限从而使模拟电路设计,尤其是低噪声低电压锁相环的设计变得非常困难。

因而,当前锁相环的设计关键集中在高速、低电压、低噪声方面。

目前国外的锁相环产品大多采用3.3V电源电压的CMOS工艺,工作频率可从100MHz一直达到2.4GHz,输出噪声(周期到周期)在几十皮秒左右。

VHDL语言的英文全写是:VHSIC(Very High Speed Integrated Circuit)Hardware Description Language.翻译成中文就是超高速集成电路硬件描述语言。

因此它的应用主要是应用在数字电路的设计中。

其是一种行为描述语言, 其编程结构类似于计算机中的C 语言, 在描述复杂逻辑设计时, 非常简洁,具有很强的逻辑描述和仿真能力,是未来硬件设计语言的主流。

基于VHDL 语言的数字锁相环设计,不仅简化了硬件的开发和制作过程,而且使硬件体积大大减小,并提高了系统的可靠性。

该方法可以在不修改硬件电路的基础上,通过修改设计软件、更改移相范围就可满足不同用户的需要。

CMOS电荷泵锁相环中的数字电路设计的开题报告一、选题背景及意义随着信息技术的不断发展,锁相环(PLL)作为一种重要的时钟同步和频率合成技术得到了广泛的应用。

在锁相环中,电荷泵是其中的重要组成部分,通过输入端的数字信号产生电荷,驱动电容的电荷转移,从而实现倍频、分频等功能。

其中,CMOS电荷泵是应用最广泛的类型之一,具有功耗低、面积小等特点,因此被广泛应用于各种数字电路中。

本课题旨在通过对CMOS电荷泵锁相环数字电路设计的研究与探讨,实现将锁相环的频率与输入信号进行同步,并产生合适的输出信号的功能,从而提高数字电路的稳定性、可靠性和性能。

二、研究内容和方法1、研究内容(1)CMOS电荷泵的基本原理及特性分析;(2)锁相环的基本原理和结构,以及CMOS电荷泵在锁相环中的应用;(3)详细分析和设计CMOS电荷泵锁相环的数字电路,包括电荷泵、反相器、相位频率检测器、比较器等组成部分,实现输入信号与输出信号同步,并输出相应的信号;(4)利用电路仿真工具进行电路仿真,分析电路性能和参数对电路工作的影响。

2、研究方法(1)查阅相关文献,系统学习CMOS电荷泵和锁相环技术原理与特性,全面了解相关概念和术语;(2)利用EDA工具(如Cadence等)设计CMOS电荷泵锁相环电路,并进行电路仿真和电路性能分析,分析参数变化对电路性能的影响;(3)通过文献分析和仿真结果,总结锁相环数字电路中常见的问题和解决方案,完善电路设计。

三、预期结果与意义本课题将研究并设计出一种基于CMOS电荷泵的锁相环数字电路,并通过仿真等实验验证电路的性能和参数。

同时,对电路中常见的问题和解决方案进行总结和分析,提高数字电路工程师对该技术的认识和应用能力,为数字电路的稳定性、可靠性和性能提高提供理论依据和技术支持。

全数字锁相环的设计及分析1 引言锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。

传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。

随着数字技术的发展,全数字锁相环ADPLL(AllDigital Phase-Locked Loop)逐步发展起来。

所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。

与传统的模拟电路实现的锁相环相比,由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点,从而具备可靠性高、工作稳定、调节方便等优点。

全数字锁相环的环路带宽和中心频率编程可调,易于构建高阶锁相环,并且应用在数字系统中时,不需A/D及D/A转换。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA)技术的发展,可以采用大规模可编程逻辑器件(如CPLD或FPGA)和VHDL语言来设计专用芯片ASIC和数字系统。

本文完成了全数字锁相环的设计,而且可以把整个系统嵌入SoC,构成片内锁相环。

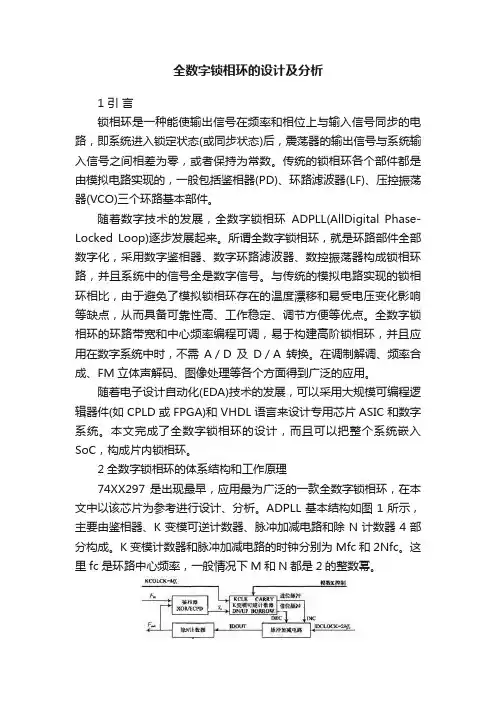

2全数字锁相环的体系结构和工作原理74XX297 是出现最早,应用最为广泛的一款全数字锁相环,在本文中以该芯片为参考进行设计、分析。

ADPLL基本结构如图1所示,主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器4部分构成。

K变模计数器和脉冲加减电路的时钟分别为Mfc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

2.1 鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD)。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差θe,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

锁相环的研究与设计——用于DSP芯片时钟发生器

的开题报告

一、研究背景

随着现代数字信号处理技术的日益成熟,数字信号处理(DSP)芯片在通信、音视频处理、图像处理等领域得到了广泛应用。

因为DSP芯片需要精确的时钟信号来同步各个模块之间的数据传输,常用的时钟发生器是基于晶振的,然而晶振的频率稳定性和精度难以满足高精度时钟信号的要求。

锁相环(PLL)是一种常用的时钟发生器,用于将一个参考时钟信号锁定到设定频率的输出时钟信号。

锁相环可以提供相对于晶振更高的频率稳定性和精度,适用于DSP芯片的时钟信号发生器。

二、研究内容

本论文将重点研究锁相环的理论原理与设计方法,并将其应用于DSP芯片的时钟发生器中。

主要研究内容包括:

1. 锁相环的基本结构和原理。

重点分析锁相环中的相位检测器、环路滤波器和控制电路等核心组成部分,并探讨其作用和影响因素。

2. 锁相环的设计方法。

基于理论分析和电路实现,设计一种高性能的锁相环,包括参数选取、电路布局和仿真验证等环节。

3. DSP芯片时钟发生器的整体设计。

将锁相环与其他电路模块相结合,构建一个完整的DSP芯片时钟发生器,并对其进行整体性能测试与验证。

三、研究意义

本论文的研究结果可以为DSP芯片时钟发生器的设计与制造提供参考,并为相关领域的进一步研究提供理论基础和实践经验。

同时,本研究探讨的锁相环设计方法可适用于其他电子设备中时钟发生器的设计与制造,具有一定的普适性和推广价值。

宽带全数字锁相环中数控振荡器设计开题报告一、选题背景随着现代通信网络的迅速发展,数据传输速率需求不断提高,数字锁相环及其关键部件数控振荡器作为频率合成器的代表性元件,越来越多地应用于数字通信领域。

为了满足高速通信系统的要求,设计一款高精度、高性能、低功耗的数字锁相环已成为研究热点。

数控振荡器是数字锁相环的核心部件之一,其作用是产生稳定的参考时钟信号,因此数控振荡器的设计也是数字锁相环设计中的关键环节。

二、选题意义数字锁相环及其关键部件数控振荡器作为频率合成器的代表性元件,应用广泛。

在高速通信系统中,数字锁相环及数控振荡器的高精度、高性能、低功耗等特性对于数据传输速率的保障至关重要。

因此,开展数字锁相环及数控振荡器的研究和改进,有助于提高通信系统的性能,提升其应用价值。

三、选题内容本文拟重点研究数控振荡器的设计问题,包括以下内容:1. 数字锁相环及数控振荡器的基本原理介绍。

2. 数控振荡器的设计方法和步骤。

3. 数控振荡器中的关键技术问题,包括开环输出波形、相位噪声、频率稳定度等。

4. 数控振荡器的硬件实现方案,包括振荡电路、数字控制器等。

5. 数控振荡器的性能测试方法及测试结果分析。

6. 数控振荡器的应用场景和未来发展方向。

四、预期研究成果本文拟设计一款基于FPGA的数控振荡器,实现高精度、高性能的参考时钟信号输出,预期达到以下成果:1. 基于数控振荡器实现稳定的参考时钟信号输出,具有高精度和低相位噪声特性。

2. 实现可编程的参考时钟频率控制功能,支持多种应用场景。

3. 分析和验证设计方案的性能指标,如频率稳定度、相位噪声、功耗等,掌握设计过程中关键技术。

4. 预期开展数控振荡器应用领域的研究,对数字锁相环的改进和优化提供支持。

五、研究方法本文拟综合采取理论分析、模拟设计及硬件验证等方法,具体包括:1. 对数控振荡器的理论进行分析研究,深入了解数字锁相环的基本原理和数控振荡器的工作原理。

2. 借鉴文献,以xilinx FPGA为平台,进行数字锁相环及数控振荡器的建模、仿真与实现,对数控振荡器进行仿真和测试,分析并改进设计方案。

基于FPGA的全数字锁相环的设计与应用的开题报告一、选题背景和研究意义随着现代电子技术的快速发展,锁相环技术已经成为一种应用广泛的时钟和信号处理技术。

锁相环的作用主要是将输入信号的时钟同步到自己的时钟上,以提高系统的可靠性和精度。

特别是在通信、雷达、测量等领域,锁相环的应用非常广泛。

基于FPGA的全数字锁相环具有易于实现、灵活性高、可编程性强等优点,已经被广泛应用。

本课题将研究基于FPGA的全数字锁相环的设计与应用,旨在探究全数字锁相环在不同应用场景下的性能和特点,并提出相应的优化策略和算法,以期对相关领域的发展贡献一份力量。

二、研究内容和方法本课题研究内容主要包括以下三个方面:1. 基于FPGA的全数字锁相环的原理与实现:主要研究全数字锁相环的工作原理和实现方法,包括相位检测器、数字控制环路、数字滤波器等模块的设计与实现。

2. 全数字锁相环在通信领域中的应用:主要研究全数字锁相环在通信领域的应用,包括同步检测、时钟恢复等。

从实际应用出发,考虑锁相环在通信系统中的性能要求、关键技术以及优化策略等。

3. 全数字锁相环在雷达测量领域中的应用:主要研究全数字锁相环在雷达测量领域中的应用,包括实时采集、数字化处理等。

从实际应用出发,考虑锁相环在雷达测量系统中的性能要求、关键技术以及优化策略等。

本课题将采用理论分析与实验验证相结合的方法进行研究,通过FPGA平台的搭建与实验验证,探究不同场景下的设计方法和性能特点,并提出相应的优化方案。

三、预期研究成果本课题预期达到的主要研究成果包括:1. 基于FPGA的全数字锁相环的工作原理和实现方法,包括相位检测器、数字控制环路、数字滤波器等模块的设计与实现。

2. 探究全数字锁相环在通信领域和雷达测量领域中的性能和特点,提出相应的设计方案、算法和优化策略。

3. 实现基于FPGA的全数字锁相环并进行实验验证,验证全数字锁相环的性能和可靠性。

四、可行性分析本课题所需要的FPGA平台、实验仪器和相关软件等均已具备条件,并且本课题所涉及的理论和实验技术已经成熟,可行性较高。

实验二数字锁相环

一.实验目的

1. 了解数字锁相环的基本概念

2. 熟悉数字锁相环与模拟锁相环的指标

3. 掌握全数字锁相环的设计

二.实验仪器

1.ZH5001通信原理综合实验系统一台

2.20MHz双踪示波器一台

3.函数信号发生器一台

三.实验内容

3. 同步带宽测量:

增加函数信号发生器输出频率TPMZ03,TPMZ02两点波形失步前频率为62khz

降低函数信号发生器输出频率TPMZ03,TPMZ02两点波形失步前频率为66.1khz

同步带:66.1-62=4.1(KHz)

4. 捕捉带测量

增加函数信号发生器输出频率TPMZ03,TPMZ02两点波形失步前频率为62.1khz

降低函数信号发生器输出频率TPMZ03,TPMZ02两点波形失步前频率为66khz

捕捉带:66-62.1=3.9(KHz)

同步带略大于捕捉带

5. 调整信号脉冲观测

改变函数信号发生器输出频率,观测TPMZ05点波形的变化规律。

本科毕业论文(设计、创作)题目:全数字锁相环的研究与设计全数字锁相环的研究与设计摘要本文主要描述了一种设计一阶全数字锁相环的方法,首先分析了课题研究的意义、锁相环的发展历程研究现状,然后描述了全数字锁相环的各个组成部件,并且详细分析了锁相环鉴相器、变模可逆计数器、加减脉冲电路、除H计数器和除N计数器各个模块的工作原理。

接着我们使用了VHDL语句来完成了鉴相器、数字滤波器和数字振荡器的设计,并且分别使用仿真工具MAX+plus II逐个验证各个模块的功能。

最后,将各个模块整合起来,建立了一个一阶全数字锁相环的电路,利用仿真工具MAX+plus II 验证了它的功能的能否实现,仿真结果与理论分析基本符合。

关键词:全数字锁相环;VHDL;数字滤波器;数字振荡器;锁定时间Design and research of ALL Digital Phase-LockedLoopAbstractIn this brief, we presented a way of designing a first-order ALL Digital Phase-Locked Loop (ADPLL) first analyzes the significance of research, the development course of phase-locked loop current research status, and then describes the component parts of all digital phase-locked loop, and detailed analysis of the phase lock loop phase discriminator, reversible counter change mould, add and subtract pulse circuit, in addition to H counter and divide N working principle of each module. Then we use the VHDL statements to complete the phase discriminator, digital filter and the design of the digital oscillator, and using the simulation tool of MAX + plus II one by one to verify the function of each module. Finally, the various modules together, established a first-order digital phase-locked loop circuit, using the simulation tool of MAX + plus II verify the realization of its function, the simulation results and principleKeywords: All Digital Phase-Locked Loop; VHDL; Digital filter; Digitaloscillator, Locking time目录1 引言(绪论) (5)1.1 课题研究的目的意义 (5)1.2 锁相环到全数字锁相环的发展历程 (5)1.3现状和发展 (6)1.4设计工具及设计语言 (7)2 全数字锁相环的结构与工作原理 (7)2.1 鉴相器 (10)2.2变模可逆计数器(模数K可预置) (10)2.3加减脉冲电路 (10)2.4除H计数器 (10)2.5 除N计数器 (10)3全数字锁相环的设计与仿真 (10)3.1鉴相器的设计 (11)3.2 数字环路滤波器的设计 (12)3.3 用VHDL语言实现除H计数器 (15)3.4 用VHDL语言实现加/减脉冲控制器 (15)3.5 除N计数器(分频器)的实现 (16)4 全数字锁相环的整体仿真 (17)5 结论(结束语) (19)主要参考文献 (20)致谢 (21)1.绪论1.1 课题研究的目的意义本次进行研究的课题是全数字锁相环。

一款数字锁相环及其分数分频实现的开题报告标题:一款数字锁相环及其分数分频实现背景:数字锁相环(digital phase-locked loop,DPLL)是一种电路系统,能够将输入信号的相位与一个局部参考信号的相位锁定,并对输入信号进行频率和相位的稳定跟踪。

它在数字通信、数字信号处理等领域广泛应用。

分数分频器(Fractional-N Frequency Divider)是一种将输入频率进行分频的电路。

与整数分频器不同的是,分数分频器可以将输入频率分频为一个分数,从而实现更高的精度。

本文提出了一款数字锁相环及其分数分频实现的方案,其主要特点是:采用开环结构,能够快速锁定输入信号的相位和频率,并能够实现较高的稳定性和精度;采用分数分频器实现分频,能够达到更高的频率控制精度。

方法:数字锁相环的核心部分是相位检测器(Phase Detector),它比较输入信号和本地参考信号的相位差,并输出一个误差信号。

误差信号被输入到控制环节,控制环节通过改变参考信号的频率和相位,使得误差信号趋近于零,从而实现输入信号与参考信号的相位和频率锁定。

本文采用了经典的鉴相相位检测器结构,其输入为输入信号和本地参考信号,输出为误差信号。

控制环节由数字的PID控制器实现,参考信号的频率和相位通过相位累加器和NCO(Numerically Controlled Oscillator)实现。

分数分频器的实现采用了莫尔斯码(Morse code)的思想。

莫尔斯码是一种将字母和数字编码为不同组合点的编码方式,具有多样性和可压缩性。

在分数分频器中,可以将分数编码为两个不同的莫尔斯码,然后将其输出到两个数字时钟模块(Digital Clock Manager)中。

两个数字时钟模块分别输出不同的时钟信号,然后经过一个分频器进行分频,最终得到所需的时钟信号。

结果:本文实现了一款数字锁相环及其分数分频实例电路,应用FPGA进行验证。

实验结果表明,数字锁相环能够快速稳定地锁定输入信号的相位和频率,分数分频器能够实现较高的频率控制精度。

毕业设计(论文)开题报告学生姓名:班级:所在院系:所在专业:设计(论文)题目:锁相放大器指导教师:20年月日毕业设计(论文)开题报告文献综述一、研究背景检测微弱信号的核心问题是对噪声的处理,最简单、最常用的办法是采用选频放大技术,使放大器的中心频率f 0与待测信号频率相同,从而对噪声进行抑制,但此法存在中心频度不稳、带宽不能太窄及对等测信号缺点。

后来发展了锁相放大技术。

它利用等测信号和参与信号的相互关检测原理实现对信号的窄带化处理,能有效的抑制噪声,实现对信号的检测和跟踪。

目前,锁相放大技术已广泛地用于物理、化学、生物、电讯、医学等领域。

因此,培养学生掌握这种技术的原理和应用,具有重要的现实意义。

锁相放大器(lock-in amplifier,LIA)不仅能像选频放大器那样利用信号的频率特性,还抓住了信号的相位特点,即“锁定”了被测信号的相位。

它的等效噪声带宽非常窄,一般可以做到lmHz,远比选频放大器的带宽窄。

因此,基于锁相放大器所具有的输出稳定性、强有力滤除噪声的能力以及能将深埋在噪声中的微弱信号提取出来并加以放大的优良特性,应当选用锁相放大器。

二.锁相放大器的原理参考信号为 Vs(t)=escosωt;待测信号为 Vr(t-τ)=ercos[(ω+Δω)t+φ].在式中r为两个信号的延迟时间。

它们进入乘法器后变换输出为V(t),即由原来以ω为中心频率的频谱变换成以Δω及和频2ω为中心的两个频谱,通过低通滤波器(简称LPF)后,和频信号被滤去,于是经LPF输出的信号为若两信号频率相同(这符合大多数实验条件),则Δω=0,上式变为(3.1.4)式中K是与低通滤波器的传输系数有关的常数。

上式表明,若两个相关信号为同频正弦波时,经相关检测后,其相关函数与两信号幅度的乘积成正比,同时与它们之间位相差的余弦成正比,特别是当待测信号和参考信号同频同位相,即Δω=0,φ=0时,输出最大,即三、相关技术及实现方法锁相放大器对于噪声的抑制能力,是由上图中低通滤波器(LPF)的截止频率来确定的。

青岛大学毕业论文(设计)开题报告题目:全数字锁相环的设计与实现院系:自动化工程学院电子工程系专业:电子信息工程班级:2007级2班姓名:张景楠指导教师:董介春2011年3月14日1 数字锁相环的研究现状及发展趋势锁相环路(PLL)是一个输出信号能够跟踪输入信号相位的闭环自动控制系统。

它在无线电技术的各个领域得到了很广泛的应用。

早在30年代无线电技术发展的初期,锁相环技术就已出现,1930年已建立了同步控制理论的基础,1932年贝尔赛什(Bellescize)提出了同步检波理论,第一次公开发表了锁相环路的数学描述,用锁相环路提取相干载波来完成同步检波。

早期的锁相环路采用电子管,且价格昂贵,只能用在实验装置中,未得到广泛应用。

到了40年代,在电视接收机的同步扫描电路中,开始广泛的应用锁相技术,使电视图像的同步性能得到很大改善。

进入50年代,随着空间技术的发展,由杰费(Jaffe)和里希廷(Rechtin)利用锁相环路作为导弹信标的跟踪滤波器获得成功,并首次发表了包含噪声效应的锁相环路理论分析的文章,同时解决了锁相环路最佳化设计问题。

一种最简单的遥测方式就是信标跟踪,在卫星上装一台低功率的连续波发射机,地面上就可以接收到信号的频率,由于卫星的径向运动而产生多普勒频移,测出多普勒频移大小,就可以算出卫星的径向运动速度,从而测定它的运行轨道。

但是,由于卫星上发射机功率小(毫瓦级),而接收机相距几千乃至几万公里以上,因而接收到的信号异常微弱,加之存在多普勒频移及振荡器的频率漂移,接收机的带宽必须足够的宽才行。

噪声强度与带宽成正比的,这样在接收点的信号噪声功率比必然很低,通常在-10~-30dB的数量级,即所需信号被深深地埋在噪声之中,在此情况下,普通接收机是无能为力的,而只有采用具有锁相环路的窄带锁相跟踪接收机才能把埋在噪声中的信号提取出来。

所以空间技术的发展,促进人们对锁相环路理论及其应用的进一步探讨。

在60年代,维特毕(Viterbl)研究了无噪声锁相环路的非线性理论问题,并发表了“相干通信原理”一书。

青岛大学毕业论文(设计)开题报告题目:全数字锁相环的设计与实现院系:自动化工程学院电子工程系专业:电子信息工程班级:2007级2班姓名:张景楠指导教师:董介春2011年3月14日1 数字锁相环的研究现状及发展趋势锁相环路(PLL)是一个输出信号能够跟踪输入信号相位的闭环自动控制系统。

它在无线电技术的各个领域得到了很广泛的应用。

早在30年代无线电技术发展的初期,锁相环技术就已出现,1930年已建立了同步控制理论的基础,1932年贝尔赛什(Bellescize)提出了同步检波理论,第一次公开发表了锁相环路的数学描述,用锁相环路提取相干载波来完成同步检波。

早期的锁相环路采用电子管,且价格昂贵,只能用在实验装置中,未得到广泛应用。

到了40年代,在电视接收机的同步扫描电路中,开始广泛的应用锁相技术,使电视图像的同步性能得到很大改善。

进入50年代,随着空间技术的发展,由杰费(Jaffe)和里希廷(Rechtin)利用锁相环路作为导弹信标的跟踪滤波器获得成功,并首次发表了包含噪声效应的锁相环路理论分析的文章,同时解决了锁相环路最佳化设计问题。

一种最简单的遥测方式就是信标跟踪,在卫星上装一台低功率的连续波发射机,地面上就可以接收到信号的频率,由于卫星的径向运动而产生多普勒频移,测出多普勒频移大小,就可以算出卫星的径向运动速度,从而测定它的运行轨道。

但是,由于卫星上发射机功率小(毫瓦级),而接收机相距几千乃至几万公里以上,因而接收到的信号异常微弱,加之存在多普勒频移及振荡器的频率漂移,接收机的带宽必须足够的宽才行。

噪声强度与带宽成正比的,这样在接收点的信号噪声功率比必然很低,通常在-10~-30dB的数量级,即所需信号被深深地埋在噪声之中,在此情况下,普通接收机是无能为力的,而只有采用具有锁相环路的窄带锁相跟踪接收机才能把埋在噪声中的信号提取出来。

所以空间技术的发展,促进人们对锁相环路理论及其应用的进一步探讨。

在60年代,维特毕(Viterbl)研究了无噪声锁相环路的非线性理论问题,并发表了“相干通信原理”一书。

到70年代林特赛(Lindscy)和查利斯(Charles)进行了由噪声的一阶、二阶及高阶锁相环路的非线性理论分析,并做了大量实验以充实理论分析。

随着对锁相技术的理论和应用进行广泛深入地研究,目前,锁相技术已经成为一门比较系统的理论科学。

由于锁相环路具有许多优良特性,它可用于频率合成与变换、自动频率调谐跟踪、模拟和数字信号的相干解调、AM波信号的同步检波、数字通信中的位同步提取、锁相稳频、锁相倍频和分频、锁相测速与测距、锁相FM(PM)调制与解调、微波锁相频率源以及微波锁相功率放大器等。

所以,锁相技术的应用已遍及无线电领域,从空间探测、卫星与导弹的跟踪测距、雷达、导航、通信、计算机、激光到电子仪器。

近几年来,冶金、水文地质、电力、机械加工、生产自动化等方面都有广泛应用。

甚至今天锁相环路已出现在每个家庭的电视机接收机和立体声收录机中。

随着半导体集成电路技术的迅速发展,从60年代后期起,已相继试制成功集成化的锁相环路部件及单片集成锁相环路。

今天集成锁相环路的商品种类日益繁多,这将使锁相技术得到更广泛的应用。

我国早在50年代就有许多科学工作者开展了对锁相技术的研究和应用工作。

特别是中远程导弹的定点发射、卫星的发射和回收、同步卫星的发射和定点等技术的发展,都离不开锁相技术,我国在1970年4月24日成功地发射了第一颗人造卫星,地面站对人造卫星发回信号的接收以及遥测控制都证明锁相技术的研究和应用达到了较先进的水平。

我国第一颗人造卫星把“东方红”乐曲传遍了全球,这极大地鼓舞了我国科学工作者攀登世界高峰的斗志。

1984年4月8日,我国成功地发射了试验通信卫星,进入同步轨道正常运行。

1986年2月1日又成功地发射了一颗实用通信广播卫星,准确定点于东经103度赤道上空。

经定点试播,图像和声音质量都达到或超过国际5号卫星的水平。

近年来,除继续发射本国各类卫星外,我国还承接外国卫星的发送业务,亚洲卫星通信有限公司的“亚洲卫星一号”是1990年4月在中国发射的。

这些都充分说明,我国科学工作者和工程技术人员,对锁相技术的研究和应用达到了较先进的水平。

近年来,锁相环路组件逐步由分立元件向中、大规模集成电路发展。

目前北京、上海、甘肃等许多地方的单位都能成批生产中、大规模集成锁相环路和部件,如鉴相器、环路滤波器、压控振荡器、二——十进制可预置可逆计数器以及集成锁相环等,对锁相技术的理论和应用的研究也日益深入、广泛,相应的论文、书籍的发展和出版也逐渐多起来,以适应科学技术的飞速发展和我国现代化建设的需要。

目前,锁相环路的理论研究正日益完善,应用范围遍及整个电子技术领域。

现在锁相环路正向着集成化、数字化、多用途、系列化、高性能方向发展,且商品化集成锁相环路日益增多,为锁相技术应用提供了广阔的前景。

对于锁相环路主要应用于信号的同步,这里有一个小故事:用斧子砍狐狸任何时候都是一件困难的事情,特别是在猎手与狐狸之间有一个180度的相差时。

猎手试图砍到狐狸,但是它不能够“同步”。

很明显,虽然猎手与狐狸以相同的频率行动,但猎手不能达到相位捕捉。

于是,故事悲剧性的发生了:斧子没击中狐狸,而击中拴着它的绳子,狐狸带着偷到的小鸡逃跑了。

简单说锁相环路就是用于正确捕捉信号避免信号丢失的一项技术。

在现代通信系统中,信号同步成为通信中的关键技术。

同步技术使得由发射端发出的信号经传输媒介正确的由接收端接收得到了保证。

同步的技术基础是锁相,因而锁相技术是通信中最重要的技术之一。

锁相就是利用输入信号与输出信号之间的相位误差来自动调节输出信号的相位,使之达到与输入信号的相位一致,或保持一个很小的相位差,从而实现自动调节的功能。

锁相技术现已广泛应用于电子技术的各个领域,特别是在数字通信的调制解调、位同步、频率合成中常常要用到各种各样的锁相环。

最初的锁相环全部由模拟电路组成,由于模拟锁相环存在温度漂移、电网电压的影响等缺点,给系统的同步调节带来了困难。

随着大规模、超大规模数字集成技术的发展,模拟锁相环逐渐被数字锁相环所取代。

由于模拟锁相环存在不少问题,为了改善数字通信系统的同步性能,保证系统工作稳定、可靠,因此发展数字锁相环路也是集成锁相环路发展的重要方面。

锁相环路的数字集成,不仅可靠性提高、降低成本,而且扩大了锁相环路的应用范围。

随着通信及其它电子系统的飞速发展,对系统的准确性、可靠性、小型性等要求越来越高。

大规模集成电路及数字技术的迅速发展,为实现上述要求提供了条件。

VHDL语言(VHSIC Hardware Description Language,VHSIC即为Very High SpeedIntegrated Circuit 的缩写词)是一种行为描述语言,其编程结构类似于计算机中的C 语言,在描述复杂逻辑设计时,非常简洁,具有很强的逻辑描述和仿真能力,是未来硬件设计语言的主流。

运用VHDL 语言设计系统一般采用自上而下分层设计的方法,首先从系统级功能设计开始,对系统高层模块进行行为描述和功能验证。

这样,在电路细节设计之前,先对系统的功能和结构进行验证,可对存在的问题早发现早修改,提高设计效率。

完成系统的功能验证后,就可以将抽象的高层设计,自顶而下逐级细化,直到所用PLD (可编程逻辑器件)结构相对应的逻辑描述。

在细化的过程中,对电路结构清楚的模块可采用结构描述;对采用什么电路结构不确定的模块可采用行为描述。

现在的EDA (电子设计自动化)工具一般都具有逻辑综合的功能,可将行为描述自动转换为与PLD 器件结构相对应的逻辑描述,这给设计者带来了极大地方便,并大大缩短了产品的开发周期。

支持行为描述与结构描述的混合使用,是VHDL 的一个重要特征,具有很大的优越性。

因为VHDL 语言的功能强大,优点突出,因此VHDL 语言自从被定为IEEE 标准后,在各EDA 系统中迅速出现,成为十分流行的硬件描述工具。

2 主要设计内容本设计从模拟锁相环研究出发,掌握锁相环的基本工作原理,了解环路失锁、捕获、跟踪过程及环路锁定条件等。

在分析模拟锁相环缺点的基础上,掌握数字锁相环的工作原理,并用VHDL 语言对该系统进行设计,给出数字锁相环电路各个主要模块的设计过程及仿真结果,得到该系统的顶层电路。

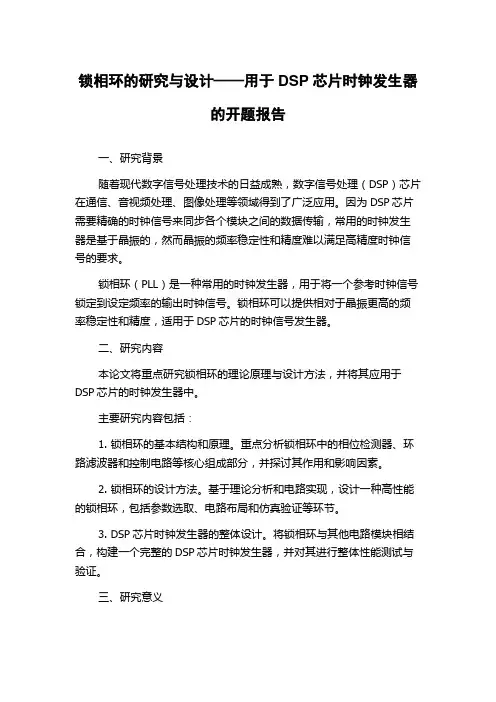

3 拟采取的设计方案数字锁相环电路的系统结构图如图1所示。

由数字鉴相器、数字滤波器和数控振荡器组成。

如果把数字滤波器看成一个分频器,其分频比为KMf c ,其输出频率为: KMf K f c ∆Φ='' (式1)图1 数字锁相环系统框图其中,∆Φ为输入信号1V 与输出信号2V 的相位差;c f 为环路的中心频率。

则数控振荡器的输出频率为:KNMf K f f c ∆Φ+='12 (式2) 由于锁定的极限范围为1'±=∆ΦK ,所以得到环路的捕捉带:KNMf f f f c =-=∆1max 2max (式3) 当环路锁定时,12f f =,系统稳态相位误差:cMf K f f NK ')()(12-=∞∆Φ (式4) 可见,只要合理选择K 值,就能使输出信号2V 的相位较好地跟踪输入1V 的相位,以达到锁定的目的。

如果K 值选的太大,环路捕捉带就会变小,导致捕捉时间增大;如果K 值太小,可能会出现频繁进位、借位脉冲,从而使相位出现抖动。

4 主要研究手段、方法数字锁相环的研究手段,大体可以分为软件仿真和硬件实现两种。

软件仿真即是在通用的微型计算机上用软件实现,如利用Quartus II 进行工程建立、程序编写、原理图输入、波形仿真等步骤最终实现。

而硬件实现则是在软件仿真成功的基础上,将正确的VHDL 程序经过转换下载到FPGA 等可编程逻辑器件中,然后对其应实现的功能进行测试。

5 预期获得的结果最终期望结果是输入信号经过此系统后的输出信号与输入信号频率完全相同,相位差保持恒定。

最终实现的功能是在通信系统中实现同步,即通信系统中发射端发出的信号经过传输媒介在接收端得到正确的接收。

6 课题进度计划调研、设计方案论证、题目发展动态综述,写出开题报告 2周 模拟锁相环的工作原理 1周 环路失锁、捕获、跟踪过程及环路锁定条件的研究 1周 数字锁相环的工作原理 1周 FPGA 芯片结构、设计流程 1周硬件描述语言的编程规则及调试下载方法1周鉴相器的工作原理以及用VHDL语言进行设计仿真1周数字滤波器的工作原理以及用VHDL语言进行设计仿真1周脉冲加/减电路的工作原理以及用VHDL语言进行设计仿真1周分频器的工作原理以及用VHDL语言进行设计仿真1周全数字锁相环总体方案设计、仿真、下载及调试2周撰写毕业设计报告及答辩2周7 参考文献1.樊昌信,通信原理(第四版),国防工业出版社,20012.潘松、黄继业,EDA技术实用教程(第3版),科学出版社,20063.潘松、王国栋,VHDL实用教程(修订版),成都电子科技大学出版社,20014.刘欲晓、方强、黄宛宁,EDA技术与VHDL电路开发应用实践,电子工业出版社,20095.徐志军、徐光辉,CPLD/FPGA的开发与应用,电子工业出版社,20026.张厥盛,锁相技术,西安电子科技大学出版社,1991。