DSP硬件开发平台设计

- 格式:doc

- 大小:259.00 KB

- 文档页数:6

DSP系统的硬件设计又称为目标板设计,是在考虑算法需求、成本、体积和功耗核算的基础上完成的,一个典型的DSP目标板主要包括:DSP芯片及DSP基本系统程序和数据存储器数/模和模/数转换器模拟控制与处理电路各种控制口和通信口电源处理电路和同步电路系统硬件设计过程:第一步:确定硬件实现方案;在考虑系统性能指标、工期、成本、算法需求、体积和功耗核算等因素的基础上,选择系统的最优硬件实现方案。

第二步:器件的选择;一个DSP硬件系统除了DSP芯片外,还包括ADC、DAC、存储器、电源、逻辑控制、通信、人机接口、总线等基本部件。

① DSP芯片的选择首先要根据系统对运算量的需求来选择;其次要根据系统所应用领域来选择合适的DSP芯片;最后要根据DSP的片上资源、价格、外设配置以及与其他元部件的配套性等因素来选择。

② ADC和DAC的选择A/D转换器的选择应根据采样频率、精度以及是否要求片上自带采样、多路选择器、基准电源等因素来选择;D/A转换器应根据信号频率、精度以及是否要求自带基准电源、多路选择器、输出运放等因素来选择。

③存储器的选择常用的存储器有SRAM、EPROM、E2PROM和FLASH等。

可以根据工作频率、存储容量、位长(8/16/32位)、接口方式(串行还是并行)、工作电压(5V/3V)等来选择。

④逻辑控制器件的选择系统的逻辑控制通常是用可编程逻辑器件来实现。

首先确定是采用CPLD还是FPGA;其次根据自己的特长和公司芯片的特点选择哪家公司的哪个系列的产品;最后还要根据DSP的频率来选择所使用的PLD器件。

⑤通信器件的选择通常系统都要求有通信接口。

首先要根据系统对通信速率的要求来选择通信方式。

然后根据通信方式来选择通信器件。

一般串行口只能达到19kb/s,而并行口可达到1Mb/s 以上,若要求过高可考虑通过总线进行通信;⑥总线的选择常用总线:PCI、ISA以及现场总线(包括CAN、3xbus等)。

可以根据使用的场合、数据传输要求、总线的宽度、传输频率和同步方式等来选择。

dsp硬件设计课程设计一、教学目标本课程的教学目标是使学生掌握DSP硬件设计的基本原理和方法,培养学生进行DSP硬件系统设计和实现的能力。

具体目标如下:1.掌握DSP芯片的基本结构和原理。

2.了解DSP硬件设计的基本流程和步骤。

3.熟悉DSP系统的硬件架构和关键模块。

4.能够使用DSP芯片进行硬件系统设计。

5.能够进行DSP系统的硬件调试和验证。

6.能够分析和解决DSP硬件设计中遇到的问题。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.培养学生对DSP硬件设计的兴趣和热情。

3.培养学生对科技发展的关注和对工程实践的重视。

二、教学内容本课程的教学内容主要包括以下几个部分:1.DSP芯片的基本结构和原理:介绍DSP芯片的内部结构、工作原理和特性。

2.DSP硬件设计的基本流程和步骤:讲解DSP硬件设计的过程,包括需求分析、硬件架构设计、硬件电路设计、硬件调试和验证等。

3.DSP系统的硬件架构和关键模块:介绍DSP系统的硬件架构,包括中央处理单元、存储器、输入输出接口等关键模块。

4.DSP硬件设计的实践案例:通过实际案例分析,使学生掌握DSP硬件设计的方法和技巧。

三、教学方法本课程的教学方法将采用多种教学手段相结合的方式,以激发学生的学习兴趣和主动性。

1.讲授法:通过教师的讲解,使学生掌握DSP硬件设计的基本原理和方法。

2.讨论法:通过分组讨论和实践案例的分析,培养学生的思考能力和团队合作精神。

3.实验法:通过实验操作,使学生熟悉DSP硬件设计的实践过程和技巧。

四、教学资源本课程的教学资源包括教材、参考书、多媒体资料和实验设备等。

1.教材:选择适合本课程的教材,为学生提供系统的学习资料。

2.参考书:提供相关的参考书籍,为学生提供更多的学习资源。

3.多媒体资料:制作课件和教学视频,以图文并茂的形式展示教学内容。

4.实验设备:提供DSP实验板和相关的实验设备,为学生提供实践操作的机会。

五、教学评估本课程的教学评估将采用多元化评估方式,全面客观地评价学生的学习成果。

DSP试验完整系统硬件设计确定硬件设计方案,器件选择,原理图设计,PCB板设计,硬件调试1,最小系统设计就是满足DSP运行的最小硬件组成:通常采用低电压设计,双电源供电,即内核电源CVDD(为芯片的内部逻辑提供电压,CPU,时钟电路,所有外设逻辑,1.6V,与3.3相比,课大大降低芯片功耗)和I/O电源DVDD(3.3V,直接与外部低电压器件进行接口,不需要额外的电平转换电路)。

电压转换电路:使用LDO稳压器(5V-3.3V),使用齐纳二极管低成本系统,使用整流二极管,使用开关稳压管,电压比较器,等等。

书上介绍的有MAX748A(5转3.3),TPS7301(5转1.6V),TPS767D301来实现双电源(5转3.3和5转1.6都有)。

咱们系统中应用的是TLV1117来实现电压转换,这是为什么?5V供电外接电解电容和电容用意何在,5V的电通过电阻给电解电容进行充电,电容两端的电会由0V慢慢的升到4V左右(此时间很短一般小于0.3秒),我觉得应该是为了稳压吧,让输入电压稳定在5V。

74LVC04是一个反相器,A为输入,Y为输出,EXT_RESET为1A输入,P4的一个引脚输出口。

EXT_RESET复位信号也送入CPLD(XC9536XL有DSPRST引脚,接主芯片的91),作为系统的复位信号之一。

EXT_RESET反相后,作为SMR接入TL16C550C 异步通信芯片的MR(主复位(高电平有效),清除最ACE 寄存器和置位各种电平的输出信号),也就是说在复位有效时,是不能进行异步串口通信的,这一点说明了复位信号不可屏蔽,在任何时候都能对系统进行复位。

TCK测试时钟输入引脚,TDI测试数据输入信号,TDO测试数据输出信号,TMS测试方式选择信号,TRST测试复位信号,EMU0仿真器中断0引脚,EMU1仿真器中断1引脚/关闭所有输出引脚。

TRST为高事,改引脚作为仿真系统的中断信号,。

为低时,所有输出设置为高阻状态。

基于DSP的永磁同步电机控制系统硬件设计胡宇;张兴华【摘要】以小功率永磁同步电机(PMSM)为研究对象,结合数字信号处理器TMS320F2812功能特点,给出了一套PMSM驱动控制系统硬件设计方案.详细阐述了功率驱动主电路、反馈信号检测电路以及供电电路的设计,介绍了主要元器件选型和参数计算方法.基于设计的硬件平台,对PMSM调速控制系统进行了测试.试验结果表明,所设计的控制系统硬件设计可靠、性能稳定、控制精度高.%Based on the controlled object of small power permanent magnet synchronous motor (PMSM),combined with the main features of digital signal processor TMS320F2812,an overall hardware design scheme had been put forward for the PMSM drive control system.Design of the power driven main circuit had illustrated,signal detection circuit and power supply circuit in detail,meanwhile introduced the main components selection and parameters calculation method.Based on the designed hardware platform,the control system of PMSM had been performed a functional test.Experimental results showed that the hareware design of control system had good reliability with stable performance and high control precision.【期刊名称】《电机与控制应用》【年(卷),期】2017(044)012【总页数】7页(P19-24,80)【关键词】永磁同步电机;功率驱动主电路;信号检测电路【作者】胡宇;张兴华【作者单位】南京工业大学电气工程与控制科学学院,江苏南京211816;南京工业大学电气工程与控制科学学院,江苏南京211816【正文语种】中文【中图分类】TM351永磁同步电机(Permanent Magnet Synchronous Motor,PMSM)因其体积小、损耗低、功率密度高和效率高等优点,在机械制造、工业控制、航空航天等领域得到广泛应用[1]。

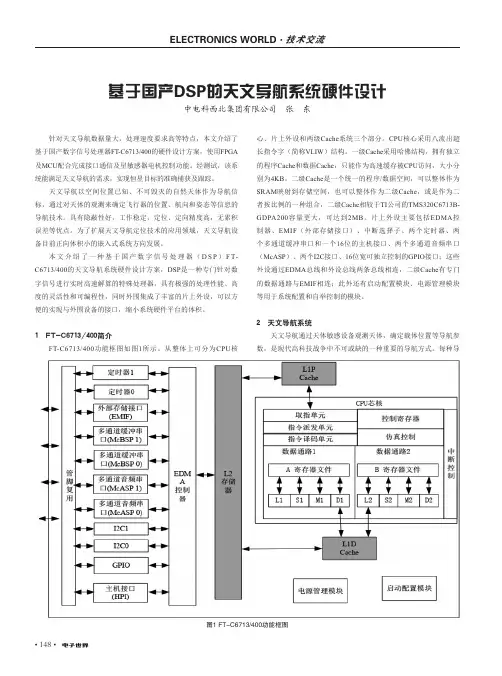

• 148•针对天文导航数据量大,处理速度要求高等特点,本文介绍了基于国产数字信号处理器FT-C6713/400的硬件设计方案,使用FPGA 及MCU 配合完成接口通信及星敏感器电机控制功能。

经测试,该系统能满足天文导航的需求,实现恒星目标的准确捕获及跟踪。

天文导航以空间位置已知、不可毁灭的自然天体作为导航信标,通过对天体的观测来确定飞行器的位置、航向和姿态等信息的导航技术。

具有隐蔽性好,工作稳定,定位、定向精度高,无累积误差等优点。

为了扩展天文导航定位技术的应用领域,天文导航设备目前正向体积小的嵌入式系统方向发展。

本文介绍了一种基于国产数字信号处理器(D S P )F T-C6713/400的天文导航系统硬件设计方案,DSP 是一种专门针对数字信号进行实时高速解算的特殊处理器,具有极强的处理性能、高度的灵活性和可编程性,同时外围集成了丰富的片上外设,可以方便的实现与外围设备的接口,缩小系统硬件平台的体积。

1 FT-C6713/400简介FT-C6713/400功能框图如图1所示。

从整体上可分为CPU 核心、片上外设和两级Cache 系统三个部分。

CPU 核心采用八流出超长指令字(简称VLIW )结构。

一级Cache 采用哈佛结构,拥有独立的程序Cache 和数据Cache ,只能作为高速缓存被CPU 访问,大小分别为4KB 。

二级Cache 是一个统一的程序/数据空间,可以整体作为SRAM 映射到存储空间,也可以整体作为二级Cache ,或是作为二者按比例的一种组合,二级Cache 相较于TI 公司的TMS320C6713B-GDPA200容量更大,可达到2MB 。

片上外设主要包括EDMA 控制器、EMIF (外部存储接口)、中断选择子、两个定时器、两个多通道缓冲串口和一个16位的主机接口、两个多通道音频串口(McASP )、两个I2C 接口、16位宽可独立控制的GPIO 接口;这些外设通过EDMA 总线和外设总线两条总线相连,二级Cache 有专门的数据通路与EMIF 相连;此外还有启动配置模块、电源管理模块等用于系统配置和自举控制的模块。

的灵活性和适应性。

图1为本信号处理系统的功能框图。

图1信号处理系统的功能框图数字脉冲压缩本雷达采用固态发射机,峰值功率受限,只能通过增加发射机的平均功率来提高作用距离。

提高发射机平均功率的办法就是要进一步加大发射脉冲的时宽。

但是,脉冲宽度的增加带来了距离分辨率的降距离分辨率和作用距离之间试一对矛盾体,解决这一矛盾的方法位寄存器的延迟数与卫星编号相关。

图4P码发生器及时域波形2.3导航电文数据码产生GPS的导航数据码的播发速度是50HZ bit,对于GPS接收的射频前端和数字中频,该数据码可以用Bernoulli随机分布模型来模拟[5],在Simulink仿真环境中可以直接调用Bernoulli模块直接产生随机序列。

2.4BPSK调制完成C/A码、P码和导航数据码等基带处理后需要对其进行BPSK调制。

BPSK调制时将基带单极性码(0,1)转换成双极性码(-1,1),然后将其乘上载波。

二进制单极性码转为双极性码的转换原理为:将输入左移1位后减1。

得到双极性码后乘上正弦波就得到调制波形。

3GPS信号的基带等效仿真由于GPS LI载波频率为1575.42MHz,若在Simulink平台下直接为基带等效通信系统进行仿真。

图5是基带仿真频谱图。

图5GPS L1基带仿真频谱图小结本文利用Simulink工具产生L1波段上的GPS信号,给出了C/A 码,数据码,BPSK等模块的仿真图,主要针对基带信号仿真。

1575.42MHz的L1波段。

由于频率较高,时域仿真不太现实,因此将频带通信系统转化为基带等效通信系统进行仿真。

【参考文献】谢钢.GPS原理与接收机设计[M].电子工业出版社.邓炜,杨东凯,寇艳红.GPS中频信号处理的Simulink实现[J].遥测遥控,2006,11,27沈超,裘正定.基于MatLab/Simulink的GPS系统仿真[J].系统仿真学报,2006,7,18涂凤琴.GPS中频卫星信号的仿真研究[D].南京:南京理工大学,2010.陈涛.GPS接收机基带信号处理的研究和设计[D].上海:上海交通大学,2009.[责任编辑:汤静(上接第69页)缘内侧虚警概率显著增加的现象。

简述使用DSP芯片进行系统开发的一般流程1. 概述DSP(Digital Signal Processor)芯片是一种专门用于处理数字信号的芯片,广泛应用于通信、音视频处理等领域。

使用DSP芯片进行系统开发需要经过一系列的步骤和流程,本文将简要介绍一般的开发流程。

2. DSP系统开发流程2.1 需求分析首先,在进行DSP系统开发之前,需进行需求分析,明确系统的功能和性能要求。

根据需求,确定DSP芯片的型号和规格,并确定系统的硬件和软件接口要求。

2.2 硬件设计硬件设计是DSP系统开发的重要一环。

根据需求分析,进行DSP系统的硬件设计,包括电路原理图和PCB设计。

在设计过程中,需要考虑电源、时钟、接口电路等因素,确保硬件设计满足系统要求。

2.3 软件设计软件设计是DSP系统开发的关键环节。

根据需求和硬件设计,进行DSP系统的软件设计。

具体步骤包括编写算法和信号处理流程、选择适当的编程语言和开发工具、设计系统框架和接口等。

2.4 软件开发在软件设计的基础上,进行DSP系统的软件开发。

根据软件设计确定的算法和接口,使用相应的编程语言和开发工具,编写软件代码。

在开发过程中,需要进行代码调试、性能优化和错误修复等工作。

2.5 硬件调试完成软件开发后,进行DSP系统的硬件调试。

通过连接电源、外部设备和接口,对DSP系统进行调试和测试。

此阶段还可以进行性能测试和功能验证。

2.6 系统集成在完成硬件调试后,进行DSP系统的系统集成。

将软件和硬件组合起来,确保系统正常运行。

在此阶段,需要进行整体测试和交付前的验收。

2.7 产品发布和维护完成系统集成后,进行DSP系统的产品发布。

将DSP系统交付给客户或用于实际应用。

同时,需要进行系统的维护和迭代,及时修复BUG和优化性能。

3. 总结使用DSP芯片进行系统开发涉及多个步骤和流程,包括需求分析、硬件设计、软件设计、软件开发、硬件调试、系统集成、产品发布和维护等。

通过合理的规划和有序的流程,可以确保DSP系统开发的顺利进行,并最终得到可靠和高性能的系统。

西安文理学院机械电子工程系本科毕业设计(论文)题目基于DSP的语音采集系统硬件设计专业班级学号学生姓名指导教师设计所在单位机械电子工程系西安文理学院本科毕业设计(论文)任务书西安文理学院本科毕业设计(论文)开题报告注:此表前三项由学生填写后,交指导教师签署意见,经教研室审批后,才能开题。

西安文理学院本科毕业设计(论文)中期检查表西安文理学院本科毕业设计(论文)答辩记录注:1、毕业论文成绩=指导教师成绩×40%+评阅教师成绩×20%+答辩成绩×40%;2、论文等级分优秀(≥90分)、良好(80~89分)、中等(70~79分)、及格(60~69分)、不及格(<60分)。

基于TMS320VC5416的语音采集系统摘要:设计采用TMS320VC5416 DSP芯片及TLC320AD50C 语音芯片,制作了一个高精度语音采集回放系统。

系统可实现对语音信号的无失真采样,满足后续的语音信号处理的要求,并可实现对语音信号录音回放或者经DSP实时处理放音等功能。

本设计从硬件到软件提供了一套完整的解决方案。

对于系统硬件部分,采用TMS320VC5416-160作为采集回放控制及算法处理器。

TLC320AD50C作为语音信号AD/DA转换芯片,采用DSP的多缓冲串口通道进行接收中断方式读取数据,读取的数据分页存放在外扩的SRAM中,可通过JATG 口读取采集的数据。

系统配有AM29LV800B FLASH存储芯片用来存放程序、数据,掉电不丢失。

系统软件部分采用CCS2.0集成环境及SZ-DSPF仿真平台进行设计及仿真,软件设计语言采用汇编及C语言进行编写,并给出了各个模块的驱动程序及详细软件实现方案。

关键词:TMS320VC5416; TLC320AD50C; 语音采集; 录音回放Audio collection system based on TMS320VC5416Abstract:The design uses a TMS320VC5416 DSP chip and TLC320AD50Caudio chip, the production of a high-precision audio capture playback system. System can realize the lossless audio signal sampling, follow-up of the voice signal processing to meet the requirements, and can realize the speech signal recording or playback of real-time processing by the DSP playback functions. This design from hardware to software to provide a complete solution. The hardware part, by collecting TMS320VC5416-160 as the playback control and algorithm processor. TLC320AD50C as a voice signal AD / DA converter chips, using DSP multi-channel buffered serial port receiver interrupt read data, read out the data page stored in the expansion of the SRAM can be read by JATG population data collected. System with AM29LV800B FLASH memory chips used to store programs, data, power down is not lost. Software part is CCS2.0 integrated simulation environment and the SZ-DSPF Design and simulation platform, software language using C language compilation and preparation, and gives the driver of each module, and details of software implementation.Key words:TMS320VC5416; TLC320AD50C; Audio collection; Recording playback目录第一章绪论 (1)1.1 选题的目的与意义 (1)1.2 本课题的发展趋势 (1)1.3 本课题主要研究内容 (2)1.4 论文的结构说明 (2)第二章 TMS320VC5416结构及原理 (3)2.1 哈佛结构 (3)2.2 流水线结构 (3)2.3 专用硬件乘法器 (4)2.4 特殊的DSP指令 (4)2.5 快速的指令周期 (5)2.6 硬件组成框图 (5)第三章语音采集系统的整体方案介绍 (6)3.1系统介绍 (6)3.2系统指标 (6)3.3系统结构框图 (6)3.4芯片选型方案 (7)3.4.1主芯片 (7)3.4.2语音处理芯片 (8)3.4.3语音放大芯片 (8)3.4.4存储芯片 (9)3.4.5显示芯片 (9)3.4.6电源芯片 (9)第四章语音采集系统的硬件设计 (10)4.1硬件电路设计 (10)4.1.1 电源设计 (10)4.1.2 存储模块设计 (12)4.1.3 DSP外围电路设计 (15)4.1.4 显示模块 (17)4.1.5 语音放大模块 (18)4.1.6 语音转换模块 (20)4.1.7 外围接口 (21)4.1.8 按键设计 (22)4.2硬件工具介绍 (23)4.2.1 DSP实验平台 (23)4.2.2 电路图设计工具 (24)4.2.3 硬件调试仪器 (24)第五章语音采集系统的软件设计 (25)5.1软件设计框架 (25)5.2驱动层软件设计 (25)5.2.1 DSP初始化设计 (25)5.2.2 AD50驱动设计 (27)5.2.3 存储驱动设计 (29)5.2.4 显示驱动设计 (30)5.3应用层软件设计 (32)5.3.1 按键设计 (32)5.3.2 采集回放设计 (34)5.3.3 显示应用设计 (35)5.4软件设计工具介绍 (35)第六章语音采集系统的应用测试 (37)6.1硬件测试 (37)6.2软件测试 (38)结束语 (39)致谢 (40)参考文献 (41)附录 (42)1硬件原理图 (42)2硬件布线图 (47)3主程序清单 (49)第一章绪论1.1 选题的目的与意义目前,由于具有运算速度快、片上资源丰富和能够实现复杂的线性和非线性算法等特性,DSP已成为通信、雷达、声纳和消费电子产品等领域的基础器件,其中在图像、语音信号处理技术方面显得尤为突出。

基于软件通信体系结构的DSP硬件抽象层研究与设计石贱弟;赵小璞【摘要】Software communications architecture is the only standard of software radio system architecture, which was approved by JPO of the department of defense in USA. At Present, the waveform development based on SCA can not create good portability and reusable components.In this paper, it presents a method for implement DSP HAL-C based on SCA after study on SCA SHS and HAL-C. The result of the test demonstrates the method is flexible in implementing and can create few resource depend and good portability components. This method also accords with the idea of SCA HAL-C.%软件通信体系结构是美国国防部的联合计划办公室JPO发布的关于软件无线电体系架构的唯一标准,当前基于软件通信体系结构的波形组件的开发存在可移植性差、重用性低等问题。

论文在对软件通信体系结构专用硬件补充规范中的硬件抽象层连通性HAL-C内容进行了深入研究的基础上,提出了一种基于软件通信体系结构的DSP硬件抽象层连通性的实现方法。

实践证明,该方法符合软件通信体系结构的硬件抽象层连通性设计思想,并具有实现方便、组件可移植性好、占用资源少等特点。

基于dsp的毕业设计基于DSP的毕业设计一、引言数字信号处理(Digital Signal Processing,DSP)是一门研究如何对数字信号进行处理和分析的学科。

它在现代通信、音频处理、图像处理等领域有着广泛的应用。

本文将探讨基于DSP的毕业设计,介绍其背景、意义以及实施过程。

二、背景与意义随着科技的不断发展,DSP技术在许多领域都扮演着重要的角色。

在音频处理中,DSP可以用于降噪、音效增强等方面;在通信领域,DSP可以用于信号解调、编码等方面。

因此,基于DSP的毕业设计具有重要的实践意义。

三、设计目标与方案基于DSP的毕业设计的设计目标通常是解决一个特定的问题或实现一个特定的功能。

例如,可以设计一个音频降噪系统,通过DSP算法对音频信号进行处理,降低噪声干扰;也可以设计一个实时图像处理系统,通过DSP算法对图像进行滤波、边缘检测等操作。

在设计方案上,可以选择使用现有的DSP开发板或自行设计硬件平台。

同时,需要选择适合的DSP开发环境和编程语言,如MATLAB、C语言等。

根据设计目标,选择合适的DSP算法和实现方法,并进行系统设计、算法调试等工作。

四、实施过程1. 系统需求分析:根据设计目标,明确系统的功能需求和性能指标。

如音频降噪系统的信噪比要求、图像处理系统的实时性要求等。

2. 硬件平台选择:根据需求选择合适的DSP开发板或自行设计硬件平台。

考虑到成本、性能等因素,可以选择TI、ADI等厂商的DSP开发板。

3. 开发环境选择:根据硬件平台选择合适的开发环境和编程语言。

如使用MATLAB进行算法开发和仿真,使用C语言进行DSP程序的编写。

4. 算法设计与实现:根据设计目标选择合适的DSP算法,并进行算法设计和实现。

可以使用现有的算法库,也可以自行设计和优化算法。

5. 系统集成与调试:将算法与硬件平台进行集成,并进行系统调试和性能测试。

根据测试结果进行优化和改进。

6. 结果分析与总结:对系统的性能进行分析和评估,总结设计过程中的经验和教训。

2010 - 2011学年第 2 学期《DSP芯片的原理与开发应用》题目:DSP硬件开发平台设计班级:学号:姓名:指导教师:成绩:基于DSP E1-16XS的硬件开发平台设计引言嵌入式系统硬件的核心是各种类型的嵌入式处理器,目前全世界嵌入式处理器的品种已经超过1000多种,流行体系结构有30多个系列,嵌入式处理器一般可以分为嵌入式微处理器、嵌入式微控制器、嵌入式DSP处理器和嵌入式片上系统。

与标准微处理器相比,嵌入式微处理器只保留了和嵌入式应用有关的功能,并且为了满足嵌入式应用的特殊要求,在工作温度、抗电磁干扰、可靠性等方面都做了各种增强。

DSP嵌入式系统是DSP系统嵌入到应用电子系统中的一种通用系统,这种系统既具有DSP器件在数据处理方面的优势,又具有应用目标所需要的技术特征,在许多嵌入式应用领域,既需要在数据处理方面具有独特的优势的DSP,也需要在智能控制方面技高一筹的微处理器(MCU);因此,将DSP与MCU融合在一起的双核平台,将成为DSP技术发展的一种新潮流。

德国Hyperstone公司是真正把DSP 成功嵌入32位微处理器的厂商之一,尤其是它的E1-XS系列更是这方面的佼佼者。

1 E1-16XS微处理器结构概述Hyperstone RISC/DSP架构框图如图1所示,Hyperstone内核是专为RISC和DSP功能的集成而设计的,但它不是两个不同内核在单个芯片上的简单组合,而是一个集成的内核和指令集。

这一全集成的内核基于单处理器模式,带有单指令流。

RISC和DSP单元间简单且高效的通信由1个96路的32位内部存储器实现,每个时钟周期内可以执行3条指令的操作,所以在100MHz的频率下可以达到300 MOPS这样优秀的性能。

Hyperstone E1-16XS是一款0.25μm CMOS工艺的微处理器,它结合了高性能的RISC微处理器和DSP处理器,利用简洁高效的指令,使嵌入式DSP处理器的实时性得以充分的发挥。

该处理器主要具有如下的特点:1、32位RISC/DSP处理器ALU、DSP单元和Load/Store单元并行处理,内部集成硬件乘法器。

2、16根数据线,22根地址线,4个外部存储体(Memory Bank)选择信号。

3、4GB内存地址空间,I/O空间和存储空间分开寻址,存储器和DSP连接无需附加逻辑电路。

4、片内集成16KB RAM和片上指令高速缓存。

5、具有全面的DRAM和DMA控制器,所有的总线时序可编程。

6、片上PLL、CPU总高频率可达到180MHz。

7、中断服务程序可在7个时钟周期内启动。

除内部中断外,还有7个外部中断可用。

8、3个可编程I/O引脚除了可配置成输入输出外,还可以配置成外部中断输入使用。

9、32位定时器和看门狗定时器,用户可利用hyRTK内核访问154个独立的"虚拟"定时器,仅需很少的处理开销。

2 嵌入式系统硬件设计2.1 系统硬件结构系统硬件结构如图2所示。

电源电路:输入5V,经过DC-DC变换,分别给微处理器提供2.5V和3.3V的电压。

晶振电路:16MHz有源晶体振荡器经过倍频,分别为Hyperstone内核/系统提供128/64MHz的时钟频率。

复位电路:可选用简单的RC复位电路,考虑到系统复位的可靠性和掉电监控,建议使用专门的复位IC,例如MAX706。

微处理器:即E1-16XS,是系统的工作和控制中心。

Flash:可存放Boot监控程序、嵌入式操作系统、用户应用程序或其他在系统掉电后需要保存的数据。

SDRAM:系统代码运行和数据变量存储的空间。

JTAG接口:通过该接口可对系统进行在线调试和程序下载。

I/O扩展接口:引出数据总线、地址总线和必需的I/O控制总线,便于用户根据自身的特定需求,扩展外围电路;DSP可以通过该扩展总线对其他板卡进行控制,或者其他板卡可以通过该接口对开发板进行操作。

2.2 系统主要硬件单元电路设计不同的DSP处理器在与DRAM、Flash连接时通常会有些差异,所以下面着重分析存储器接口电路的工作原理和设计方法。

(1)Flash接口电路由于Flash存储器具有低功耗、大容量,可整片或分扇区快速烧写、擦除、掉电后信息不丢失等特点,在各种嵌入式系统中得到广泛应用。

本系统中,Flash存储器采用Hynix的HY29LV160。

他是16位数据宽度,存储容量为16Mb(2MB),可以在2.7-3.6V电压范围内进行读、编程(烧写)和擦除操作。

在大多数系统中,选用1片16位的Flash存储器芯片(单片容量有1MB、2MB、4MB、8MB等)构建16位的Flash存储系统已经足够。

在此采用1片HY29LV160构建16位的Flash存储器系统,图3为16位模式Flash与处理器E1-16XS的基本接法。

Flash存储器在系统中通常用于存放程序代码,系统上电或复位后从此获取指令并开始执行。

因此,应将存有程序代码的Flash存储器配置到Bank3,即将E1-16XS的CS3接至HY29LV160的片选端CE。

输出使能端OE接E1-16XS的OE;写使能端WE接E1-16XS的WE1,模式选择BYTE上拉,使HY29LV160工作在16位数据模式。

RY/BY(就绪/忙)指示HY29LV160编程或擦除操作的工作状态。

HY29LV160地址总线A[19-0]与E1-16XS的地址总线A[20-1]相连;16位数据总线D[15-0]与E1-16XS的16位数据总线D[15-0相连,此时应将E1-16XS 的BOOTB置为0,即选择外部Flash为16位工作方式。

(2)DRAM接口电路与Flash存储器相比较,动态随机存储器DRAM虽然不具有掉电保持数据的特性,但其存取速度大大高于Flash存储器,在系统中主要用作程序的运行空间。

E1-16XS内部的DRAM控制器支持DRAM的各种形式,例如Fast-Page Mode、EDO 和SDRAM,都可以直接和处理器无缝连接。

存储器存取的总线时序刷新控制等可由总线控制寄存器(BCR)设定,这里以目前嵌入式系统设计中常用的SDRAM说明电路的具体连接。

系统中SDRAM选用IS42S16100-7T。

它的存储容量为2Banks×512K×16位(2MB),工作电压为(3.3±0.3)V,16位数据宽度,如果用户需要运行嵌入式操作系统以及各种相对较复杂的功能,可以考虑增加SDRAM的容量,E1-16XS最大支持128MB。

图4为IS42S16100-7T SDRAM存储器和E1-16XS的连接框图,将该SDRAM配置到系统存储器的Bank0,即将E1-16XS的DP0(SDRAM选择信号)接至IS42S16100的CS端,表1可以清晰地反应出E1-16XS和IS42S16100的连接情况。

(3)I/O扩展由于DSP本身的I/O口相对比较少,在很多应用场合下,需要进行I/O扩展,E1-16XS内部I/O总线控制寄存器提供了6位作为芯片选择用,有就是可以连接64个周边器件;另外还有3位作为I/O器件内部寄存器地址寻址用,9位用来设定读写访问的总线时序设置,例如地址建立时间和保持时间等,这样可以降低对外设的访问速度,适应低速外设的要求,一般对外设I/O的访问连接如图5所示。

图5中,IORD和IOWR为I/O访问时的读控制信号和写控制信号,分别连接到I/O 设计的读和写控制端;I/O设备的中断输出信号INT连接到DSP的中断输入信号INTn。

E1-16XS提供了最多7个外部中断输入可供连接。

3 PCB板设计要点设计好电路图后,就可以设计PCB板了,在系统中,E1-16XS的片内工作频率可以达到150MHz以上,系统总线频率也接近100MHz,因此,在PCB设计过程中,应该遵循高频电路设计的基本原则。

首先应注意电源的质量与分配,其次要注意信号线和时钟线的分布。

(1)电源质量与分配在设计PCB板时,给各个单元电路提供高质量的电源,会使系统的稳定性大幅度提高。

一般应在电源进入印刷电路板的位置和靠近各器件的电源引脚处加上几十~几百μf的电容,以滤除电源噪声,还要注意在器件的电源和地之间加上0.01μF-0.1μF左右的电容,用来滤除元器件工作时产生的高频噪声,由于双面PCB板电源采用电源总线的方式,受到电路板面积的限制,一般存在较大的直流电阻,所以为了提高系统的稳定性,通常采用多层板,一般专门拿出两层,作为电源层和地层,而不在其上布信号线。

低阻抗的电源层也可以像地层一样作为高频信号的返回通路,可以有效地降低噪声。

(2)同类型信号线的分布在设计PCB时,对于处理器的输入输出信号中的数据线、地址线等相同类型的线应该成组、平行分布、并保持它们之间的长短差异不要太大,采用这种方式布线的既可以减少干扰,增加系统的稳定性,还可以简化布线,使PCB板的外观美观。

(3)时钟信号线的分布较高频的时钟信号是电路板的关键信号,频率越高的时钟其布线要求也越高,布线时应使时钟源到负载的联线尽量短,线应尽量宽,不同时钟之间,时钟与其他信号之间避免平行走线。

信号负载较多时,在一个驱动器上不要驱动其他时钟信号,保持时钟信号的质量良好。

结语该精简开发板具有最小化的功能,用户仅仅需要在Flash里预先烧写Boot监控程序,就可以进行应用程序的调试和下载,该开发板具有良好的扩展性,通过I/O扩展接口为户的硬件扩展提供了很多的便利。

用户可以在不更改Boot监控程序的前提下对该精简开发板进行硬件功能(串口、USB、可编程器件等)的扩充。