脉冲边沿检测器

- 格式:doc

- 大小:161.00 KB

- 文档页数:6

的电路结构与动作特点由两个与非门互耦而成的RS锁存器【图4.2.2(a)】是各种触发器的基本单元电路,它有两个低电平有效的数据输入端(S--:置位输入;R--:复位输入)和一对互补的数据输出端(Q和Q--)。

Q=1,Q--=0时,锁存器处于置位状态;Q=0,Q--=1时,锁存器处于复位状态。

S--和 R--有四种组合,如果S--无效,R--无效,锁存器的状态将与初态相同;如果S--有效,R--无效,锁存器的状态将为Q=1,Q--=0;如果S--无效,R--有效,锁存器的状态将为Q=0,Q--=1;如果S--有效,R--有效,锁存器的状态将是不确定的。

如何理解最后一种输入组合呢?图4.2.2 用与非门组成的基本RS触发器(a)电路结构RS锁存器可以(并且只可以)存储一个二进制位,要么存储1,要么存储0。

如果我们想存储1,就在 S--端加上一个负脉冲。

所谓的负脉冲,就是一个由高电平跳变到低电平,然后再由低电平跳变到高电平的信号。

当 S--由高电平跳变到低电平时,S--=0,R--=1,Q=1,Q--=0,锁存器的状态为1;当 S--由低电平跳变到高电平时,S--=1,R--=1,锁存器的状态保持不变,仍为1。

换句话说,负脉冲到来时,锁存器的状态为1;负脉冲消失后,锁存器维持这个一状态。

同理,如果我们想存储0,我们就在 R--端加上一个负脉冲。

那么,同时在 S--端和 R--端加上负脉冲是什么意思呢?难道既要存储1,又要存储0?显然,这种要求在逻辑上是矛盾的,也是无法实现的。

我们不可能提出这种无理要求。

那么,这种输入组合又是怎么出现的呢?哇!一定是干扰(或噪声)在作怪!干扰的存在,可能会使锁存器误动作。

假如我们要存储“1”,我们就在S--端加上一个负脉冲P1当P1到来时,S--=0,R--=1,Q=1,Q--=0。

如果P1结束前,在 R--端出现一个干扰脉冲P2,那么我们有S--=0,R--=0,Q=1, Q--=1,问题就发生了。

异步信号同步器设计(2)时间:2011-09-19 14:59 作者:赵信来源:网站投稿三、异步电路中同步的三种方法如果使用GALS设计电路,那么就需要将异步信号进行同步处理,那么同步处理最大的问题就是如何消除亚稳态,本章将主要介绍四种同步方法。

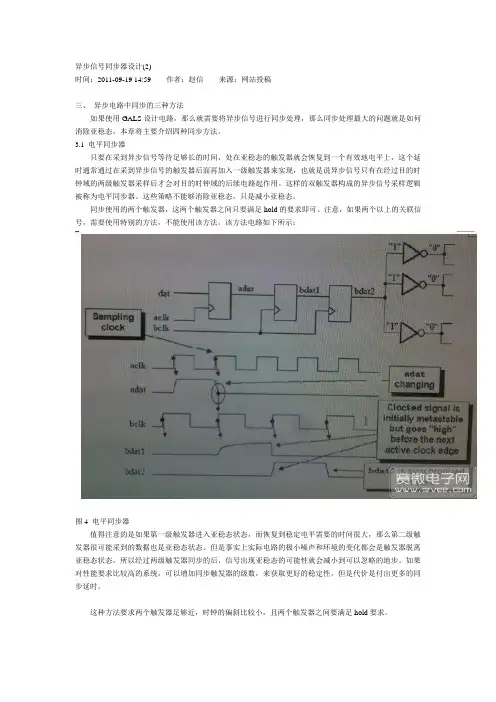

3.1 电平同步器只要在采到异步信号等待足够长的时间,处在亚稳态的触发器就会恢复到一个有效地电平上,这个延时通常通过在采到异步信号的触发器后面再加入一级触发器来实现,也就是说异步信号只有在经过目的时钟域的两级触发器采样后才会对目的时钟域的后续电路起作用。

这样的双触发器构成的异步信号采样逻辑被称为电平同步器。

这些策略不能够消除亚稳态,只是减小亚稳态。

同步使用的两个触发器,这两个触发器之间只要满足hold的要求即可。

注意,如果两个以上的关联信号,需要使用特别的方法,不能使用该方法。

该方法电路如下所示:图4 电平同步器值得注意的是如果第一级触发器进入亚稳态状态,而恢复到稳定电平需要的时间很大,那么第二级触发器很可能采到的数据也是亚稳态状态。

但是事实上实际电路的极小噪声和环境的变化都会是触发器脱离亚稳态状态,所以经过两级触发器同步的后,信号出现亚稳态的可能性就会减小到可以忽略的地步。

如果对性能要求比较高的系统,可以增加同步触发器的级数,来获取更好的稳定性,但是代价是付出更多的同步延时。

这种方法要求两个触发器足够近,时钟的偏斜比较小,且两个触发器之间要满足hold要求。

3.2 脉冲同步器脉冲同步器如下图所示:图5 脉冲同步器波形如下:图6 脉冲同步器波形这种方法的功能是将一个时钟域的单时钟周期信号转换为另一个时钟域的单周期信号,这种方法的局限是两个脉冲之间必须有最小的时间间隔,如果两个脉冲离的太近,那么在同步时钟域的两个脉冲就可能相邻,导致在同步时钟域的信号可能大于一个时钟时钟周期。

如果两个脉冲信号非常近,那么同步器将检测不到任何一个脉冲,一般要求两个脉冲的时间间隔大于两个接受时钟周期。

㊀2020年㊀第12期仪表技术与传感器Instrument㊀Technique㊀and㊀Sensor2020㊀No.12㊀基金项目:国家科技重大专项(2017ZX02101006-003)收稿日期:2019-12-10纳米光刻调焦调平传感器光电探测系统设计龚士彬1,2,3,谢冬冬1,3,武志鹏1,3,宗明成1,2,3(1.中国科学院微电子研究所,北京㊀100029;2.中国科学院大学,北京㊀100049;3.中国科学院微电子研究所微电子器件与集成技术重点实验室,北京㊀100029)㊀㊀摘要:针对光刻机调焦调平传感器的高实时性数据采集的设计需求,设计了一种多通道同步采集的光电探测系统㊂该系统使用FPGA作为数据处理和逻辑控制核心,实现了21个通道测量数据的实时采集和高速传输,与硅片台位置同步以保证测量数据与被测位置间的同步性,利用高速差分串行传输和PCIe协议完成数据的高速传输,并由上位机软件保存数据㊂实验结果证明该系统测量精度好于4nm,并可稳定采集调焦调平传感器的测量结果㊂关键词:光刻机;调焦调平;探测系统;同步性;实时数据采集;多通道中图分类号:TP274㊀㊀㊀文献标识码:A㊀㊀㊀文章编号:1002-1841(2020)12-0006-04DesignofPhotoelectricDetectingSystemforFocusingandLevelingSensorinNanoscaleLithographyGONGShi⁃bin1,2,3,XIEDong⁃dong1,3,WUZhi⁃peng1,3,ZONGMing⁃cheng1,2,3(1.InstituteofMicroelectronics,ChineseAcademyofSciences,Beijing100029,China;2.UniversityofChineseAcademyofSciences,Beijing100049,China;3.KeyLaboratoryofMicroelectronicsDevices&IntegratedTechnology,InstituteofMicroelectronics,ChineseAcademyofSciences,Beijing100029,China)Abstract:Fortherequirementofhighreal⁃timedataacquisitionoffocusingandlevelingsensorsinthelithographysystem,amultichannelsynchronousphotoelectricdetectingsystemwasdesigned.ThephotoelectricdetectingsystemwasbasedonFPGAasthecoreofdataprocessingandlogiccontroltorealizethe21real⁃timedataacquisitionchannelsandhigh⁃speeddatatransmis⁃sion.Thesystemsynchronizedwiththewaferstagetoensurethesynchronizationbetweenthemeasurementdataandthemeasuredposition.High⁃speeddifferentialserialtransmissionandPCIewereusedtorealizethehigh⁃speeddatatransmissionwhensavingdatatouppercomputersoftware.Experimentsshowthatthemeasurementaccuracyisbetterthan4nm,andthesystemcanstablycollectthemeasurementresultsofthefocusingandlevelingsensor.Keywords:lithographymachine;focusingandleveling;detectingsystem;synchronization;real⁃timedataacquisition;multichannel0㊀引言光刻机是集成电路生产制造过程中的关键设备之一㊂提高光刻机曝光分辨率通常有两种方式 缩短光源波长λ和增大数值孔径NA,但同时会造成镜头的焦深范围变小[1]㊂在20/14nm节点,关键光刻层的焦深已经只有60nm左右,曝光时的对焦精度必须控制在10nm以下[2]㊂为保证不离焦,光刻机在测量位置测量晶圆表面形貌,在曝光位置调整其曝光时的姿态[3]㊂光刻机利用调焦调平传感器测量晶圆高度,主流厂商都采用了基于光学三角法的测量技术[4]㊂ASML公司的调焦调平传感器采用了归一化分时差分测量方法,将一组差分形式的测量光斑由光弹调制器分时成像在光电探测器上[5-7]㊂计算机根据测量结果计算出晶圆高度,绘制出晶圆表面的形貌图㊂国内研究机构和SMEE公司的光刻机均采用VME控制系统控制调焦调平传感器实现硅片形貌的测量和对焦控制㊂上述的调焦调平实现方法存在2个导致同步性差的因素:在分时差分测量方法中,前后两次所采数据实际对应晶圆上的不同位置,从而产生时延误差;操作系统的任务调度存在延时,造成测量的晶圆形貌与实际的晶圆形貌存在偏移㊂针对分时差分测量的缺点,本文提出一种基于空间分光的调焦调平传感器同步光电探测系统㊂本探测系统采用多通道同步采集方法进行光电转换,解决㊀㊀㊀㊀㊀第12期龚士彬等:纳米光刻调焦调平传感器光电探测系统设计7㊀㊀分时采集造成的时延误差;并针对软件延时造成的形貌偏差问题,在探测系统上引入硅片台位置同步机制,即使用硬件电路保存硅片台位置㊂1㊀调焦调平实现原理调焦调平传感器利用光学三角法和空间分光技术测量晶圆表面各个曝光区域内的高度,硅片台根据该高度数据调整晶圆的位置和姿态,以保证曝光区域位于焦深范围内㊂光学三角法的测量原理如图1所示,其中A㊁B分别为投影光栅和探测光栅,h1㊁h2对应同一反射面在不同时刻的表面位置㊂在给定入射角α时,若反射面向下移动距离h,反射光的位置对应移动Δx㊂根据式(1)所示的几何关系可算得反射面的相对位置㊂h=Δx2sinα(1)空间分光的过程如图2所示,投影光栅的条纹由双远心成像系统成像在晶圆表面,晶圆表面反射后再次经过双远心成像系统成像在探测光栅㊂探测光栅图1㊀光学三角法高度测量原理图的前面板依次粘贴着偏振片和分光晶体,于是投影光栅像由偏振片起偏,分光晶体将起偏的投影光栅像分离为在垂直方向上相差半个条纹周期的o光和e光,如图2(b)所示㊂随后经探测光栅调制形成图2(d)所示条纹㊂根据光学三角法原理,晶圆表面高度的变化会造成投影光栅像在垂直于光栅条纹的方向上移动,从而改变调制后o光和e光通过探测光栅的比例㊂光栅像进入光电探测器前,利用渥拉斯顿棱镜将o光与e光在空间上完全分开,探测器即可同时采集o光与e光条纹的光强值㊂㊀(a)投影光栅像㊀㊀㊀㊀㊀(b)半周期分光㊀㊀㊀㊀㊀(c)经过探测光栅㊀㊀㊀㊀(d)探测光栅像㊀(e)空间分光图2㊀空间分光示意图空间分光后的o光㊁e光光强为Io=(N-|Δx|P)c4{P2[1+2sinc2(12)]+4Pπsinc(12)sin(2πPΔx)}(2)Ie=(N-|Δx|P)c4{P2[1+2sinc2(12)]-4Pπsinc(12)sin(2πPΔx)}(3)式中:P为光栅周期,μm;N为光栅条数;c为组件(偏振片+分光晶体)的透过率;Δx为晶圆表面高度的位移量,μm[8]㊂根据上述公式绘制晶圆表面高度与光强的关系曲线(图3),图(3)中Io为o光光强的归一化值,Ie为e光光强的归一化值㊂0μm位置处o光与e光光强曲线相交,且为所有交点中的最大值,即在零位时o光㊁e光光强有最大的相等值㊂图3㊀光强与晶圆表面高度关系仿真晶圆表面高度值的计算公式为h=G(Ie-Be)-(Io-Bo)(Ie-Be)+(Io-Bo)(4)式中:Be与Bo为探测器的背景噪声;G为比例系数㊂G同光栅周期P㊁测量光入射角α的关系为㊀㊀㊀㊀㊀8㊀InstrumentTechniqueandSensorDec.2020㊀G=P/42sinα(5)基于上述空间分光测量原理以及调焦调平传感器的精度需求,设计了一种高精度㊁高实时性㊁多通道同步采集的光电探测系统㊂2㊀光电探测系统设计2.1㊀探测系统总体设计光电探测系统由光电二极管阵列㊁数据采集板㊁PCIe板和上位机软件组成,图4为总体框图㊂光电二极管阵列由紧凑排列的21个高灵敏度探测区域组成,可将600 1000nm波长的光强值转换为电流信号,包括9对o光㊁e光探测区和3个粗对准探测区㊂数据采集板根据上位机和硅片台的指令,同步采集光电二极管产生的模拟信号,经16bitADC模数转换后以数字信号的形式发送至位于上位机主板上的PCIe板㊂数据通过高速串行链路向PCIe板发送时,利用SERDES芯片以10bit串并转换的方式,将高两位分别作为 测量数据有效 和 温度数据有效 控制信号,每个时钟发送1个字节的数据,保证每次采样完成后,将包括温度数据在内的44个字节数据以MSB方式有序传输㊂PCIe板从高速串行链路上恢复来自数据采集板的数据至片上RAM,再通过PCIe协议发送至上位机,上位机上的光电探测系统测试程序可对数据进行保存㊂图4㊀总体关系图为了克服造成探测系统精度下降的两个因素:o光与e光之间存在采样延迟㊁硅片台实际位置与采样位置偏离,文中采用了 多通道同步采集 和 硅片台同步触发 这两项针对性设计㊂2.2㊀多通道同步采集设计传统的探测系统采集光强信号时采用分时采集的方式,每组o光与e光由同一个ADC在间隔1μs的2个时刻先后采样㊂例如,在1xnm光刻机内,为实现250/h的产率,要求扫描速度为800mm/s[9]㊂依照该扫描速度,两次采样的实际位置相差800nm㊂根据式(4)计算可知,对于时刻0位置的高度测量结果,由分时采集方式造成的偏差值约为时刻0与时刻1两个位置之间高度差值Δh的一半,即时刻0位置的测量值为真实值h与偏差量Δh/2的和,这种偏差将在nm尺度下影响测量的精确性㊂本设计则采用同步采集方式,在收到采样脉冲后,探测系统同步采集21路光强信号,克服了上述分时电路造成的测量结果偏差㊂2.3㊀硅片台同步触发设计本设计针对硅片台位置与实际采样位置存在的偏差,在探测系统上引入了硅片台同步信号㊂相比于使用软件读取硅片台位置,由探测系统的硬件电路接收硅片台的位置信号可减少软件处理信息所带来的延时问题,且硬件电路的延时较稳定㊂控制硅片台常用的操作系统是VxWorks嵌入式系统,操作系统内任务切换时间最高接近2μs[10]㊂本设计使用触发器电路处理硅片台同步信号的执行时间可缩小到百ns以内㊂具体实现方法是为硅片台的运动路径建立坐标,并对硅片台的控制电路进行编程:当运动至预定的测量位置时发出同步信号,光电探测系统处理这个同步信号时使用一个触发器提取出其上升沿,根据该上升沿触发数据采集和硅片台位置更新,硅片台位置更新由计数器实现㊂光电探测系统的实物如图5所示,数据采集板和PCIe板之间的互连线内集成了高速串行传输链路㊁12V/20V供电㊁RS485传输线㊂数据采集板的三段式柔性连接有利于位置固定和节省空间㊂图5㊀光电探测系统实物图3㊀实验验证3.1㊀背景噪声测试探测系统背景噪声数据如图6(a)所示,总计18路探测光路数据和3路捕获光数据,图中选取了噪声最为明显的o7光路㊂对连续的500次采样数据进行㊀㊀㊀㊀㊀第12期龚士彬等:纳米光刻调焦调平传感器光电探测系统设计9㊀㊀分析后得到该噪声数据的3σ值为0.25mV,该结果很好地满足了调焦调平实验平台对光电探测系统所规定的1mV指标要求㊂根据该数据进行精度分析㊂Io+Bo㊁Ie+Be两项与探测系统的输出的电压值之间为线性关系,因此直接将o7光路数据及其对应的e7光路数据带入式(4)中得到图6(b)的高度曲线,可知探测系统在最糟糕情况下的高度数据3σ为3.72nm,探测系统的噪声对精度的影响在nm量级㊂(a)原始电压值(b)高度计算值图6㊀探测系统背景噪声3.2㊀硅片台同步触发测试利用Vivado集成逻辑分析仪(ILA)在线抓取硅片台同步脉冲信号SYNC_SIG㊁硅片台同步脉冲边沿检测信号SYNC_POS㊁硅片台位置计数器POSITION㊁采集信号DATA_E0 DATA_E8和DATA_O0 DATA_O8㊂如图7所示,游标T所在时刻,光电探测系统接收到SYNC_SIG输入脉冲,SYNC_POS寄存器提取出输入脉冲的上升沿作为采集的启动信号和硅片台位置更新的信号,等待ADC芯片完成模数转换后更新测量数据㊂从硅片台位置脉冲到达光电探测系统开始至硅片台位置更新,这个过程的延迟为60 80ns,延迟主要产生在异步信号的处理过程㊂图7中采样结果的产生时刻也表明o光与e光为多通道同步采样㊂3.3㊀调焦调平在线测试在调焦调平实验平台上对探测系统进行测试,测试结果如图8所示,放置晶圆的位移台在Z方向上从相对调焦调平实验平台零位的下方75μm处向上移动至零位的上方75μm处,复现了图3的仿真曲线㊂测试结果中的偏置是由于光学背景噪声和机械装配误差造成的,但因为测量信号的形式是差分光强,所以共模干扰不会对计算结果产生影响㊂图7㊀硅片台同步触发信号时序图图8㊀探测系统测量结果4㊀结束语本文基于FPGA设计了一种用于光刻调焦调平传感器的光电探测系统,实现了实时采集光刻调焦调平传感器测量数据㊂根据空间分光原理对21路模拟数据同步采集,解决了分时采集所产生的时延误差;引入硅片台同步信号,提高了测量值与测量位置之间对应的精度;并针对探测系统背景噪声和(下转第15页)㊀㊀㊀㊀㊀第12期师琪等:基于光纤光栅传感器的智能螺栓开发及应用15㊀㊀Mechanical,andAerospaceSystems.InternationalSocietyforOpticsandPhotonics,2005,5765:364-376.[24]㊀AMERINIF,BARBIERIE,MEOM,etal.Detectingloose⁃ning/tighteningofclampedstructuresusingnonlinearvibra⁃tiontechniques[J].Smartmaterialsandstructures,2010,19(8):085013.[25]㊀RENL,FENGT,HOM,etal.Asmart shearsensing boltbasedonFBGsensors[J].Measurement,2018,122:240-246.[26]㊀LIHN,LIDS,SONGGB.Recentapplicationsoffiberopticsensorstohealthmonitoringincivilengineering[J].Engineeringstructures,2004,26(11):1647-1657.[27]㊀RAOYJ.Recentprogressinapplicationsofin⁃fibreBragggratingsensors[J].OpticsandlasersinEngineering,1999,31(4):297-324.[28]㊀PEIHF,TENGJ,YINJH,etal.Areviewofpreviousstudiesontheapplicationsofopticalfibersensorsingeotechnicalhealthmonitoring[J].Measurement,2014,58:207-214.[29]㊀LAUKT.StructuralhealthmonitoringforsmartcompositesusingembeddedFBGsensortechnology[J].Materialsscienceandtechnology,2014,30(13):1642-1654.[30]㊀ROVERIN,CARCATERRAA,SESTIERIA.Real⁃timemo⁃nitoringofrailwayinfrastructuresusingfibreBragggratingsensors[J].MechanicalSystemsandSignalProcessing,2015,60:14-28.[31]㊀黄永阔.基于光纤光栅的高温法兰螺栓紧固力测量技术研究[D].上海:华东理工大学,2017.[32]㊀王永洪,张明义,张春巍,等.夹持式封装低温敏FBG应变传感器的设计[J].传感技术学报,2018,31(3):347-349.[33]㊀任亮,李宏男,胡志强,等.一种增敏型光纤光栅应变传感器的开发及应用[J].光电子.激光,2008(11):1437-1441.[34]㊀任亮,姜涛,李东升,等.微型FBG应变传感器在大坝模型试验中的应用[J].振动.测试与诊断,2013,33(2):277-283;341.[35]㊀贾子光,任亮,李宏男,等.应用光纤光栅传感器监测复合材料固化过程[J].中国激光,2010,37(5):1298-1303.[36]㊀RENL,CHENJ,LIHN,etal.DesignandapplicationofafiberBragggratingstrainsensorwithenhancedsensitivityinthesmall⁃scaledammodel[J].SmartMaterialsandStructures,2009,18(3):035015.[37]㊀徐望国,罗青,杨智,等.衡阳市湘江盾构隧道管片结构受力分析[J].矿业工程研究,2018,33(3):58-63.[38]㊀林荣安,刘伯莹.富水淤泥质软土地层盾构隧道管片受力特征研究[J].中国公路学报,2018,31(9):112-118.[39]㊀姜燕,杨光华,陈富强,等.湛江湾高水头跨海盾构隧道管片结构典型断面受力计算与监测反馈分析[J].岩土力学,2018,39(1):275-286.[40]㊀林伟波,杨小平,严振瑞,等.湛江湾跨海盾构隧道管片变形与受力分析[J].隧道建设,2016,36(3):288-294.[41]㊀陈晓坚.跨海地铁盾构隧道管片结构受力分析[J].南昌航空大学学报(自然科学版),2014,28(4):67-71.作者简介:师琪(1996 ),硕士研究生,主要研究方向为光纤光栅传感器的应用㊂E⁃mail:2712022922@qq.com任亮(1979 ),副教授,主要从事结构健康监测的关键技术研究,光纤传感器的开发及应用㊂E⁃mail:renliang@dlut.edu.cn(上接第9页)平台数据采集做了测试㊂结果表明:该系统可以在满足精度要求的条件下稳定地将调焦调平传感器所产生的光强信号采集至上位机,测量精度高于4nm(3σ),满足调焦调平传感器光电探测系统的设计要求㊂参考文献:[1]㊀姚汉明,胡松,邢廷文.光学投影曝光微纳加工方法[M].北京:北京工业大学出版社,2006:61-62.[2]㊀韦亚一.超大规模集成电路先进光刻理论与应用[M].北京:科学出版社,2016:117-119.[3]㊀BOONMANM,VANDEVINC,TEMPELAARSS,etal.Theperformanceadvantagesofadualstagesystem[C].SPIE,2004,5377:742-757.[4]㊀曾爱军,王向朝,徐德衍.投影光刻机调焦调平传感技术的研究进展[J].激光与光电子学进展,2004,41(7):24-30.[5]㊀MODDERMANTM,NIJMEIJERGJ,JASPERJCM.Off⁃axislevelinginlithographicprojectionapparatus:7206058B2[P].2007-04-17.[6]㊀DENBOEFAJ,BENSCHOPJPH,BRINKHOFR,etal.Levelsensor,lithographicapparatus,andsubstratesurfacepositioningmethod:US2013/0077079A1[P].2013-03-28.[7]㊀VANDERWERFJE.Opticalfocusandlevelsensorforwafersteppers[J].JVacSciTechnolB,1992,10(2):735-740.[8]㊀孙裕文,李世光,宗明成.基于空间分光的纳米级调焦调平测量技术[J].光学学报,2016,36(5):105-112.[9]㊀BORNEBROEKF.ExtendingArFiimmersionscannercapabilityinsupportof1xnmproductionnodes[C/OL].SPIEAdvancedlithography.(2014-03-05).http://staticwww.asml.com/doclib/misc/asml_20140306_Extending_ArFi_immersion_scanner_ca⁃pability_in_support_of_1xnm_production_nodes.pdf.[10]㊀毕延帅.面向双工件台的VxWorks实时嵌入式系统设计与优化[D].哈尔滨:哈尔滨工业大学,2013.作者简介:龚士彬(1994 ),硕士研究生,主要从事光刻技术与电控方面的研究㊂E⁃mail:gongshibin@ime.ac.cn通讯作者:宗明成(1963 ),研究员,博士,主要从事光刻技术㊁精密测控技术㊁精密计量等方面的研究㊂E⁃mail:zongmingcheng@ime.ac.cn。

stm32外部中断实验报告_STM32实例外部中断实验上⼀篇⽂章我们介绍了 STM32F10x 的中断,这次我们就来学习下外部中断。

本⽂中要实现的功能与按键实验⼀样,即通过按键控制LED,只不过这⾥采⽤外部中断⽅式进⾏控制。

学习时可以参考《STM32F10x 中⽂参考⼿册》-9 中断和事件章节。

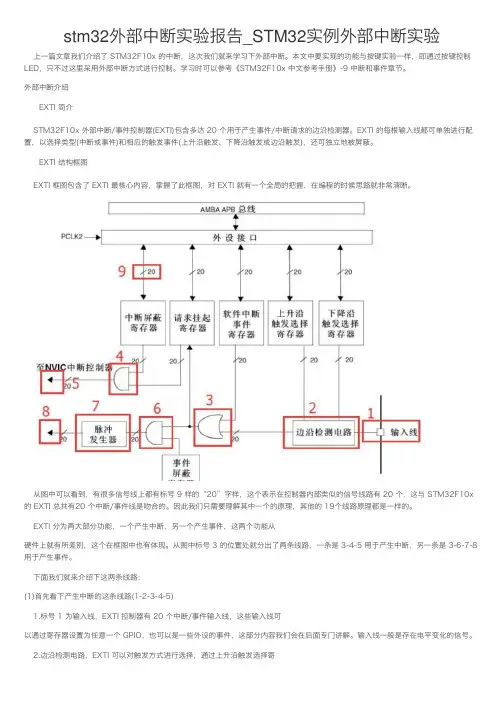

外部中断介绍EXTI 简介STM32F10x 外部中断/事件控制器(EXTI)包含多达 20 个⽤于产⽣事件/中断请求的边沿检测器。

EXTI 的每根输⼊线都可单独进⾏配置,以选择类型(中断或事件)和相应的触发事件(上升沿触发、下降沿触发或边沿触发),还可独⽴地被屏蔽。

EXTI 结构框图EXTI 框图包含了 EXTI 最核⼼内容,掌握了此框图,对 EXTI 就有⼀个全局的把握,在编程的时候思路就⾮常清晰。

从图中可以看到,有很多信号线上都有标号 9 样的“20”字样,这个表⽰在控制器内部类似的信号线路有 20 个,这与 STM32F10x 的 EXTI 总共有20 个中断/事件线是吻合的。

因此我们只需要理解其中⼀个的原理,其他的 19个线路原理都是⼀样的。

EXTI 分为两⼤部分功能,⼀个产⽣中断,另⼀个产⽣事件,这两个功能从硬件上就有所差别,这个在框图中也有体现。

从图中标号 3 的位置处就分出了两条线路,⼀条是 3-4-5 ⽤于产⽣中断,另⼀条是 3-6-7-8⽤于产⽣事件。

下⾯我们就来介绍下这两条线路:(1)⾸先看下产⽣中断的这条线路(1-2-3-4-5)1.标号 1 为输⼊线,EXTI 控制器有 20 个中断/事件输⼊线,这些输⼊线可以通过寄存器设置为任意⼀个 GPIO,也可以是⼀些外设的事件,这部分内容我们会在后⾯专门讲解。

输⼊线⼀般是存在电平变化的信号。

2.边沿检测电路,EXTI 可以对触发⽅式进⾏选择,通过上升沿触发选择寄存器和下降沿触发选择寄存器对应位的设置来控制信号触发。

边沿检测电路以输⼊线作为信号输⼊端,如果检测到有边沿跳变就输出有效信号 1 给红⾊框 3 电路,否则输出⽆效信号 0。

IC/OC选择寄存器(TIOS) 【IOSx=0 输入捕捉(1C)通道】【IOSx=1 输出比较OC通道】输出比较通道7屏蔽寄存器(OC7M)【当某通道为输出比较(OC)时,若OC7Mx=1,对应的引脚就是输出状态】输出比较通道7数据寄存器(OC7D)【若OC7Mx=1,则内部逻辑将OC7Dx送到PORTT对应引脚】定时器核心寄存器(TCNT)【递增计数器,按字(双字节同时)访问】计时器系统控制寄存器1(TSCR1)TEN:定时器使能位【0:主计时器、包括计数器均被禁止】。

【1:定时器使能,正常工作。

】TSWAI:等待模式下计时器关闭控制位【0:在中断等待模式下允许MCU继续运行。

】【1:当MCU进入中断等待模式时,禁止计时器。

】TSFR:在冻结模式下计时器和计数器停止位。

【0:在冻结模式下允许计时器和计数器继续运行。

】【1:在冻结模式下禁止计时器和计数器,用于仿真调试。

】TFFCA:定时器标志快速清除选择位。

【0:定时器标志普通清除方式。

】计时器溢出绑定寄存器1(TTOV)【0:输出比较的管脚发生溢出时绑定功能不发生作用。

】【1:输出比较的管脚发生溢出时绑定功能使能。

】控制寄存器(TCTLl-TCTL4)TCTL1 寄存器偏移量:$0008TCTL2 寄存器偏移量:$0009TCTL3 寄存器偏移量:$000ATCTL4 寄存器偏移量:$000B计时器中断使能寄存器(TIE)TIEx=0,状态寄存器TFLG1的相应标志位就不能引发硬件中断。

TIEx=1,可引起中断。

计时器系统控制寄存器2(TSCR2)TOI:计时器溢出中断使能。

【0:中断被禁止】【1:当TOF标志被置位时发出硬件中断请求】TCRE:时钟计数器复位使能。

【0:计数器复位禁止】【1:通道7成功输出比较后计数器将被复位】PR2,PR1,PR0:计数器预分频选择【分频因子=2n】主定时器中断标志寄存器(TFLG1、TFLG2)TFLG1 CxF:IC/OC通道中断请求标志。

实验一集成电路的逻辑功能测试一、实验目的1、掌握Multisim软件的使用方法。

2、掌握集成逻辑门的逻辑功能。

3、掌握集成与非门的测试方法。

二、实验原理TTL集成电路的输入端和输出端均为三极管结构,所以称作三极管、三极管逻辑电路(Transistor -Transistor Logic )简称TTL电路。

54 系列的TTL电路和74 系列的TTL电路具有完全相同的电路结构和电气性能参数。

所不同的是54 系列比74 系列的工作温度范围更宽,电源允许的范围也更大。

74 系列的工作环境温度规定为0—700C,电源电压工作范围为5V±5%V,而54 系列工作环境温度规定为-55—±1250C,电源电压工作范围为5V±10%V。

54H 与74H,54S 与74S 以及54LS 与74LS 系列的区别也仅在于工作环境温度与电源电压工作范围不同,就像54 系列和74 系列的区别那样。

在不同系列的TTL 器件中,只要器件型号的后几位数码一样,则它们的逻辑功能、外形尺寸、引脚排列就完全相同。

TTL 集成电路由于工作速度高、输出幅度较大、种类多、不易损坏而使用较广,特别对我们进行实验论证,选用TTL 电路比较合适。

因此,本实训教材大多采用74LS(或74)系列TTL 集成电路,它的电源电压工作范围为5V±5%V,逻辑高电平为“1”时≥2.4V,低电平为“0”时≤0.4V。

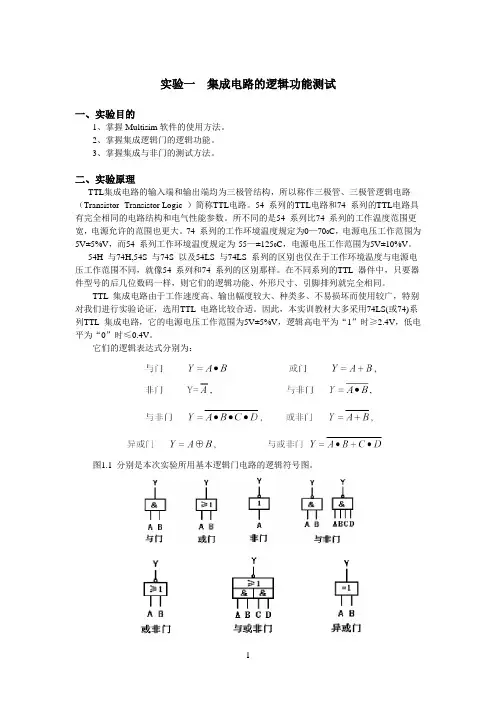

它们的逻辑表达式分别为:图1.1 分别是本次实验所用基本逻辑门电路的逻辑符号图。

图1.1 TTL 基本逻辑门电路与门的逻辑功能为“有0 则0,全1 则1”;或门的逻辑功能为“有1则1,全0 则0”;非门的逻辑功能为输出与输入相反;与非门的逻辑功能为“有0 则1,全1 则0”;或非门的逻辑功能为“有1 则0,全0 则1”;异或门的逻辑功能为“不同则1,相同则0”。

三、实验设备1、硬件:计算机2、软件:Multisim四、实验内容及实验步骤1、基本集成门逻辑电路测试 (1)测试与门逻辑功能74LS08是四个2输入端与门集成电路(见附录1),请按下图搭建电路,再检测与门的逻辑功能,结果填入下表中。

测试与光电工程学院课程设计任务书电子科学与技术系班学生课题名称:脉冲序列检测器的设计课题要求:查找相关资料,确定基于FPGA的多路脉冲序列检测器的设计方案,要求能对多路脉冲序列信号进行检测。

课题容:1、系统设计要求:脉冲序列检测器广泛应用于现代数字通信系统中。

随着通信技术的发展,对多路脉冲序列信号检测要求越来越高,本实验设计一个基于FPGA的多路脉冲序列检测器。

设计完成后,经综合和仿真验证后,在FPGA中实现。

2、工作进度安排:查找相关资料,确定脉冲序列检测器设计方案 11月15日~11月21日第12周系统各模块的详细设计 11月22日~12月28日第13周系统仿真及修正 11月29日~12月5日第14周系统测试,课程设计报告的撰写 12月6日~12月10日第15周主要参考资料:【1】潘松,黄继业 EDA技术使用教程(第三版)科学2006【2】邬波,王曙光,胡建平有限状态机VHDL设计及优化信息技术 2004(01) 【3】欲晓 EDA技术与VHDL技术电子工业 2009.4【4】鄢靖丰,晓黎,王平用Verilog-HDL设计序列检测器 2005(11)【5】唐瑜,符兴吕,罗江用VHDL语寿实现序列信号的产生和检测 2008(09) 【6】蒋昊,哲英基于多种EDA工具的FPGA设计流程[J].微计算机信息,2007 【7】束礼宝,宋克柱,王砚方.伪随机数发生器的FPGA实现与研究[J].电路与系统学报,2003.8系负责人:指导教师:柴明钢时间:2010年11月10日摘要脉冲序列检测器广泛应用于现代数字通信系统中,随着通信技术的发展,对多路脉冲序列信号检测要求越来越高。

现代通信系统的发展方向是功能更强、体积更小、速度更快、功耗更低,大规模可编程逻辑器件FPGA器件的集成度高、工作速度快、编程方便、价格较低,易于实现设备的可编程设计,这些优势正好满足通信系统的这些要求。

随着器件复杂程度的提高,电路逻辑图变得过于复杂,不便于设计。

跨越鸿沟:同步世界中的异步信号作者:Mike Stein,Paradigm Works开栏的话从本期起,《EDN CHINA电子设计技术》将正式推出“技术论坛”这个新栏目。

通过这个栏目,我们将向广大读者定期推介来自业界领先的技术供应商的充满了设计灵思的、最前沿的、高质量的技术文章;同时也会采用一系列创新的形式促进设计工程师与技术供应商的沟通与互动。

这样以来,当每个月读者拿到EDN CHINA杂志时,就好象是足不出户参加了一个技术研讨会,享受了一顿丰盛的信息“大餐”。

虽说是“新”栏目,但实际上作为它前身的“技术交流”——原先“技术纵横”中的子栏目——已经与读者相伴很多年了,这种对新技术的传播方式也已经得到了读者和技术供应商双方的认同。

“技术交流”中的文章在上的点击率排名总是名列前茅就是一个很好的例证。

现在我们将“技术交流”升格为一个独立的“技术论坛”栏目,其最主要的用意就是给这个栏目一个更广阔、更自由的发展空间。

而对于“技术交流”栏目所开创的“刊网互动”的形式,我们仍将沿用。

同时我们也将充分利用网络平台为读者提供更富于想象力的交互式的信息服务,比如读者可以将基于某篇文章的启发所迸发出的灵感火花发布到 网站上,经过我们的编辑整理则可以刊登在杂志上与更多的业内同仁分享。

新的栏目是一种新的尝试,当然其发展也需要读者热心的支持。

而实际上你会发现,你的参与意识越强,“技术论坛”所给予你的越丰富——这也正是我们的编辑理想所在。

只有最初级的逻辑电路才使用单一的时钟。

大多数与数据传输相关的应用都有与生俱来的挑战,即跨越多个时钟域的数据移动,例如磁盘控制器、CDROM/DVD 控制器、调制解调器、网卡以及网络处理器等。

当信号从一个时钟域传送到另一个时钟域时,出现在新时钟域的信号是异步信号。

在现代 IC、ASIC 以及 FPGA 设计中,许多软件程序可以帮助工程师建立几百万门的电路,但这些程序都无法解决信号同步问题。

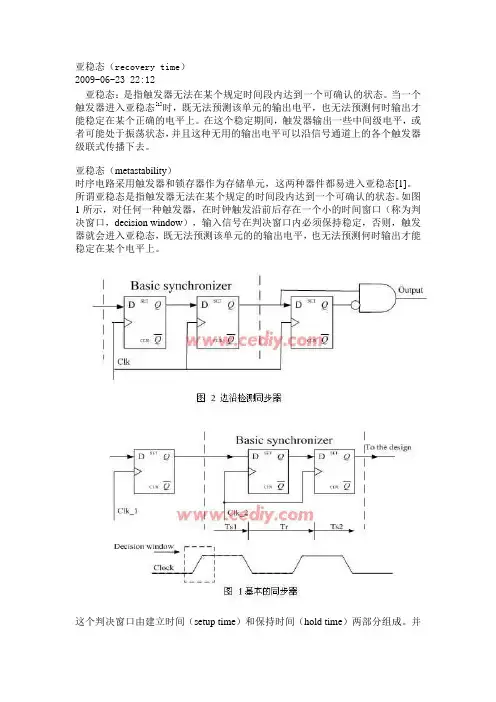

亚稳态(recovery time)2009-06-23 22:12亚稳态:是指触发器无法在某个规定时间段内达到一个可确认的状态。

当一个触发器进入亚稳态[1]时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

亚稳态(metastability)时序电路采用触发器和锁存器作为存储单元,这两种器件都易进入亚稳态[1]。

所谓亚稳态是指触发器无法在某个规定的时间段内达到一个可确认的状态。

如图1所示,对任何一种触发器,在时钟触发沿前后存在一个小的时间窗口(称为判决窗口,decision window),输入信号在判决窗口内必须保持稳定,否则,触发器就会进入亚稳态,既无法预测该单元的的输出电平,也无法预测何时输出才能稳定在某个电平上。

这个判决窗口由建立时间(setup time)和保持时间(hold time)两部分组成。

并且时间窗口也是多种因素的函数,包括触发器设计、实现技术、运行环境以及无缓冲输出的负载等。

输入信号陡峭的边沿可以将此窗口减至最小,随着时钟频率的升高,会出现更多有问题的时间窗口,而随着数据频率的提升,这种窗口的命中概率会增加,即进入亚稳态的概率会增加。

亚稳态不能从根本上消除,但可以通过采取一定的措施使其对电路造成的影响降低。

[2]通常我们用故障间隔平均时间(MTBF,mean time between failures)来衡量亚稳态的影响。

MTBF越大则说明亚稳态对电路产生地影响越小,反之亦然。

如当MTBF等于几十年或者上百年时,我们就认为它对电路的影响基本上可以忽略。

实验结果表明:对于输入为异步信号的电路,其MTBF与从亚稳态状态下恢复的时间长度(如图1所示的)有着指数的关系[3]。

2 同步器(synchronizer)在实际中,我们常用的是采用两级触发器串联的同步器(如图1)[4]。

脉冲探测器原理

脉冲探测器是一种用于测量电流或电压脉冲信号的设备。

它的工作原理基于以下几个步骤:

1. 输入信号:脉冲探测器通过一个输入端口接收待测信号。

2. 增益放大:接收到的信号会先被放大,以增加其幅度,以便后续的处理。

3. 峰值检测:脉冲探测器使用峰值检测电路来提取信号的最大振幅值。

常见的峰值检测方法包括包络检测和整流电路。

4. 脉宽测量:脉冲探测器还可以测量信号的脉宽。

脉宽测量可以通过计时器或者基于时间延迟的方法实现。

5. 输出显示:脉冲探测器可以将处理后的信号通过显示设备显示出来,以便用户进行观察和分析。

脉冲探测器广泛应用于各种领域,如通信、雷达、医学、生物学等。

它可以帮助我们测量脉冲信号的幅度、频率和脉宽,为相关领域的研究和应用提供重要的数据支持。

BLDC开发笔记3.霍尔接⼝与触发换相希望看过的各位对错误之处可以帮忙指正。

长期更新。

霍尔接⼝初始化使⽤⾼级控制定时器(TIM1或TIM8)产⽣PWM信号驱动马达时,可以⽤另⼀个通⽤TIMx(TIM2、TIM3、 TIM4或TIM5)定时器作为“接⼝定时器”来连接霍尔传感器。

这⾥选⽤定时器3。

stm32的通⽤定时器内部集成了针对霍尔/编码器信号处理的电路。

如下图:⼯作过程1. TIMx_CH1、TIMx_CH2和TIMx_CH3三个引脚接受到的霍尔信号,经过输⼊异或(XOR)功能,传到输⼊通道TI12. 信号从TI1的经过输⼊滤波器(配置滤波长度)和边沿检测器(输⼊触发有效极性,这⾥配置为双极性有效,即上升沿和下降沿都能触发)后产⽣脉冲信号TI1F_ED,经过选择器后作为TRC输⼊,再将TRC作为输⼊捕获通道IC1的输⼊信号。

IC1PS就是计数器的捕获触发信号(脉冲),决定什么时候将计数器的值传进输⼊捕获寄存器。

整个过程就是映射过程。

3. 配置时基,内部时钟分频后作为计数器时钟,将从模式控制器配置为复位模式,每当3个输⼊之⼀变化时,计数器从新从0开始计数,计数到下⼀个变化开始为⽌,这个计数器值CNT就反映了两个霍尔状态之间的时间间隔,通过这个值我们可以计算出电机的转速信息。

注意,TI1F_ED是⼀个脉冲,根据这点之后触发也是脉冲触发。

如下图,当异或后信号发⽣跳变,都会产⽣⼀个脉冲 TI1F_ED。

GPIO初始化先在头⽂件进⾏宏定义#define HALL_TIMx TIM3#define HALL_TIM_APBxClock_FUN RCC_APB1PeriphClockCmd#define HALL_TIM_CLK RCC_APB1Periph_TIM3#define HALL_TIM_PERIOD 0xFFFF //ARR,计数周期,配置为最⼤65535#define HALL_TIM_PRESCALER (72-1) //预分频系数为72#define HALL_TIM_Channel_x TIM_Channel_1 //通道1#define HALL_TIM_GPIO_REMAP GPIO_FullRemap_TIM3 //引脚重映射#define HALL_TIM_GPIO_CLK RCC_APB2Periph_GPIOC#define HALL_TIM_CH1_PIN GPIO_Pin_6#define HALL_TIM_CH1_GPIO GPIOC#define HALL_TIM_CH2_PIN GPIO_Pin_7#define HALL_TIM_CH2_GPIO GPIOC#define HALL_TIM_CH3_PIN GPIO_Pin_8#define HALL_TIM_CH3_GPIO GPIOC#define HALL_TIM_IRQn TIM3_IRQn#define HALL_TIM_IRQHANDLER TIM3_IRQHandler需要注意的是,时基编程中,要将TIMx_ARR置为其最⼤值(计数器必须通过TI1的变化清零)。

河北理工大学轻工学院信息科学技术部

课程设计说明书

设计题目脉冲边沿检测器

班级

姓名

学号

指导教师

年月日

时间地点电工电子实验中心

课程设计内容

一、课程设计题目

脉冲边沿检测器。

二、课程设计要求

1开关A为复位键。

2开关B为单脉冲输入端,可先输入负脉冲,也可先输入正脉冲。

3由红灯来表示正脉冲,绿灯表示负脉冲,且复位前指示灯一直亮。

4复位后,可重新检测。

三、课程设计目的

1通过实验了解掌握脉冲边沿检测电路的工作原理以及设计方法。

2熟悉TTL集成JK触发器74LS73和集成或非门74LS02的使用方法。

四、课程设计任务分析

根据课程设计要求,检测输入脉冲为正脉冲或负脉冲。

脉冲指电子电路中的电平状态突变,既可以是突然升高(脉冲的上升沿),也可以是突然降低(脉冲的下降沿).即正脉冲就是脉冲的上降沿;负脉冲就是脉冲的下降沿。

由此可知课程设计任务为检测脉冲跳变情况。

并用发光二极管表示出来。

五、课程设计方案论证

1.通过任务分析,确定课程设计所需器件为

74LS73 双JK触发器

74LS02 四-2输入或非门

红、绿发光二极管

适当的电阻

2考虑到经济适用原则,设计出下列既简单又实用的设计结果。

(电路图见课程设计内容)该设计结果可以识别脉冲的第一个跳变沿究竟是上升沿还是下降沿(既确定是正脉冲或负脉冲),并能将结果显示出来。

该电路所能检测的TTL脉冲信号的最小宽度可达50ns,由于电路中只用了两片集成电路,在校验和调试数字电路时,可以很方便地装在一个探头里。

该电路选用单刀双掷开关来代替单脉冲发生器,使电路更加

简单,容易操作。

所以确定该课程设计为最优结果。

六、单元电路设计与元器件选择

1、单脉冲产生电路

用74LS00四2输入与非门组成的RS触发器制作一个单脉冲产生电路,用于产生测试脉冲。

电路图如下

74LS00管脚图

单脉冲产生电路

2、74LS73双JK触发器引脚图如下

3、4LS02四2输入或非门引脚图如下

七、总体电路设计及原理

电路原理图下图所示。

电路主要由两个JK触发器和由或非门组成的基本RS触发器组成。

两个从触发器受相位相反的时钟脉冲控制,而且J、K与Q相连接,Q为0时,J=K=0,输出保持原状态;Q为1时,J=K=1,在时钟脉冲下降沿到来时,触发器的输出状态翻转。

从而控制基本RS触发器,使两只LED中有一只发光,表示时钟脉冲的方向是上升沿(或下降沿)。

具体的过程如下:

先按下复位开关A,使JK触发器的两个输出端Q=1,或非门两个输出端皆为低电平,即U1A=0, U1B=0,两只LED截止。

松开开关A后,若没有时钟脉冲到来,则电路保持原状态。

若第一次跳变是上升沿时, U1B不触发,

U1A=0,LED

1暗;而U1B的输出翻转,

2

Q=0,使G2输出高电平,即 U1B=1,LED2亮。

不管下一次输入

脉冲如何转换,因U1B的J、K均为0,输出不会翻转,

2

Q= 0,LED2继续亮。

因U1B点为高电平,所以无

论

1

Q是什么状态,U1A点都为低电平,LED1不亮。

若输入的第一次跳变是下降沿,则过程相反,LED1亮,

LED

2

暗。

图中LED1为绿灯,LED2为红灯

八、参考文献

[1] 康华光.电力技术基础数字部分(第四版) 华中理工大学电子学教研室编.高等教育出版社.

[2] 任绍发.脉冲与数字电路实验及其应用. 重庆大学出版社

[3] 龚之春电子基础课实验系列教材-脉冲与数字电路实验浙江大学出版社.

[4] 姚福安编著。

电子电路设计与实践,山东科学技术出版社

[5] 粱宗善。

电子技术基础课程设计,华中理工大学出版社

[6] Multisim使用手册

实习收获

九、学习收获

通过这次脉冲边沿检测器的课程设计,让我知道设计电路的一些程序,也让我初步了解了关于脉冲边沿检测器的一般原理与设计理念,加深了对各种芯片逻辑功能的了解,更重要的是掌握了许多实际操作技能。

这次课程设计历时半个月,所以我们进行了充分的前期准备。

包括上网找资料和区图书馆借阅有关书籍,结合课上所学知识,先对脉冲边沿检测器的设计有个总体的把握,再画出了它的总体设计框图。

接下来就是对组成脉冲边沿检测器的各个功能模块的设计了。

通过用multisin软件对我们设计的电路进行仿真,不仅肯定了我们课程设计方向的正确性,也在仿真过程中,学会了如何使用multisim软件的方法,这又是我本次课程设计的一大收获

通过这次课程设计,让我对各种电路都有了大概的了解,所以说,坐而言不如立而行,对于这些电路还是应该自己动手设计操作才会有深刻理解和达到学习的目的。

学生:

(手写签名)

年月日

成绩评定

优秀良好中等及格不及格

指导教师:2009年6月20日。