脉冲边沿检测电路原理

- 格式:ppt

- 大小:274.00 KB

- 文档页数:2

一种高速低抖动四相位时钟电路的设计崔伟;张铁良;杨松【摘要】超高速A/D转换器对精准的时钟电路提出严格要求,时钟抖动是影响其精度的重要因素.文章在分析时钟抖动对A/D转换器的影响后,介绍了一种适用于GHz的低抖动四相位时钟电路.电路采用时钟恢复电路、四相位分布网络和相位校正电路,得到占空比稳定、相位误差小的四相位时钟.采用0.18μm CMOS工艺实现,电路仿真表明,四相位输出时钟抖动102 fs,占空比调整范围30%~70%,功耗**********.【期刊名称】《电子元件与材料》【年(卷),期】2019(038)001【总页数】6页(P67-71,77)【关键词】高速时钟;时钟抖动;多相位;时钟恢复;模数转换器;CMOS【作者】崔伟;张铁良;杨松【作者单位】北京微电子技术研究所, 北京 100076;北京微电子技术研究所, 北京100076;北京微电子技术研究所, 北京 100076【正文语种】中文【中图分类】TN432A/D转换器 (Analog to Digital Converter,ADC)是模拟系统与数字系统接口的关键部件,广泛应用于工业、民用、雷达等领域。

转换器的发展使采样速率不断提升,在超高速A/D转换器中,广泛采用多通道时间交织技术来提高整体采样率,其必须严格按照时间序列进行信号采样和数模转换,因而对时钟电路提出严格要求。

随着工艺技术的提升,时钟的上升、下降时间在整个时钟周期中所占的比例不断增大,占空比失调问题越发严重[1]。

此外,时钟抖动直接影响A/D转换器的信噪比(Signal Noise Ratio,SNR)等参数指标[2]。

目前,有多种方法可以实现低抖动高速时钟电路,包括基于延迟锁相环技术的时钟电路[3-4],基于连续时间积分器的时钟电路[5]和基于脉宽控制环路的时钟电路[6-7],它们各有特点,适用于不同类型的A/D转换器。

本文提出的高速低抖动四相位时钟电路,应用于时间交织ADC,为ADC采样保持电路提供精准的高速四相位时钟。

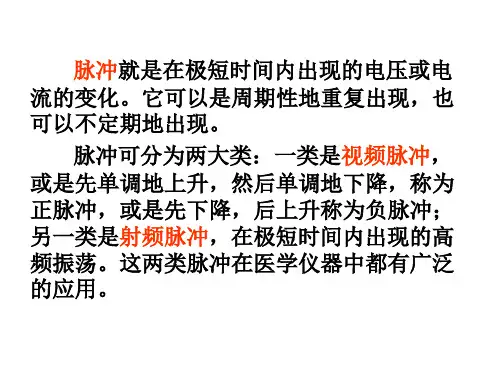

脉冲电路脉冲电路的基本知识在数字电路中分别以高电平和低电平表示1状态和0状态。

此时电信号的波形是非正弦波。

通常,就把一切既非直流又非正弦交流的电压或电流统称为脉冲。

图Z1601表示出几种常见的脉冲波形,它们既可有规律地重复出现,也可以偶尔出现一次。

脉冲波形多种多样,表征它们特性的参数也不尽相同,这里,仅以图Z1602所示的矩形脉冲为例,介绍脉冲波形的主要参数。

(1)脉冲幅度Vm--脉冲电压或电流的最大值。

脉冲电压幅度的单位为V、mV,脉冲电流幅度的单位为A、mA。

(2)脉冲前沿上升时间tr--脉冲前沿从0.1Vm上升到0.9Vm所需要的时间。

单位为ms、μs、ns。

(3)脉冲后沿下降时间tf--脉冲后沿从0.9Vm下降到0.1Vm所需要的时间。

单位为:ms、μs、ns。

(4)脉冲宽度tk--从脉冲前沿上升到0.5Vm处开始,到脉冲下降到0.5Vm处为止的一段时间。

单位为:s、ms、μs或ns。

(5)脉冲周期T--周期性重复的脉冲序列中,两相邻脉冲重复出现的间隔时间。

单位为:s、ms、μs。

(6)脉冲重复频率--脉冲周期的倒数,即f =1/T,表示单位时间内脉冲重复出现的次数,单位为Hz、kHz、MHz。

(7)占空比tk/T--脉冲宽度与脉冲周期的比值,亦称占空系数。

对电路来说,有个阻抗匹配问题,只有当阻抗匹配时,输出效果才最好,否则,有可能导致负载力不足,导致一旦外加电路,就会把电压拉下了,建议后面加一级运放增大负载能力交流电源的零交越脉冲电路设计时间:2012-04-25 14:58:04 来源:作者:本设计中的电路可生成一个交流电源的零交越脉冲,并提供电气绝缘。

输出脉冲的下降沿出现在零交越点前约200μs。

使用这个电路可以安全地停止一个可控硅栅极的触发,使之有时间正常地关断。

只有当主电压约为0V时,电路才产生短脉冲,因此在230V、50Hz输入下只耗电200mW。

电路为电容C1充电,直至达到22V齐纳二极管D3的上限(图1与参考文献1)。

脉冲电位器原理

脉冲电位器是一种用于测量和监测电压或电位差的电气设备。

它由一个可移动的导电材料(如金属滑动触点)和一个固定的电阻组成。

脉冲电位器的工作原理基于滑动触点与电阻之间的接触。

当滑动触点移动时,它会接触到不同长度的电阻,导致电阻的长度发生变化。

由于电阻与电阻长度成正比,电位差(或电压)也会相应地改变。

在脉冲电位器中,固定电阻一般是一个连续的线性电阻,它以一定的电阻值单位进行刻度。

当滑动触点连接到电源电压时,通电的电路便形成了。

当滑动触点处在电阻的起点时,电位差为零。

然而,当滑动触点沿着电阻线移动时,由于电阻长度的改变,电位差也相应地改变。

这样,滑动触点的位置就可以显示电压或电位差的大小。

滑动触点一般通过旋钮或手柄进行移动。

在大多数脉冲电位器中,旋钮或手柄上会标有刻度,可以用来读取或调节所测量或监测的电压值。

脉冲电位器主要适用于需要频繁调节电位差或电压的应用,如实验室实验、电路调试和电子设备校准等。

它们提供了一种简单而有效的方法来测量和监测电压,并在电路设计和维护中起到重要的作用。

脉冲金属探测器原理图

脉冲金属探测器是一种常用于地下金属探测的设备,它利用电磁感应原理来探测和定位地下金属物体。

脉冲金属探测器的原理图如下所示:

首先,脉冲金属探测器由探测线圈、控制单元、电源和显示器等部分组成。

探测线圈是脉冲金属探测器的核心部件,它通过发射电磁脉冲信号并接收反射信号来实现金属探测。

控制单元负责处理接收到的信号,并将结果显示在显示器上。

电源为脉冲金属探测器提供工作所需的电能。

在实际工作中,脉冲金属探测器通过控制单元发出高频脉冲信号,这些脉冲信号通过探测线圈传播到地下。

当脉冲信号遇到地下金属物体时,会引起金属物体内部电流的产生。

根据法拉第电磁感应定律,金属物体内部电流产生的磁场会与探测线圈产生的磁场发生相互作用,从而产生一个反射信号。

探测线圈接收到这个反射信号后,控制单元会对信号进行处理,并将结果显示在显示器上,从而实现对地下金属物体的探测和定位。

脉冲金属探测器的原理图中还包括了一些重要的参数,如探测

深度、灵敏度和地面平衡等。

探测深度是指脉冲金属探测器能够探测到地下金属物体的最大深度,这取决于探测线圈的尺寸和工作频率等因素。

灵敏度则是指脉冲金属探测器对地下金属物体的探测能力,灵敏度越高,探测到的金属物体越小。

地面平衡是指脉冲金属探测器在不同地质环境下的性能调节,通过地面平衡可以减小地质矿物对探测结果的干扰。

总的来说,脉冲金属探测器通过发射和接收电磁脉冲信号来实现对地下金属物体的探测和定位。

它在考古、矿产勘探、安全检查等领域有着广泛的应用,是一种非常重要的地下探测设备。

以上就是关于脉冲金属探测器原理图的相关介绍,希望对您有所帮助。

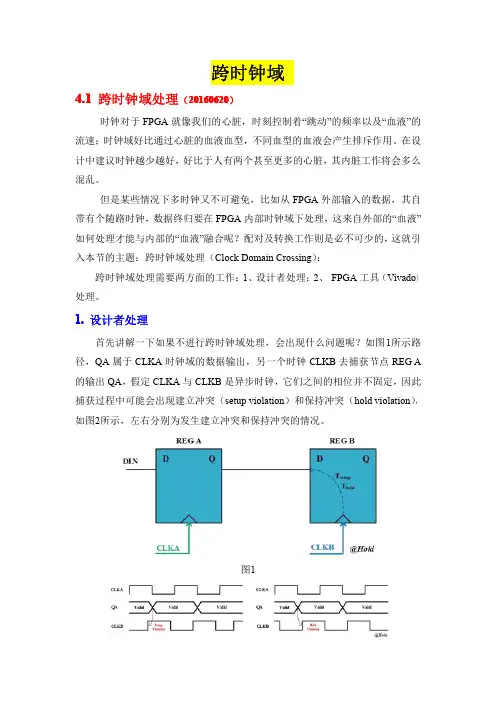

跨时钟域4.1跨时钟域处理(20160620)时钟对于FPGA就像我们的心脏,时刻控制着“跳动”的频率以及“血液”的流速;时钟域好比通过心脏的血液血型,不同血型的血液会产生排斥作用。

在设计中建议时钟越少越好,好比于人有两个甚至更多的心脏,其内脏工作将会多么混乱。

但是某些情况下多时钟又不可避免,比如从FPGA外部输入的数据,其自带有个随路时钟,数据终归要在FPGA内部时钟域下处理,这来自外部的“血液”如何处理才能与内部的“血液”融合呢?配对及转换工作则是必不可少的,这就引入本节的主题:跨时钟域处理(Clock Domain Crossing):跨时钟域处理需要两方面的工作:1、设计者处理;2、FPGA工具(Vivado)处理。

1.设计者处理首先讲解一下如果不进行跨时钟域处理,会出现什么问题呢?如图1所示路径,QA属于CLKA时钟域的数据输出,另一个时钟CLKB去捕获节点REG A 的输出QA,假定CLKA与CLKB是异步时钟,它们之间的相位并不固定,因此捕获过程中可能会出现建立冲突(setup violation)和保持冲突(hold violation),如图2所示,左右分别为发生建立冲突和保持冲突的情况。

图1图2当冲突出现时(我感觉整个人都不好了),会发生什么事情呢?在发生建立冲突或者保持冲突,捕获节点(REG B)会处于一个不定的状态,正常的状态是高电平或者低电平,而此时的状态停留在高电平和低电平的中间,无效的电平X,称这个状态为亚稳态。

如图3所示,捕获节点输出保持在亚稳态,可能在整个时钟周期内都保持在亚稳态,由于不正确的状态,其后连接的逻辑在功能实现上就会出现问题,比如一个判断信号上升沿的逻辑,通常判断D==HIGH&&D_PREV==LOW(D为信号当前电平状态,D_PREV为信号上个时钟的电平状态)是否成立,而发生亚稳态时则D_PREV==X,这个上升沿将会错过。

因此,加入跨时钟域处理设计是必须的。

脉冲电流法检测原理嘿,朋友们!今天咱来聊聊脉冲电流法检测原理。

这玩意儿啊,就像是我们生活中的一个小侦探!你看啊,脉冲电流就好像是一个特别机灵的小使者,在各种设备和线路里跑来跑去。

它呀,专门去探寻那些可能存在的问题和隐患。

比如说,我们家里的电线就像一条条小路,电流呢,就是在这些小路上奔跑的小汽车。

要是哪条路有点不对劲,脉冲电流这个小侦探就能敏锐地察觉到。

它是怎么做到的呢?就好像小侦探有一双特别厉害的眼睛,能看到别人看不到的细节。

当脉冲电流通过的时候,如果遇到了电阻、电容或者电感这些家伙,它就能根据它们的反应来判断是不是一切正常。

这不就跟我们找东西一样嘛!我们在一堆东西里找一个特别的东西,会仔细观察每一个细节,脉冲电流也是这样啊。

它在那些线路里穿梭,不放过任何一个蛛丝马迹。

你想想,要是没有这个小侦探,我们怎么能知道设备是不是健康呢?说不定哪天就突然出问题啦!那可就麻烦咯!脉冲电流法检测原理真的太重要啦!它就像是我们的保护神,默默地守护着那些复杂的电路和设备。

它能让我们提前发现问题,及时解决,避免出现大的故障。

这就好比我们身体不舒服了,去医院做检查,早点发现问题才能早点治疗呀!而且啊,这个小侦探还很智能呢!它可以根据不同的情况调整自己的检测方式,就像一个经验丰富的老侦探,什么场面都能应对自如。

咱再打个比方,脉冲电流检测就像是一场精彩的魔术表演。

魔术师能变出各种神奇的东西,而脉冲电流能检测出各种隐藏的问题。

它真的是太神奇啦!我们可不能小瞧了它。

在很多重要的领域,比如电力系统、电子设备制造等等,都离不开它呢!所以啊,朋友们,一定要好好认识这个神奇的脉冲电流法检测原理啊!它可是我们生活中的好帮手,能为我们解决很多潜在的大麻烦呢!相信我,一旦你了解了它,你就会感叹:哇塞,原来还有这么厉害的东西存在啊!。

计算机原理与应用实验实验名称:外部中断实验学院:信息与通信工程学院班级:2017211113姓名:***学号:**********同组成员姓名:李凝同组成员学号:**********一、实验目的1. 掌握NVIC 中断优先级配置。

2. 学会外部中断配置。

二、实验原理及内容(一)实验原理电路结构如图3.1 所示1. NVIC 中断优先级NVIC 是嵌套向量中断控制器,控制着整个芯片中断相关的功能,它跟内核紧密耦合,是内核里面的一个外设。

但是各个芯片厂商在设计芯片的时候会对Cortex-M4 内核里面的NVIC 进行裁剪,把不需要的部分去掉,所以说STM32 的NVIC 是Cortex-M4 的NVIC 的一个子集。

CM4 内核可以支持256个中断,包括16个内核中断和240个外部中断,256 级的可编程中断设置。

对于STM32F4 没有用到CM4 内核的所有东西,只是用到了一部分,对于STM32F40 和41 系列共有92个中断,其中有10个内核中断和82个可屏蔽中断,常用的为82个可屏蔽中断。

ISER[8]—中断使能寄存器组,用来使能中断,每一位控制一个中断,由于上面已经说明了控制82 个可屏蔽的中断,因此利用ISER[0~2]这三个32 位寄存器就够了。

一下的几个寄存器同理。

ICER[8]—中断除能寄存器组,用来消除中断。

ISPR[8]—中断挂起控制寄存器组,用来挂起中断。

ICPR[8]—中断解挂控制寄存器组,用来解除挂起。

IABR[8]—中断激活标志寄存器组,对应位如果为1 则表示中断正在被执行。

IP[240]—中断优先级控制寄存器组,它是用来设置中断优先级的。

我们只用到了IP[0]~IP[81],每个寄存器只用到了高4 位,这4 位又用来设置抢占优先级和响应优先级(有关抢占优先级和响应优先级后面会介绍到),而对于抢占优先级和响应优先级各占多少位则由AIRCR 寄存器控制,相关设置如表 3.1 所示。

脉冲探测器原理

脉冲探测器是一种用于测量电流或电压脉冲信号的设备。

它的工作原理基于以下几个步骤:

1. 输入信号:脉冲探测器通过一个输入端口接收待测信号。

2. 增益放大:接收到的信号会先被放大,以增加其幅度,以便后续的处理。

3. 峰值检测:脉冲探测器使用峰值检测电路来提取信号的最大振幅值。

常见的峰值检测方法包括包络检测和整流电路。

4. 脉宽测量:脉冲探测器还可以测量信号的脉宽。

脉宽测量可以通过计时器或者基于时间延迟的方法实现。

5. 输出显示:脉冲探测器可以将处理后的信号通过显示设备显示出来,以便用户进行观察和分析。

脉冲探测器广泛应用于各种领域,如通信、雷达、医学、生物学等。

它可以帮助我们测量脉冲信号的幅度、频率和脉宽,为相关领域的研究和应用提供重要的数据支持。

跨时钟域4.1跨时钟域处理(20160620)时钟对于FPGA就像我们的心脏,时刻控制着“跳动”的频率以及“血液”的流速;时钟域好比通过心脏的血液血型,不同血型的血液会产生排斥作用。

在设计中建议时钟越少越好,好比于人有两个甚至更多的心脏,其内脏工作将会多么混乱。

但是某些情况下多时钟又不可避免,比如从FPGA外部输入的数据,其自带有个随路时钟,数据终归要在FPGA内部时钟域下处理,这来自外部的“血液”如何处理才能与内部的“血液”融合呢?配对及转换工作则是必不可少的,这就引入本节的主题:跨时钟域处理(Clock Domain Crossing):跨时钟域处理需要两方面的工作:1、设计者处理;2、FPGA工具(Vivado)处理。

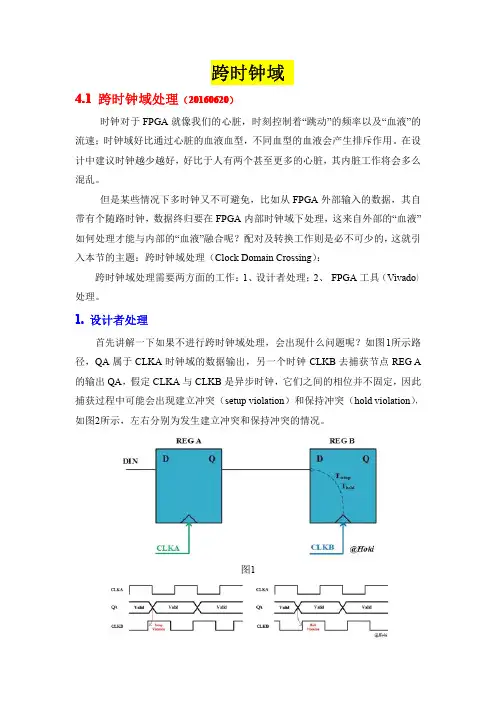

1.设计者处理首先讲解一下如果不进行跨时钟域处理,会出现什么问题呢?如图1所示路径,QA属于CLKA时钟域的数据输出,另一个时钟CLKB去捕获节点REG A 的输出QA,假定CLKA与CLKB是异步时钟,它们之间的相位并不固定,因此捕获过程中可能会出现建立冲突(setup violation)和保持冲突(hold violation),如图2所示,左右分别为发生建立冲突和保持冲突的情况。

图1图2当冲突出现时(我感觉整个人都不好了),会发生什么事情呢?在发生建立冲突或者保持冲突,捕获节点(REG B)会处于一个不定的状态,正常的状态是高电平或者低电平,而此时的状态停留在高电平和低电平的中间,无效的电平X,称这个状态为亚稳态。

如图3所示,捕获节点输出保持在亚稳态,可能在整个时钟周期内都保持在亚稳态,由于不正确的状态,其后连接的逻辑在功能实现上就会出现问题,比如一个判断信号上升沿的逻辑,通常判断D==HIGH&&D_PREV==LOW(D为信号当前电平状态,D_PREV为信号上个时钟的电平状态)是否成立,而发生亚稳态时则D_PREV==X,这个上升沿将会错过。

因此,加入跨时钟域处理设计是必须的。

脉冲测试原理

脉冲测试是一种用于检测电子设备、电路或系统性能的测试方法。

它通过施加脉冲信号来刺激被测对象,并通过分析被测对象的响应来评估其状态。

脉冲测试的原理基于以下几个关键步骤:

1. 产生脉冲信号:脉冲测试通常使用高频率,短脉冲宽度的信号来刺激被测对象。

这些脉冲信号可以通过脉冲发生器或信号发生器产生。

2. 施加脉冲信号:产生的脉冲信号通过连接器或探针连接到被测对象的输入端或特定节点上。

3. 监测响应信号:当脉冲信号施加到被测对象上时,被测对象会产生响应信号。

这些响应信号可以是电压、电流或其他形式的信号。

4. 捕获与记录信号:响应信号通过连接器或探针传递到测试仪器中,如示波器或数据采集系统。

这些仪器捕获和记录响应信号的特征。

5. 分析和评估:捕获的响应信号可以通过分析和对比与已知良好设备或电路的标准响应信号进行比较,以评估被测对象的性能、传输特性或其他关键参数。

脉冲测试的好处在于它能够提供非常快速的测量结果,并且对

于检测故障、评估设备性能以及调试电路等方面非常有用。

它广泛应用于电子设备制造、电路设计与测试、通信和计算机系统等领域。