eda程序

- 格式:doc

- 大小:110.00 KB

- 文档页数:20

eda加法器程序eda加法器完整程序:library ieee;use ieee. std_logic_1164. All;entity adderisport(a,b: in std_logic_vector(3 downto 0);cin: in std_logic;s: out std_logic vector(3 downto 0);cout: out std_logic);end adder; architecture adder of adderis signalc:std_logic_vector(4 downto 0);begin c(O)<=cin; G1:for i in 0 to 3 generates(i)<=a(i) xor b(i) xor c(i);c(i+1)<=(a(i) and b(i) yor(a(i) and c(i)) or(b(i) and c(i));end generate; cout<-c(4); end adder;library ieee; use ieee. std_logic_1164. All;USE IEEE. STD LOGIC UNSIGNED. ALL;entity adder8 is port(m,n: in std_logic vector(7 downto 0);p: out std_logic vector(8 downto 0));end adder8; architecture addB of adder8is component adder is port(a,b: in std logic vector(3 downto 0);cin: in std_logic;s: out std_logic_vector(3 downto 0); cout: outstd_logic);end component;signalx1,x2,y1,y2:std_logic;begin;x1<=0';u5:adder port map(a->m(3 downto 0),b->n(3 downto 0),cin->x1,a->p(3downto 0),cout->y1);x2<=y1;u6:adder port map(a=>m(7 downto 4),b=>n(7 downto 4),cin=>x2,s=>p(7downto 4),cout=>y2);P(8)<=y2;end add8;lbrary ieee;use leee, std_1og1c_1164, all;use leee, std_logic_unsigned, all;use leee. atd_1ogic_arith. All;entity convert ia port(m,n: in std_loglc_vector(7 downto 0);p: in atd logic_vector(8 downto 0);ge1, ge2, ge3, ahi1, ahi2, ahi3, bail, bai2, bai3: out integer range 0 to9);end convert; architecture convert of convert i8aigna1d1,d2,d3;integer range 0 to 512;beqin dl<mconv_integer(m);d2<=conv integer(n);d3<aconv integer(p);M1: process(d1)begin ge1<-d1rem 10;shi1<-(d1rem 100)/10; bai1<-d1/100;end procesaM1;M2: procesa(d1)begin ge2<=d2rem 10; shi2<=(d2 rem 100)/10; bai2<-d2/100; end process M2;M3:process(d1)begin ge3<=d3 rem 10;shi3<=(d3 rem 100)/10; bai3<=d3/100; end process M3; end convert;。

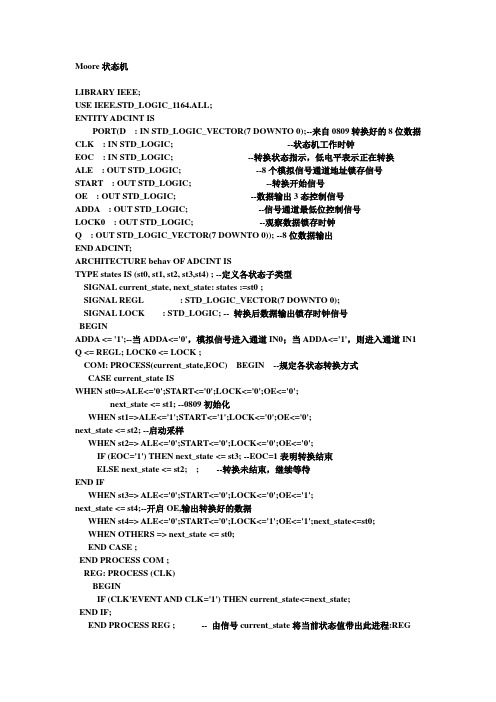

Moore状态机LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ADCINT ISPORT(D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--来自0809转换好的8位数据CLK : IN STD_LOGIC; --状态机工作时钟EOC : IN STD_LOGIC; --转换状态指示,低电平表示正在转换ALE : OUT STD_LOGIC; --8个模拟信号通道地址锁存信号START : OUT STD_LOGIC; --转换开始信号OE : OUT STD_LOGIC; --数据输出3态控制信号ADDA : OUT STD_LOGIC; --信号通道最低位控制信号LOCK0 : OUT STD_LOGIC; --观察数据锁存时钟Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --8位数据输出END ADCINT;ARCHITECTURE behav OF ADCINT ISTYPE states IS (st0, st1, st2, st3,st4) ; --定义各状态子类型SIGNAL current_state, next_state: states :=st0 ;SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL LOCK : STD_LOGIC; -- 转换后数据输出锁存时钟信号BEGINADDA <= '1';--当ADDA<='0',模拟信号进入通道IN0;当ADDA<='1',则进入通道IN1 Q <= REGL; LOCK0 <= LOCK ;COM: PROCESS(current_state,EOC) BEGIN --规定各状态转换方式CASE current_state ISWHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0';next_state <= st1; --0809初始化WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0';next_state <= st2; --启动采样WHEN st2=> ALE<='0';START<='0';LOCK<='0';OE<='0';IF (EOC='1') THEN next_state <= st3; --EOC=1表明转换结束ELSE next_state <= st2; ; --转换未结束,继续等待END IFWHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1';next_state <= st4;--开启OE,输出转换好的数据WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1';next_state<=st0;WHEN OTHERS => next_state <= st0;END CASE ;END PROCESS COM ;REG: PROCESS (CLK)BEGINIF (CLK'EVENT AND CLK='1') THEN current_state<=next_state;END IF;END PROCESS REG ; -- 由信号current_state将当前状态值带出此进程:REGLATCH1: PROCESS (LOCK) -- 此进程中,在LOCK的上升沿,将转换好的数据锁入BEGINIF LOCK='1' AND LOCK'EVENT THEN REGL <= D ;END IF;END PROCESS LATCH1 ;END behav;5.2.1 多进程状态机COM1: PROCESS(current_state,EOC) BEGINCASE current_state ISWHEN st0=> next_state <= st1;WHEN st1=> next_state <= st2;WHEN st2=> IF (EOC='1') THEN next_state <= st3;ELSE next_state <= st2; END IF ;WHEN st3=> next_state <= st4;--开启OEWHEN st4=> next_state <= st0;WHEN OTHERS => next_state <= st0;END CASE ;END PROCESS COM1 ;COM2: PROCESS(current_state) BEGINCASE current_state ISWHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0' ;WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0' ;WHEN st2=>ALE<='0';START<='0';LOCK<='0';OE<='0' ;WHEN st3=>ALE<='0';START<='0';LOCK<='0';OE<='1' ;WHEN st4=>ALE<='0';START<='0';LOCK<='1';OE<='1' ;WHEN OTHERS => ALE<='0';START<='0';LOCK<='0';END CASE ;END PROCESS COM2 ;7.1.3 CASE语句LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY alu ISPORT( a, b : IN STD_LOGIC_VECTOR (7 DOWNTO 0);opcode: IN STD_LOGIC_VECTOR (1 DOWNTO 0);result: OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END alu;ARCHITECTURE behave OF alu ISCONSTANT plus : STD_LOGIC_VECTOR (1 DOWNTO 0) := b"00";CONSTANT minus : STD_LOGIC_VECTOR (1 DOWNTO 0) := b"01";CONSTANT equal : STD_LOGIC_VECTOR (1 DOWNTO 0) := b"10";CONSTANT not_equal: STD_LOGIC_VECTOR (1 DOWNTO 0) := b"11"; BEGINPROCESS (opcode,a,b)BEGINCASE opcode ISWHEN plus => result <= a + b; -- a、b相加WHEN minus => result <= a - b; -- a、b相减WHEN equal => -- a、b相等IF (a = b) THEN result <= x"01";ELSE result <= x"00";END IF;WHEN not_equal => -- a、b不相等IF (a /= b) THEN result <= x"01";ELSE result <= x"00";END IF;END CASE;END PROCESS;END behave;4.10流水线乘法器的混合输入设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER16B ISPORT ( CIN : IN STD_LOGIC;A,B : IN STD_LOGIC_VECTOR(15 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);COUT : OUT STD_LOGIC );END ADDER16B;ARCHITECTURE behav OF ADDER16B ISSIGNAL SINT : STD_LOGIC_VECTOR(16 DOWNTO 0);SIGNAL AA,BB : STD_LOGIC_VECTOR(16 DOWNTO 0);BEGINAA<='0'&A; BB<='0'& B;SINT <= AA + BB + CIN; S <= SINT(15 DOWNTO 0); COUT <= SINT(4); END behav;5.4.2 顺序编码...SIGNAL CRURRENT_STATE,NEXT_STATE: STD_LOGIC_VECTOR(2 DOWNTO 0 ); CONSTANT ST0 : STD_LOGIC_VECTOR(2 DOWNTO 0) := "000" ;CONSTANT ST1 : STD_LOGIC_VECTOR(2 DOWNTO 0) := "001" ;CONSTANT ST2 : STD_LOGIC_VECTOR(2 DOWNTO 0) := "010" ;CONSTANT ST3 : STD_LOGIC_VECTOR(2 DOWNTO 0) := "011" ;CONSTANT ST4 : STD_LOGIC_VECTOR(2 DOWNTO 0) := "100" ;...8线-3线优先编码器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY coder ISPORT ( din : IN STD_LOGIC_VECTOR(0 TO 7);output : OUT STD_LOGIC_VECTOR(0 TO 2) );END coder;ARCHITECTURE behav OF coder ISSIGNAL SINT : STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINPROCESS (din)BEGINIF (din(7)='0') THEN output <= "000" ;ELSIF (din(6)='0') THEN output <= "100" ;ELSIF (din(5)='0') THEN output <= "010" ;ELSIF (din(4)='0') THEN output <= "110" ;ELSIF (din(3)='0') THEN output <= "001" ;ELSIF (din(2)='0') THEN output <= "101" ;ELSIF (din(1)='0') THEN output <= "011" ;ELSE output <= "111" ;END IF ;END PROCESS ;END behav;3-8译码器代码library ieee;use ieee.std_logic_1164.all;entity decoder38 isport (Q0: out std_logic_vector(7 downto 0);Q1: in std_logic_vector(2 downto 0);g1,g2,g3: in std_logic);end entity decoder38;architecture code1 of decoder38 isbeginprocess(Q1,g1,g2,g3)beginif (g1 ='1'or g2 ='1'or g3 ='1') then Q0<= "ZZZZZZZZ";elsecase Q1 iswhen "000" => Q0<= "00000001";when "001" => Q0<= "00000010";when "010" => Q0<= "00000100";when "011" => Q0<= "00001000";when "100" => Q0<= "00010000";when "101" => Q0<= "00100000";when "110" => Q0<= "01000000";when "111" => Q0<= "10000000";when others=> Q0<= "ZZZZZZZZ";end case;end if;end process;end architecture code1;3-1. 画出与下例实体描述对应的原理图符号元件:ENTITY buf3s IS -- 实体1:三态缓冲器PORT (input : IN STD_LOGIC ; -- 输入端enable : IN STD_LOGIC ; -- 使能端output : OUT STD_LOGIC ) ; -- 输出端END buf3x ;ENTITY mux21 IS --实体2:2选1多路选择器PORT (in0, in1, sel : IN STD_LOGIC;output : OUT STD_LOGIC);十进制加法计数器【例3-21】LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT (CLK,RST,EN : IN STD_LOGIC;CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); COUT : OUT STD_LOGIC );END CNT10;ARCHITECTURE behav OF CNT10 ISBEGINPROCESS(CLK, RST, EN)V ARIABLE CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF RST = '1' THEN CQI := (OTHERS =>'0') ; --计数器异步复位ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿IF EN = '1' THEN --检测是否允许计数(同步使能)IF CQI < 9 THEN CQI := CQI + 1; --允许计数, 检测是否小于9ELSE CQI := (OTHERS =>'0'); --大于9,计数值清零END IF;END IF;END IF;IF CQI = 9 THEN COUT <= '1'; --计数大于9,输出进位信号ELSE COUT <= '0';END IF;CQ <= CQI; --将计数值向端口输出END PROCESS;END behav;老师演示的程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY s_machine_srl ISPORT ( DATAIN :IN STD_LOGIC_VECTOR(3 DOWNTO 0);CLK,RST : IN STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END s_machine_srl;ARCHITECTURE behav OF s_machine_srl ISTYPE ST_TYPE IS (ST0, ST1, ST2, ST3);SIGNAL C_ST : ST_TYPE ;SIGNAL ST0_OUTPUT : STD_LOGIC_VECTOR(3 DOWNTO 0) ;SIGNAL ST1_OUTPUT : STD_LOGIC_VECTOR(3 DOWNTO 0) ;SIGNAL ST2_OUTPUT : STD_LOGIC_VECTOR(3 DOWNTO 0) ;SIGNAL ST3_OUTPUT : STD_LOGIC_VECTOR(3 DOWNTO 0) ;SIGNAL C_ST_OUTPUT : STD_LOGIC_VECTOR(3 DOWNTO 0) ;BEGINST0_OUTPUT <= DATAIN;ST1_OUTPUT <= DATAIN(2 DOWNTO 0)& DATAIN(3);ST2_OUTPUT <= DATAIN(1 DOWNTO 0)& DATAIN(3 DOWNTO 2);ST3_OUTPUT <= DATAIN(0)& DATAIN(3 DOWNTO 1);PROCESS(CLK,RST)BEGINIF RST ='1' THEN C_ST <= ST0;ELSIF CLK'EVENT AND CLK='1' THENCASE C_ST ISWHEN ST0 => C_ST <= ST1 ;WHEN ST1 => C_ST <= ST2 ;WHEN ST2 => C_ST <= ST3 ;WHEN ST3 => C_ST <= ST0 ;WHEN OTHERS => C_ST <= ST0;END CASE;End IF;End Process;PROCESS(C_ST)BEGINCASE C_ST ISWHEN ST0 => C_ST_OUTPUT <= ST0_OUTPUT ;WHEN ST1 => C_ST_OUTPUT <= ST1_OUTPUT ;WHEN ST2 => C_ST_OUTPUT <= ST2_OUTPUT ;WHEN ST3 => C_ST_OUTPUT <= ST3_OUTPUT ;WHEN OTHERS => C_ST_OUTPUT <= ST0_OUTPUT;END CASE;End Process;Q <=C_ST_OUTPUT;End behav;。

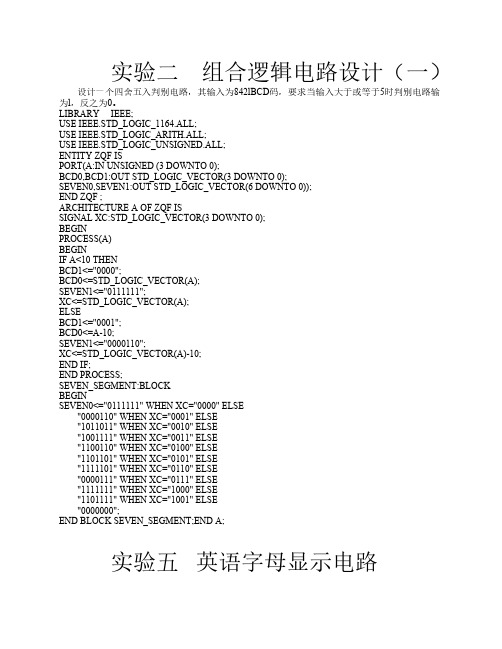

实验二组合逻辑电路设计(一)设计一个四舍五入判别电路,其输入为842lBCD码,要求当输入大于或等于5时判别电路输为l,反之为0。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ZQF ISPORT(A:IN UNSIGNED (3 DOWNTO 0);BCD0,BCD1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);SEVEN0,SEVEN1:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END ZQF ;ARCHITECTURE A OF ZQF ISSIGNAL XC:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(A)BEGINIF A<10 THENBCD1<="0000";BCD0<=STD_LOGIC_VECTOR(A);SEVEN1<="0111111";XC<=STD_LOGIC_VECTOR(A);ELSEBCD1<="0001";BCD0<=A-10;SEVEN1<="0000110";XC<=STD_LOGIC_VECTOR(A)-10;END IF;END PROCESS;SEVEN_SEGMENT:BLOCKBEGINSEVEN0<="0111111" WHEN XC="0000" ELSE"0000110" WHEN XC="0001" ELSE"1011011" WHEN XC="0010" ELSE"1001111" WHEN XC="0011" ELSE"1100110" WHEN XC="0100" ELSE"1101101" WHEN XC="0101" ELSE"1111101" WHEN XC="0110" ELSE"0000111" WHEN XC="0111" ELSE"1111111" WHEN XC="1000" ELSE"1101111" WHEN XC="1001" ELSE"0000000";END BLOCK SEVEN_SEGMENT;END A;实验五英语字母显示电路LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.STD_LOGIC_ARITH.ALL;use ieee.std_logic_unsigned.all;----------------------------------------------------entity zimum isport(clk: in std_logic;ledag:out std_logic_vector(6 downto 0));end zimum;architecture behave of zimum issignal clk1khzs: std_logic;signal charcnt: std_logic;signal cnt: integer range 0 to 7 :=0;BEGINprocess(clk)variable clknum:integer range 0 to 1999999 :=0;beginif clk'event and clk='1' thenif clknum=1999999 then clknum:=0;clk1khzs<= not clk1khzs; -----1s else clknum:=clknum+1;end if;end if;end process;process(clk1khzs)beginif clk1khzs'event and clk1khzs='1' thenif cnt=7 then cnt<=0;else cnt<=cnt+1;end if;end if;end process;process(cnt)begincase cnt iswhen 0=>ledag<="0110111"; ------Hwhen 1=>ledag<="1001111"; ------Ewhen 2=>ledag<="0001110"; ------Lwhen 3=>ledag<="0001110"; ------Lwhen 4=>ledag<="1001110"; ------Cwhen 5=>ledag<="1100111"; ------Pwhen 6=>ledag<="0001110"; ------Lwhen 7=>ledag<="1111101"; ------Dwhen others=>null;END CASE;end process;END ARCHITECTURE BEHAVE;实验九异步计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DFF_4ISPORT (CLK,KEY,RESET:IN STD_LOGIC;Q:BUFFER STD_LOGIC_VECTOR(0 TO 3));END DFF_4;ARCHITECTURE BEHAVE OF DFF_4ISCOMPONENT D_FFPORT(CLK,D,RESET:IN STD_LOGIC;Q,QN:OUT STD_LOGIC);END COMPONENT;SIGNAL KEY_FLAG:STD_LOGIC;SIGNAL CLK20HZ:STD_LOGIC;SIGNAL QN:STD_LOGIC_VECTOR(0 TO 3);SIGNAL CNT:STD_LOGIC;BEGINPROCESS(CLK)VARIABLE CLKNUM:INTEGER RANGE 0 TO 99999 :=0;BEGINIF CLK'EVENT AND CLK='1' THENIF CLKNUM=99999 THEN CLKNUM:=0;CLK20HZ<=NOT CLK20HZ;ELSE CLKNUM:=CLKNUM+1;END IF;END IF;END PROCESS;PROCESS(CLK20HZ)BEGINIF CLK20HZ'EVENT AND CLK20HZ='1' THENIF KEY='1' AND KEY_FLAG='0' THENKEY_FLAG<='1';ELSIF KEY='0' AND KEY_FLAG='1' THENKEY_FLAG<='0';END IF;END IF;END PROCESS;DFF1:D_FF PORT MAP(KEY_FLAG,QN(0),RESET,Q(0),QN(0));DFFX:FOR I IN 1 TO 3 GENERATEDFF2TO4: D_FF PORT MAP(QN(I-1),QN(I),RESET,Q(I),QN(I));END GENERATE;END BEHAVE;例化:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY D_FF ISPORT(CLK,D,RESET:IN STD_LOGIC;Q,QN:OUT STD_LOGIC);END ENTITY;ARCHITECTURE BEHAVE OF D_FF ISSIGNAL Q1:STD_LOGIC;BEGINPROCESS(CLK,RESET)BEGINIF RESET='1' THENQ1<='0';ELSIF CLK'EVENT AND CLK='1' THENQ1<=D;END IF;Q<=Q1;QN<=NOT Q1;END PROCESS;END BEHAVE;实验十九频率计1、设计一个3位十进制频率计,其测量范围为lMHz。

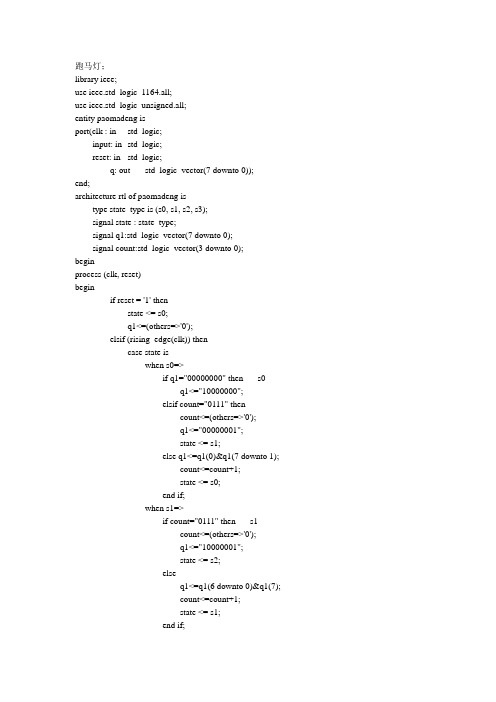

跑马灯;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity paomadeng isport(clk : in std_logic;input: in std_logic;reset: in std_logic;q: out std_logic_vector(7 downto 0)); end;architecture rtl of paomadeng istype state_type is (s0, s1, s2, s3);signal state : state_type;signal q1:std_logic_vector(7 downto 0);signal count:std_logic_vector(3 downto 0);beginprocess (clk, reset)beginif reset = '1' thenstate <= s0;q1<=(others=>'0');elsif (rising_edge(clk)) thencase state iswhen s0=>if q1="00000000" then --s0q1<="10000000";elsif count="0111" thencount<=(others=>'0');q1<="00000001";state <= s1;else q1<=q1(0)&q1(7 downto 1);count<=count+1;state <= s0;end if;when s1=>if count="0111" then --s1count<=(others=>'0');q1<="10000001";state <= s2;elseq1<=q1(6 downto 0)&q1(7);count<=count+1;state <= s1;end if;when s2=>if count="0111" then --s2count<=(others=>'0');q1<="00011000";state <= s3;elseq1(7 downto 4)<=q1(4)&q1(7 downto 5);q1(3 downto 0)<=q1(2 downto 0)&q1(3);count<=count+1;state <= s2;end if;when s3=>if count="0111" then --s1count<=(others=>'0');q1<="10000000";state <= s0;elseq1(7 downto 4)<=q1(6 downto 4)&q1(7);q1(3 downto 0)<=q1(0)&q1(3 downto 1);count<=count+1;state <= s3;end if;end case;end if;end process;q<=q1;end rtl;S0模式:从左到右逐个点亮LEDS1模式:从右到左逐个点亮LEDS2模式:从两边到中间逐个点亮LEDS3模式:从中间到两边逐个点亮LED四位全加器;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsinged.all;entity adder4 isport(a,b:in std_logic_vector(3 downto 0);ci:in std_logic;s:out std_logic_vector(3 downto 0);c:out std_logic);end;architecture two of adder4 issignal temp:std_logic_vector(4 downto 0);begintemp<=('0'&a)+b+ci;s<=temp(3 downto 0);c<=temp(4);end;四位全减器;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsinged.all;entity sub4 isport(a,b:in std_logic_vector(3 downto 0); --被减数、减数ci:in std_logic; --低位借位dout:out std_logic_vector(3 downto 0); --差值cout:out std_logic); --借位end;architecture two of sub4 issignal temp:std_logic_vector(4 downto 0);begintemp<=('0'&a)-b-ci;dout<=temp(3 downto 0);cout<=temp(4);end;【例5-11】forloop--8位奇偶校验电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY p_check ISPORT(a: IN STD_LOGIC_VECTOR(7 DOWNTO 0);y: OUT STD_LOGIC);END p_check;ARCHITECTURE behave OF p_check ISSIGNAL tmp: STD_LOGIC;BEGINPROCESS(a)BEGINtmp<='0';FOR n IN 0 TO 7 LOOP --FOR循环语句tmp<=tmp XOR a(n);END LOOP;y<=tmp;END PROCESS;END behave;【例5-12】whileloop --8位奇偶校验电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY p_check2 ISPORT(a: IN STD_LOGIC_VECTOR(7 DOWNTO 0);y: OUT STD_LOGIC);END p_check2;ARCHITECTURE behave OF p_check2 ISSIGNAL tmp: STD_LOGIC;BEGINPROCESS(a)V ARIABLE i:INTEGER:=0;BEGINtmp<='0';WHILE i<8 LOOP --WHILE循环tmp<=tmp XOR a(i);i:=i+1;END LOOP;y<=tmp;END PROCESS;END behave;例if语句,3-4选1LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4 ISPORT(a,b,c,d:IN STD_LOGIC_VECTOR (3 DOWNTO 0);s:IN STD_LOGIC_VECTOR(1 DOWNTO 0);X:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END mux4;ARCHITECTURE behave OF mux4 ISBEGINMux4:PROCESS(a,b,c,d)BEGINIF s="00" THEN --第3种IF语句,实现多选1功能X<=a;ELSIF s="01" THENX<=b;ELSIF s="10" THENX<=c;ELSEX<=d;END IF;END process mux4;END behave;IF语句12-4位等值比较器;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY eqcomp4 ISPORT(a,b:IN STD_LOGIC_VECTOR(3 DOWNTO 0);equals:OUT STD_LOGIC);END eqcomp4;ACHITECTURE behave1 OF eqcomp4 ISBEGINPROCESS(a,b)BEGINequals<='0';IF a=b THENequals<='1';END IF;END PROCESS;END behave1;ACHITECTURE behave2 OF eqcomp4 ISBEGINPROCESS(a,b)BEGINIF a=b THENequals<='1';ELSEequals<='0';END IF;END PROCESS;END behave2;半加器;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsinged.all;entity half_adder isport(a,b:in std_logic;s,c:out std_logic);end;architecture one of half_adder isbegins<=a xor b;c<=a and b;end;architecture two of half_adder issignal temp:std_logic_vector(1 downto 0);begintemp<=('0'&a)+b;s<=temp(0);c<=temp(1);end;半减器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsinged.all;entity half_sub isport(a:in std_logic; --被减数b:in std_logic; --减数dout:out std_logic; --差值cout:out std_logic);--借位end;architecture one of half_sub isbegindout<=a xor b;cout<=nota and b;end;architecture two of half_sub issignal temp:std_logic_vector(1 downto 0);begintemp<=('0'&a)-b;s<=temp(0);c<=temp(1);end;【例5-50】--单向总线缓冲器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY trl_buf8 ISPORT(din:IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入8位二进制数dout:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --输出8位二进制数en:IN STD_LOGIC); --使能端口END trl_buf8;ARCHITECTURE behave OF trl_buf8 ISBEGINPROCESS(en,din)BEGINIF(en='1')THENdout<=din;ELSEdout<="ZZZZZZZZ";END IF;END PROCESS;END behave;【例5-48】--多位加法运算LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY adder ISPORT(a,b:IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入两个8位二进制数cin:IN STD_LOGIC; --低位来的进位s:OUT STD_LOGIC_VECTOR(8 DOWNTO 0)); --输出8位结果及产生的进位END adder;ARCHITECTURE behave OF adder ISBEGINs<=('0'&a)+('0'&b)+("0000000"&cin);END behave;赋值语句;例:…SIGNAL s1,s2:STD_LOGIC;SIGNAL svec:STD_LOGIC_VECTOR(0 TO 3);…PROCESS(s1,s2)V ARIABLE v1,v2:STD_LOGIC;BEGINv1:=’1’;--立即将变量v1置位为1v2:=’1’; --立即将变量v2置位为1s1<=’1’; --信号s1被赋值为1s2<=’1’; --由于在本进程中,这里的s2不是最后一个赋值语句故不作任何赋值操作xsvec(0)<=v1;--将变量v1在上面的赋值1,赋给svec(0)svec(1)<=v2;--将变量v2在上面的赋值1,赋给svec(1)svec(2)<=s1;--将信号s1在上面的赋值1,赋给svec(2)svec(3)<=s2;--将最下面的赋予s2的值‘0’,赋给svec(3)v1:=’0’; --将变量v1置入新值0v2:=’0’; --将变量v2置入新值0s2:<=’0’; --由于这是信号s2最后一次赋值,赋值有效,此‘0’将--上面准备赋入的‘1’覆盖掉END PROCESS;全加器;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsinged.all;entity adder isport(a,b,ci:in std_logic;s,c:out std_logic);end;architecture two of adder issignal temp:std_logic_vector(1 downto 0);begintemp<=('0'&a)+b+ci;s<=temp(0);c<=temp(1);end;全减器;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsinged.all;entity sub isport(a,b,ci:in std_logic; --被减数、减数、低位借位dout,cout:out std_logic); --差值、借位end;architecture two of sub issignal temp:std_logic_vector(1 downto 0);begintemp<=('0'&a)-b-ci;dout<=temp(0);cout<=temp(1);end;【例】--三态门电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY tristate ISPORT(en,din:IN STD_LOGIC; --en为使能端口,din为输入端口dout:OUT STD_LOGIC); --输出端口END tristate;ARCHITECTURE tri OF tristate ISBEGINPROCESS(en,din)BEGINIF en='1' THENdout<=din;ELSEdout<='Z';END IF;END PROCESS;end tri;设计一个序列检测器,要求当检测到连续收到1110010后,输出为1,否则输出为0。

1、用AHDL语言编写图中的组合逻辑电路。

. 参考答案:SUBDESIGN decode1(a0,a1,b:input;out1,out2:output;)beginout1=a0&!a1out2=out1&b;end;2、门电路构成的半加器结构如下图半加器h_adder表示如下:图中SO为相加和的输出,CO为进位输出信号。

用VHDL语言对半加器进行描述。

参考答案:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY half adder ISPORT(a,b: IN STD_LOGIC;So,co:OUT STD_LOGIC);END half_adder;ARCHITECYURE hahav1 OF half_adder ISSIGNAL c,d:STD_LOGICBEGINc<=a OR b:d<=a NAND b;co<=NOT d AFTER 5ns;so<=c AND d AFTER 5ns;END behav1;3、本题为一个4位加法器的VHDL语言描述,4位加法器其输入为a0、a1、a2、a3、b0、b1、b2、b3、进位输入为cin;输出为s0、s1、s2、s3,进位输出为cout。

请完善本程序。

文件名为adder_4bits.vhdLIBRARY IEEE;USE IEEE.STD.LOGIC_1164.ALL;ENTITY adder_4bits ISPORT ( a0,a1,a2,a3 :IN STD_LOGIC;b0,b1,b2,b3,cin :IN STD_LOGIC;s0,s1,s2,s3 :OUT STD_LOGIC);END adder_4bits ;ARCHITECTURE strc OF adder_4bits ISCOMPONENT full_adderPORT(a,b,cin:IN std_LOGIC;S,co:OUT std_logic);END COMPONENT;SIGNAL U0_c,U1_c,U2_c:STD_LOGIC;1BEGINU0:full_adder PORT MAP (a0,b0,cin,s0,U0_c);U1:full_adder PORT MAP (a1,b1,U0_c,s1,U1_c);U2:full_adder PORT MAP (a2,b2,U1_c,s2,U2_c);U3:full_adder PORT MAP (a3,b3,U2_c,s3,cout);End strc;4、用VHDL语言描述不带复位/置位端的D触发器。

院系:物电学院班级:12级电信班学号:20125042090 姓名:王迎雪设计一个0.7s的计数器系统时钟CLK为12MHZ,则计数值counter为0.7*12M,即0.7s 显示一个数字。

8*8LED点阵的动态显示编写每个学号的各个数字所对应的LED点阵代码,用8位的二进制数表示点阵的8排led,低电平代表点亮;用两位十六进制数表示每排led所对应的列,同样低电平代表点亮。

点阵的行或排在系统时钟CLK的上升沿到来时更新,更新的同时此行所对应的所有的列也在更新,8行全部点亮后才能显示一个数字。

显示的两个数字之间间隔0.7s,可以用一个中间变量来控制,即此变量每0.7s更新一次,学号显示完后清零,循环。

代码:module led_arry_disp(clk_12M, rst_n, row_sel, col_sel);input clk_12M, rst_n;output[7:0] row_sel, col_sel; //the row or column of 8*8LEDreg[7:0] row_sel;reg[7:0] col_sel;reg[3:0]disp_num; //student number has 11 numbers,so disp_num displays number from 0 to 11reg[23:0] counter; //generating 0.7s counterreg[2:0] i; //the change of row_selalways @(posedge clk_12M or negedge rst_n) //generating 0.7sbeginif(!rst_n)counter <= 24'd0;else if(counter==24`d8399999) //12MHZ*0.7=8.4*10^(6)counter <= 0;elsecounter <= counter + 24'd1;endalways @(posedge clk_12M or negedge rst_n) //the time of every 0.7s displays one data of student numberbeginif(!rst_n)disp_num<=4'd0;else if(counter>=24`d8399999)disp_num<=disp_num+4'd1;else if( disp_num==4'd10)disp_num<=4'd0;elsedisp_num<=disp_num;always @(posedge clk_12M or negedge rst_n) //changing the row of 8*8LED arraybeginif(!rst_n)i <= 3'd0;elsei <= i + 3'd1;endalways @(posedge clk_12M) //displaying the code of rowbegincase(i)3'b000 :row_sel = 8'b1111_1110;3'b001 :row_sel = 8'b1111_1101;3'b010 :row_sel = 8'b1111_1011;3'b011 :row_sel = 8'b1111_0111;3'b100 :row_sel = 8'b1110_1111;3'b101 :row_sel = 8'b1101_1111;3'b110 :row_sel = 8'b1011_1111;3'b111 :row_sel = 8'b0111_1111;default: row_sel = 8'b1111_1111;endcasealways @(posedge clk_12M) begincase(disp_num)4'd0:begincase(row_sel)8'b1111_1110: col_sel = 8'hff; 8'b1111_1101: col_sel = 8'hc3; 8'b1111_1011: col_sel = 8'hbd; 8'b1111_0111: col_sel = 8'hfb; 8'b1110_1111: col_sel = 8'hf7; 8'b1101_1111: col_sel = 8'hef; 8'b1011_1111: col_sel = 8'hdf; 8'b0111_1111: col_sel = 8'h81; default: col_sel = 8'hff; endcaseend4'd1:begincase(row_sel)8'b1111_1110: col_sel = 8'hc3; 8'b1111_1101: col_sel = 8'hbd;8'b1111_1011: col_sel = 8'hbd; 8'b1111_0111: col_sel = 8'hbd; 8'b1110_1111: col_sel = 8'hbd; 8'b1101_1111: col_sel = 8'hbd; 8'b1011_1111: col_sel = 8'hbd; 8'b0111_1111: col_sel = 8'hc3; default: col_sel = 8'hff; endcaseend4'd2:begincase(row_sel)8'b1111_1110: col_sel = 8'he7; 8'b1111_1101: col_sel = 8'hc7; 8'b1111_1011: col_sel = 8'he7; 8'b1111_0111: col_sel = 8'he7; 8'b1110_1111: col_sel = 8'he7; 8'b1101_1111: col_sel = 8'he7; 8'b1011_1111: col_sel = 8'he7; 8'b0111_1111: col_sel = 8'hc3; default: col_sel = 8'hff; endcaseend4'd3:begincase(row_sel)8'b1111_1110: col_sel = 8'hff; 8'b1111_1101: col_sel = 8'hc3; 8'b1111_1011: col_sel = 8'hbd; 8'b1111_0111: col_sel = 8'hfb; 8'b1110_1111: col_sel = 8'hf7; 8'b1101_1111: col_sel = 8'hef; 8'b1011_1111: col_sel = 8'hdf; 8'b0111_1111: col_sel = 8'h81; default: col_sel = 8'hff; endcaseend4'd4:begincase(row_sel)8'b1111_1110: col_sel = 8'hdf; 8'b1111_1101: col_sel = 8'hc3; 8'b1111_1011: col_sel = 8'hdf; 8'b1111_0111: col_sel = 8'hdf; 8'b1110_1111: col_sel = 8'hc3; 8'b1101_1111: col_sel = 8'hfb; 8'b1011_1111: col_sel = 8'hfb;default: col_sel = 8'hff; endcaseend4'd5:begincase(row_sel)8'b1111_1110: col_sel = 8'hc3; 8'b1111_1101: col_sel = 8'hbd; 8'b1111_1011: col_sel = 8'hbd; 8'b1111_0111: col_sel = 8'hbd; 8'b1110_1111: col_sel = 8'hbd; 8'b1101_1111: col_sel = 8'hbd; 8'b1011_1111: col_sel = 8'hbd; 8'b0111_1111: col_sel = 8'hc3; default: col_sel = 8'hff; endcaseend4'd6:begincase(row_sel)8'b1111_1110: col_sel = 8'hff; 8'b1111_1101: col_sel = 8'h93; 8'b1111_1011: col_sel = 8'h93;8'b1110_1111: col_sel = 8'h93; 8'b1101_1111: col_sel = 8'h81; 8'b1011_1111: col_sel = 8'h81; 8'b0111_1111: col_sel = 8'hf3; default: col_sel = 8'hff; endcaseend4'd7:begincase(row_sel)8'b1111_1110: col_sel = 8'hff; 8'b1111_1101: col_sel = 8'hc3; 8'b1111_1011: col_sel = 8'hbd; 8'b1111_0111: col_sel = 8'hfb; 8'b1110_1111: col_sel = 8'hf7; 8'b1101_1111: col_sel = 8'hef; 8'b1011_1111: col_sel = 8'hdf; 8'b0111_1111: col_sel = 8'h81; default: col_sel = 8'hff; endcaseend4'd8:begincase(row_sel)8'b1111_1110: col_sel = 8'hc3; 8'b1111_1101: col_sel = 8'hbd; 8'b1111_1011: col_sel = 8'hbd; 8'b1111_0111: col_sel = 8'hbd; 8'b1110_1111: col_sel = 8'hbd; 8'b1101_1111: col_sel = 8'hbd; 8'b1011_1111: col_sel = 8'hbd; 8'b0111_1111: col_sel = 8'hc3; default: col_sel = 8'hff; endcaseend4'd9:begincase(row_sel)8'b1111_1110: col_sel = 8'hff; 8'b1111_1101: col_sel = 8'hc3; 8'b1111_1011: col_sel = 8'hdb; 8'b1111_0111: col_sel = 8'hc3; 8'b1110_1111: col_sel = 8'hfb; 8'b1101_1111: col_sel = 8'hfb; 8'b1011_1111: col_sel = 8'hc3; 8'b0111_1111: col_sel = 8'hff;default: col_sel = 8'hff; endcaseend4'd10:begincase(row_sel)8'b1111_1110: col_sel = 8'hc3; 8'b1111_1101: col_sel = 8'hbd; 8'b1111_1011: col_sel = 8'hbd; 8'b1111_0111: col_sel = 8'hbd; 8'b1110_1111: col_sel = 8'hbd; 8'b1101_1111: col_sel = 8'hbd; 8'b1011_1111: col_sel = 8'hbd; 8'b0111_1111: col_sel = 8'hc3; default: col_sel = 8'hff;endcaseendendcaseendendmodulequartus2仿真图ModelsimSE10.1a仿真3.1 Testbench源代码`timescale 1ns/1psmodule tb_led_array_disp;reg clk_12M;reg rst_n;wire [7:0] row_sel;wire [7:0] col_sel;initialbeginclk_12M<=0;rst_n<=1;#100 rst_n<=0;#200 rst_n<=1;endalways #41.667 clk_12M<=~clk_12M;led_array_disp led_array_disp_inst(clk_12M,rst_n, row_sel, col_sel); endmodule仿真步骤1.准备好功能仿真需要的文件:用Verilog语言设计的HDL源代码;测试激励代码:根据设计要求输入/输出的激励程序。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dianzz isport(clk,clrm,stop:in std_logic;----时钟/清零信号secm1,secm0:out std_logic_vector(3 downto 0);----秒高位/低位co:out std_logic);-------输出/进位信号end dianzz;architecture SEC of dianzz issignal clk1,DOUT2:std_logic;beginprocess(clk,clrm)variable cnt1,cnt0:std_logic_vector(3 downto 0);---计数V ARIABLE COUNT2 :INTEGER RANGE 0 TO 10 ;beginIF CLK'EVENT AND CLK='1'THENIF COUNT2>=0 AND COUNT2<10 THENCOUNT2:=COUNT2+1;ELSE COUNT2:=0;DOUT2<= NOT DOUT2;END IF;END IF;if clrm='1' then----当clr为1时,高低位均为0cnt1:="0000";cnt0:="0000";elsif clk'event and clk='1' thenif stop='1' thencnt0:=cnt0;cnt1:=cnt1;end if;if cnt1="1001" and cnt0="1000" then----当记数为98(实际是经过59个记时脉冲)co<='1';----进位cnt0:="1001";----低位为9elsif cnt0<"1001" then----小于9时cnt0:=cnt0+1;----计数--elsif cnt0="1001" then--clk1<=not clk1;elsecnt0:="0000";if cnt1<"1001" then----高位小于9时cnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;secm1<=cnt1;secm0<=cnt0;end process;end SEC;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity SECOND isport(clk,clr:in std_logic;----时钟/清零信号sec1,sec0:out std_logic_vector(3 downto 0);----秒高位/低位co:out std_logic);-------输出/进位信号end SECOND;architecture SEC of SECOND isbeginprocess(clk,clr)variable cnt1,cnt0:std_logic_vector(3 downto 0);---计数beginif clr='1' then----当ckr为1时,高低位均为0cnt1:="0000";cnt0:="0000";elsif clk'event and clk='1' thenif cnt1="0101" and cnt0="1000" then----当记数为58(实际是经过59个记时脉冲)co<='1';----进位cnt0:="1001";----低位为9elsif cnt0<"1001" then----小于9时cnt0:=cnt0+1;----计数elsecnt0:="0000";if cnt1<"0101" then----高位小于5时cnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;sec1<=cnt1;sec0<=cnt0;end process;end SEC;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity MINUTE isport(clk,en:in std_logic;min1,min0:out std_logic_vector(3 downto 0);co:out std_logic);end MINUTE;architecture MIN of MINUTE isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0); beginif clk'event and clk='1' thenif en='1' thenif cnt1="0101" and cnt0="1000" thenco<='1';cnt0:="1001";elsif cnt0<"1001" thencnt0:=cnt0+1;elsecnt0:="0000";if cnt1<"0101" thencnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;end if;min1<=cnt1;min0<=cnt0;end process;end MIN;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity HOUR isport(clk,en:in std_logic;----输入时钟/高电平有效的使能信号h1,h0:out std_logic_vector(3 downto 0));----时高位/低位end HOUR;architecture hour_arc of HOUR isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0);----记数beginif clk'event and clk='1' then---上升沿触发if en='1' then---同时“使能”为1if cnt1="0010" and cnt0="0011" thencnt1:="0000";----高位/低位同时为0时cnt0:="0000";elsif cnt0<"1001" then----低位小于9时,低位记数累加cnt0:=cnt0+1;elsecnt0:="0000";cnt1:=cnt1+1;-----高位记数累加end if;end if;end if;h1<=cnt1;h0<=cnt0;end process;end hour_arc;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity SELTIME isport(clk:in std_logic;------扫描时钟secm1,secm0,sec1,sec0,min1,min0,h1,h0:in std_logic_vector(3 downto 0);-----分别为秒个位/时位;分个位/daout:out std_logic_vector(3 downto 0);----------------输出sel:out std_logic_vector(2 downto 0));-----位选信号end SELTIME;architecture fun of SELTIME issignal count:std_logic_vector(2 downto 0);----计数信号beginsel<=count;process(clk)beginif(clk'event and clk='1') thenif(count>="111") thencount<="000";elsecount<=count+1;end if;end if;case count iswhen"111"=>daout<= secm0;----秒个位when"110"=>daout<= secm1;----秒十位when"101"=>daout<= sec0;----分个位when"100"=>daout<= sec1;----分十位when"011"=>daout<=min0; ----时个位when"010"=>daout<=min1;----时十位when"001"=>daout<=h0;when others =>daout<=h1;end case;end process;end fun;library ieee;use ieee.std_logic_1164.all;entity ALERT isport(m1,m0,s1,s0:in std_logic_vector(3 downto 0);------输入秒、分高/低位信号clk:in std_logic;------高频声控制q500,qlk:out std_logic);----低频声控制end ALERT;architecture sss_arc of ALERT isbeginprocess(clk)beginif clk'event and clk='1' thenif m1="0101" and m0="1001" and s1="0101" then----当秒高位为5,低位为9时且分高位为5if s0="0001" or s0="0011" or s0="0101" or s0="0111" then---当分的低位为1或3或5或7时q500<='1';----低频输出为1elseq500<='0';----否则输出为0end if;end if;if m1="0101" and m0="1001" and s1="0101" and s0="1001" then---当秒高位为5,低位为9时且分高位为5,----分低位为9时,也就是“59分59秒”的时候“报时”qlk<='1';-----高频输出为1elseqlk<='0';end if;end if;end process;end sss_arc;library ieee;use ieee.std_logic_1164.all;entity DISPLAY isport(d:in std_logic_vector(3 downto 0);----连接seltime扫描部分d信号q:out std_logic_vector(6 downto 0));----输出段选信号(电平)end DISPLA Y;architecture disp_are of DISPLAY isbeginprocess(d)begincase d iswhen"0000" =>q<="0111111";--显示0when"0001" =>q<="0000110";--显示1when"0010" =>q<="1011011";--显示2when"0011" =>q<="1001111";--显示3when"0100" =>q<="1100110";--显示4when"0101" =>q<="1101101";--显示5when"0110" =>q<="1111101";--显示6when"0111" =>q<="0100111";--显示7when"1000" =>q<="1111111";--显示8when others =>q<="1101111";--显示9end case;end process;end disp_are;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity SECON isport(clk,clr:in std_logic;sec1,sec0:out std_logic_vector(3 downto 0);co:out std_logic);end SECON;architecture SEC of SECON isbeginprocess(clk,clr)variable cnt1,cnt0:std_logic_vector(3 downto 0); beginif clr='1' thencnt1:="0000";cnt0:="0000";elsif clk'event and clk='1' thenif cnt1="0101" and cnt0="1000" thenco<='1';cnt0:="1001";elsif cnt0<"1001" thencnt0:=cnt0+1;elsecnt0:="0000";if cnt1<"0101" thencnt1:=cnt1+1;cnt1:="0000";co<='0';end if;end if;end if;sec1<=cnt1;sec0<=cnt0;end process;end SEC;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity MINUT isport(clk,en:in std_logic;min1,min0:out std_logic_vector(3 downto 0);co:out std_logic);end MINUT;architecture MIN of MINUT isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0); beginif clk'event and clk='1' thenif en='1' thenif cnt1="0101" and cnt0="1000" thenco<='1';cnt0:="1001";elsif cnt0<"1001" thencnt0:=cnt0+1;elsecnt0:="0000";if cnt1<"0101" thencnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;min1<=cnt1;min0<=cnt0;end process;end MIN;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity HOU isport(clk,en:in std_logic;h1,h0:out std_logic_vector(3 downto 0)); end HOU;architecture hour_arc of HOU isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0); beginif clk'event and clk='1' thenif en='1' thenif cnt1="0010" and cnt0="0011" thencnt1:="0000";cnt0:="0000";elsif cnt0<"1001" thencnt0:=cnt0+1;end if;end if;end if;h1<=cnt1;h0<=cnt0;end process;end hour_arc;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity SELTIM isport(clk:in std_logic;sec1,sec0,min1,min0,h1,h0:in std_logic_vector(3 downto 0);daout:out std_logic_vector(3 downto 0);sel:out std_logic_vector(2 downto 0));end SELTIM;architecture fun of SELTIM issignal count:std_logic_vector(2 downto 0);beginsel<=count;process(clk)beginif(clk'event and clk='1') thenif(count>="101") thencount<="000";elsecount<=count+1;end if;end if;case count iswhen"000"=>daout<= sec0;when"001"=>daout<= sec1;when"010"=>daout<= min0;when"011"=>daout<= min1;when"100"=>daout<=h0;when others =>daout<=h1;end case;end process;end fun;library ieee;use ieee.std_logic_1164.all;entity DISPLA isport(d:in std_logic_vector(3 downto 0);q:out std_logic_vector(6 downto 0));end DISPLA;architecture disp_are of DISPLA isbeginprocess(d)begincase d iswhen"0000" =>q<="0111111";when"0001" =>q<="0000110";when"0010" =>q<="1011011";when"0011" =>q<="1001111";when"0100" =>q<="1100110";when"0101" =>q<="1101101";when"0110" =>q<="1111101";when"0111" =>q<="0100111";when"1000" =>q<="1111111";when others =>q<="1101111";end case;end process;end disp_are;library ieee;use ieee.std_logic_1164.all;entity ALE isport(m1,m0,s1,s0:in std_logic_vector(3 downto 0);clk:in std_logic;q500,qlk:out std_logic);end ALE;architecture sss_arc of ALE isbeginprocess(clk)beginif clk'event and clk='1' thenif m1="0101" and m0="1001" and s1="0101" thenif s0="0001" or s0="0011" or s0="0101" or s0="0111" thenq500<='1';elseq500<='0';end if;end if;if m1="0101" and m0="1001" and s1="0101" and s0="1001" then qlk<='1';elseqlk<='0';end if;end if;end process; end sss_arc;。

部件一:60进制程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK60 ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK60;ARCHITECTURE ARTCLOCK60 OF CLOCK60 ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0';----进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN -----异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN------同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9)THENQL<="0000";IF(QH=5)THENQH<="0000";ELSEQH<=QH+1;END IF;ELSEQL<=QL+1;END IF;END IF;END IF;END PROCESS;END ARTCLOCK60;60进制波形图如下:部件二:24进制程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK24 ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK24;ARCHITECTURE ARTCLOCK24 OF CLOCK24 ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0';----进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN -----异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN------同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9 or (QH=2 AND QL=3))THENQL<="0000";IF(QH=2)THENQH<="0000";ELSEQH<=QH+1;END IF;ELSEQL<=QL+1;END IF;END IF;END IF;END PROCESS;END ARTCLOCK24;24进制的波形图如下:数字钟的全部程序如下:LIBRARY IEEE; ---秒信号USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK60s ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK60s;ARCHITECTURE ARTCLOCK60s OF CLOCK60s ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0'; --进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN ---异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN --同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9)THENQL<="0000";IF(QH=5)THENQH<="0000";ELSEQH<=QH+1;END IF;ELSEQL<=QL+1;END IF;END IF;END IF;END PROCESS;END ARTCLOCK60s;LIBRARY IEEE; ---分信号USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK60m ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK60m;ARCHITECTURE ARTCLOCK60m OF CLOCK60m ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0'; --进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN --异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN ---同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9)THENQL<="0000";IF(QH=5)THENQH<="0000";ELSEEND IF;ELSEQL<=QL+1;END IF;END IF;END IF;END PROCESS;END ARTCLOCK60m;LIBRARY IEEE; ---时信号USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK24 ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; --进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK24;ARCHITECTURE ARTCLOCK24 OF CLOCK24 ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0'; ---进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN ---异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN ---同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9 or (QH=2 AND QL=3))THENQL<="0000";IF(QH=2)THENQH<="0000";ELSEQH<=QH+1;END IF;ELSEEND IF;END IF;END IF;END PROCESS;END ARTCLOCK24;LIBRARY IEEE; ---时信号USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY hour ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESETS: IN STD_LOGIC; ---复位端LOADS: IN STD_LOGIC; ---置数端NRESETM: IN STD_LOGIC; ---复位端LOADM: IN STD_LOGIC; ---置数端NRESETH: IN STD_LOGIC; ---复位端LOADH: IN STD_LOGIC; ---置数端DS: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端DM: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端DH: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH1: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL1: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QH2: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL2: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QH3: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL3: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END hour;ARCHITECTURE ART OF hour ISCOMPONENT CLOCK60SPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT CLOCK60MPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT CLOCK24PORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; --始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;SIGNAL Z1,Z2:STD_LOGIC;BEGINU1: CLOCK60S PORT MAP(CLK,NRESETS,LOADS,DS,CI,Z1,QH1,QL1);U2: CLOCK60M PORT MAP(CLK,NRESETM,LOADM,DM,Z1,Z2,QH2,QL2);U3: CLOCK24 PORT MAP(CLK,NRESETH,LOADH,DH,Z2,CO,QH3,QL3);END ARCHITECTURE ART;电子钟全部引脚显示波形:00:00:59波形显示如下:00:59:59波形图如下,进位后为01:00:00 23:59:59波形图如下:调时间波形如下:用置位端进行调时,调到02:51:15波形如下:经验证,以上设计完全符合题目要求!。

1、分频器的设计奇数y分频:(式中y为我们所要分频的数,而x取只要小于y就行,尽量取中间点的值)module jifenpin(clk,q,reset);input clk,reset;output q;reg[3:0] i;reg q;always@(posedge clk)if(!reset)beginq<=1;i<=0;endelse if(i==x)beginq<=~q;i<=i+1;endelse if(i==y)beginq<=~q;i<=0;endelsei<=i+1;endmodule偶数n分频module erfenpin (q,clk,reset); input reset,clk;output q;reg q;reg [4:0]i;always @ (posedge clk )if(!reset)beginq<=1'b1;i<=0;endelse if(i==n/2)beginq<=~q;i<=0;endelse i<=i+1;endmodule2、频率计module pinlvji(clk,fin,en,reset,load,reg32b); input clk,fin;output en,reset,load,reg32b;reg en;reg[5:0] i,j,reg32b;always @(posedge clk)en<=~en;assign reset=~(en|clk);assign load=~en;always @(posedge fin)beginif(reset)i=0;else if(en)i=i+1;j=i;endalways @(posedge load)if(en==0)reg32b=j;endmodule3、交通灯(状态机)modulejiaotongdeng(clk,reset,sensor1,sensor2,red1,red2,yellow1 ,yellow2,green1,green2);input clk,reset,sensor1;input [2:0]sensor2;output red1,red2,yellow1,yellow2,green1,green2;reg red1,red2,yellow1,yellow2,green1,green2;reg [2:0]state;always @(posedge clk)if(!reset)beginstate<=1;red1<=0;red2<=0;yellow1<=0;yellow2<=0;green1<=0;green2<=0;endelsecase(state)0:beginif(sensor1==0)beginstate<=1;green1<=1;red2<=1;endend1:beginif(sensor1==0&&sensor2[2]==1) beginstate<=2;red2<=1;yellow1<=1;endelse if(sensor1==1)beginred1<=1;red2<=1;state<=0;endelsestate=1;end2:beginif(sensor1==0&&sensor2[1]==1) beginstate<=3;red1<=1;green2<=1;endelse if(sensor1==1)beginred1=1;red2=1;state<=0;endelsestate=2;end3:beginif(sensor1==0&&sensor2[0]==1) beginstate<=4;red1<=1;yellow2<=1;endelse if(sensor1==1)beginred1=1;red2=1;state<=0;endelsestate=3;end4:beginif(sensor1==0&&sensor2[1]==1) beginstate<=1;red2<=1;green1<=1;endelse if(sensor1==1)beginred1=1;red2=1;state<=0;endelsestate=4;endendcaseendmodule4、数字时钟module shizhong(clk,s,m,h);input clk;output[5:0] s,m,h;reg[5:0] s,m,h;reg mt,ht;wire mtclk,htclk;always@(posedge clk) beginif(s==59)begins<=0;mt<=1;endelsebegins<=s+1;mt<=0;endendassign mtclk=mt; always@(posedge mtclk) beginif(m==59)beginm<=0;ht<=1;endelsebeginm<=m+1;ht<=0;endendassign htclk=ht; always@(posedge htclk) beginif(h==23)h<=0;elseh<=h+1;endendmodule5、组合逻辑(数字时钟)module digit_clock(s,m,h,clk,clr,en);output [7:0] s,m;output [7:0] h;input clk,clr,en;wire clk,clr,en;wire[7:0] s,m,h;wire count_s,count_m,count_h;count_60 u0(s[7:4],s[3:0],count_s,clk,clr,en);count_60u1(m[7:4],m[3:0],count_m,clk,clr,count_s);count_24u2(h[7:4],h[3:0],count_h,clk,clr,count_m); endmodule。

1、流水灯(简易)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity roll isport ( clk :in std_logic;dout:out std_logic_vector(0 to 7));end roll;architecture behave of roll issignal count:std_logic_vector(0 to 7):="00000001";begindout<=count;process(clk)variable x:integer range 0 to 19999999;beginif rising_edge(clk) thenif x<19999999 then x:=x+1;else x:=0;count<=count(1 to 7)&count(0);end if;end if;end process;end behave;2、流水灯(模板)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led_water isport(clk:in std_logic;qout:out std_logic_vector(7 downto 0));end;architecture a of led_water issignal num:integer range 0 to 7 :=0;signal q0 :std_logic:='0';beginprocess(clk)variable count :integer range 0 to 10000000;beginif rising_edge(clk) thenif count<10000000 then count:=count+1;else q0<= NOT q0;count:=0;end if;end if;end process;process(q0)beginif rising_edge(q0) thenif num<7 then num<=num+1;else num<=0;end if;case num iswhen 0=> qout<="00000001";when 1=> qout<="00000010";when 2=> qout<="00000100";when 3=> qout<="00001000";when 4=> qout<="00010000";when 5=> qout<="00100000";when 6=> qout<="01000000";when 7=> qout<="10000000";end case;end if;end process;end;3、1到8同时显示library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity easy isport ( clk :in std_logic;cou:out std_logic_vector(2 downto 0);seg:out std_logic_vector(7 downto 0));end easy;architecture behave of easy issignal clkms :std_logic:='0';signal count:std_logic_vector(2 downto 0):="000";beginwith count selectseg <= "00000110" when "000", --可以修改代码实现不同数字显示"01011011" when "001","01001111" when "010","01100110" when "011","01101101" when "100","01111101" when "101","00000111" when "110","01111111" when "111","00100000" when others;process(clk)variable x:integer range 0 to 9999;beginif rising_edge (clk) thenif x<9999 then x:=x+1;else x:=0;clkms<= NOT clkms;end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif count<7 then count<=count+1;else count<="000";end if;end if;end process;cou<=count;end behave;4、点阵(模板)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dian isport ( clk :in std_logic;Q :out std_logic_vector(0 to 15);din:out std_logic_vector(3 downto 0));end;architecture behave of dian issignal count:std_logic_vector(3 downto 0):="1111";signal clkms :std_logic:='0';beginwith count selectQ<= x"0000" when "1111", --改成相应代码x"0000" when "1110",x"0000" when "1101",x"0000" when "1100",x"0000" when "1011",x"0000" when "1010",x"0000" when "1001",x"0000" when "1000",x"0000" when "0111",x"0000" when "0110",x"0000" when "0101",x"0000" when "0100",x"0000" when "0011",x"0000" when "0010",x"0000" when "0001",x"0000" when "0000",x"0000" when others;process(clk)variable x :integer range 0 to 9999;beginif rising_edge(clk) thenif x<9999 then x:=x+1;else clkms<= NOT clkms;x:=0;end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif count>0 then count<=count-1;else count<="1111";end if;end if;din<=count;end process;end behave;5、秒表(1)去抖library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity qudou isport ( clk :in std_logic;key :in std_logic;q :out std_logic);end qudou;architecture behave of qudou isbeginprocess(clk)variable x:integer range 0 to 3;beginif rising_edge(clk) thenif key='0' then q<='0';x:=0;elseif x<3 then x:=x+1;q<='0';else q<='1';end if;end if;end if;end process;end behave;(2)主程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity seconds isport ( clk :in std_logic;key1,key2:in std_logic; --清零/开始count:buffer std_logic_vector(2 downto 0); --数码管位选seg:out std_logic_vector(7 downto 0); --段选beep:out std_logic); --蜂鸣器(可以设定一定时间响)end seconds;architecture behave of seconds iscomponent qudouport ( clk :in std_logic;key :in std_logic;q :out std_logic);end component;signal clks,clkms,clksms:std_logic;signal out1,out2,flag:std_logic:='0';signal shi,ge,data:integer range 0 to 9;beginM1:qudou port map(clksms,key1,out1);M2:qudou port map(clksms,key2,out2);with data selectseg<="00111111" when 0,"00000110" when 1,"01011011" when 2,"01001111" when 3,"01100110" when 4,"01101101" when 5,"01111101" when 6,"00000111" when 7,"01111111" when 8,"01101111" when 9,"00000000" when others;process(clk)variable x:integer range 0 to 9999999;variable y:integer range 0 to 9999;variable z:integer range 0 to 99990;beginif rising_edge(clk) thenif x<9999999 then x:=x+1;else x:=0;clks<= NOT clks;end if;if y<9999 then y:=y+1;else y:=0;clkms<= NOT clkms;end if;if z<99999 then z:=z+1;else z:=0;clksms<= NOT clksms;end if;end if;end process;process(clks,flag)variable n:integer range 0 to 99;beginif flag='0' then n:=0;elsif rising_edge(clks) thenif n<99 then n:=n+1;else n:=0;end if;end if;shi<=n/10;ge<=n rem 10;end process;process(out1,out2)beginif out1='1' then flag<='0'; --清零elsif out2='1' then flag<='1'; --开始end if;end process;process(clkms)beginif rising_edge(clkms) thenif count<1 then count<=count+1;else count<="000";end if;end if;end process;beep<= clkms when (shi=5 AND ge=9) else'0';data<=shi when count="001" elsege;end behave;6、电子琴(去抖模块同4)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dianziqin isport ( clk :in std_logic;key1,key2,key3,key4,key5,key6,key7,key8:in std_logic;q :out std_logic); --蜂鸣器end dianziqin;architecture behave of dianziqin issignal clksms,q0:std_logic:='0';signal con1,con2,con3,con4,con5,con6,con7,con8:std_logic:='0';signal mus:integer range 0 to 38221;COMPONENT qudouport ( clk :in std_logic;din :in std_logic;q :out std_logic);end COMPONENT;beginM1:qudou PORT MAP(clksms,key1,con1);M2:qudou PORT MAP(clksms,key2,con2);M3:qudou PORT MAP(clksms,key3,con3);M4:qudou PORT MAP(clksms,key4,con4);M5:qudou PORT MAP(clksms,key5,con5);M6:qudou PORT MAP(clksms,key6,con6);M7:qudou PORT MAP(clksms,key7,con7);M8:qudou PORT MAP(clksms,key8,con8);q<=q0 AND (con1 OR con2 OR con3 OR con4 OR con5 OR con6 OR con7 OR con8);process(clk)variable count :integer range 0 to 49999;beginif rising_edge(clk) thenif count<49999 then count:=count+1;else clksms<= NOT clksms;count:=0;end if;end if;end process;process(clk)variable count :integer range 0 to 38221;beginif rising_edge(clk) thenif count<38221 then count:=count+1;else count:= mus;q0<= NOT q0;end if;end if;end process;process(con1,con2,con3,con4,con5,con6,con7,con8)beginif con1='1' then mus<=0;elsif con2='1' then mus<=4170;elsif con3='1' then mus<=7885;elsif con4='1' then mus<=9587;elsif con5='1' then mus<=12712;elsif con6='1' then mus<=15495;elsif con7='1' then mus<=17974;elsif con8='1' then mus<=19102;else NULL;end if;end process;end behave;7、数字钟(去抖模块同4)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity shuzi isport ( clk :in std_logic;key1 :in std_logic; --调时key2 :in std_logic; --调分fuc :in std_logic; --暂停sss :in std_logic; --秒清零beep :out std_logic; --蜂鸣器segout :out std_logic_vector (7 downto 0); --数码管段选count :out std_logic_vector (2 downto 0));--位选end shuzi;architecture behave of shuzi iscomponent qudouport ( clk :in std_logic;din :in std_logic;q :out std_logic);end component;signal clks,clkms,clksms,tm,th,tf,ss,beep1,beep2,flag0:std_logic:='0';signal outs,outss,outm,outsm,outh,outsh:integer range 0 to 11;signal count0:std_logic_vector (2 downto 0):="000";signal segout0:integer range 0 to 10;beginM1:qudou PORT MAP(clksms,fuc,tf);M2:qudou PORT MAP(clksms,key1,th);M3:qudou PORT MAP(clksms,key2,tm);M4:qudou PORT MAP(clksms,sss,ss);count<=count0;beep<=beep1 when outsm=5 AND outm=9 AND outss=5 AND (outs=0 OR outs=2 OR outs=4OR outs=6 OR outs=8) elsebeep2 when outsm=0 AND outm=0 AND outss=0 AND outs=0 else'0';with count0 selectsegout0<=outs when "000",outss when "001",10 when "010",outm when "011",outsm when "100",10 when "101",outh when "110",outsh when "111";with segout0 selectsegout <= "00111111" when 0,"00000110" when 1,"01011011" when 2,"01001111" when 3,"01100110" when 4,"01101101" when 5,"01111101" when 6,"00000111" when 7,"01111111" when 8,"01101111" when 9,"01000000" when 10,"00000000" when others;process(clk)variable cts:integer range 0 to 9999999;variable ctms:integer range 0 to 4999;variable ctsms:integer range 0 to 99999;variable ctb1:integer range 0 to 19999;variable ctb2:integer range 0 to 9999;beginif rising_edge(clk) thenif ctms<4999 then ctms:=ctms+1; else ctms:=0;clkms<= NOT clkms; end if;if ctb2<9999 then ctb2:=ctb2+1; else ctb2:=0;beep2<= NOT beep2; end if;if ctb1<19999 then ctb1:=ctb1+1; else ctb1:=0;beep1<= NOT beep1; end if;if ctsms<99999 then ctsms:=ctsms+1; else ctsms:=0;clksms<= NOT clksms; end if;if cts<9999999 then cts:=cts+1; else cts:=0;clks<= NOT clks; end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif count0<7 then count0<=count0+1;else count0<="000";end if;end if;end process;process(tf)beginif rising_edge(tf) then flag0<= NOT flag0;end if;end process;process(clks,th,tm,ss)variable min,sec:integer range 0 to 59;variable hour:integer range 0 to 23;beginif ss='1' then sec:=0;elsif rising_edge(clks) thencase flag0 iswhen '0'=> if sec<59 then sec:=sec+1;else sec:=0;if min<59 then min:=min+1;else min:=0;if hour<23 then hour:=hour+1;else hour:=0;end if;end if;end if;when '1'=> if th='1' thenif hour<23 then hour:=hour+1;else hour:=0;end if;end if;if tm='1' thenif min<59 then min:=min+1;else hour:=0;end if;end if;end case;end if;outsh<=hour/10;outh<=hour rem 10;outsm<=min/10;outm<=min rem 10;outss<=sec/10;outs<=sec rem 10;end process;end behave;8、点阵(上)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dianzhen isport ( clk :in std_logic;q :out std_logic_vector (3 downto 0);q1 :out std_logic_vector (0 to 15));end dianzhen;architecture behave of dianzhen istype str is array (0 to 79) of std_logic_vector(0 to 15);signal clkms :std_logic;signal q0:std_logic_vector(3 downto 0):="1111";signal n:integer range 0 to 79;signal num:integer range 0 to 15;signal ziku:str:=(x"0100",x"0100",x"0100",x"3FF8",x"2108",x"2108",x"2108",x"3FF8",x"2108",x"2108",x"2108",x"3FF8",x"210A",x"0102",x"0102",x"00FE",x"0000",x"7FF8",x"0010",x"0020",x"0040",x"0180",x"0100",x"FFFE",x"0100",x"0100",x"0100",x"0100",x"0100",x"0100",x"0500",x"0200",x"1000",x"087C",x"FF44",x"0048",x"7E48",x"4250",x"7E48",x"0048",x"7E44",x"0444",x"0844",x"0F68",x"F850",x"0840",x"2840",x"1040",x"0000",x"1FF0",x"1010",x"1010",x"1210",x"1110",x"1110",x"1010", x"FFFE",x"1010",x"1010",x"1010",x"2010",x"2010",x"4050",x"8020",x"0000",x"7C00",x"45FC",x"4904",x"4904",x"5104",x"4904",x"4904", x"45FC",x"4504",x"4504",x"6904",x"5104",x"4104",x"41FC",x"4104" );beginprocess(clk)variable count:integer range 0 to 2499;beginif rising_edge (clk) thenif count<2499 then count:=count+1;else count:=0;clkms<= NOT clkms;end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif q0>0 then q0<=q0-1;else q0<="1111";end if;if num<15 then num<=num+1;else num<=0;end if;end if;end process;process(q0(3))variable x:integer range 0 to 40;beginif rising_edge(q0(3)) thenif x<40 then x:=x+1;else x:=0;if n<79 then n<=n+1;else n<=0;end if;end if;end if;end process;q1<=ziku(n+num) when n+num<80 elseziku(n+num-80);q<=q0;end behave;9、点阵(左)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dianzhen isport ( clk :in std_logic;q :out std_logic_vector (3 downto 0);q1 :out std_logic_vector (0 to 15));end dianzhen;architecture behave of dianzhen istype stru is array (0 to 79) of std_logic_vector( 0 to 15);signal clkms :std_logic;signal flag,num:integer range 0 to 15;signal n:integer range 0 to 4;signal q0:std_logic_vector(3 downto 0):="1111";signal data1:std_logic_vector(0 to 31);signal ziku:stru:=(x"0100",x"0100",x"0100",x"3FF8",x"2108",x"2108",x"2108",x"3FF8", x"2108",x"2108",x"2108",x"3FF8",x"210A",x"0102",x"0102",x"00FE",x"0000",x"7FF8",x"0010",x"0020",x"0040",x"0180",x"0100",x"FFFE", x"0100",x"0100",x"0100",x"0100",x"0100",x"0100",x"0500",x"0200",x"1000",x"087C",x"FF44",x"0048",x"7E48",x"4250",x"7E48",x"0048", x"7E44",x"0444",x"0844",x"0F68",x"F850",x"0840",x"2840",x"1040", x"0000",x"1FF0",x"1010",x"1010",x"1210",x"1110",x"1110",x"1010", x"FFFE",x"1010",x"1010",x"1010",x"2010",x"2010",x"4050",x"8020",x"0000",x"7C00",x"45FC",x"4904",x"4904",x"5104",x"4904",x"4904", x"45FC",x"4504",x"4504",x"6904",x"5104",x"4104",x"41FC",x"4104");begindata1<=ziku(n*16+num)&ziku(n*16+16+num) when n<4 elseziku(n*16+num)&ziku(num);process(clk)variable count:integer range 0 to 2499;beginif rising_edge (clk) thenif count<2499 then count:=count+1;else count:=0;clkms<= NOT clkms;end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif q0>0 then q0<=q0-1;else q0<="1111";end if;if num<15 then num<=num+1;else num<=0;end if;end if;end process;with flag selectq1<=data1(15 to 30) when 15,data1(14 to 29) when 14,data1(13 to 28) when 13,data1(12 to 27) when 12,data1(11 to 26) when 11,data1(10 to 25) when 10,data1(9 to 24) when 9,data1(8 to 23) when 8,data1(7 to 22) when 7,data1(6 to 21) when 6,data1(5 to 20) when 5,data1(4 to 19) when 4,data1(3 to 18) when 3,data1(2 to 17) when 2,data1(1 to 16) when 1,data1(0 to 15) when 0,(others=>'0') when others; process(q0(3))variable x :integer range 0 to 40;beginif rising_edge(q0(3)) thenif x<40 then x:=x+1;else x:=0;if flag<15 then flag<=flag+1;elseif n<4 then n<=n+1;else n<=0;end if;flag<=0;end if;end if;end if;end process;q<=q0;end behave;10、频率计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity plj isport ( start:in std_logic; --复位信号clk :in std_logic; --系统时钟clk1:in std_logic; --被测时钟yy1:out std_logic_vector(7 downto 1); --八段码w1 :out std_logic_vector(2 downto 0)); --位选信号end plj;architecture behav of PLj issignal b1,b2,b3,b4,b5,b6,b7,b8:std_logic_vector(3 downto 0); --十进制计数器signal v1,v2,v3,v4,v5,v6,v7,v8:std_logic_vector(3 downto 0);signal bcd:std_logic_vector(3 downto 0); --BCD码寄存器signal q :integer range 0 to 39999999; --秒分频系数signal qq : integer range 0 to 79999; --动态扫描分频系数signal en,bclk,e1:std_logic; --使能信号,有效被测信号signal sss : std_logic_vector(3 downto 0); --小数点signal bcd0,bcd1,bcd2,bcd3 : std_logic_vector(3 downto 0); --寄存7位十位计数器中有效的高4位数据beginsecond:process(clk) --此进程产生一个持续时间为一秒的的闸门信号beginif start='1' then q<=0;elsif clk'event and clk='1' thenif q<39999999 then q<=q+1;else q<=0;end if;end if;if q<19999999 and start='0' then en<='1';else en<='0';end if;if q=0 then e1<='0';else e1<='1';end if;end process;com:process(en,start,clk1) --此进程完成对被测信号计脉冲数beginif (start='1' or e1='0') and en='1' thenb1<="0000";b2<="0000";b3<="0000";b4<="0000";b5<="0000";b6<="0000";b7<="0000";b8<="0000";elsif clk1'event and clk1='1' and en='1' thenif b1="1001" then b1<="0000"; --完成个位十进制计数if b2="1001" then b2<="0000"; --完成百位十进制计数if b3="1001" then b3<="0000"; --完成千位十进制计数if b4="1001" then b4<="0000"; --完成万位十进制计数if b5="1001" THEN b5<="0000"; --完成十万位十进制计数if b6="1001" then b6<="0000"; --完成百万位十进制计数if b7="1001" then b7<="0000"; --完成千万位十进制计数if b8="1001" then b8<="0000"; --完成千万位十进制计数else b8<=b8+1;end if;else b7<=b7+1;end if;else b6<=b6+1;end if;else b5<=b5+1;end if;else b4<=b4+1;end if;else b3<=b3+1;end if;else b2<=b2+1;end if;else b1<=b1+1;end if;end if;if en='0' then v1<=b1;v2<=b2;v3<=b3;v1<=b4;v5<=b5;v6<=b6;v7<=b7;v8<=b8;else v1<=v1;v2<=v2;v3<=v3;v4<=v4;v5<=v5;v6<=v6;v7<=v7;v8<=v8;end if;end process;weixuan:process(clk) --此进程完成数据的动态显示beginif clk'event and clk='1' thenif qq< 9999 then qq<=qq+1;bcd<=v1; w1<="000";elsif qq<19999 then qq<=qq+1;bcd<=v2; w1<="001";elsif qq<29999 then qq<=qq+1;bcd<=v3; w1<="010";elsif qq<39999 then qq<=qq+1;bcd<=v4; w1<="011";elsif qq<49999 then qq<=qq+1;bcd<=v5; w1<="100";elsif qq<59999 then qq<=qq+1;bcd<=v6; w1<="101";elsif qq<69999 then qq<=qq+1;bcd<=v7; w1<="110";elsif qq<79999 then qq<=qq+1;bcd<=v8; w1<="111";else qq<=0;end if;end if;end process;m0: process (bcd) --译码begincase bcd iswhen "0000"=>yy1(7 downto 1)<="1111110";when "0001"=>yy1(7 downto 1)<="0110000";when "0010"=>yy1(7 downto 1)<="1101101";when "0011"=>yy1(7 downto 1)<="1111001";when "0100"=>yy1(7 downto 1)<="0110011";when "0101"=>yy1(7 downto 1)<="1011011";when "0110"=>yy1(7 downto 1)<="1011111";when "0111"=>yy1(7 downto 1)<="1110000";when "1000"=>yy1(7 downto 1)<="1111111";when "1001"=>yy1(7 downto 1)<="1111011";when others=>yy1(7 downto 1)<="0000000";end case;end process;end behav;11、抢答器library ieee;use ieee.std_Logic_1164.all;use ieee.std_Logic_unsigned.all;use ieee.std_Logic_arith.all;entity xuan81 isport(rst,clk:in std_logic;--复位,时钟接口key:in std_logic_vector(8 downto 1);--选手抢答的按键segout :out std_logic_vector (0 to 6);count:out std_logic_vector(2 downto 0);d:out std_logic);--不同频率的叫声end;architecture a of xuan81 issignal count2 :integer range 0 to 3:=1;signal en :std_logic:='1';signal c3,c4 :std_logic:='1';signal c1,c2: std_logic;signal qh,ql:integer range 0 to 10;signal sz:integer range 0 to 10:=10;signal ld :std_LOGIC:='1';--一个控制数码管计数显示的信号量signal q0:integer range 0 to 10000000;signal q1:integer range 0 to 10000;signal q2:integer range 0 to 20000;signal clk0,clk1,clk2:std_logic;signal count1 : integer range 0 to 2 ;signal Q: integer range 0 to 10;signal CQI:std_logic_vector(2 downto 0):="000";beginprocess(clk)beginif clk'event and clk='1' thenif q0<10000000 then q0<=q0+1;else clk0<=not clk0; q0<=0;end if;if q1<10000 then q1<=q1+1;else clk1<=not clk1; q1<=0;end if;if q2<20000 then q2<=q2+1;else clk2<=not clk2; q2<=0;end if;end if;end process;process(c1,c2)beginif c1='1' and c3='1' then d<=clk1;en<='1';elsif c2='1' and c4='1' then d<=clk2;en<='1';else d<='0';en<='0';end if;end process;process(clk0,en)beginif clk0'event and clk0='1' thenif en='1' thenif count2<3 then count2<=count2+1;else c3<='0';c4<='0';count2<=0;end if;end if;end if;if c1='0' then c3<='1';end if;if c2='0' then c4<='1';end if;end process;process(clk0,rst,key)variable m:integer range 1 to 31:=30;beginif rst='1' then m:=31;sz<=10;ld<='1';c1<='0';c2<='1';elsif rst='0' thenif ld='0' then m:=31;elsif ld<='1' thenif clk0'event and clk0='1' thenif m=1 then c1<='1';ld<='0';else m:=m-1;c1 <='0';end if ;if (key(1)='1') then sz<=1; c2<='1';ld<='0';elsif (key(2)='1') then sz<=2; c2<='1';ld<='0';elsif (key(3)='1') then sz<=3; c2<='1';ld<='0';elsif (key(4)='1') then sz<=4; c2<='1';ld<='0';elsif (key(5)='1') then sz<=5; c2<='1';ld<='0';elsif (key(6)='1') then sz<=6; c2<='1';ld<='0';elsif (key(7)='1') then sz<=7; c2<='1';ld<='0';elsif (key(8)='1') then sz<=8; c2<='1';ld<='0';else c2<='0';end if;END IF;END IF;if m=31 then qh<=10;ql<=10;elseqh<=m/10;ql<=m rem 10;end if;END IF;end process;process(clk1)beginif clk1'event and clk1='1' thenif count1<2 then count1<=count1+1;else count1<=0;end if;if CQI<2 THEN CQI<=CQI+1;ELSE CQI<="000";end if;end if;case CQI iswhen "000"=> count<="001";when "001"=> count<="000";when "010"=> count<="011";when others=>null;end case;case count1 iswhen 0=>Q<=qh;when 1=>Q<=ql;when 2=>Q<=sz;end case;end process;process (Q)begincase Q iswhen 0 => segout<="1111110";when 1 => segout<="0110000";when 2 => segout<="1101101";when 3 => segout<="1111001";when 4 => segout<="0110011";when 5 => segout<="1011011";when 6 => segout<="1011111";when 7 => segout<="1110000";when 8 => segout<="1111111";when 9 => segout<="1111011";when others=>segout<="0000000";end case;end process;end;。