EDA 常见实例源程序代码vhdl

- 格式:doc

- 大小:637.50 KB

- 文档页数:62

EDA常见实例源程序代码vhdl第4章用VHDL程序实现常用逻辑电路4.1 组合逻辑电路设计4.1.1 基本逻辑门library ieee;use iee.std_logic_1164.all;entity jbm isport(a,b: in bit;f1,f2,f3,f4,f5,f: out bit);end jbm;architecture a of jbm isbeginf1<=a and b; --构成与门f2<=a or b; --构成或门f<=not a; --构成非门f3<=a nand b; --构成与非门f4<=a nor b; --构成异或门f5<=not(a xor b); --构成异或非门即同门end;4.1.2 三态门library ieee;use ieee.std_logic_1164.all;entity tri_s isport(enable: in std_logic;datain: in std_logic_vector(7 downto 0); dataout: out std_logic_vector(7 downto0)); end tri_s;architecture bhv of tri_s isbeginprocess(enable,datain)beginif enable='1' thendataout<=datain;elsedataout<="ZZZZZZZZ";end if;end process;end bhv;4.1.3 3-8译码器library ieee;use ieee.std_logic_1164.all;entity decoder3_8 isport(a,b,c,g1,g2a,g2b: in std_logic; y: out std_logic_vector(7 downto 0)); end decoder3_8;architecture a of decoder3_8 is signal dz:std_logic_vector(2 downto 0); begindz<=c&b&a;process (dz,g1,g2a,g2b)beginif(g1='1'and g2a='0'and g2b='0')then case dz iswhen "000"=> y<="11111110"; when "001"=> y<="11111101"; when "010"=> y<="11111011"; when "011"=> y<="11110111"; when "100"=> y<="11101111"; when "101"=> y<="11011111";when "110"=> y<="10111111";when "111"=> y<="01111111";when others=>y<="XXXXXXXX";end case;elsey<="11111111";end if;end process;4.1.4 优先编码器library ieee;use ieee.std_logic_1164.allentity coder isport(din: in std_logic_vector(0 to 7); output: out std_logic_vector(0 to 2)); end coder;architecture behave of coder issignal sint: std_logic_vevtor(4 downto 0); beginprocess(din)beginif (din(7)='0') thenoutput <= "000" ;elsif (din(6)='0') thenoutput <= "100" ;elsif (din(5)='0') thenoutput <= "010" ;elsif (din(4)='0') thenoutput <= "110" ;elsif (din(3)='0') thenoutput <= "001" ;elsif (din(2)='0') thenoutput <= "101" ;elsif (din(1)='0') thenoutput <= "011" ;elseoutput <= "111" ;end if;end process;end behav;4.1.5 7段码译码器library ieee;use ieee.std_logic_1164.allentity decl7s isport (a: in std_logic_vector (3 downto 0); led7s: out std_logic_vector(6 downto 0)); end decl7s;architecture behave of decl7s isbeginprocess(a)begincase a iswhen "0000" => led7s <= "0111111" ; when "0001" => led7s <= "0000110" ; when "0010" => led7s <= "1011011" ; when "0011" => led7s <= "1001111" ; when "0100" => led7s <= "1100110" ; when "0101" => led7s <= "1101101" ; when "0110" => led7s <= "1111101" ; when "0111" => led7s <= "0000111" ; when "1000" => led7s <= "1111111" ;when "1001" => led7s <= "1101111" ; when "1010" => led7s <= "1110111" ; when "1011" => led7s <= "1111100" ; when "1100" => led7s <= "0111001" ; when "1101" => led7s <= "1011110" ; when "1110" => led7s <= "1111001" ; when "1111" => led7s <= "1110001" ; when others => null;end case;end process;end behave;4.1.6二-十进制BCD译码器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity bcdymq isport(din : in integer range 15 downto 0; a,b : out integer range 9 downto 0); end;architecture fpq1 of bcdymq isbeginp1: process(din)beginif din<10 thena< =din;b< =0;elsea< =din-10;end if;end process p1;end;4.1.7 多位加(减)法器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all; entity jianfaqi isport(a,b : in std_logic_vector(0 to 3); c0: in std_logic;c1: out std_logic;d : out std_logic_vector(0 to 3)); end;architecture a of jianfaqi isbeginprocessbeginif a>b+c0 thend<=a-(b+c0);c1<='0';elsec1<='1';d<=("10000")-(b+c0-a);end if;end process ;end ;4.2 时序逻辑电路设计4.2.1 触发器RS触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity rsff isport(r,s,clk:in std_logic;q,qb:buffer std_logic);end rsff;architecture rsff_art of rsff is signal q_s,qb_s:std_logic; beginprocess(clk,r,s)beginif (clk'event and clk='1') then if (s='1' and r='0') thenq_s<='0' ;qb_s<='1' ;elsif (s='0' and r='1') thenq_s <= '1' ;qb_s <= '0' ;elsif (s='0' and r='0') thenq_s <= q_s;qb_s <= qb_s;end if;q_s <= q_s;qb_s <= qb_s;end process;end rsff_art;同步复位D触发器library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_signed.all; entity syndff isport(d,clk,reset:in std_logic;q,qb:out std_logic);end syndff;architecture dff_art of syndff is beginprocess(clk)beginif (clk'event and clk='1') thenif (reset='0') thenq<='0';qb<='1';elseq<=d;qb<=not q;end if;end if;end process;end dff_art;JK触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all; entity asynjkff isport(j,k,clk,set.reset:in std_logic; q,qb:out std_logic);end asynjkff;architecture jkff_art of asynjkff is singal q_s,qb_s:std_logic;beginprocess(clk,set,reset)beginif (set='0' and reset='1' ) then q_s<='1';qb_s<='0';elsif (set='1' and reset='0' ) then q_s<='0';qb_s<='1';elsif (clk'event and clk='1') then if (j='0' and k='1' ) thenq_s<='0';qb_s<='1';elsif (j='1' and k='0' ) thenq_s<='1';qb_s<='0';elsif (j='1' and k='1' ) thenq_s<=not q_s;qb_s<=not qb_s;end if;end if;q<= q_s;qb<= qb_s;end process;end jkff_art;T触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all; entity tff isport(t,clk: in std_logic;q: out std_logic);end;architecture tff_art of tff issignal q_temp: std_logic;beginp1:process(clk)beginif rising_edge(clk) thenif t='1' then --当T=1时T触发器具有2分频的功能q_temp<=not q_temp;elseq_temp<=q_temp;end if;end if;q<=q_temp;end process;q<=q_temp;end tff_art;4.2.2计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt4 ISport( clk: in std_logic;q: out std_logic_vector(3 downto 0));end cnt4;architecture behave of cnt4 issignal q1: std_logic_vector(3 downto 0);beginprocess(clk)beginif (clk'event and clk = '1') thenq1<=q1+1;end if;end process;q<=q1;一般计数器设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport( clk,rst,en,updown: in std_logic;cq: out std_logic_vector(3 downto 0));end cnt10;architecture behave of cnt10 isbeginprocess(clk,rst,en,updown)variable cqi:std_logic_vector(3 downto 0);beginif rst='1' thencqi:=(others=>'0'); --计数器异步复位elsif (clk'event and clk = '1') then --检测时钟上升沿if en='1'then --检测是否允许计数(同步使能)if updown='0'thenif cqi<9 thencqi:=cqi+1; --允许计数,检测是否小于9elsecqi:=(others=>'0'); --大于9,计数值清零end if;elseif cqi>0 thencqi:=cqi-1; --检测是否大于0elsecqi:=(others=>'1'); ---否则,计数值置1end if;end if;end if;end if;cq<=cqi; --将计数值向端口输出end process;end behave;4.2.3 分频器library ieee;use std_logic_1164.all;use std_logic_unsigned.all;entity freq1 isport(clk: in std_logic;d: in std_logic_vector(7 downto 0);fout: out std_logic);end;architecture one of dvf issignal full: std_logic;beginp_reg:process(clk)variable cnt8: std_logic_vector(7 downto 0);if clk'event and clk='1'then --检测时钟上升沿if cnt8=''11111111'' thencnt8:=d; --当CNT8计数计满时,输入数据D被同步预置给计数器CNT8full<='1';--同时使溢出标志信号FULL输出为高电平elsecnt8:=cnt8+1;--否则继续作加1计数full<='0'; --且输出溢出标志信号FULL为低电平end if;end if;end process p_reg;p_div:process(full)variable cnt2: std_logic;beginif full'event and full='1' thencnt2:=not cnt2; --如果溢出标志信号FULL为高电平,T触发器输出取反if cnt2='1'thenfout<='1';elsefout<='0';end if;end if;end process p_div;end;4.2.4 移位寄存器library ieee;use ieee.std_logic_1164.all;entity shift isport(clk,c0: in std_logic;--时钟和进位输入md: in std_logic_vector(2 downto 0);--移位模式控制字d: in std_logic_vector(7 downto 0);--待加载移位的数据qb: out std_logic_vector(7 downto 0);--移位数据输出cn: out std_logic);--进位输出end;architecture behave of shift issignal reg: std_logic_vector(7 downto 0);signal cy: std_logic;beginprocess(clk,md,c0)beginif clk'event and clk='1' thencase md iswhen "001" => reg (0) <= c0 ;reg (7 downto 1) <= reg (6 downto 0);cy <= reg (7); --带进位循环左移when "010" => reg (0) <= reg (7);reg (7 downto 1) <= reg (6 downto 0); --自循环左移when "011" => reg (7) <= reg (0);reg (6 downto 0) <= reg (7 downto 1); --自循环右移when "100" => reg (7) <= C0 ;reg (6 downto 0) <= reg (7 downto 1);cy <= reg (0); --带进位循环右移when "101" => reg (7 downto 0) <= d(7 downto 0); --加载待移数when others => reg<= reg ; cy<= cy ; --保持end case;end if;end process;qb(7 downto 0) <= reg (7 downto 0); cn <= cy; --移位后输出end behav;4.3 状态机逻辑电路设计4.3.1 一般状态机设计library ieee;use ieee.std_logic_1164.all;entity s_machine isport ( clk,reset : in std_logic;state_inputs : in std_logic_vector(0 to1);comb_outputs : out integer range 0 to 15 );end s_machine;architecture behv of s_machine istype fsm_st is (s0, s1, s2, s3); --数据类型定义,状态符号化signal current_state, next_state: fsm_st; --将现态和次态定义为新的数据类型beginreg: process(reset,clk) --主控时序进程beginif reset = '1' thencurrent_state <= s0; --检测异步复位信号elsif clk='1' and clk'event thencurrent_state <= next_state;end if;end process;com:process(current_state, state_inputs) --主控组合进程begincase current_state iswhen s0 => comb_outputs<= 5;if state_inputs = "00" thennext_state<=s0;elsenext_state<=s1;end if;when s1 => comb_outputs<= 8;if state_inputs = "00" thennext_state<=s1;elsenext_state<=s2;end if;when s2 => comb_outputs<= 12;if state_inputs = "11" thennext_state <= s0;elsenext_state <= s3;end if;when s3 => comb_outputs <= 14;if state_inputs = "11" thennext_state <= s3;elsenext_state <= s0;end if;end case;end process;end behv;4.3.2状态机的应用library ieee;use ieee.std_logic_1164.all;entity asm_led isport(clk,clr : in std_logic;led1,led2,led3:out std_logic);end;architecture a of asm_led istype states is (s0,s1,s2,s3,s4,s5); --对状态机的状态声明signal q: std_logic_vector( 0 to 2);signal state : states;beginp1: process(clk,clr)beginif(clr='0')thenstate<=s0;elsif (clk'event and clk='1') thencase state iswhen s0=> state <=s1;when s1=> state <=s2;when s2=> state <=s3;when s3=> state <=s4;when s4=> state <=s5;when s5=> state <=s0;when others => state<=s0;end case;end if;end process p1;p2: process (clr,state)beginif(clr='0') thenled1<='0';led2<='0';led3<='0';elsecase state iswhen s0=> led1<='1';led2<='0';led3<='0'; when s1=> led1<='0';led2<='1';led3<='0'; when s2=> led1<='0';led2<='1';led3<='0'; when s3=> led1<='0';led2<='0';led3<='1'; when s4=> led1<='0';led2<='0';led3<='1'; when s5=> led1<='0';led2<='0';led3<='1'; when others => null;end case;end if;end process p2;end ;第6章EDA仿真技术应用实例6.1带使能和片选端的16:4线优先编码器设计子模块设计源代码:library ieee;use ieee.std_logic_1164.all;entity pencoder isport(d:in std_logic_vector(7 downto 0);ei:in std_logic; --ei:enable inputgs,eo:out bit; --gs:chip select output;eo:enable output q2,q1,q0:out std_logic);end pencoder;architecture encoder of pencoder isbeginprocess(d)beginif(d(0)='0' and ei='0')thenq2<='1';q1<='1';q0<='1';gs<='0';eo<='1';elsif(d(1)='0' and ei='0')thenq2<='1';q1<='1';q0<='0';gs<='0';eo<='1';elsif(d(2)='0' and ei='0')thenq2<='1';q1<='0';q0<='1';gs<='0';eo<='1';elsif(d(3)='0' and ei='0')thenq2<='1';q1<='0';q0<='0';gs<='0';eo<='1';elsif(d(4)='0' and ei='0')thenq2<='0';q1<='1';q0<='1';gs<='0';eo<='1';elsif(d(5)='0' and ei='0')thenq2<='0';q1<='1';q0<='0';gs<='0';eo<='1';elsif(d(6)='0' and ei='0')thenq2<='0';q1<='0';q0<='1';gs<='0';eo<='1';elsif(d(7)='0' and ei='0')then --d7 prioty encoder q2<='0';q1<='0';q0<='0';gs<='0';eo<='1';elsif(ei='1')thenq2<='1';q1<='0';q0<='1';gs<='1';eo<='1';elsif(d="11111111" and ei='0')thenq2<='1';q1<='1';q0<='1';gs<='1';eo<='0';end if;end process;end encoder;6.27段显示译码器设计译码器设计源代码:library ieee;use ieee.std_logic_1164.all;entity decoder47 isport(lt,ibr,ib_ybr:in bit;a: in std_logic_vector(3 downto 0);y:out std_logic_vector(6 downto 0));end decoder47;architecture art of decoder47 isbeginprocess(lt,ibr,ib_ybr,a)variable s: std_logic_vector(3 downto 0);begins:=a(3)&a(2)&a(1)&a(0);if lt='0' and ib_ybr='1' theny<="1111111"; --检查七段显示管是否正常elsif ibr='0' and a="0000" theny<="0000000";elsecase s iswhen"0000"=>y<="1111110"; --7Ewhen"0001"=>y<="0110000"; --30when"0010"=>y<="1101101"; --6Dwhen"0011"=>y<="1111001"; --79when"0100"=>y<="0110011"; --33when"0101"=>y<="1011011"; --5Bwhen"0110"=>y<="0011111"; --5Fwhen"0111"=>y<="1110000"; --70when"1000"=>y<="1111111"; --7Ewhen"1001"=>y<="1110011"; --7Bwhen"1010"=>y<="0001101"; --0Dwhen"1011"=>y<="0011001"; --19when"1100"=>y<="0100011"; --23when"1101"=>y<="1001011"; --4Bwhen"1110"=>y<="0001111"; --0Fwhen"1111"=>y<="0000000";end case;end if;end process;end art;6.3带异步清零端的12位二进制全加器设计子模块源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder4b isport(clr,cin: in std_logic;a,b: in std_logic_vector(3 downto 0);s: out std_logic_vector(3 downto 0); cout:out std_logic);end adder4b;architecture art of adder4b issignal sint:std_logic_vector(4 downto 0); signal aa,bb:std_logic_vector(4 downto 0); beginprocess(clr)beginif clr='1'thensint<="00000";elseaa<='0'&a;bb<='0'&b;sint<=aa+bb+cin;end if;s<=sint(3 downto 0);cout<=sint(4);end process;end art;顶层模块设计源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder12b isport(clr,cin: in std_logic;a,b: in std_logic_vector(11 downto 0);s: out std_logic_vector(11 downto 0);cout:out std_logic);end adder12b;architecture art of adder12b iscomponent adder4b isport(clr,cin: in std_logic;a,b: in std_logic_vector(3 downto 0);s: out std_logic_vector(3 downto 0);cout:out std_logic);end component;signal carry_out1:std_logic;signal carry_out2:std_logic;beginu1:adder4b port map(clr=>clr,cin=>cin,a=>a(3 downto 0),b=>b(3 downto 0),s=>s(3 downto 0),cout=>carry_out1);u2:adder4b port map(clr=>clr,cin=>carry_out1,a=>a(7 downto 4),b=>b(7 downto 4),s=>s(7 downto 4),cout=>carry_out2);u3:adder4b port map(clr=>clr,cin=>carry_out2,a=>a(11 downto 8),b=>b(11 downto 8),s=>s(11 downto 8),cout=>cout);end art;6.4 带异步清零/置位端的JK触发器设计带异步清零/置位端的JK触发器源程序如下:library ieee;use ieee.std_logic_1164.all;entity jkff_logic isport(j,k,clk,clr,set:in std_logic;q:out std_logic);end jkff_logic;architecture art of jkff_logic issignal q_s:std_logic;beginprocess(clk,clr,set,j,k)if set='0' thenq_s<='1'; --异步置位elsif clr='1' thenq<='0'; --异步复位elsif clk'event and clk='1' thenif (j='0') and (k='1') thenq_s<='0';elsif(j='1') and (k='0') thenq_s<='1';elsif(j='1') and (k='1') thenq_s<=not q_s;end if;end if;q<=q_s;end process;end art;6.5 4位锁存器设计子模块设计源代码:library ieee;use ieee.std_logic_1164.all;entity latch1b isport(d: in std_logic;ena: in std_logic; --使能端q: out std_logic);end latch1b;architecture art of latch1b isbeginprocess(d,ena)beginif ena='1' thenq<=d;end if;end process;end art;元件声明程序包设计源代码:library ieee;use ieee.std_logic_1164.all;package my_package iscomponent latch1port(d:in std_logic;ena:in std_logic;q: out std_logic);end component;end;顶层模块设计源代码:library ieee;use ieee.std_logic_1164.all;use work.my_package.all; --使用用户自定义的程序包entity latch4d isport(d: in std_logic_vector(3 downto 0);oen: in bit;q:out std_logic_vector(3 downto 0));end latch4d;architecture one of latch4d issignal sig_save:std_logic_vector(3 downto 0);begingetlatch:for n in 0 to 3 generate --用for_generate语句循环例化4个1位锁存器latchx:latch1 port map(d(n),g,sig_save(n)); --关联end generate;q<=sig_save when oen='0'else"ZZZZ";end one;6.6 32进制多样型计数器设计(1)32进制同步加法计数器源程序32进制同步加法计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_plus isport(clk,clr:in std_logic;dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_plus issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr,)begind1<=(others=>'0');d0<="0000"; --同步清零elsif clk'event and clk='1' thenif(d1=3 and d0=1)thend1<="0000";d0<="0000"; --计数到32时清零elsif(d0=1) thend0<="0000";d1<=d1+1;elsed0<=d0+1;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(2)32进制同步减法计数器源程序32进制同步减法计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_sub isport(clk,clr:in std_logic;dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_sub issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr)begind1<="0000";d0<="0000"; --异步清零elsif clk'event and clk='1' thenif(d1=0 and d0=0) thend1<="0011";d0<="0001"; --设定容量31elsif(d0=0) thend0<="0001";d1<=d1-1;elsed0<=d0-1;d1<=d1;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(3)32进制同步可逆计数器源程序32进制同步可逆计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_reversible isport(clk,clr,s:in std_logic; --s=1加法计数,s=0减法计数dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_reversible issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr,s)beginif clr='1'thend1<="0000";d0<="0000"; --异步清零elsif (clk'event and clk='1' )then if s='1' thenif(d1=3 and d0=1) thend1<="0000";d0<="0000"; --计数到31时清零elsif(d0=1) thend0<="0000";d1<=d1+1;else d0<=d0+1;end if;elsif s='0' thenif(d1=0 and d0=0)thend1<="0011";d0<="0001"; --设定容量31elsif(d0=0) thend0<="0001";d1<=d1-1;elsed0<=d0-1;d1<=d1;end if;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(4)32进制异步加法计数器源程序32进制异步加法计数器源程序如下:①子模块D触发器源程序设计。

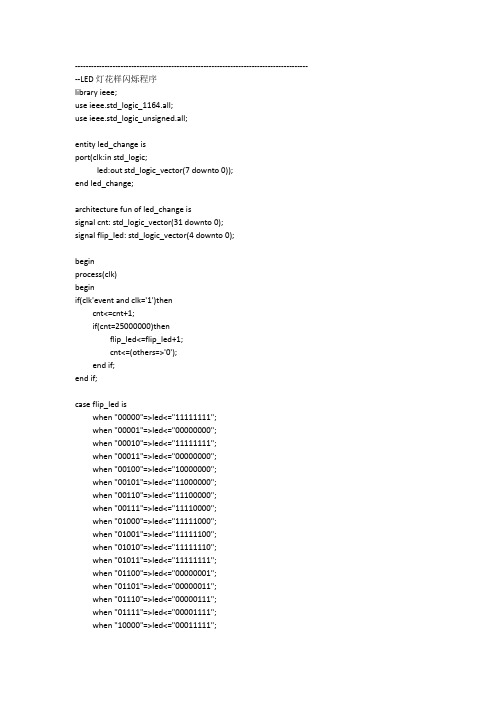

--------------------------------------------------------------------------------------- --LED灯花样闪烁程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led_change isport(clk:in std_logic;led:out std_logic_vector(7 downto 0));end led_change;architecture fun of led_change issignal cnt: std_logic_vector(31 downto 0);signal flip_led: std_logic_vector(4 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thencnt<=cnt+1;if(cnt=25000000)thenflip_led<=flip_led+1;cnt<=(others=>'0');end if;end if;case flip_led iswhen "00000"=>led<="11111111";when "00001"=>led<="00000000";when "00010"=>led<="11111111";when "00011"=>led<="00000000";when "00100"=>led<="10000000";when "00101"=>led<="11000000";when "00110"=>led<="11100000";when "00111"=>led<="11110000";when "01000"=>led<="11111000";when "01001"=>led<="11111100";when "01010"=>led<="11111110";when "01011"=>led<="11111111";when "01100"=>led<="00000001";when "01101"=>led<="00000011";when "01110"=>led<="00000111";when "01111"=>led<="00001111";when "10000"=>led<="00011111";when "10001"=>led<="00111111";when "10010"=>led<="01111111";when "10011"=>led<="11111111";when "10100"=>led<="00000000";when others =>led<="ZZZZZZZZ";end case;if(flip_led>"10100")thenflip_led<="00000";end if;end process;end fun;--拨码开关控制LED程序library ieee;use ieee.std_logic_1164.all;entity switch_led isport(key : in std_logic_vector(1 downto 0);led : out std_logic_vector(7 downto 0)); --八个led灯end switch_led;architecture fun of switch_led isbeginprocess(key)begincase key iswhen "00" => led <="00000000"; -- // "0"when "01" => led <="00001111"; -- // "1"when "10" => led <="11110000"; -- // "2"when "11" => led <="11111111"; -- // "3"when others => led <="ZZZZZZZZ";end case;end process;end;--按键消抖控制LED程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity stable_key isport(clk :in std_logic;key_in:in std_logic;key_out: out std_logic);end ;architecture fun of stable_key issignal cnt : integer range 0 to 1999999;signal key ,key_d : std_logic;beginprocess(clk)beginif clk'event and clk='1' thenif key /= key_in then -----键值变化开始计时10ms key_d <= key_in;cnt <= 0;elsif cnt=1999999 then ---10mskey_out <= not key_d;cnt <= 0;elsecnt <= cnt + 1 ;end if ;key<= key_in;end if ;end process;end ;--蜂鸣器电子琴程序library ieee;use ieee.std_logic_1164.all;entity digital_piano isport(key : in std_logic_vector(7 downto 0); --定义8个按键key1~key8clk : in std_logic; --时钟输入端50Mhzbeep: out std_logic); --蜂鸣器输出端end digital_piano;architecture fun of digital_piano issignal freq : integer range 0 to 50000;signal beep_reg: std_logic;beginbeep_process: process(clk,freq) --分频进程--本工程内核心进程,计数器的大小由counter决定variable cnt : integer range 0 to 50000;beginif clk'event and clk='1' thenif cnt < freq thencnt := cnt + 1;elsecnt := 0 ;beep_reg <=not beep_reg;end if;end if;end process beep_process;freq_process: process(key)begincase key iswhen "11111110" => freq <= 47774; ---------------------------------counter 计算公式:中音do的频率为523.3hz,为了在上个beep_pro进程中得到523的频率counter= 50*1000000/(523*2)when "11111101" => freq <= 42568; --中音re的频率为587.3hzwhen "11111011" => freq <= 37919; --中音mi的频率为659.3hzwhen "11110111" => freq <= 35791; --中音fa的频率为698.5hzwhen "11101111" => freq <= 31888; --中音sol的频率为784hzwhen "11011111" => freq <= 28409; --中音la的频率为880hzwhen "10111111" => freq <= 25309; --中音si的频率为987.8hzwhen "01111111" => freq <= 23912; --高音do的频率为1045.5hzwhen "01111101" => freq <= 21282; --高音re的频率为1174.7hzwhen "01111011" => freq <= 18961; --高音mi的频率为1318.5hzwhen "01110111" => freq <= 17897; --高音fa的频率为1396.9hzwhen "01101111" => freq <= 15944; --高音sol的频率为1568hzwhen "01011111" => freq <= 14205; --高音la的频率为1760hzwhen "00111111" => freq <= 12605; --高音si的频率为1975.5hzwhen others => freq <= 0;end case;end process freq_process;beep <= beep_reg;end;--数码管静态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity static_segled isport(clk : in std_logic;data:out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0));end ;architecture fun of static_segled issignal num : std_logic_vector(3 downto 0);signal cnt : integer range 0 to 12499999 ;beginsel <= "00000000"; --静态显示,全部位选中process(clk)beginif clk'event and clk='1' then --每四秒改变一次数字if cnt=12499999 thencnt<=0;num<= num + 1;elsecnt<= cnt + 1 ;end if ;end if ;end process;process(num)begincase num iswhen "0000" => data<=x"c0"; -- // "0"when "0001" => data<=x"f9"; -- // "1"when "0010" => data<=x"a4"; -- // "2"when "0011" => data<=x"b0"; -- // "3"when "0100" => data<=x"99"; -- // "4"when "0101" => data<=x"92"; -- // "5"when "0110" => data<=x"82"; -- // "6"when "0111" => data<=x"f8"; -- // "7"when "1000" => data<=x"80"; -- // "8"when "1001" => data<=x"90"; -- // "9"when "1010" => data<=x"88"; -- // "a"when "1011" => data<=x"83"; -- // "b"when "1100" => data<=x"c6"; -- // "c"when "1101" => data<=x"a1"; -- // "d"when "1110" => data<=x"86"; -- // "e"when "1111" => data<=x"8e"; -- // "f"when others => data<=x"ff";end case;end process;end ;--数码管动态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity dynamic_segled isport(clk : in std_logic;data: out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0) );end ;architecture fun of dynamic_segled issignal cnt: integer range 0 to 62449;signal flip_led: integer range 0 to 7;beginprocess(clk)beginif clk'event and clk='1' then ----- 动态扫描if cnt=62499 thencnt<=0;flip_led<=flip_led+1; -- 数据改变elsecnt<=cnt + 1;end if ;end if ;end process;process(flip_led)begincase flip_led is ---译码显示when 0 =>sel<="01111111";data<=x"c0";when 1 =>sel<="10111111";data<=x"f9";when 2 =>sel<="11011111";data<=x"a4";when 3 =>sel<="11101111";data<=x"b0";when 4 =>sel<="11110111";data<=x"99";when 5 =>sel<="11111011";data<=x"92";when 6 =>sel<="11111101";data<=x"82";when 7 =>sel<="11111110";data<=x"f8";when others=>sel<="11111111";data<=x"ff"; end case;end process;end ;。

vhdl语言100例程序以下是100个关于VHDL语言的程序示例:1. 用VHDL编写一个计数器模块2. 用VHDL编写一个SR-Latch模块3. 用VHDL编写一个JK-Flip Flop模块4. 用VHDL编写一个D-Flip Flop模块5. 用VHDL编写一个T-Flip Flop模块6. 用VHDL编写一个复位计数器模块7. 用VHDL编写一个移位寄存器模块8. 用VHDL编写一个状态机模块9. 用VHDL编写一个MUX模块10. 用VHDL编写一个DeMUX模块11. 用VHDL编写一个加法器模块12. 用VHDL编写一个减法器模块13. 用VHDL编写一个乘法器模块14. 用VHDL编写一个除法器模块15. 用VHDL编写一个比较器模块16. 用VHDL编写一个位逻辑模块17. 用VHDL编写一个字逻辑模块18. 用VHDL编写一个数据选择器模块19. 用VHDL编写一个FIFO队列模块20. 用VHDL编写一个LIFO栈模块21. 用VHDL编写一个流水线模块22. 用VHDL编写一个中断控制器模块23. 用VHDL编写一个时钟分频器模块24. 用VHDL编写一个IO控制器模块25. 用VHDL编写一个SPI通信控制器模块26. 用VHDL编写一个I2C通信控制器模块27. 用VHDL编写一个UART通信控制器模块28. 用VHDL编写一个哈希函数模块29. 用VHDL编写一个随机数产生器模块30. 用VHDL编写一个CRC校验器模块31. 用VHDL编写一个AES加密算法模块32. 用VHDL编写一个DES加密算法模块33. 用VHDL编写一个SHA加密算法模块34. 用VHDL编写一个MD5加密算法模块35. 用VHDL编写一个RSA加密算法模块36. 用VHDL编写一个卷积滤波器模块37. 用VHDL编写一个峰值检测器模块38. 用VHDL编写一个平滑滤波器模块39. 用VHDL编写一个中值滤波器模块40. 用VHDL编写一个微处理器模块41. 用VHDL编写一个信号发生器模块42. 用VHDL编写一个信号采集器模块43. 用VHDL编写一个频率计算器模块44. 用VHDL编写一个相位计算器模块45. 用VHDL编写一个时序分析器模块46. 用VHDL编写一个正弦波产生器模块47. 用VHDL编写一个余弦波产生器模块48. 用VHDL编写一个数字滤波器模块49. 用VHDL编写一个数字信号处理器模块50. 用VHDL编写一个数字识别模块51. 用VHDL编写一个自动售货机模块52. 用VHDL编写一个二进制加法器模块53. 用VHDL编写一个二进制减法器模块54. 用VHDL编写一个二进制乘法器模块55. 用VHDL编写一个二进制除法器模块56. 用VHDL编写一个自然对数模块57. 用VHDL编写一个指数函数模块58. 用VHDL编写一个三角函数模块59. 用VHDL编写一个高斯滤波器模块60. 用VHDL编写一个激光传感器模块61. 用VHDL编写一个超声波传感器模块62. 用VHDL编写一个光电传感器模块63. 用VHDL编写一个温度传感器模块64. 用VHDL编写一个气压传感器模块65. 用VHDL编写一个陀螺仪模块67. 用VHDL编写一个电流传感器模块68. 用VHDL编写一个电容传感器模块69. 用VHDL编写一个磁场传感器模块70. 用VHDL编写一个通信电缆模块71. 用VHDL编写一个电源控制器模块72. 用VHDL编写一个电机控制器模块73. 用VHDL编写一个汽车控制器模块74. 用VHDL编写一个飞机控制器模块75. 用VHDL编写一个摄像头模块76. 用VHDL编写一个音频控制器模块77. 用VHDL编写一个扬声器控制器模块78. 用VHDL编写一个拨号器模块79. 用VHDL编写一个振动控制器模块80. 用VHDL编写一个压力控制器模块81. 用VHDL编写一个过滤器模块82. 用VHDL编写一个微波发射模块84. 用VHDL编写一个智能电表模块85. 用VHDL编写一个闹钟模块86. 用VHDL编写一个计时器模块87. 用VHDL编写一个时间戳模块88. 用VHDL编写一个脉冲宽度模块89. 用VHDL编写一个电路仿真模块90. 用VHDL编写一个电路控制模块91. 用VHDL编写一个电路测试模块92. 用VHDL编写一个电路优化模块93. 用VHDL编写一个电路布局模块94. 用VHDL编写一个电路验证模块95. 用VHDL编写一个数字信号发生器模块96. 用VHDL编写一个数字信号反演器模块97. 用VHDL编写一个数字信号滤波器模块98. 用VHDL编写一个数字信号加速器模块99. 用VHDL编写一个数字信号降噪器模块100. 用VHDL编写一个数字信号解调器模块VHDL语言是一种硬件描述语言,它用于描述数字电路和系统。

3.7 3-8译码器程序设计与仿真实验1 实验目的(1) 掌握3-8译码器的工作原理。

(2) 学会用VHDL语言进行逻辑电路设计。

2 实验原理3-8译码器是把一组三位二进制代码译成对应的八个输出信号,其三位二进制译码器状态如表3.7.1所示。

表3.7.1 三位二进制译码器状态表3 实验内容(1) 用VHDL语言编写3-8译码器源程序。

(2) 将源程序进行综合、优化及功能仿真。

(3)把适配后生成的下载,通过编程器向FPGA下载,进行硬件调试和验证。

4 实验预习与思考(1) 熟悉3-8译码器的工作原理。

(2) 若下载器件的显示电路是共阴极的,编程时译码输出的二进制代码怎样改变。

5 VHDL仿真实验(1)为此工程新建一个文件夹。

启动QuartusⅡ软件工作平台。

新建工程设计文件名为decoder.vhd。

在新建的VHDL模型窗口下编写的源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity decoder is --实体说明Port ( reset : in std_logic;input : in std_logic_vector(2 downto 0);output : out std_logic_vector(7 downto 0));end decoder;architecture Behavioral of decoder is --结构体beginprocess(reset,input) --进程beginif ( reset = '1') thenoutput <= "00000000";elsecase input iswhen "000" => output <= "00000001";when "001" => output <= "00000010";when "010" => output <= "00000100";when "011" => output <= "00001000";when "100" => output <= "00010000";when "101" => output <= "00100000";when "110" => output <= "01000000";when "111" => output <= "10000000";when others => output<= "00000000";end case;end if;end process;end Behavioral;(2) 创建工程及全程编译完成源代码输入后即可创建工程。

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

10线-4线优先编码器的VHDL描述LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY coder ISPORT ( din : IN STD_LOGIC_VECTOR(9 DOWNTO 0);output : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );END coder;ARCHITECTURE behav OF CODER ISSIGNAL SIN : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS (DIN)BEGINIF (din(9)='0') THEN SIN <= "1001" ;ELSIF (din(8)=‟0‟) THEN SIN <= "1000" ;ELSIF (din(7)='0') THEN SIN <= "0111" ;ELSIF (din(6)='0') THEN SIN <= "0110" ;ELSIF (din(5)='0') THEN SIN <= "0101" ;ELSIF (din(4)='0') THEN SIN <= "0100" ;ELSIF (din(3)='0') THEN SIN <= "0011" ;ELSIF (din(2)='0') THEN SIN <= "0010" ;ELSIF (din(1)='0') THEN SIN <= "0001" ;ELSE SIN <= “0000” ;END IF;END PROCESS ;Output <= sin ;END behav;计数器1 LIBRARY IEEE;2 USE IEEE.STD_LOGIC_1164.ALL;3 use IEEE.std_logic_unsigned.all;4 ENTITY CNT4 IS5 PORT ( CLK : IN STD_LOGIC ;6 Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)) ;7 END CNT4;8 ARCHITECTURE bhv OF CNT4 IS9 SIGNAL Q1 : STD_LOGIC_VECTOR(3 DOWNTO 0);10 BEGIN11 PROCESS (CLK) BEGIN12 IF RISING_EDGE(CLK) zhen13 IF Q1 < 15 THEN14 Q1 <= Q1 + 1 ;15 ELSE16 Q1 <= (OTHERS => '0');17 END IF;18 END IF;19 END PROCESS ;20 Q <= Q1;21 END bhv;228位分频器程序设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY PULSE ISPORT ( CLK : IN STD_LOGIC;D : IN STD_LOGIC_VECTOR (7 DOWNTO 0);FOUT : OUT STD_LOGIC );END;ARCHITECTURE one OF PULSE ISSIGNAL FULL : STD_LOGIC;BEGINP_REG: PROCESS(CLK)VARIABLE CNT8 : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINIF CLK‟EVENT AND CLK = …1‟ THENIF CNT8 = "11111111" THENCNT8 := D; --当CNT8计数计满时,输入数据D被同步预置给计数器CNT8FULL <= '1'; --同时使溢出标志信号FULL输出为高电平ELSE CNT8 := CNT8 + 1; --否则继续作加1计数FULL <= '0'; --且输出溢出标志信号FULL为低电平END IF;END IF;END PROCESS P_REG;P_DIV: PROCESS(FULL)VARIABLE CNT2 : STD_LOGIC;BEGINIF FULL'EVENT AND FULL = '1' THENCNT2 <= NOT CNT2; --如果溢出标志信号FULL为高电平,D触发器输出取反IF CNT2 = '1' THEN FOUT <= '1';ELSE FOUT <= '0';END IF;END IF;END PROCESS P_DIV;END;同步递增计数器USE IEEE.STD_LOGIC_1164.ALL;USE IEEE STD_LOGIC_UNSIGNED.ALL;ENTITY Exe_8 IS ;PORT ( CLK: IN STD_LOGIC;Q: BUFFER STD_LOGIC_VECTOR (7 DOWNTO 0));END Exe_8;ARCHITECTURE a OF Exe_8 ISBEGINPROCESS(CLK)VARIABLE QTEMP : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENQTEMP:=QTEMP+1;END IF;Q<=QTEMP;END PROCESS;END a;描述下列VHDL程序的逻辑功能:要求:指出输入、输出端子;实体功能说明;画出逻辑功能图。

第4章用VHDL程序实现常用逻辑电路4.1 组合逻辑电路设计4.1.1 基本逻辑门library ieee;use iee.std_logic_1164.all;entity jbm isport(a,b: in bit;f1,f2,f3,f4,f5,f: out bit);end jbm;architecture a of jbm isbeginf1<=a and b; --构成与门f2<=a or b; --构成或门f<=not a; --构成非门f3<=a nand b; --构成与非门f4<=a nor b; --构成异或门f5<=not(a xor b); --构成异或非门即同门end;4.1.2 三态门library ieee;use ieee.std_logic_1164.all;entity tri_s isport(enable: in std_logic;datain: in std_logic_vector(7 downto 0);dataout: out std_logic_vector(7 downto0));end tri_s;architecture bhv of tri_s isbeginprocess(enable,datain)beginif enable='1' thendataout<=datain;elsedataout<="ZZZZZZZZ";end if;end process;end bhv;4.1.3 3-8译码器library ieee;use ieee.std_logic_1164.all;entity decoder3_8 isport(a,b,c,g1,g2a,g2b: in std_logic;y: out std_logic_vector(7 downto 0));end decoder3_8;architecture a of decoder3_8 issignal dz:std_logic_vector(2 downto 0);begindz<=c&b&a;process (dz,g1,g2a,g2b)beginif(g1='1'and g2a='0'and g2b='0')thencase dz iswhen "000"=> y<="11111110";when "001"=> y<="11111101";when "010"=> y<="11111011";when "011"=> y<="11110111";when "100"=> y<="11101111";when "101"=> y<="11011111";when "110"=> y<="10111111";when "111"=> y<="01111111";when others=>y<="XXXXXXXX";end case;elsey<="11111111";end if;end process;4.1.4 优先编码器library ieee;use ieee.std_logic_1164.allentity coder isport(din: in std_logic_vector(0 to 7);output: out std_logic_vector(0 to 2));end coder;architecture behave of coder issignal sint: std_logic_vevtor(4 downto 0);beginprocess(din)beginif (din(7)='0') thenoutput <= "000" ;elsif (din(6)='0') thenoutput <= "100" ;elsif (din(5)='0') thenoutput <= "010" ;elsif (din(4)='0') thenoutput <= "110" ;elsif (din(3)='0') thenoutput <= "001" ;elsif (din(2)='0') thenoutput <= "101" ;elsif (din(1)='0') thenoutput <= "011" ;elseoutput <= "111" ;end if;end process;end behav;4.1.5 7段码译码器library ieee;use ieee.std_logic_1164.allentity decl7s isport (a: in std_logic_vector (3 downto 0);led7s: out std_logic_vector(6 downto 0));end decl7s;architecture behave of decl7s isbeginprocess(a)begincase a iswhen "0000" => led7s <= "0111111" ;when "0001" => led7s <= "0000110" ;when "0010" => led7s <= "1011011" ;when "0011" => led7s <= "1001111" ;when "0100" => led7s <= "1100110" ;when "0101" => led7s <= "1101101" ;when "0110" => led7s <= "1111101" ;when "0111" => led7s <= "0000111" ;when "1000" => led7s <= "1111111" ;when "1001" => led7s <= "1101111" ;when "1010" => led7s <= "1110111" ;when "1011" => led7s <= "1111100" ;when "1100" => led7s <= "0111001" ;when "1101" => led7s <= "1011110" ;when "1110" => led7s <= "1111001" ;when "1111" => led7s <= "1110001" ;when others => null;end case;end process;end behave;4.1.6二-十进制BCD译码器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity bcdymq isport(din : in integer range 15 downto 0;a,b : out integer range 9 downto 0);end;architecture fpq1 of bcdymq isbeginp1: process(din)beginif din<10 thena< =din;b< =0;elsea< =din-10;end if;end process p1;end;4.1.7 多位加(减)法器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity jianfaqi isport(a,b : in std_logic_vector(0 to 3);c0: in std_logic;c1: out std_logic;d : out std_logic_vector(0 to 3));end;architecture a of jianfaqi isbeginprocessbeginif a>b+c0 thend<=a-(b+c0);c1<='0';elsec1<='1';d<=("10000")-(b+c0-a);end if;end process ;end ;4.2 时序逻辑电路设计4.2.1 触发器RS触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity rsff isport(r,s,clk:in std_logic;q,qb:buffer std_logic);end rsff;architecture rsff_art of rsff issignal q_s,qb_s:std_logic;beginprocess(clk,r,s)beginif (clk'event and clk='1') thenif (s='1' and r='0') thenq_s<='0' ;qb_s<='1' ;elsif (s='0' and r='1') thenq_s <= '1' ;qb_s <= '0' ;elsif (s='0' and r='0') thenq_s <= q_s;qb_s <= qb_s;end if;q_s <= q_s;qb_s <= qb_s;end process;end rsff_art;同步复位D触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity syndff isport(d,clk,reset:in std_logic;q,qb:out std_logic);end syndff;architecture dff_art of syndff isbeginprocess(clk)beginif (clk'event and clk='1') thenif (reset='0') thenq<='0';qb<='1';elseq<=d;qb<=not q;end if;end if;end process;end dff_art;JK触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity asynjkff isport(j,k,clk,set.reset:in std_logic;q,qb:out std_logic);end asynjkff;architecture jkff_art of asynjkff issingal q_s,qb_s:std_logic;beginprocess(clk,set,reset)beginif (set='0' and reset='1' ) thenq_s<='1';qb_s<='0';elsif (set='1' and reset='0' ) thenq_s<='0';qb_s<='1';elsif (clk'event and clk='1') thenif (j='0' and k='1' ) thenq_s<='0';qb_s<='1';elsif (j='1' and k='0' ) thenq_s<='1';qb_s<='0';elsif (j='1' and k='1' ) thenq_s<=not q_s;qb_s<=not qb_s;end if;end if;q<= q_s;qb<= qb_s;end process;end jkff_art;T触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity tff isport(t,clk: in std_logic;q: out std_logic);end;architecture tff_art of tff issignal q_temp: std_logic;beginp1:process(clk)beginif rising_edge(clk) thenif t='1' then --当T=1时T触发器具有2分频的功能q_temp<=not q_temp;elseq_temp<=q_temp;end if;end if;q<=q_temp;end process;q<=q_temp;end tff_art;4.2.2计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt4 ISport( clk: in std_logic;q: out std_logic_vector(3 downto 0));end cnt4;architecture behave of cnt4 issignal q1: std_logic_vector(3 downto 0);beginprocess(clk)beginif (clk'event and clk = '1') thenq1<=q1+1;end if;end process;q<=q1;一般计数器设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport( clk,rst,en,updown: in std_logic;cq: out std_logic_vector(3 downto 0));end cnt10;architecture behave of cnt10 isbeginprocess(clk,rst,en,updown)variable cqi:std_logic_vector(3 downto 0);beginif rst='1' thencqi:=(others=>'0'); --计数器异步复位elsif (clk'event and clk = '1') then --检测时钟上升沿if en='1'then --检测是否允许计数(同步使能)if updown='0'thenif cqi<9 thencqi:=cqi+1; --允许计数,检测是否小于9elsecqi:=(others=>'0'); --大于9,计数值清零end if;elseif cqi>0 thencqi:=cqi-1; --检测是否大于0elsecqi:=(others=>'1'); ---否则,计数值置1end if;end if;end if;end if;cq<=cqi; --将计数值向端口输出end process;end behave;4.2.3 分频器library ieee;use std_logic_1164.all;use std_logic_unsigned.all;entity freq1 isport(clk: in std_logic;d: in std_logic_vector(7 downto 0);fout: out std_logic);end;architecture one of dvf issignal full: std_logic;beginp_reg:process(clk)variable cnt8: std_logic_vector(7 downto 0);if clk'event and clk='1'then --检测时钟上升沿if cnt8=''11111111'' thencnt8:=d; --当CNT8计数计满时,输入数据D被同步预置给计数器CNT8full<='1';--同时使溢出标志信号FULL输出为高电平elsecnt8:=cnt8+1;--否则继续作加1计数full<='0'; --且输出溢出标志信号FULL为低电平end if;end if;end process p_reg;p_div:process(full)variable cnt2: std_logic;beginif full'event and full='1' thencnt2:=not cnt2; --如果溢出标志信号FULL为高电平,T触发器输出取反if cnt2='1'thenfout<='1';elsefout<='0';end if;end if;end process p_div;end;4.2.4 移位寄存器library ieee;use ieee.std_logic_1164.all;entity shift isport(clk,c0: in std_logic;--时钟和进位输入md: in std_logic_vector(2 downto 0);--移位模式控制字d: in std_logic_vector(7 downto 0);--待加载移位的数据qb: out std_logic_vector(7 downto 0);--移位数据输出cn: out std_logic);--进位输出end;architecture behave of shift issignal reg: std_logic_vector(7 downto 0);signal cy: std_logic;beginprocess(clk,md,c0)beginif clk'event and clk='1' thencase md iswhen "001" => reg (0) <= c0 ;reg (7 downto 1) <= reg (6 downto 0);cy <= reg (7); --带进位循环左移when "010" => reg (0) <= reg (7);reg (7 downto 1) <= reg (6 downto 0); --自循环左移when "011" => reg (7) <= reg (0);reg (6 downto 0) <= reg (7 downto 1); --自循环右移when "100" => reg (7) <= C0 ;reg (6 downto 0) <= reg (7 downto 1);cy <= reg (0); --带进位循环右移when "101" => reg (7 downto 0) <= d(7 downto 0); --加载待移数when others => reg<= reg ; cy<= cy ; --保持end case;end if;end process;qb(7 downto 0) <= reg (7 downto 0); cn <= cy; --移位后输出end behav;4.3 状态机逻辑电路设计4.3.1 一般状态机设计library ieee;use ieee.std_logic_1164.all;entity s_machine isport ( clk,reset : in std_logic;state_inputs : in std_logic_vector(0 to1);comb_outputs : out integer range 0 to 15 );end s_machine;architecture behv of s_machine istype fsm_st is (s0, s1, s2, s3); --数据类型定义,状态符号化signal current_state, next_state: fsm_st; --将现态和次态定义为新的数据类型beginreg: process(reset,clk) --主控时序进程beginif reset = '1' thencurrent_state <= s0; --检测异步复位信号elsif clk='1' and clk'event thencurrent_state <= next_state;end if;end process;com:process(current_state, state_inputs) --主控组合进程begincase current_state iswhen s0 => comb_outputs<= 5;if state_inputs = "00" thennext_state<=s0;elsenext_state<=s1;end if;when s1 => comb_outputs<= 8;if state_inputs = "00" thennext_state<=s1;elsenext_state<=s2;end if;when s2 => comb_outputs<= 12;if state_inputs = "11" thennext_state <= s0;elsenext_state <= s3;end if;when s3 => comb_outputs <= 14;if state_inputs = "11" thennext_state <= s3;elsenext_state <= s0;end if;end case;end process;end behv;4.3.2状态机的应用library ieee;use ieee.std_logic_1164.all;entity asm_led isport(clk,clr : in std_logic;led1,led2,led3:out std_logic);end;architecture a of asm_led istype states is (s0,s1,s2,s3,s4,s5); --对状态机的状态声明signal q: std_logic_vector( 0 to 2);signal state : states;beginp1: process(clk,clr)beginif(clr='0')thenstate<=s0;elsif (clk'event and clk='1') thencase state iswhen s0=> state <=s1;when s1=> state <=s2;when s2=> state <=s3;when s3=> state <=s4;when s4=> state <=s5;when s5=> state <=s0;when others => state<=s0;end case;end if;end process p1;p2: process (clr,state)beginif(clr='0') thenled1<='0';led2<='0';led3<='0';elsecase state iswhen s0=> led1<='1';led2<='0';led3<='0';when s1=> led1<='0';led2<='1';led3<='0';when s2=> led1<='0';led2<='1';led3<='0';when s3=> led1<='0';led2<='0';led3<='1';when s4=> led1<='0';led2<='0';led3<='1';when s5=> led1<='0';led2<='0';led3<='1';when others => null;end case;end if;end process p2;end ;第6章EDA仿真技术应用实例6.1带使能和片选端的16:4线优先编码器设计子模块设计源代码:library ieee;use ieee.std_logic_1164.all;entity pencoder isport(d:in std_logic_vector(7 downto 0);ei:in std_logic; --ei:enable inputgs,eo:out bit; --gs:chip select output;eo:enable outputq2,q1,q0:out std_logic);end pencoder;architecture encoder of pencoder isbeginprocess(d)beginif(d(0)='0' and ei='0')thenq2<='1';q1<='1';q0<='1';gs<='0';eo<='1';elsif(d(1)='0' and ei='0')thenq2<='1';q1<='1';q0<='0';gs<='0';eo<='1';elsif(d(2)='0' and ei='0')thenq2<='1';q1<='0';q0<='1';gs<='0';eo<='1';elsif(d(3)='0' and ei='0')thenq2<='1';q1<='0';q0<='0';gs<='0';eo<='1';elsif(d(4)='0' and ei='0')thenq2<='0';q1<='1';q0<='1';gs<='0';eo<='1';elsif(d(5)='0' and ei='0')thenq2<='0';q1<='1';q0<='0';gs<='0';eo<='1';elsif(d(6)='0' and ei='0')thenq2<='0';q1<='0';q0<='1';gs<='0';eo<='1';elsif(d(7)='0' and ei='0')then --d7 prioty encoderq2<='0';q1<='0';q0<='0';gs<='0';eo<='1';elsif(ei='1')thenq2<='1';q1<='0';q0<='1';gs<='1';eo<='1';elsif(d="11111111" and ei='0')thenq2<='1';q1<='1';q0<='1';gs<='1';eo<='0';end if;end process;end encoder;6.27段显示译码器设计译码器设计源代码:library ieee;use ieee.std_logic_1164.all;entity decoder47 isport(lt,ibr,ib_ybr:in bit;a: in std_logic_vector(3 downto 0);y:out std_logic_vector(6 downto 0));end decoder47;architecture art of decoder47 isbeginprocess(lt,ibr,ib_ybr,a)variable s: std_logic_vector(3 downto 0);begins:=a(3)&a(2)&a(1)&a(0);if lt='0' and ib_ybr='1' theny<="1111111"; --检查七段显示管是否正常elsif ibr='0' and a="0000" theny<="0000000";elsecase s iswhen"0000"=>y<="1111110"; --7Ewhen"0001"=>y<="0110000"; --30when"0010"=>y<="1101101"; --6Dwhen"0011"=>y<="1111001"; --79when"0100"=>y<="0110011"; --33when"0101"=>y<="1011011"; --5Bwhen"0110"=>y<="0011111"; --5Fwhen"0111"=>y<="1110000"; --70when"1000"=>y<="1111111"; --7Ewhen"1001"=>y<="1110011"; --7Bwhen"1010"=>y<="0001101"; --0Dwhen"1011"=>y<="0011001"; --19when"1100"=>y<="0100011"; --23when"1101"=>y<="1001011"; --4Bwhen"1110"=>y<="0001111"; --0Fwhen"1111"=>y<="0000000";end case;end if;end process;end art;6.3带异步清零端的12位二进制全加器设计子模块源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder4b isport(clr,cin: in std_logic;a,b: in std_logic_vector(3 downto 0);s: out std_logic_vector(3 downto 0);cout:out std_logic);end adder4b;architecture art of adder4b issignal sint:std_logic_vector(4 downto 0);signal aa,bb:std_logic_vector(4 downto 0);beginprocess(clr)beginif clr='1'thensint<="00000";elseaa<='0'&a;bb<='0'&b;sint<=aa+bb+cin;end if;s<=sint(3 downto 0);cout<=sint(4);end process;end art;顶层模块设计源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder12b isport(clr,cin: in std_logic;a,b: in std_logic_vector(11 downto 0);s: out std_logic_vector(11 downto 0);cout:out std_logic);end adder12b;architecture art of adder12b iscomponent adder4b isport(clr,cin: in std_logic;a,b: in std_logic_vector(3 downto 0);s: out std_logic_vector(3 downto 0);cout:out std_logic);end component;signal carry_out1:std_logic;signal carry_out2:std_logic;beginu1:adder4b port map(clr=>clr,cin=>cin,a=>a(3 downto 0),b=>b(3 downto 0),s=>s(3 downto 0),cout=>carry_out1);u2:adder4b port map(clr=>clr,cin=>carry_out1,a=>a(7 downto 4),b=>b(7 downto 4),s=>s(7 downto 4),cout=>carry_out2);u3:adder4b port map(clr=>clr,cin=>carry_out2,a=>a(11 downto 8),b=>b(11 downto 8),s=>s(11 downto 8),cout=>cout);end art;6.4 带异步清零/置位端的JK触发器设计带异步清零/置位端的JK触发器源程序如下:library ieee;use ieee.std_logic_1164.all;entity jkff_logic isport(j,k,clk,clr,set:in std_logic;q:out std_logic);end jkff_logic;architecture art of jkff_logic issignal q_s:std_logic;beginprocess(clk,clr,set,j,k)beginif set='0' thenq_s<='1'; --异步置位elsif clr='1' thenq<='0'; --异步复位elsif clk'event and clk='1' thenif (j='0') and (k='1') thenq_s<='0';elsif(j='1') and (k='0') thenq_s<='1';elsif(j='1') and (k='1') thenq_s<=not q_s;end if;end if;q<=q_s;end process;end art;6.5 4位锁存器设计子模块设计源代码:library ieee;use ieee.std_logic_1164.all;entity latch1b isport(d: in std_logic;ena: in std_logic; --使能端q: out std_logic);end latch1b;architecture art of latch1b isbeginprocess(d,ena)beginif ena='1' thenq<=d;end if;end process;end art;元件声明程序包设计源代码:library ieee;use ieee.std_logic_1164.all;package my_package iscomponent latch1port(d:in std_logic;ena:in std_logic;q: out std_logic);end component;end;顶层模块设计源代码:library ieee;use ieee.std_logic_1164.all;use work.my_package.all; --使用用户自定义的程序包entity latch4d isport(d: in std_logic_vector(3 downto 0);oen: in bit;q:out std_logic_vector(3 downto 0));end latch4d;architecture one of latch4d issignal sig_save:std_logic_vector(3 downto 0);begingetlatch:for n in 0 to 3 generate --用for_generate语句循环例化4个1位锁存器latchx:latch1 port map(d(n),g,sig_save(n)); --关联end generate;q<=sig_save when oen='0'else"ZZZZ";end one;6.6 32进制多样型计数器设计(1)32进制同步加法计数器源程序32进制同步加法计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_plus isport(clk,clr:in std_logic;dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_plus issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr,)beginif clr='1'thend1<=(others=>'0');d0<="0000"; --同步清零elsif clk'event and clk='1' thenif(d1=3 and d0=1)thend1<="0000";d0<="0000"; --计数到32时清零elsif(d0=1) thend0<="0000";d1<=d1+1;elsed0<=d0+1;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(2)32进制同步减法计数器源程序32进制同步减法计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_sub isport(clk,clr:in std_logic;dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_sub issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr)beginif clr='1' thend1<="0000";d0<="0000"; --异步清零elsif clk'event and clk='1' thenif(d1=0 and d0=0) thend1<="0011";d0<="0001"; --设定容量31elsif(d0=0) thend0<="0001";d1<=d1-1;elsed0<=d0-1;d1<=d1;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(3)32进制同步可逆计数器源程序32进制同步可逆计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_reversible isport(clk,clr,s:in std_logic; --s=1加法计数,s=0减法计数dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_reversible issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr,s)beginif clr='1'thend1<="0000";d0<="0000"; --异步清零elsif (clk'event and clk='1' )thenif s='1' thenif(d1=3 and d0=1) thend1<="0000";d0<="0000"; --计数到31时清零elsif(d0=1) thend0<="0000";d1<=d1+1;else d0<=d0+1;end if;elsif s='0' thenif(d1=0 and d0=0)thend1<="0011";d0<="0001"; --设定容量31elsif(d0=0) thend0<="0001";d1<=d1-1;elsed0<=d0-1;d1<=d1;end if;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(4)32进制异步加法计数器源程序32进制异步加法计数器源程序如下:①子模块D触发器源程序设计。