VHDL语言及程序设计

- 格式:ppt

- 大小:687.00 KB

- 文档页数:65

vhdl设计实验报告VHDL设计实验报告引言VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和验证。

本实验旨在通过设计一个简单的电路来熟悉VHDL语言的基本语法和设计流程。

一、实验背景数字电路是现代电子系统的基础,而VHDL则是描述和设计数字电路的重要工具。

VHDL可以帮助工程师们以一种形式化的语言来描述电路的功能和结构,从而实现电路的模拟和验证。

二、实验目的本实验的目的是通过使用VHDL语言设计一个简单的电路,加深对VHDL语言的理解,并掌握基本的电路设计流程。

三、实验步骤1. 确定电路功能在设计电路之前,首先需要明确电路的功能。

本实验中,我们选择设计一个4位加法器电路。

2. 设计电路结构根据电路功能的要求,设计电路的结构。

在本实验中,我们需要设计一个4位加法器,因此需要使用4个输入端口和一个输出端口。

3. 编写VHDL代码使用VHDL语言编写电路的描述代码。

在代码中,需要定义输入和输出端口的类型和位宽,并实现电路的功能。

4. 进行仿真使用仿真工具对设计的电路进行仿真,以验证电路的功能是否符合预期。

通过输入不同的测试数据,观察输出是否正确。

5. 下载到FPGA开发板将设计好的电路代码下载到FPGA开发板上进行验证。

通过连接输入信号和观察输出信号,验证电路在实际硬件上的运行情况。

四、实验结果与分析经过仿真和实际验证,我们设计的4位加法器电路在功能上符合预期。

输入不同的数据进行加法运算时,输出结果都正确。

五、实验总结通过本次实验,我们深入了解了VHDL语言的基本语法和设计流程。

通过设计一个简单的电路,我们掌握了VHDL的应用方法,并通过仿真和实际验证,加深了对电路设计的理解。

六、实验心得本实验让我对VHDL语言有了更深入的认识。

通过实际操作,我更加熟悉了VHDL的编写和仿真流程。

VHDL语言教程VHDL是一种硬件描述语言,用于描述数字电路和系统,并进行硬件的设计和仿真。

它被广泛应用于数字电路设计、嵌入式系统开发和可编程逻辑控制器等领域。

本教程将介绍VHDL语言的基本概念和语法,帮助您了解和学习这门强大的硬件描述语言。

一、VHDL概述VHDL是Very High Speed Integrated Circuit Hardware Description Language的缩写,意为高速集成电路硬件描述语言。

它是一种硬件描述语言,用于描述数字电路和系统。

与传统的电路设计方法相比,使用VHDL可以更加方便、高效地进行电路设计和测试。

1.VHDL的起源和发展VHDL最早由美国国防部为了解决数字电路设计复杂、效率低下的问题而研发。

后来,VHDL成为了一种IEEE标准(IEEE1076)并被广泛应用于数字电路设计和仿真。

2.VHDL的优点VHDL具有以下几个优点:-高级抽象:VHDL提供了一种高级描述电路的方法,使得设计者能够更加方便地表达复杂的电路结构和行为。

-可重用性:VHDL支持模块化设计,使得设计者可以将电路的不同部分进行抽象和封装,提高了电路的可重用性。

-高效仿真:VHDL可以进行高效的电路仿真和测试,有助于验证电路设计的正确性和可靠性。

-灵活性:VHDL可以应用于各种不同类型和规模的电路设计,从小规模的数字逻辑电路到大规模的系统级设计。

二、VHDL语法和基本概念1.VHDL的结构VHDL程序由程序单元(unit)组成,程序单元是VHDL描述的最小单元。

程序单元包括实体(entity)、结构(architecture)、过程(process)和包(package)等。

2. 实体(entity)实体是VHDL描述电路模块的一个部分,包括输入输出端口、信号声明和实体标识符等。

3. 结构(architecture)结构描述了实体的具体电路结构和行为,包括组件声明、信号赋值和行为描述等。

VHDL语言VHDL(VHSIC Hardware Description Language)是用于描述数字电路和系统的硬件描述语言,是一种标准化的硬件描述语言,广泛应用于数字电路设计和电子系统设计领域。

VHDL语言是一种强大的工具,可以帮助工程师描述复杂的数字电路,并进行仿真和综合。

它可以描述电路的结构、功能和时序行为,是一种形式化的语言,能够准确地描述电路的行为特性,有助于工程师在设计阶段发现和解决问题。

VHDL语言的基本概念实体(Entity)•实体描述了电路的接口和功能,可以看作是一种抽象的模块。

•实体中定义了输入输出端口,以及对应的信号类型和位宽。

•实体可以包含多个体系结构(Architecture)。

体系结构(Architecture)•体系结构描述了实体的具体实现,定义了实体的行为。

•体系结构中包含了处理逻辑、时序行为以及信号的赋值。

•体系结构可以描述电路的功能和行为。

信号(Signal)•信号是VHDL语言中的基本数据类型,用于在电路中传递信息。

•信号可以是标量(Scalar)或矢量(Vector),可以是时序或组合。

•信号的赋值可以是同步的或异步的。

过程(Process)•过程描述了VHDL中的行为,通常用于描述组合逻辑或时序逻辑。

•过程中可以包含逻辑运算、条件语句、循环语句等。

•过程中的代码在仿真或综合时会被执行。

VHDL语言的应用VHDL语言主要用于数字电路设计、电子系统设计、FPGA设计等领域。

工程师可以使用VHDL语言描述数字电路的结构和行为,进行仿真和综合,快速验证设计的正确性。

VHDL语言的应用领域包括但不限于:•数字电路设计•通信系统设计•控制系统设计•图像处理系统设计•嵌入式系统设计VHDL语言在电子设计领域具有广泛的应用前景,可以帮助工程师快速高效地设计数字电路系统,并满足不同应用场景的需求。

总结VHDL语言是一种强大的硬件描述语言,可以帮助工程师描述数字电路的结构和行为,进行仿真和综合,快速验证设计的正确性。

vhdl语言100例程序以下是100个关于VHDL语言的程序示例:1. 用VHDL编写一个计数器模块2. 用VHDL编写一个SR-Latch模块3. 用VHDL编写一个JK-Flip Flop模块4. 用VHDL编写一个D-Flip Flop模块5. 用VHDL编写一个T-Flip Flop模块6. 用VHDL编写一个复位计数器模块7. 用VHDL编写一个移位寄存器模块8. 用VHDL编写一个状态机模块9. 用VHDL编写一个MUX模块10. 用VHDL编写一个DeMUX模块11. 用VHDL编写一个加法器模块12. 用VHDL编写一个减法器模块13. 用VHDL编写一个乘法器模块14. 用VHDL编写一个除法器模块15. 用VHDL编写一个比较器模块16. 用VHDL编写一个位逻辑模块17. 用VHDL编写一个字逻辑模块18. 用VHDL编写一个数据选择器模块19. 用VHDL编写一个FIFO队列模块20. 用VHDL编写一个LIFO栈模块21. 用VHDL编写一个流水线模块22. 用VHDL编写一个中断控制器模块23. 用VHDL编写一个时钟分频器模块24. 用VHDL编写一个IO控制器模块25. 用VHDL编写一个SPI通信控制器模块26. 用VHDL编写一个I2C通信控制器模块27. 用VHDL编写一个UART通信控制器模块28. 用VHDL编写一个哈希函数模块29. 用VHDL编写一个随机数产生器模块30. 用VHDL编写一个CRC校验器模块31. 用VHDL编写一个AES加密算法模块32. 用VHDL编写一个DES加密算法模块33. 用VHDL编写一个SHA加密算法模块34. 用VHDL编写一个MD5加密算法模块35. 用VHDL编写一个RSA加密算法模块36. 用VHDL编写一个卷积滤波器模块37. 用VHDL编写一个峰值检测器模块38. 用VHDL编写一个平滑滤波器模块39. 用VHDL编写一个中值滤波器模块40. 用VHDL编写一个微处理器模块41. 用VHDL编写一个信号发生器模块42. 用VHDL编写一个信号采集器模块43. 用VHDL编写一个频率计算器模块44. 用VHDL编写一个相位计算器模块45. 用VHDL编写一个时序分析器模块46. 用VHDL编写一个正弦波产生器模块47. 用VHDL编写一个余弦波产生器模块48. 用VHDL编写一个数字滤波器模块49. 用VHDL编写一个数字信号处理器模块50. 用VHDL编写一个数字识别模块51. 用VHDL编写一个自动售货机模块52. 用VHDL编写一个二进制加法器模块53. 用VHDL编写一个二进制减法器模块54. 用VHDL编写一个二进制乘法器模块55. 用VHDL编写一个二进制除法器模块56. 用VHDL编写一个自然对数模块57. 用VHDL编写一个指数函数模块58. 用VHDL编写一个三角函数模块59. 用VHDL编写一个高斯滤波器模块60. 用VHDL编写一个激光传感器模块61. 用VHDL编写一个超声波传感器模块62. 用VHDL编写一个光电传感器模块63. 用VHDL编写一个温度传感器模块64. 用VHDL编写一个气压传感器模块65. 用VHDL编写一个陀螺仪模块67. 用VHDL编写一个电流传感器模块68. 用VHDL编写一个电容传感器模块69. 用VHDL编写一个磁场传感器模块70. 用VHDL编写一个通信电缆模块71. 用VHDL编写一个电源控制器模块72. 用VHDL编写一个电机控制器模块73. 用VHDL编写一个汽车控制器模块74. 用VHDL编写一个飞机控制器模块75. 用VHDL编写一个摄像头模块76. 用VHDL编写一个音频控制器模块77. 用VHDL编写一个扬声器控制器模块78. 用VHDL编写一个拨号器模块79. 用VHDL编写一个振动控制器模块80. 用VHDL编写一个压力控制器模块81. 用VHDL编写一个过滤器模块82. 用VHDL编写一个微波发射模块84. 用VHDL编写一个智能电表模块85. 用VHDL编写一个闹钟模块86. 用VHDL编写一个计时器模块87. 用VHDL编写一个时间戳模块88. 用VHDL编写一个脉冲宽度模块89. 用VHDL编写一个电路仿真模块90. 用VHDL编写一个电路控制模块91. 用VHDL编写一个电路测试模块92. 用VHDL编写一个电路优化模块93. 用VHDL编写一个电路布局模块94. 用VHDL编写一个电路验证模块95. 用VHDL编写一个数字信号发生器模块96. 用VHDL编写一个数字信号反演器模块97. 用VHDL编写一个数字信号滤波器模块98. 用VHDL编写一个数字信号加速器模块99. 用VHDL编写一个数字信号降噪器模块100. 用VHDL编写一个数字信号解调器模块VHDL语言是一种硬件描述语言,它用于描述数字电路和系统。

EDA技术-VHDL-四选⼀数据选择器程序设计与仿真实验四选⼀数据选择器程序设计与仿真实验1 实验⽬的(1) 熟悉在QuartusⅡ软件平台上建⽴⼯作库⽂件和编辑设计⽂件的⽅法。

(2) 熟悉创建⼯程⽂件⽅法。

(3) 熟悉编译前设置和启动全程编译设置的⽅法。

(4) 熟悉波形编辑器的使⽤⽅法(5) 熟悉在QuartusⅡ软件平台上对设计进⾏仿真的操作全过程(6) 会⽤VHDL语⾔设计⼀个四选⼀数据选择器。

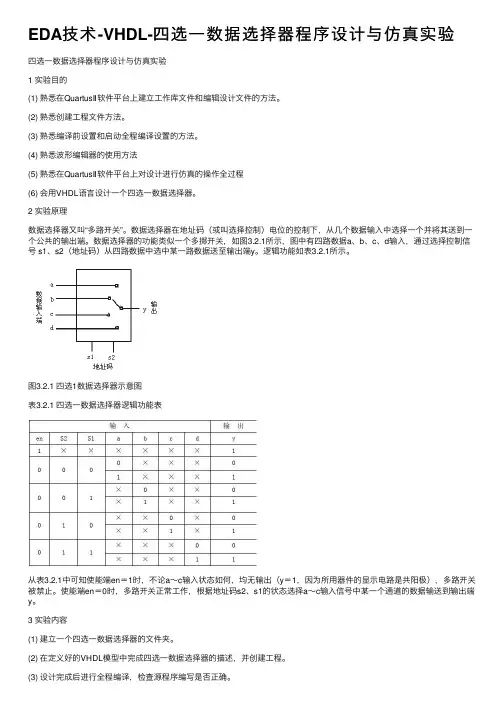

2 实验原理数据选择器⼜叫“多路开关”。

数据选择器在地址码(或叫选择控制)电位的控制下,从⼏个数据输⼊中选择⼀个并将其送到⼀个公共的输出端。

数据选择器的功能类似⼀个多掷开关,如图3.2.1所⽰,图中有四路数据a、b、c、d输⼊,通过选择控制信号 s1、s2(地址码)从四路数据中选中某⼀路数据送⾄输出端y。

逻辑功能如表3.2.1所⽰。

图3.2.1 四选1数据选择器⽰意图表3.2.1 四选⼀数据选择器逻辑功能表从表3.2.1中可知使能端en=1时,不论a~c输⼊状态如何,均⽆输出(y=1,因为所⽤器件的显⽰电路是共阳极),多路开关被禁⽌。

使能端en=0时,多路开关正常⼯作,根据地址码s2、s1的状态选择a~c输⼊信号中某⼀个通道的数据输送到输出端y。

3 实验内容(1) 建⽴⼀个四选⼀数据选择器的⽂件夹。

(2) 在定义好的VHDL模型中完成四选⼀数据选择器的描述,并创建⼯程。

(3) 设计完成后进⾏全程编译,检查源程序编写是否正确。

(4) 建⽴波形编辑⽂件并对输⼊波形进⾏编辑。

(5) 启动仿真器进⾏仿真,并分析仿真结果。

4 实验预习与思考(1) 进⼀步学习在QuartusⅡ软件平台上建⽴⼯作库⽂件和编辑设计⽂件的⽅法。

(2) 进⼀步学习建⽴波形编辑器⽂件编辑输⼊波形的⽅法。

(3) VHDL语⾔的结构体在整个程序中起什么作⽤。

5 VHDL仿真实验(1)新建⼀个⽂件夹。

本例中⽂件夹名为mux。

(2)输⼊源程序,打开计算机桌⾯上图标。

《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

VHDL硬件描述语言与数字逻辑电路设计第三版课程设计本次课程设计旨在帮助大家深入理解VHDL硬件描述语言和数字逻辑电路设计的相关知识,提高大家的实践能力和设计能力。

本文将对课程设计的要求和实现方法进行详细说明。

课程设计要求本次课程设计要求大家完成一个基于VHDL的数字逻辑电路设计,包括以下要求:1.手动编写VHDL程序,对指定的数字电路进行仿真分析,并输出相应的波形图。

2.设计一个数字电路,要求该电路可完成特定的逻辑功能,例如加法器、多路选择器等。

3.基于现实的场景需求,完成一个实际的数字电路设计。

例如,实现一个音乐播放器控制器、机器人控制器等。

设计步骤步骤一:了解VHDL语言和数字逻辑电路设计原理在进行数字电路设计之前,需要先理解VHDL语言和数字逻辑电路设计原理。

VHDL语言是一种硬件描述语言,主要用于描述数字逻辑电路。

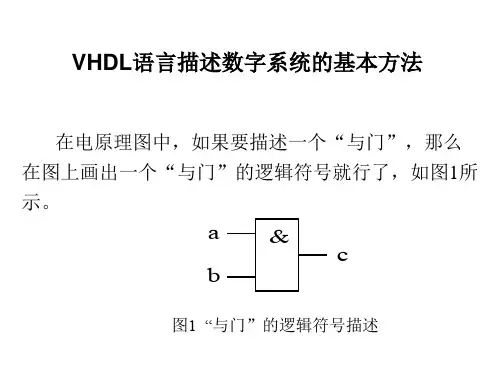

数字逻辑电路由基本的逻辑单元组成,包括与门、或门、非门等,通过组合这些逻辑单元可以实现更复杂的逻辑电路设计。

步骤二:选择仿真工具选择一款仿真工具进行仿真分析。

常见的仿真工具有ModelSim、Xilinx ISE 等。

步骤三:编写VHDL程序编写VHDL程序,对指定的数字电路进行仿真分析。

根据实际需要,可以选择不同的VHDL语言结构进行编写。

步骤四:仿真分析在仿真工具中进行仿真分析,根据VHDL程序模拟出相应的波形图。

步骤五:设计数字电路基于数字逻辑电路设计原理,设计出特定的数字电路。

需要首先确定电路所需要的逻辑功能,然后根据这个功能设计出合适的电路。

步骤六:实现实际场景需求参考现实的场景需求,设计出一个实际的数字电路,并进行调试测试。

VHDL程序编写规范在编写VHDL程序时,需要遵循一定的编写规范,以保证程序的可读性和可维护性。

1.命名规范:变量和信号的命名应具有较好的描述性,易于理解和记忆。

2.缩进规范:代码缩进应该统一,便于代码的阅读和理解。

3.注释规范:代码中应加入必要的注释,解释各个模块的功能和作用。

VHDL的设计流程,它主要包括以下几个步骤:1. 文本编辑: 用任何文本编辑器都可以进行,也可以用专用的HDL编辑环境。

2. 功能仿真: 将文件调入HDL仿真软件进行功能仿真,检查逻辑功能是否正确。

3. 逻辑综合: 将源文件调入逻辑综合软件进行综合,即把语言综合成最简的布尔表达式。

4. 时序仿真: 需要利用在布局布线中获得的精确参数,用仿真软件验证电路的时序。

5. 器件编程: 对使用的元件可以进行编程。

秒表设计一、设计实验目的在QuartusII软件平台上,熟练运用VHDL语言,完成数字时钟设计的软件编程、编译、综合、仿真,使用EDA实验箱,实现数字秒表的硬件功能。

二、设计实验说明及要求1、数字秒表主要由:分频器、扫描显示译码器、一百进制计数器、六十进制计数器(或十进制计数器与6进制计数器)、十二进制计数器(或二十四进制计数器)电路组成。

在整个秒表中最关键的是如何获得一个精确的100HZ计时脉冲,除此之外,数字秒表需有清零控制端,以及启动控制端、保持保持,以便数字时钟能随意停止及启动。

2、数字秒表显示由时(12或24进制任选)、分(60进制)、秒(60进制)、百分之一秒(一百进制)组成,利用扫描显示译码电路在八个数码管显示。

3、能够完成清零、启动、保持(可以使用键盘或拨码开关置数)功能。

4、时、分、秒、百分之一秒显示准确。

三、数字时钟组成及功能1、分频率器:用来产生100HZ计时脉冲;2、十二或二十四进制计数器:对时进行计数3、六十进制计数器:对分和秒进行计数;4、六进制计数器:分别对秒十位和分十位进行计数;5、十进制计数器:分别对秒个位和分个位进行计数;6、扫描显示译码器:完成对7字段数码管显示的控制;四、系统硬件要求1、时钟信号为10MHz;2、FPGA芯片型号EPM7128LC84—15、EP1K30TC144—3或EP1K100QC208—3(根据实验箱上FPGA芯片具体选择);3、8个7段扫描共阴级数码显示管;4、按键开关(清零、启动、保持,暂停);五、设计内容及步骤1、根据电路持点,用层次设计概念。

《VHDL语言及应用》Quartus II 软件使用与 VHDL 基础程序设计实验一、实验目的:(1)掌握 Quartus II 开发软件的基本使用,包括新建工程,代码编写与添加,工程编译与综合,建立波形仿真等步骤;(2)通过与门电路(AndGate)功能的编写,掌握 VHDL 程序的基本设计结构。

二、实验设备及软件:电脑,Quartus II 软件四、实验过程1.新建工程打开软件,File--New--New Quartus II Projec然后点击OK, 新建工程的第一个界面直接点击 Next, 界面第一行要在FPGA工程文件夹路径后再加上单独工程的名字,界面第二,第三行分别与工程目录名设定相同,因此都写AndGate。

选择实验需要的器件型号。

2.新建与添加代码文件对.vhd文件先进行编辑,编辑之后才可进行保存,点击左上方保存按钮,将代码文件保存至工程目录中,文件名为 AndGate。

第1行,第2行:库、程序包的调用说明。

第4行:ENTITY实体名IS。

第6行,第7行:输入的端口类型,输出的端口类型。

第12行:将信号赋值给对应的输出端口。

3.工程编译编译完成,通过下方的 Message窗口可以确认编译是否成功,如有错误,从Message信息提示判断代码何处出现错误,在编译完成后,点击左侧编译窗口中的RTL Viewer 可以查看代码综合生成的电路,此时编译窗口中还有一布EDA Netlist Writer没有自动完成,如果要进行功能波形仿真,则此时要再双击EDA Netlist Writer完成。

4.波形仿真点击左上角的 File—New--Vector Waveform File点击OK,出现波形文件界面后,点击左上方保存按钮,将其保存至工程目录中,默认命名与工程名相同,都为AndGate。

在波形文件界面左侧的Name拦中右键,选择Insert-->Insert Node or Bus,在弹出的界面中,点击Node Finder。

VLSI电路设计课设VHDL语言基础胡小玲主要内容z硬件描述语言简介z VHDL基本结构z VHDL数据和表达式z VHDL描述语句z系统仿真z综合硬件描述语言HDLz Hardware Description Language广义地说,描述电子实体的语言:逻辑图,电路图。

硬件描述语言能在高层设计阶段描述硬件。

z起源:大规模电路的出现,使得逻辑图、布尔方程不太适用,需要在更高层次上描述系统;出现多种HDL语言,为便于信息交换和维护,出现工业标准。

•分类:VHDL、Verilog HDL等。

硬件描述语言HDLz HDL语言的特点–用HDL语言设计电路能够获得非常抽象的描述–用HDL描述电路设计,在设计的前期就可以完成电路功能级的验证–用HDL设计电路类似于计算机编程。

带有注解的文字描述更有利于电路的开发与调试z能提供HDL模拟器的公司:Cadence、Altera、Mentor Graphics、Synopsys等大型EDA公司和专门公司学习HDL的几点重要提示了解HDL的可综合性问题HDL有两种用途:系统仿真和硬件实现。

如果程序只用于仿真,那么几乎所有的语法和编程方法都可以使用。

但如果我们的程序是用于硬件实现(例如:用于FPGA设计),那么我们就必须保证程序“可综合”(程序的功能可以用硬件电路实现)。

不可综合的HDL语句在软件综合时将被忽略或者报错。

我们应当牢记一点:“所有的HDL描述都可以用于仿真,但不是所有的HDL描述都能用硬件实现。

”用硬件电路设计思想来编写HDL学好HDL的关键是充分理解HDL语句和硬件电路的关系。

编写HDL,就是在描述一个电路,我们写完一段程序以后,应当对生成的电路有一些大体上的了解,而不能用纯软件的设计思路来编写硬件描述语言。

要做到这一点,需要我们多实践,多思考,多总结。

语法掌握贵在精,不在多30%的基本HDL语句就可以完成95%以上的电路设计,很多生僻的语句并不能被所有的综合软件所支持,在程序移植或者更换软件平台时,容易产生兼容性问题,也不利于其他人阅读和修改。

VHDL程序设计教程习题参考解答第1章思考题解答1.什么是VHDL?简述VHDL的发展史。

答:VHDL是美国国防部为电子项目设计承包商提供的,签定合同使用的,电子系统硬件描述语言。

1983年成立VHDL语言开发组,1987年推广实施,1993年扩充改版。

VHDL 是IEEE标准语言,广泛用于数字集成电路逻辑设计。

2.简述VHDL设计实体的结构。

答:实体由实体名、类型表、端口表、实体说明部分和实体语句部分组成。

根据IEEE标准,实体组织的一般格式为:ENTITY 实体名 IS[GENERIC(类型表);] --可选项[PORT(端口表);] --必需项实体说明部分; --可选项[BEGIN实体语句部分;]END [ENTITY] [实体名];3.分别用结构体的3种描述法设计一个4位计数器。

答:用行为描述方法设计一个4位计数器如下,其它描述方法,读者可自行设计。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_unsigned.all;ENTITY countA ISPORT (clk,clr,en:IN STD_LOGIC;Qa,qb,qc,qd:OUT STD_LOGIC);END countA;ARCHITECTURE example OF countA ISSIGNAL count_4:STD_LOGIC_vector (3 DOWNTO 0);BEGINQa <= count_4(0);Qb <= count_4(1);Qc <= count_4(2);Qd <= count_4(3);PROCESS (clk,clr)BEGINIF (clr = '1' ) THENCount_4 <= "0000";ELSIF (clk'EVENT AND clk = '1' ) THENIF (en = '1' ) THENIF (count_4 = "1111") THENcount_4 <= "0000";ELSEcount_4 <= count_4+ '1';END IF;END IF;END IF;END PROCESS;END example;第2章思考题解答1.什么叫对象?对象有哪几个类型?答:在VHDL语言中,凡是可以赋于一个值的客体叫对象(object)。

VHDL (VHSIC Hardware Description Language) is like the architect's blueprint for digital systems. It's a language that hardware engineers use to paint a vivid picture of how these systems are structured and how they behave. Think of it as a virtual playground where designers can play around with digital logic circuits before they bring them to life. With VHDL, they can test and verify their creations, ensuring that everything runs smoothly before it's time to hit the hardware. In other words, VHDL is the ultimate tool for digital wizards to work their magic and bring their ideas to life!VHDL(VHSIC硬件描述语言)就像建筑师的数字系统蓝图。

这种语言是硬件工程师用来描绘这些系统的结构及其表现的生动画面。

把它当作一个虚拟游乐场,设计者可以在带他们复活前用数字逻辑电路来游玩。

通过VHDL,他们可以测试和验证他们的创造,确保一切在击中硬件之前顺利运行。

VHDL是数位魔法师运用魔法,将想法带入生命的终极工具!One of the coolest things about VHDL is that it lets you test out your digital creations virtually before you actually build them. It's like a digital playground where you can play around with your ideas and see how they behave without spending a ton of money on physical prototypes. And the best part? You cancatch any design boo-boos early on and make sure everything is working smoothly. Not only that, VHDL also lets you create these little building blocks, kind of like digital Legos, that you can easily snap together to make bigger and better designs. It's like having a superpower for makingplex digital systems with lots of parts moving at the same time. So basically, VHDL is like the superhero of digital design – making things faster, cheaper, and a whole lot more fun!VHDL最酷的一件事就是它让你在实际建造之前测试你的数字创造。