基于锁相环的频率合成器的设计

- 格式:doc

- 大小:117.50 KB

- 文档页数:4

基于NE564D锁相环频率合成器的设计The Design of PLL Frequency Synthesizer Based on NE564D曾素琼(嘉应学院电子信息工程学院,广东梅州514015)Zeng Su-qiong(School of Electronics and Information Engineer, Jiaying University,Guangdong Meizhou 514015)摘要:设计基于NE564D的锁相频率合成器,对系统的实现作了详细描述,最后对系统作了实验验证及分析。

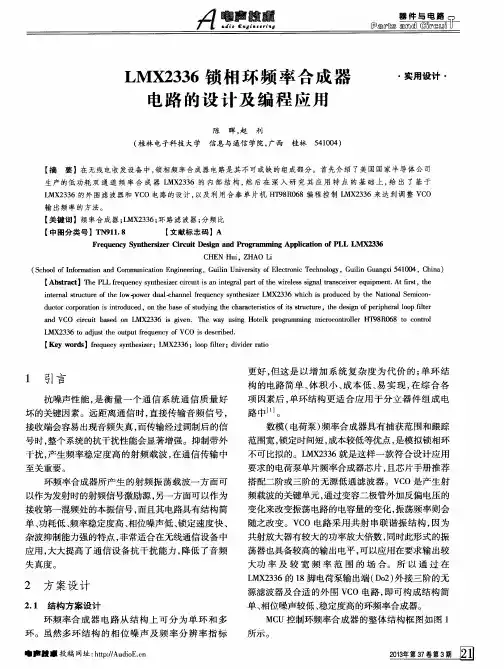

关键词:锁相环;锁相频率合成器;压控振荡器(VCO);NE564D中图分类号:TP273;TN915 文献标识码:B 文章编号:Abstract: In this paper, PLL frequency synthesizer based on NE564 is designed. The realization of the system was described in detail. Finally, experimental verification and analyzed of the system were made.Keywords: phase-locked loop; PLL frequency synthesizer; voltage-controlled oscillator (VCO);NE564DCLC number: TP273;TN915 Document code: B Article ID:1基于NE564D锁相环频率合成器的设计思路与系统框图锁相环NE564D是一种工作频率可高达50MHz的常用超高频集成锁相环,利用74LS393(74LS393是双四位二进制计数器)作为频率合成器的分频器,组成倍频锁相环频率合成器。

合成器输出频率为fo=Nfr。

式中fr为参考频率,通常是用高稳定度的晶体振荡器产生,对晶振频率固定之后获得的。

基于锁相环频率合成技术的波形发生器设计一、引言波形发生器是一种用于产生特定波形信号的电子设备,广泛应用于通信、测量、实验室等领域。

基于锁相环频率合成技术的波形发生器能够高精度地产生各种复杂的波形信号,具有频率可调、相位可控、稳定性高等优点,因此在现代电子设备中得到了广泛的应用。

二、基本原理基于锁相环频率合成技术的波形发生器主要由锁相环(Phase-Locked Loop, PLL)和数字控制电路组成。

其中,锁相环是一种反馈控制系统,它通过比较输入参考信号和输出信号的相位差,并根据差值进行调整,使输出信号的频率和相位与输入参考信号保持一致。

数字控制电路则负责接收用户设置的参数,控制锁相环的工作状态和输出信号的波形特性。

三、设计步骤1. 确定波形要求:首先需要明确设计的波形类型和要求,例如正弦波、方波、三角波等,以及所需的频率范围和分辨率。

2. 选择锁相环芯片:根据波形要求选择合适的锁相环芯片,考虑芯片的性能指标、工作频率范围、稳定性等因素。

3. 设计参考信号源:波形发生器的基准时钟通常采用稳定的晶振或时钟源,根据锁相环芯片的需求设计参考信号源电路。

4. 设计数字控制电路:根据用户需求设计数字控制电路,包括参数输入、控制逻辑和输出接口等部分。

5. 编程设置参数:利用数字控制电路进行参数设置,包括频率、相位、幅度等参数的输入和调整。

6. 输出波形信号:锁相环芯片根据输入的参数和参考信号源产生稳定的波形信号,并输出给用户使用。

四、应用场景基于锁相环频率合成技术的波形发生器广泛应用于多个领域。

在通信领域,它可以用于产生各种调制信号,用于调试和测试通信设备的性能。

在测量领域,它可以用于产生精确的时钟信号,用于同步测量设备的采样时序。

在实验室研究中,它可以用于产生特定频率和相位的信号,用于控制和激励实验装置。

五、总结基于锁相环频率合成技术的波形发生器具有频率可调、相位可控、稳定性高等优点,能够产生各种复杂的波形信号。

题目:频率合成器——基于4046的锁相环频率合成器一、课程设计目的:1.熟悉期间4046的基本原理和性能。

2.掌握频率合成器的原理和合成技术。

3.熟悉和掌握所学的各个器件,芯片,以及熟练的应用。

4.理解入锁和失锁的概念和原理。

5.融会贯通所学的高频知识,能够灵活的应用和设计。

6.理解和熟练分析基本的电路。

二、课程设计题目描述和要求:频率合成是以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出的准确度与稳定度与参考频率是一致的。

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成。

频率合成器有直接式频率合成器、直接数字式频率合成器及锁相频率合成器三种基本模式,前两种属于开环系统,因此是有频率转换时间短,分辨率较高等优点,而锁相频率合成器是一种闭环系统,其频率转换时间和分辨率均不如前两种好,但其结构简单,成本低。

并且输出频率的准确度不逊色与前两种,因此采用锁相频率合成。

频率合成器是一个系统,最初产生的一系列频率为参考频率的整数倍,参考频率通常是固定的。

这样的合成器称为整数N频率合成器。

频率合成器技术也不断前进,出现也很多新型的频率合成电路,并在通信电路中得到广泛应用。

锁相环由鉴相器、环路滤波器和压控振荡器组成。

频率合成一个或少量的高准确度高稳定的标准频率作为参考频率,由此导出多个或大量的输出频率.这些输出频率的准确度和稳定度与参考频率是一致的,频率合成器就是用来产生这些频率的部件.技术要求:1.达到输出为4-10M赫兹。

2.频率间隔为5K 赫兹。

3.基于4046芯片的设计。

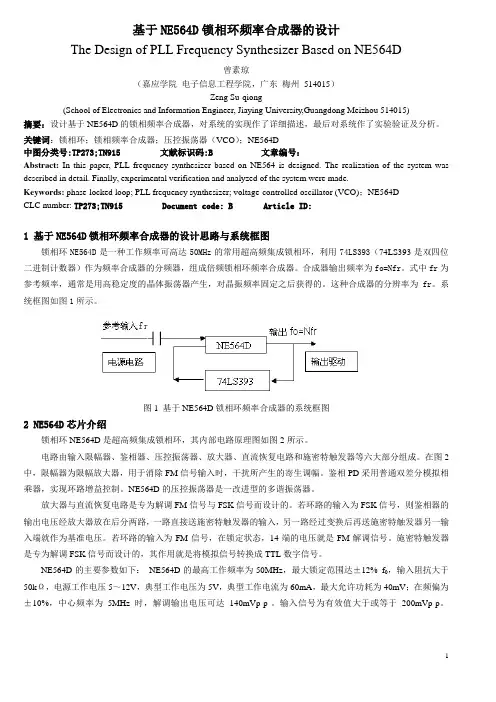

三、课程设计报告内容及原理:原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N ,从而就得到N 倍参考频率的稳定输出。

锁相环及频率合成器的原理及电路设计方案介绍引言锁相环简称PLL,是实现相位自动控制的一门技术,早期是为了解决接收机的同步接收问题而开发的,后来应用在电视机的扫描电路中。

由于锁相技术的发展,该技术已逐渐应用到通信、导航、雷达、计算机到家用电器的各个领域。

自从20世纪70年代起,随着集成电路的发展,开始出现集成的锁相环器件、通用和专用集成单片锁相环,使锁相环逐渐变成一个低成本、使用简便的多功能器件。

如今,PLL技术主要应用在调制解调、频率合成、彩电色幅载波提取、雷达、FM立体声解码等各个领域。

随着数字技术的发展,还出现了各种数字PLL器件,它们在数字通信中的载波同步、位同步、相干解调等方面起着重要的作用。

随着现代电子技术的飞快发展,具有高稳定性和准确度的频率源已经成为科研生产的重要组成部分。

高性能的频率源可通过频率合成技术获得。

随着大规模集成电路的发展,锁相式频率合成技术占有越来越重要的地位。

由一个或几个高稳定度、高准确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环及频率合成器的原理1.1 锁相环原理PLL是一种反馈控制电路,其特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因PLL可以实现输出信号频率对输入信号频率的自动跟踪,所以PLL通常用于闭环跟踪电路。

PLL在工作的过程中,当输出信号的频率与输入信号的频率相同时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是PLL名称的由来。

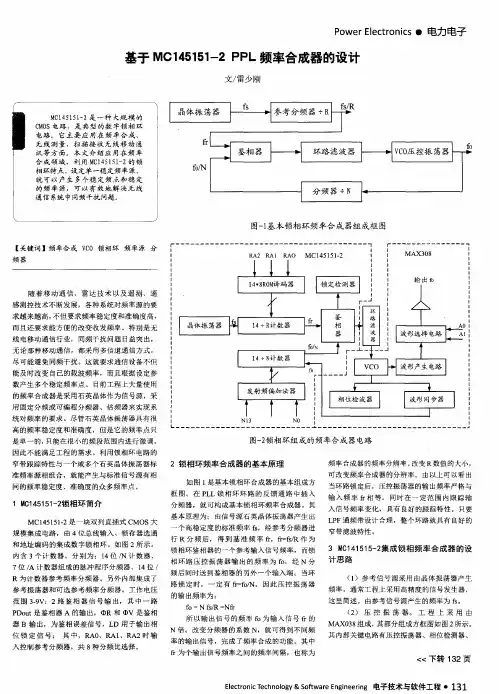

PLL通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,PLL组成的原理框图如图1所示。

PLL中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控。

第一章 绪论1.1 锁相环路锁相环路(PLL)是一个能够跟踪输入信号相位的闭环自动控制系统,它在无线电 技术的各个领域得到了很广泛的应用。

锁相环路有其独特的优良性能,它具有载波跟踪特 性,作为一个窄带跟踪滤波器,可提取淹没在噪声之中的信号;用高稳定的参考振荡器锁 定,可作提供一系列频率高稳定的频率源;可进行高精度的相位与频率测量等等。

它具有 调制跟踪特性,可制成高性能的调制器和解调器。

它具有低门限特性,可大大改善模拟信 号和数字信号的解调质量。

70 年代以来,随着集成电路技术的发展,逐渐出现了集成的 环路部件、通用单片集成锁相环路以及多种专用集成锁相环路,锁相环路逐渐变成了一个 成本低、使用简便的多功能组件,这就为锁相技术在更广泛的领域应用提供了条件。

锁相环是一个相位误差控制系统。

它比较输入信号和振荡器输出信号之间的相位差, 从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。

所谓全数字锁 相环路(DPLL)就是环路部件全部数字化, 采用数字鉴相器 (DPD)、 数字环路滤波器(DLF)、 数控振荡器(DCO)构成的锁相环路。

本文采用锁相式频率合成的实现方法, 实现中必须解决的关键技术问题是减小相位噪 声,以满足用户提出的较为苛刻的相位噪声指标。

本课题是设计一个由单片机、 定时计数器及单片机集成锁相环路组成的可程控频率合 成器,所以设计过程会涉及到锁相环路、频率合成器和单片机方面的知识。

1.2 锁相技术发展锁相原理在数学理论方面,早在 30 年代无线电技术发展的初期就己出现。

1930 年 己建立了同步控制理论的基础。

1932 年贝尔赛什(Bellescize)第一次公开发表了锁相环路的 数学描述,用锁相环路提取相干载波来完成同步检波。

到了 40 年代,电视接收机的同步 扫描电路中开始广泛地应用锁相技术,使电视图像的同步性能得到很大改善。

进入 50 年 代,随着空间技术的发展,由杰斐(Jaffe)和里希廷(Rechtin)利用锁相环路作为导弹信标的 跟踪滤波器获得成功,并首次发表了包含噪声效应的锁相环路线性理论分析的文章,同时 解决了锁相环路最佳化设计问题。

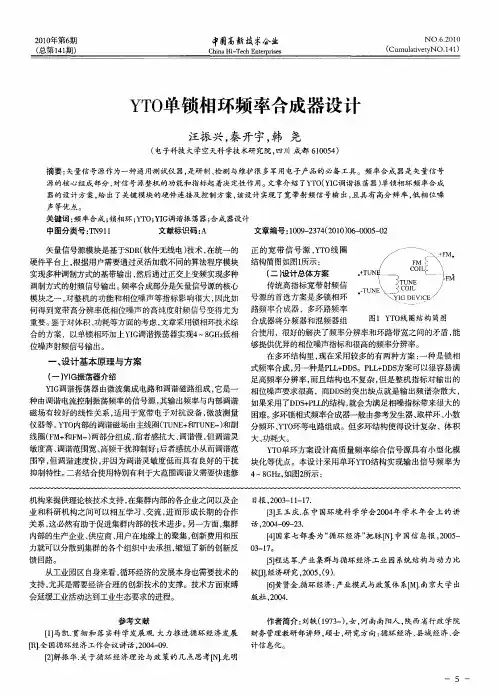

Technology Study技术研究DCW7数字通信世界2020.010 引言近年来,卫星通信技术的快速发展和各类机载、车载、地面等终端设备的广泛应用,对终端设备的体积和功耗要求越来越高,传统的锁相环和压控振荡器为两种独立的器件,尺寸较大,无法满足越来越迫切的产品小型化需求[1][2][3],本文利用ATMEL 公司的8位单片机ATTINY9结合TI 公司新一代集成VCO 的频合器LMX2572设计了一款输出频率为4875MHz 的锁相频率源。

设计要求:(1)相位噪声<-70dBc@100Hz ,<-80dBc@ 1kHz ,<-90dBc@ 10kHz ,<-100dBc@100kHz 。

(2)输出电平≥5dBm 。

1 硬件选择与实现1.1 硬件选择LMX2572是美国TI 公司2019年推出的一款低功耗、高性能宽带合成器,可以输出12.4MHz 到6.4GHz 之间的任何频率且不需要内部倍频,这就大大减少了混频输出的本振产生的分频和倍频杂散,PLL 可提供优异的性能,在3.3V 单电源中的电流消耗仅为75mA 。

LMX2572允许用户同步多个器件的输出,并可支持需要输入和输出之间具有确定延迟的应用并提供了一个可精准调节相位的选项,以解决电路板上或器件内的延迟不匹配问题;芯片内部的频率斜升发生器可在自动斜坡生成选项或手动选项中最多合成2段斜坡,以实现最大的灵活性。

通过快速校准算法,用户可在不到20μs 的时间内改变频率。

LMX2572集成了通过3.3V 单电源供电的LDO ,无需再配备板载低噪声LDO ,综合以上描述LMX2572为目前业界同类产品中比较领先的一款芯片,在100kHz 偏频和6.4GHz 载波的情况下具有-106dBc/Hz 的超低相位噪声[4]。

单片机选用的是ATMEL 公司ATTINY9芯片,该单片机是一个6个引脚的8位单片机,尺寸小,功耗低,其内部含有32Byte 的可编程可擦除存储器[5]。

集成电路课程设计一-锁相环CD4046设计频率合成器学号:110800316 姓名:苏毅坚指导老师:罗国新2011年1月锁相环CD4046设计频率合成器实验目的:设计一个基于锁相环CD4046设计频率合成器范围是10k〜100K,步进为1K设计和制作步骤:确定电路形式,画出电路图。

计算电路元件参数并选取元件O组装焊接电路。

调试并测量电路性能。

确定电路组成方案原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。

晶体振荡器输出的信号频率n,经固定分频后(M分频)得到基准频率fi,,输入锁相环的相位比较器(PC)。

锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:n/M=fF=f2/N 故f2=N『l (Fl为基准频率)当N变化时,就可以得到一系列的输出频率f2o设计方法(一)、振荡源的设计用CMOS与非门和1M晶体组成1MHz振荡器,如图14。

图中Rf使F1工作于线性放大区。

晶体的等效电感,Cl> C2构成谐振回路。

C1、C2可利用器件的分布电容不另接。

Fl、F2、F3 使用CD4049o(二)、N分频的设计N分频采用CD40103进行分频。

CD40103是BCD码8位分频器。

采用8位拨码开关控制分频大小。

输入的二进制大小即为分频器N分频。

图中RP1为1K排阻(三)、1KHZ标准信号源设计(即M分频的设计)根据4518的输出波形图,可以看出4518包含二分频、四分频、十分频,用二片CD4518 (共4个计数器)组成一个1000分频器,也就是三个十分频器,这样信号变为2Khz.再经过双D触发器,这样就可把2MHz的晶振信号变成500hz 的标准信号。

如下图所示:(四)4046锁相环的设计锁相环4046为主芯片。

电路图如下:500Hz信号从14脚输入。

3脚4脚接N分频电路,即40103分频电路。