电子系统设计综合实验

- 格式:doc

- 大小:534.50 KB

- 文档页数:6

电子系统电子系统综合综合综合设计设计一、 实验目的验目的::本次电子设计要求学生自行完成脉宽调制法电容/电压(C/V)转换器电路设计和方波-三角波发生器电路设计,并运用电子仿真软件multisim 对所设计的电路进行分析、测试,直至测试结果符合设计要为止,使学生了解、掌握电子仿真软件multisim 的应用,并通过仿真软件的仿真结果,使学生进一步掌握脉宽调制法电容/电压(C/V)转换器和方波-三角波发生器的电路设计思路、电路结构、元器件参数的选取及计算过程,最后根据电路原理图进行电路板焊接和调试,对模拟仿真结果进行验证,从而为学生以后的科研工作打下一个坚实的基础。

二、 实验器材实验器材::电脑一套,multisim 仿真软件一套。

三、 实验进度安排实验进度安排::(1) 根据所给题目要求,自行设计电路原理图,并对电路设计原理进行分析。

(2) 运用multisim 仿真软件对电路进行仿真,用虚拟示波器观察各点波形,根据波各点波形对器件参数进行适当的修改,直道测试结果满意为止,从而加深了学生对电路设计原理的进一步掌握。

(3) 按照电路原理图焊接电路、调试电路,用示波器观察各点波形,分析测得波形与虚拟示波器观察各点波形是否一样。

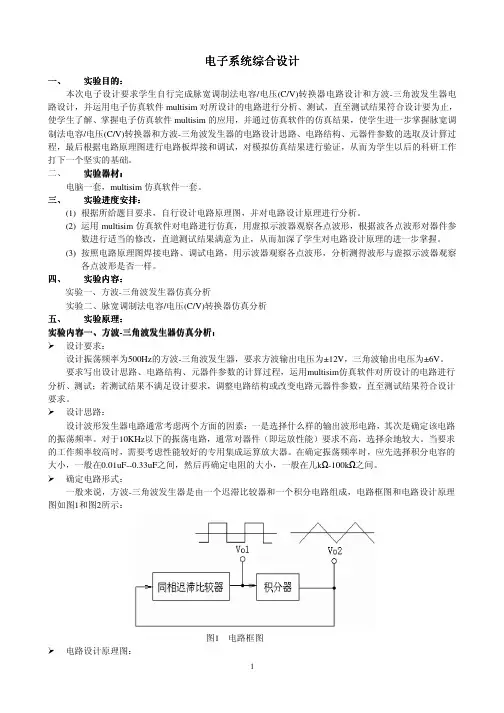

四、 实验内容内容::实验一、方波-三角波发生器仿真分析实验二、脉宽调制法电容/电压(C/V)转换器仿真分析 五、 实验原理实验原理:: 实验内容一实验内容一、、方波-三角波发生器仿真分析三角波发生器仿真分析:: 设计要求:设计振荡频率为500Hz 的方波-三角波发生器,要求方波输出电压为±12V ,三角波输出电压为±6V 。

要求写出设计思路、电路结构、元器件参数的计算过程,运用multisim 仿真软件对所设计的电路进行分析、测试;若测试结果不满足设计要求,调整电路结构或改变电路元器件参数,直至测试结果符合设计要求。

设计思路:设计波形发生器电路通常考虑两个方面的因素:一是选择什么样的输出波形电路,其次是确定该电路的振荡频率。

基于单片机和FPGA的等精度频率计一、设计任务工作频率通信系统极为重要的参数,频率测量是通信系统基本的参数测试之一。

本设计的主要任务是使用单片机与 EDA 技术设计制作一个简易的等精度频率测试仪,可对输入周期信号的频率进行测量、显示。

被测信号的频率范围和测试的精度要求见相应的设计任务书。

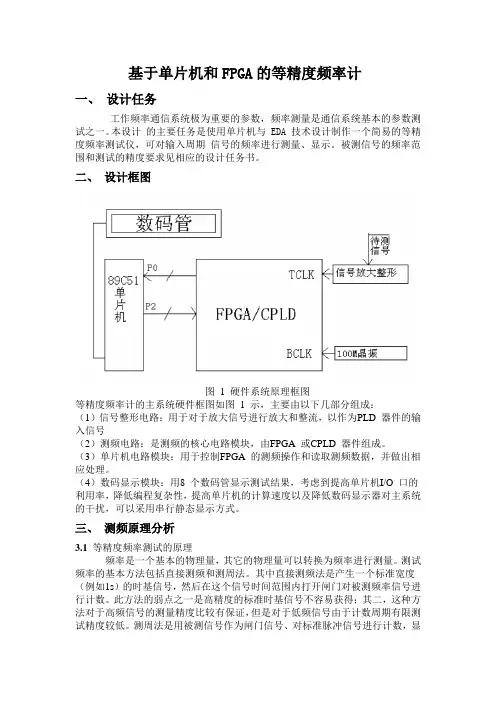

二、设计框图图 1 硬件系统原理框图等精度频率计的主系统硬件框图如图1 示,主要由以下几部分组成:(1)信号整形电路:用于对于放大信号进行放大和整流,以作为PLD 器件的输入信号(2)测频电路:是测频的核心电路模块,由FPGA 或CPLD 器件组成。

(3)单片机电路模块:用于控制FPGA 的测频操作和读取测频数据,并做出相应处理。

(4)数码显示模块:用8 个数码管显示测试结果,考虑到提高单片机I/O 口的利用率,降低编程复杂性,提高单片机的计算速度以及降低数码显示器对主系统的干扰,可以采用串行静态显示方式。

三、测频原理分析3.1 等精度频率测试的原理频率是一个基本的物理量,其它的物理量可以转换为频率进行测量。

测试频率的基本方法包括直接测频和测周法。

其中直接测频法是产生一个标准宽度(例如1s)的时基信号,然后在这个信号时间范围内打开闸门对被测频率信号进行计数。

此方法的弱点之一是高精度的标准时基信号不容易获得;其二,这种方法对于高频信号的测量精度比较有保证,但是对于低频信号由于计数周期有限测试精度较低。

测周法是用被测信号作为闸门信号、对标准脉冲信号进行计数,显然这种方法适合测量低频信号的频率。

等精度测频法的核心思想是用两个计数器分别对标准和被测脉冲进行计数,计数的时间严格同步于被测脉冲。

这种方法的最大优点是测试的精度和被测信号的频率无关,因而可以做到等精度测量。

其测试原理如图2 示。

预置闸门信号是测试命令,即测频的使能信号,该信号为高电平的期间进行测频。

但是当预置闸门信号为高电平时,测频并不是立即开始,而是要等到被测信号的上升沿到来以后,实际闸门信号跳为高电平,测频才真正开始。

电子系统综合实验实验指导书温州大学物理与电子信息学院2007.9D34S255 、• % 2: 2K 32_ \ 3133 292S 0 1234 呂&7 DD D01234567 …H A A A A A A A pp pppp pp = I • H LId Pa 1 ; ~L P A 2 i 4心: •甘 III 4"PAE : 英F餐M? F 口 7 :U RZ 36A 19A2旦RST 35DR R uRESETCS@123456?BBBBBBBB p plp pp ppp01234567 cc c cc c c c IP 户p ipp lp lplpD3374LS240DL 1 2 DL2 4 DL4 81 A 1 1 A2 1 A3 1 fl41¥1 1 V2 1 Y3 1 742 A 1 2 A22 A3 2 A4 2V1 2V2 2V3 2?41T5 2GRN7 68O*S RrSPACKS实验一 IO 扩展芯片实验[实验目的和要求]1. 了解8255芯片结构及编程方法。

2. 了解8255输入/输出实验方法。

3. 掌握扫描键盘和显示的编程方法。

[实验内容]1、输入/输出实验:利用8255可编程并行口芯片,进行输入/输出实验,实 验中用8255PA 口作输出,PB 口作输入。

①实验电路及连线:RD/CSX 61召F 目0 .PB1:户I2 J PB2£斗尸日直2E PB7K8255的CS/接138的8400H ,则命令字地址为8406H,PA 口地址为8400H , PB 口地址为8402H , PC 口地址为8404H。

PA0~PA7 (PA 口)接DL1~DL7 (LED );PB0~PB7 (PB 口)接K1~K8 (开关量)。

②实验说明:可编程通用接口芯片8255A有三个八位的并行I/O 口,它有三种工作方式。

本实验采用的是方式0 : PA,PC 口输出,PB 口输入。

实验报告格式要求二.实验目的、任务和要求:本实验要求设计SCI串行接口芯片, 其功能包括串行及并行数据的接收和互相转换。

三.实验系统结构设计分析1.模块划分思想和方法:该芯片需根据功能分为串并转换电路和并串转换电路两部分。

实现串并转换的关键器件就是移位寄存器, 其功能可以使串行输入的数据先寄存到一个位矢量中, 等到一组数据全部输入完毕后再一起处理, 并行输出。

而实现并串转换的关键器件是锁存器, 它可以将并行输入的数据先锁存起来, 再一位一位的转化成串行数据。

计数器在这一芯片中也起到了重要作用, 因为计数器可以产生时间脉冲的分频, 用于配合时间脉冲控制各器件的工作。

2.各模块引脚定义和作用.串并电路:输入: rxd读入数据, clk系统时钟, reset计数器复位端, rd读入控制四进制计数器:C4四分频十进制计数器:Count_10计数分量, C10四十分频(c4的十分频)移位寄存器:Read读入数据, d0~d9并行输出(d0起始端, d1~d8数据端, d9校验位(本实验中不起作用))锁存器:K0~k7数据位状态发生器:RdST读入状态(0为读入, 1为寄存器已满)四.实验代码设计以及分析:1.给出模块层次图;2.按模块完成的代码及注释.USE IEEE.STD_LOGIC_1164.ALL;ENTITY SCI ISPORT(cs,rxd,clk,SCIrd,reset,SCIwr,in7,in6,in5,in4,in3,in2,in1,in0: IN STD_LOGIC;rdFULL,tdEMPTY,c4:buffer std_logic;e7,e6,e5,e4,e3,e2,e1,e0,wxd:OUT STD_LOGIC);END SCI;ARCHITECTURE WORK OF SCI ISSIGNAL wr,rd,read,c10,d9,d8,d7,d6,d5,d4,d3,d2,d1,d0,k7,k6,k5,k4,k3,k2,k1,k0,mid: STD_ULOGIC;SIGNAL wri : STD_LOGIC_vector(7 downto 0);SIGNAL count_10 ,counter_8:std_logic_vector(3 downto 0);BEGINPROCESS(cs)BEGINrd<=cs OR SCIrd;wr<=cs OR SCIwr;END PROCESS;//注释: 片选输入, cs=1时, 串入并出为“写”, 并入串出为“读”;cs=0时, 串入并出为“读”, 并入串出为“写”;PROCESS(rxd)BEGINread<=rxd;END PROCESS;PROCESS(clk)VARIABLE count_4 : STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINIF(clk'EVENT AND clk='1')THENIF(count_4="00")THENcount_4 := "01";c4 <= '1';ELSIF(count_4="01")THENcount_4 := "11";c4 <= '1';ELSIF(count_4="11")THENcount_4 := "10";c4 <= '0';ELSIF(count_4="10")THENcount_4 := "00";c4 <= '0';END IF;END IF;END PROCESS;PROCESS(c4)BEGINIF(c4'EVENT AND c4='1')THENIF(rd='1')THENd0<=read;d1<=d0;d2<=d1;d3<=d2;d4<=d3;d5<=d4;d6<=d5;d7<=d6;d8<=d7;d9<=d8;END IF;END IF;END PROCESS;PROCESS(c4,reset,rd)BEGINIF(reset='0' OR rd='0')THEN count_10<="0000";c10 <= '0';ELSIF(c4'EVENT AND c4='1')THENIF(count_10="0000" AND rxd='1' AND rdFULL='0')THEN count_10 <= "0001";c10 <= '0';ELSIF(count_10="0001")THENcount_10 <= "0010";c10 <= '0';ELSIF(count_10="0010")THENcount_10 <= "0011";c10 <= '0';ELSIF(count_10="0011")THENcount_10 <= "0100";c10 <= '0';ELSIF(count_10="0100")THENcount_10 <= "0101";c10 <= '0';ELSIF(count_10="0101")THENcount_10 <= "0110";c10 <= '0';ELSIF(count_10="0110")THENcount_10 <= "0111";c10 <= '0';ELSIF(count_10="0111")THENcount_10 <= "1000";c10 <= '0';ELSIF(count_10="1000")THENcount_10 <= "1001";c10 <= '0';ELSIF(count_10="1001")THENcount_10 <= "1010";c10 <= '0';ELSIF(count_10="1010")THENcount_10 <= "1011";c10 <= '1'; END IF;END IF;END PROCESS;PROCESS(c10)BEGINIF(c10'EVENT AND c10='1')THENk7<=d8;k6<=d7;k5<=d6;k4<=d5;k3<=d4;k2<=d3;k1<=d2;k0<=d1;END IF;END PROCESS;PROCESS(rd)BEGINIF(rd='0')THENe7<=k7;e6<=k6;e5<=k5;e4<=k4;e3<=k3;e2<=k2;e1<=k1;e0<=k0;END IF;END PROCESS;PROCESS(rd,c10)BEGINIF(rd='0')THEN rdFULL<='0';ELSIF(c10='1')THENrdFULL<='1';ELSE rdFULL<='0';END IF;END PROCESS;process(wr)beginif(wr='0')thenwri(0)<=in0;wri(1)<=in1;wri(2)<=in2;wri(3)<=in3;wri(4)<=in4;wri(5)<=in5;wri(6)<=in6;wri(7)<=in7;end if;end process;process(c4)beginif(c4'event and c4='1')thenif(wr='0')thencounter_8<="0000";elsif(wr='1' and counter_8="0000")then counter_8<="0001"; elsif(counter_8="0001")then counter_8<="0010";elsif(counter_8="0010")then counter_8<="0011";elsif(counter_8="0011")then counter_8<="0100";elsif(counter_8="0100")then counter_8<="0101"; elsif(counter_8="0101")then counter_8<="0110";elsif(counter_8="0110")then counter_8<="0111";elsif(counter_8="0111")then counter_8<="1000";elsif(counter_8="1000")then counter_8<="1001";end if;end if;end process;process(wr,counter_8)beginif(wr='1' and counter_8="1001")thenmid<='1';tdEMPTY<='1';elsif(wr='0')thenmid<='0';tdEMPTY<='0';end if;end process;process(counter_8)beginif(wr='0' or mid='1')thenwxd<='0';elsif(wr='1' and mid='0')thenif(counter_8="0001")thenwxd<=wri(0);elsif(counter_8="0010")thenwxd<=wri(1);elsif(counter_8="0011")thenwxd<=wri(2);elsif(counter_8="0100")thenwxd<=wri(3);elsif(counter_8="0101")thenwxd<=wri(4);elsif(counter_8="0110")thenwxd<=wri(5);elsif(counter_8="0111")thenwxd<=wri(6);elsif(counter_8="1000" )thenwxd<=wri(7);end if;end if;end process;END WORK;五.仿真图(输入输出波形)以及分析:六.实验问题分析和经验总结:在该实验的设计中, 我们发现时序逻辑中最重要的部分就是时间信号对各进程的控制, 因为为了保持各进程在时间上的同步性和正确性, 需要用一个或几个相关联的时间信号来控制各进程。

电子系统设计实验报告电子系统设计实验报告引言:电子系统设计是现代科技领域中非常重要的一部分,它涉及到电子元件、电路设计、信号处理等多个方面的知识。

本次实验旨在通过设计一个简单的电子系统来加深对电子系统设计的理解和掌握。

实验目的:本次实验的目的是设计一个基于Arduino的温度监测系统。

通过该系统,能够实时监测环境温度并将数据显示在LCD屏幕上。

实验器材:1. Arduino开发板2. 温度传感器3. LCD显示屏4. 连接线等实验步骤:1. 首先,将温度传感器与Arduino开发板连接。

将传感器的VCC引脚连接到5V引脚,GND引脚连接到GND引脚,将信号引脚连接到Arduino的A0引脚。

2. 接下来,连接LCD显示屏。

将显示屏的VCC引脚连接到5V引脚,GND引脚连接到GND引脚,将SDA引脚连接到A4引脚,SCL引脚连接到A5引脚。

3. 在Arduino开发环境中编写代码。

首先,需要包含所需的库文件,如LiquidCrystal_I2C库和Wire库。

然后,定义温度传感器引脚和LCD显示屏的相关参数。

接着,在setup函数中初始化LCD显示屏,并设置显示屏的列数和行数。

在loop函数中,通过调用温度传感器库函数获取环境温度,并将其显示在LCD屏幕上。

4. 将Arduino开发板与电脑连接,并上传代码到开发板上。

5. 实验完成后,观察LCD屏幕上的温度显示,确保温度监测系统正常工作。

实验结果:经过实验,我们成功设计并实现了一个基于Arduino的温度监测系统。

该系统能够准确地测量环境温度,并将数据实时显示在LCD屏幕上。

通过该系统,我们可以方便地监测环境温度的变化。

实验总结:通过本次实验,我们对电子系统设计有了更深入的了解。

我们学会了如何使用Arduino开发板和相关传感器进行电子系统的设计。

同时,我们也掌握了如何编写代码并将其上传到开发板上。

这些技能对于今后从事电子系统设计工作将非常有帮助。

第1篇一、实验目的本次实验旨在通过设计和实现一个电子考勤系统,了解电子考勤系统的基本原理和开发流程,掌握相关技术,提高实际操作能力。

通过本实验,学生应能够熟练使用相关技术,实现考勤数据的录入、查询、统计和分析等功能。

二、实验内容1. 系统需求分析(1)功能需求电子考勤系统应具备以下功能:1)考勤数据录入:系统应能实现员工打卡、请假、加班等考勤数据的录入;2)考勤数据查询:系统应能实现按时间、部门、岗位等条件查询考勤数据;3)考勤数据统计:系统应能实现考勤数据的统计和分析,如迟到、早退、缺勤等;4)考勤数据导出:系统应能将考勤数据导出为Excel、CSV等格式;5)系统管理:系统应具备用户管理、权限管理、数据备份与恢复等功能。

(2)性能需求1)系统应具备良好的稳定性,能够保证在高峰时段正常运行;2)系统应具备较高的安全性,防止数据泄露和非法访问;3)系统应具备良好的可扩展性,方便后续功能扩展和升级。

2. 系统设计(1)系统架构本系统采用B/S架构,前端使用HTML、CSS、JavaScript等技术,后端使用Java语言进行开发。

数据库采用MySQL,系统运行在Tomcat服务器上。

(2)系统模块设计1)用户模块:实现用户登录、注册、修改密码等功能;2)考勤模块:实现考勤数据录入、查询、统计和分析等功能;3)权限模块:实现用户权限管理和数据备份与恢复等功能;4)数据模块:实现考勤数据的存储、查询、统计和分析等功能。

3. 系统实现(1)前端开发前端使用HTML、CSS、JavaScript等技术实现系统界面,包括登录、注册、考勤录入、查询、统计等功能模块。

(2)后端开发后端使用Java语言进行开发,采用Spring Boot框架进行开发,实现系统核心功能。

(3)数据库设计数据库采用MySQL,设计考勤表、用户表、权限表等数据表,实现数据存储和查询。

4. 系统测试(1)功能测试对系统各个功能模块进行测试,确保系统功能完整、稳定。

2022年12月第49期Dec. 2022No.49教育教学论坛EDUCATION AND TEACHING FORUM“电子系统综合设计”的实践教学设计研究郜东瑞,汪曼青(成都信息工程大学 计算机学院,四川 成都 610225)[摘 要] 围绕以成果为导向的教育理念,在计算机学院配合电子系统综合设计课程,开展实践教学设计。

实践教学设计通过设计开发综合类的电子系统,聚焦学以致用,培养学生理论知识和专业技能,提高学生解决工程问题的能力,培养学生统筹工程开发的综合素养。

结合成都信息工程大学的实际,开展面向注意力在线监测系统的电子系统综合设计,带领学生完成任务规划、电路设计、嵌入式开发、软件开发、系统集成,并进行注意力监测的实验验证。

总结了教学体会并拓展改革思路,对引导计算机专业学生实现OBE的课程目标具有参考意义。

[关键词] OBE;注意力监测系统;综合设计实践[作者简介] 郜东瑞(1987—),男,河南南阳人,博士,成都信息工程大学计算机学院副教授,主要从事人工智能、脑机接口研究;汪曼青(1989—),女,重庆人,博士,成都信息工程大学计算机学院讲师(通信作者),主要从事人工智能、脑机接口研究。

[中图分类号] G642 [文献标识码] A [文章编号] 1674-9324(2022)49-0119-04 [收稿日期] 2022-04-12引言成果导向教育(OBE)是一种以学习成果为导向的工程教育理念,通过目标—措施—评价的闭环结构,以学生为主体,以学到了什么为目的,重点培养学生进入工作岗位后所具备分析问题和解决问题的能力[1-2]。

相比于传统教育模式,OBE教学理念将以教师为中心转变为以学生为中心,面向学生的专业设置、毕业要求和职业目标,设计教学方法、教学内容和课程体系,有利于教学相长和学习效果的持续改进,已成为工科课程教学改革的新方向[3-4]。

因此,笔者结合所在院校的培养目标,以“电子系统综合设计”课程为例,构建综合系统设计课程的教学内容、教学技巧和教学考核,达到串联学生已有知识、培养学生的动手能力、提升综合素质的目的。

电子系统综合设计实验报告所选课题:±15V直流双路可调电源学院:信息科学与工程学院专业班级:学号:学生姓名:指导教师:2016年06月摘要本次设计本来是要做±15V直流双路可调电源的,但由于买不到规格为±18V 的变压器,只有±15V大小的变压器,所以最后输出结果会较原本预期要小。

本设计主要采用三端稳压电路设计直流稳压电源来达到双路可调的要求。

最后实物模型的输出电压在±13左右波动。

1、任务需求⑴有+15V和-15V两路输出,误差不超过上下1.5V。

(但在本次设计中,没有所需变压器,所以只能到±12.5V)⑵在保证正常稳压的前提下,尽量减小功效。

⑶做出实物并且可调满足需求2、提出方案直流可变稳压电源一般由整流变压器,整流电路,滤波器和稳压环节组成如下图a所示。

⑴单相桥式整流作用之后的输出波形图如下:⑵电容滤波作用之后的输出波形图如下:⑶可调式三端集成稳压器是指输出电压可以连续调节的稳压器,有输出正电压的LM317三端稳压器;有输出负电压的LM337三端稳压器。

在可调式三端集成稳压器中,稳压器的三个端是指输入端、输出端和调节端。

LM317的引脚图如下图所示:(LM337的2和3引脚作用与317相反)3、详细电路图:因为大容量电解电容C1,C2有一定的绕制电感分布电感,易引起自激振荡,形成高频干扰,所以稳压器的输入、输出端常 并入瓷介质小容量电容C5,C6,C7,C8用来抵消电感效应,抑制高频干扰。

参数计算: 滤波电容计算:变压器的次级线圈电压为15V ,当输出电流为0.5A 时,我们可以求得电路的负载为I =U /R=34Ω时,我们可以根据滤波电容的计算公式: C=т/R,来求滤波电容的取值范围,其中在电路频率为50HZ 的情况下,T 为20ms 则电容的取值范围大于600uF ,保险起见我们可以取标准值为2200uF 额定电压为50V的点解电容。

北京邮电大学电子电路综合实验报告示波器功能扩展电路的设计学院:电子工程学院班级:学号:班内序号:姓名:目录摘要关键字 (3)实验目的 (3)实验仪器与器件 (3)实验任务要求 (3)设计思路和总体结构框图 (3)分块电路原理 (4)总体结构框图与电路原理总结 (6)实现功能说明以及主要测试数据 (7)故障及问题分析 (9)总结和心得体会 (9)PROTEL绘制的原理图 (11)面包板与PCB板 (11)所有元器件及测试仪表清单 (12)参考文献 (13)课题名称:示波器功能扩展电路的设计与实现摘要:本实验是示波器功能扩展电路,可同时用一路通道检测分离4路信号。

电路分为五个基本分块电路——(1)555定时器作多谐振荡器产生时钟信号,时钟电路产生方波;(2)地址产生电路:计数器74LS169产生方波的二分频与四分频信号;(3)位移电路:CD4052一路为直流通道,另一路为信号通道,两路信号通过衰减器后在示波器水平位置上同时显示四路不同的信号;(4)放大调整和加法器电路:集成运放用于信号衰减放大与加法,将交流信号叠加到直流信号上实现纵向分离。

关键词:选通电路、信号叠加、交流放大,多踪显示。

一、实验目的:1.了解掌握555定时器的用作多谢振荡器的方法。

2.了解运算放大器组成的加法器实际应用。

3.学习模拟多路选择器的工作原理和使用方法。

4.复习巩固示波器原理和使用的相关知识。

5.提高独立设计电路和验证试验的能力二、实验仪器与器件:1. 直流稳压电源2. 函数信号发生器3. 示波器4. 晶体管毫伏表5. 万用表6. 芯片:NE555定时器;集成运算放大器LF353;计数器74LS169;多路模拟开关CD4052;7.电阻电容导线若干8. 面包板三、实验任务要求设计制作一个示波器功能拓展电路,能够实现将普通双踪示波器改装成为多踪示波器进行多路信号测试。

1.基本要求:(1)能够实现用示波器一路探头输入稳定显示四路被测波形;(2)输入信号幅度为0~10V,频率不低于500Hz;(3)系统电源DC+-5V。

电子系统设计专题实验报告实验一、基于 AVR ATMega128 的硬件(PCB)设计 一、 实验目的和要求目的: (1)掌握印制电路板设计的基本原则及印制电路板的设计制作流程。

(2)掌握 Protel DXP 2004 SP2 软件的基本功能。

(3)在 Protel DXP 2004 SP2 软件平台,完成电路图到 PCB 图的设计制作过 程。

要求: (1)根据实验要求, 完成原理图的设计,并在 Protel DXP 2004 SP2 软件平台 上设计制作出相应的 PCB 图。

(2)要求 PCB 图布局布线美观,抗干扰性能强。

图中所用到的元件封装必须 符合实际的元件尺寸。

二、 实验设备及设计开发环境操作系统: XP 软件:Protel DXP 2004 SP 2三、 实验内容根据 ATMega128 的电路图设计一个单片机电路板,其中包括基本电路、复位 电路、时钟振荡器(ISP、键盘、RT Clock)。

MCU 原理图如图四、 实验步骤1. 创建新的工程项目,并新建原理图图纸 2. 设置工程参数,包括基本原理图参数设置。

3. 绘制原理图:在元件库中查找所用元件,并进行必要说明,如标签、总线、 端口等。

4. 放置各个模块与图纸合适位置,方便之后端口的对接及导入。

5. 对原理图进行电气检查,编译查错时,直至消除后保存原理图。

6. 创建新的 PCB 文件,并对 PCB 进行正确合理的参数设置(注意:在设置尺 寸时,不宜设置太小,不利于元件布局及布线),保存文件。

7. 导入原理图,将元件合理放置,原则:组合功能的元件(键盘开关)有序放 置在一起,使得各个元件布线交叉尽可能的少。

8. 对电路板自动布线,进行规则检查,注意检查 PCB 有没有缺线、缺元件的 情况修改错误的地方,并注意印刷线路的宽度设置,不宜太宽。

9. 重复步骤 8,对电路板布局不断进行修改优化,直到 PCB 的规则检查没有警告、错误,电路板元件布局思路清晰,布线方式正确合理。

电⼦电路综合设计实验报告(数控直流稳压电源设计)北京邮电⼤学电⼦电路综合设计实验实验报告实验名称:简易数控直流稳压电源的设计学院:电⼦⼯程学院班级:XXX班学号:XXXXXXXX姓名:XXX班内序号:XX2012年3⽉25⽇课题名称:简易数控直流稳压电源的设计摘要:本设计实验要求我们设计出简易数控直流稳压电源,通过⼿动调节实现输出不同电压的功能,通过电压与电流的放⼤实现较强的带负载能⼒,通过滤波电容消除纹波对直流的影响,并运⽤protel 软件进⾏仿真。

该设计实验旨在培养我们的实验兴趣与学习兴趣,提⾼实验技能与探究技能,引导我将所学所想运⽤到实际中去。

关键字:稳压电源,设计,仿真⼀、设计任务要求1.基本要求(1)设计实现⼀个简易数控直流稳压电源,设计指标及给定条件为:1) 输出电压调节范围:5V ~ 9V,步进0.5V 递增,纹波⼩于50mV;2) 输出电流⼤于100mA;3) 由预制输⼊控制输出电压递增;4) 电源为12V。

(2)设计+5V电源电路(不要求实际搭建),⽤PROTEL软件绘制完整的电路原理图(SCH)。

2.提⾼要求(1) 数字控制部分采⽤+/-按键来调整控制⼀可逆⼆进制计数器来预设电压值;(2) ⽤PROTEL软件绘制电路的印刷电路板图(PCB)。

3.探究要求输出电压调节范围更宽,步进更⼩:范围:0 ~ 10 V, 步进:0.1V。

本次探究实验主要着重完成了基本要求部分的设计与探究。

⼆、设计思路、总体结构框图本实验要求设计⼀个可以充当数控直流稳压电源的电路,电路由数字控制部分、D/A 转换部分、可调稳压部分组成。

数字控制部分采⽤+/-按键来调整控制⼀可逆⼆进制计数器来预设电压值(此部分为提⾼部分),⼆进制计数器输出输⼊到D/A 转换器中,经过D/A 转换后实现输出电压的可调。

其框图如图1所⽰。

图1 系统总体结构框图三、分块电路和总体电路的设计1.第⼀部分——数字电路控制部分此部分是电路的数字控制部分,也是电路输⼊端,其电路原理图如图2所⽰。

《电子系统设计与实践》课程设计报告课程设计题目:多点温度测量系统设计专业班级:2012级电子信息科学与技术学生姓名:罗滨志(120802010051)张倩(120802010020)冯礼哲(120802010001)吴道林(120802010006)朱栖安(120802010039)指导老师:刘万松老师成绩:2015 年6 月27日目录摘要 (4)1 总体设计 (4)1.1 功能要求 (5)1.2 总体方案及工作原理 (5)2 系统硬件设计 (6)2.1 器件选择 (6)2.1.1主要器件的型号 (6)2.1.2 AT89C51 (6)2.1.3智能温度传感器DS18B20 (8)2.1.4晶振电路方案 (9)2.1.5 LED液晶显示器 (9)2.1.6复位电路方案 (10)2.2 硬件原理图 (10)3 系统软件设计 (10)3.1基本原理 (11)3.1.1主程序 (11)3.1.2读ROM地址程序 (11)3.1.3显示ROM地址程序 (12)3.1.4读选中DS18B20温度的程序 (12)3.1.5显示温度程序 (13)3.2软件清单 (14)4实验步骤 (22)4.1实验程序调试 (22)4.2实验仿真 (23)5设计总结 (24)6参考文献: (25)摘要温度是我们生活中非常重要的物理量。

随着科学技术的不断进步与发展,温度测量在工业控制、电子测温计、医疗仪器,家用电器等各种控制系统中广泛应用。

温度测量通常可以使用两种方式来实现:一种是用热敏电阻之类的器件,由于感温效应,热敏电阻的阻值能够随温度发生变化,当热敏电阻接入电路时,则流过它的电流或其两端的电压就会随温度发生相应的变化,再将随温度变化的电压或者电流采集过来,进行A/D转换后,发送到单片机进行数据处理,通过显示电路,就可以将被测温度显示出来。

这种设计需要用到A/D转换电路,其测温电路比较麻烦。

第二种方法是用温度传感器芯片,温度传感器芯片能把温度信号转换成数字信号,直接发送给单片机,转换后通过显示电路显示即可。

南通大学电工电子实验中心电子系统综合设计实验报告课题名称:峰值检测系统的设计姓名:沈益学号:0812002017指导教师:陈娟实验时间:2011年1月3日至14日峰值检测系统主要由传感器、放大器、采样/保持、采样/保持控制电路、A/D转换电路、数码显示、数字锁存控制电路组成。

其关键任务是检测峰值并使之保持稳定,且用数字显示峰值。

一、设计目的1、掌握峰值检测系统的原理;2、掌握峰值检测系统的设计方法;3、掌握峰值检测系统的性能指标和调试方法。

二、设计任务及要求1、任务:设计一个峰值检测系统;2、要求:(1)传感器输出0~5mV,对应承受力0~2000kg;(2)测量值要用数字显示,显示范围是0~1999;(3)测量的峰值的电压要稳定。

三、设计原理1、设计总体方案据分析,可确定需设计系统的电路原理框图如图1所示:图1 峰值检测系统原理框图2、各部分功能传感器:将被测信号量转换成电量;放大器:将传感器输出的小信号放大,放大器的输出结果满足模数转换器的转换范围;采样/保持:对放大后的被测模拟量进行采样,并保持峰值; 采样/保持控制电路:该电路通过控制信号实现对峰值采样,小于峰值时,保持原峰值,大于原峰值时保持新的峰值;A/D 转换:将模拟量转换成数字量; 译码显示:完成峰值数字量的译码显示;数字锁存控制电路:对模数转换的峰值数字量进行锁存,小于峰值的数字量不锁存。

三、电路设计1、传感器:本文不予考虑;2、放大器:由于输出信号为0~5mV ,1mV 对应400kg ,因此选用电压增益为400的差动放大电路(该电路精度高),如图2所示。

741741741u 1u 2u o1R 1R 2R 2R 3R 3R 4R 4+++---u i图2 差动放大电路根据公式 400R )/R 2R (1R u u A 3124i o1U =+-==,分配第一级放大器放大倍数为8/R 2R 112=+,分配第二级放大器放大倍数为508400R R 34==,则选取电阻值分别为 1.6K R 1=, 5.6K R 2=,2K R 3=,K 001R 4=,四只电阻均选1/8W金属膜电阻,三个放大器可选具有高输入共模电压和输入差模电压范围,具有失调电压调整能力以及短路保护等特点的μ741型运算放大器。

北京邮电大学电子电路综合设计实验报告课题名称:函数信号发生器的设计学院:信息与通信工程学院 班级:2013211123姓名:周亮学号:2013211123班内序号:9一、 摘要方波与三角波发生器由集成运放电路构成,包括比较器与RC积分器组成。

方波发生器的基本电路由带正反馈的比较器及RC组成的负反馈构成;三角波主要由积分电路产生。

三角波转换为正弦波,则是通过差分电路实现。

该电路振荡频率和幅度便于调节,输出方波幅度大小由稳压管的稳压值决定,方波经积分得到三角波;而正弦波发生电路中两个电位器实现正弦波幅度与电路的对称性调节,实现较理想的正弦波输出波形。

二、关键词: 函数信号发生器 方波 三角波 正弦波三、设计任务要求1.基本要求:设计制作一个函数信号发生器电路,该电路能够输出频率可调的正弦波、三角波和方波信号。

(1) 输出频率能在1-‐10KHz范围内连续可调,无明显失真。

(2) 方波输出电压Uopp=12V(误差小于20%),上升、下降沿小于10us。

(3) 三角波Uopp=8V(误差小于20%)。

(4) 正弦波Uopp1V,无明显失真。

2. 提高要求:(1) 输出方波占空比可调范围30%-‐70%。

(2) 三种输出波形的峰峰值Uopp均可在1V-‐10V内连续可调电源电路 方波-‐三角波发生电路 正弦波发生电路方波输三角波输正弦波输现输出信号幅度的连续调节。

利用二极管的单向导通性,将方波-‐三角波中间的电阻改为两个反向二极管一端相连,另一端接入电位器,抽头处输出的结构,实现占空比连续可调,达到信号发生器实验的提高要求。

五、分块电路和总体电路的设计过程1. 方波-‐三角波产生电路设计过程:①根据所需振荡频率的高低和对方波前后沿陡度的要求,选择电压转换速率S R合适的运算放大器。

方波要求上升、下降沿小于10us,峰峰值为12V。

LM741转换速率为0.7V/us,上升下降沿为17us,大于要求值。

电子系统设计综合实验指导书

(选择以下项目中的一项作为综合实验项目)。

项目一等精度频率计

一、课程设计目的

1、进一步熟悉QuartusⅡ的软件使用方法,熟悉keil软件使用;

2、熟悉单片机与可编程逻辑器件的开发流程及硬件测试方法;

3、掌握等精度频率计设计的基本原理。

4、掌握独立系统设计及调试方法,提高系统设计能力。

二、设计任务

利用单片机与FPGA设计一款等精度频率计,待测脉冲的检测及计数部分由FPGA实现,FPGA的计数结果送由单片机进行计算,并将最终频率结果显示在数码管上。

要求该频率计具有较高的测量精度,且在整个频率区域能保持恒定的测试精度,具体指标如下:

a)具有频率测试功能:测频范围100Hz~5MHz。

测频精度:相对误差恒为基准频率的万分之一。

b)具有脉宽测试功能:测试范围10μs~1s,测试精度:0.1μs。

c)具有占空比测试功能:测试精度1%~99%。

d)具有相位测试功能。

(注:任务a为基本要求,任务b、c、d为提高要求)

三、基本原理

基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,而且在整个频率区域能保持恒定的测试精度。

3.1 等精度测频原理

等精度频率计主控结构如图1所示。

图 1 等精度频率计主控结构 测频计测控时序如图2所示。

图 2 频率计测控时序

预置门控信号CL 选择为0.1~1s 之间(通过测试实验得出结论:CL 在这个范围内选择时间宽度对测频精度几乎没有影响)。

BZH 和TF 分别是2个高速计数器,BZH 对标准频率信号(频率为Fs )进行计数,设计数结果为Ns ;TF 对被测信号(频率为Fx )进行计数,计数结果为Nx ,则有

MUX64-8模块并不是必须的,可根据实际设计进行取舍。

分析测频计测控时序,着重分析START 的作用,完成等精度频率计设计。

3.2 FPGA 模块

FPGA 模块所要完成的功能如图1所示,由于单片机的速度慢,不能直接测量高频信号,所以使用高速FPGA 为测频核心。

100MHZ 的标准频率信号由FPGA 内部的PLL 倍频实现,待测信号TCLK 为方波,由信号发生器给出待测方波信号(注意:该方波信号带有直流偏置,没有负电压,幅值3.3V )。

预制门控信号CL 由单片机发出,BRNA 和ENA 分别是BZH 与TF 两个计数器的计数允许信号端。

FPGA 将允许计数时间内的BZH 、TF 的运行结果送入单片机进行最后的计算。

3.3 单片机模块

Ns

Fs Nx Fx //

单片机模块完成对整个测频系统的控制,包括对FPGA的控制以及数码管的显示控制。

测频允许信号由单片机发出,并且单片机的P0 口负责循环读取FPGA 发送过来的测频结果数据(BZH、TF两个计数器的计数结果,每次传送8位数据),P2负责发送控制信号,单片机可以通过结束信号了解测频记数是否结束,以确定何时开始读取数据。

四、整体系统设计

1、根据以上的原理介绍,按照设计任务要求,利用VHDL进行等精度频率计系

统的和核心程序设计,通过QuartusⅡ进行编辑、编译、综合、适配、仿真测试。

2、利用单片机实现等精度频率计的频率计算以及实时显示。

3、利用EDA最小系统板实现设计。

五、设计报告要求

1.说明数字等精度频率计的工作原理。

2.画出所设计的等精度频率计模块方框图,包括FPGA部分与单片机部分。

3. 结合频率计设计任务指标,记录频率测试指标,并进行误差分析计算。

4. 记录结果图形,并将电子档存档。

5.总结设计中遇到的问题,问题出现的原因及解决问题的方法。

六、实验设备

EDA最小系统板一块(康芯)、PC机一台、示波器一台、信号发生器一台、万用表一个。

项目二VGA彩色信号演示系统设计

一、课程设计目的

1、进一步熟悉QuartusⅡ的软件使用方法;

2、熟悉可编程逻辑器件的开发流程及硬件测试方法;

3、学习FPGA硬件资源的使用和控制方法;

4、掌握VGA时序控制的基本原理,掌握FPGA对液晶的显示控制,掌握状态

机的设计方法;

5、掌握图像显示原理;

6、掌握独立系统设计及调试方法,提高系统设计能力。

二、设计任务

利用FPGA设计VGA 彩色信号演示系统,该演示系统可演示彩条信号、图像信号。

具体任务为:

a)显示彩条信号,通过外部控制产生三种模式的显示变化,如表1-1所示。

表1 VGA 彩色信号显示控制器三种模式表

模式控制参数由外部按键输入,并将显示模式显示在LCD上。

例如:如果选择模式1,在VGA上显示了竖彩条,则在LCD上显示:“模式1:竖彩条”。

在VGA上显示相应的竖彩条。

b)显示图像信号,将像素点数据存于FPGA内部的RAM或ROM中,通过读取RAM或ROM来获得图像数据,将图像数据进行VGA时序控制(时序控制利用状态机进行编写),并送入VGA进行显示,同时在LCD上显示“显示模式4:图像名称”。

c)将VGA的时序控制固化为VGA显示控制IP核,方便移植调用。

(注:任务a为基本要求,任务b、c为提高要求)

三、基本原理

VGA工业标准要求的频率如下:

●时钟频率:25.175MHZ(像素输出的频率)。

●行频:31469HZ。

●场频:59.96HZ。

设计VGA图像显示控制要注意两个问题:一个是时序驱动,这是完成设计的关键。

时序稍有偏差,显示必然不正常;另一个是VGA信号的电平驱动。

3.1 VGA显示原理

VGA 彩色显示器(640X480/60Hz)在显示过程中除R、G、B 三基色信号外,还有同步HS信号和场同步VS 信号。

在显示器显示过程中,HS 和VS 极性可正可负,其极性转换逻辑在显示器内自动切换。

以正极性为例,R、G、B 信号为正极性信号,并高电平有效,当VS=0、HS=0,CRT显示的内容为亮的过程,当一行扫描完毕,行同步HS=1,这时的VGA显示器扫描产生消隐及电子束回到VGA 显示器的左边下一行的起始位置(X=0 Y=1);当扫描完480 行后,VGA 显示器的场同步VS=1,产生场同步使扫描线回到VGA 显示器的第一行第一列(X=0 Y=0,约为2 个行周期)。

行、场扫描示意图如图1所示。

时序要求如表2所示。

图1 VGA行扫描、场扫描时序示意图

表2 行、场扫描时序要求

3.2 FPGA模块

FPGA完成的功能模块如图2所示。

图2 FPGA模块框图

VGA显示控制模块完成对VGA的时序控制,以驱动CRT进行彩条显示;LCD显示控制模块完成对LCD_16207的显示控制,驱动LCD_16207进行汉字显示,增强可读性。

四、主要步骤

1、编写相应程序,编译、仿真、绑定管脚、下载程序,在

GX-SOPC-EDA-EP2C8-STARTER-EDK开发板上实现。

2、4个跳线器连接在F1_SW1_JP1(1-2),F1_SW1_JP2(1-2),F1_SW1_JP3(1-2),

F1_SW1_JP4(1-2)状态,这样可以使用SW1A,SW2A,SW3A,SW4A。

3、SW4A 为复位信号,按下复位时屏幕显示为黑色;

4、SW4A 为高,正常工作,改变SW1A、SW2A 为01,11,10 三种输出方式,在

VGA 显示器上输出三种图形,并将模式方式显示在LCD上。

五、设计报告要求

1.说明VGA显示器的工作原理,主要是时序控制原理。

2.画出所设计的VGA控制器方框图,分析设计的时序是如何实现的。

3. 记录引脚配置结果。

4. 记录结果图形,并将电子档存档。

5.总结设计中遇到的问题,问题出现的原因及解决问题的方法。

六、实验设备

EDA最小系统板一块(革新GX-SOPC-EDA-EP2C8-STARTER-EDK)、PC 机一台、示波器一台、万用表一个。