数字集成电路课后习题1-4章作业解析

- 格式:pdf

- 大小:249.91 KB

- 文档页数:13

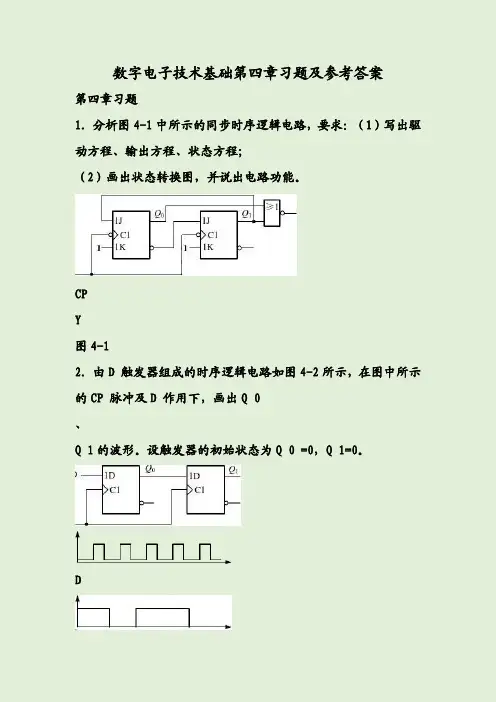

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

第一章 信号发生电路题4.1.1 一个负反馈放大器产生自激振荡的相位条件为πϕ)12(+=n AF ,而正弦振荡器中的相位平衡条件是πϕn AF 2=,这里有无矛盾?题4.1.2 振荡器的幅度平衡条件为1=F A,而起振时,则要求1>F A ,这是为什么? 题4.1.3 RC 桥式正弦振荡器如图题4.1.3所示,其中二极管在负反馈支路内起稳幅作用。

(1) 试在放大器框图A 内填上同相输入端(+)和反相输入端(—)的符号,若A 为μA741型运放,试注明这两个输入端子的管脚号码。

(2) 如果不用二极管,而改用下列热敏元件来实现稳幅:(a )具有负温度系数的热敏电阻器;(b )具有正温度系数的钨丝灯泡。

试挑选元件(a )或(b )来替代图中的负反馈支路电阻(R 1或R 3),并画出相应的电路图。

解:(1) RC 桥式正弦振荡器中,由于RC 串并联网络在f=f o 时,其相移φAF =0,为满足相位条件:φAF =φA +φF =0,放大器必须接成同相放大器,因此与RC 串并联网络连接的输入端为(+),与负反馈支路连接的输入端为(-),若A 为A741,其管脚号为:反相输入端为2,同相输入端为3。

(2) (a)负温度系数的热敏电阻取代R 3; (b)正温度系数的钨丝灯泡取代R 1。

图题4.1.3题4.1.4 试用相位平衡条件判别图题4.1.4所示各振荡电路。

(1) 哪些可能产生正弦振荡,哪些不能?(注意耦合电容C b 、C e 在交流通路中可视作短路。

)(2) 对哪些不能满足相位平衡条件的电路,如何改变接线使之满足相位平衡条件?(用电路图表示。

)解:(1) 不满足相位平衡条件。

(2) 电路(b)中,通过切环与瞬时极性法,可判断该电路不满足相位平衡条件。

而将反馈信号引入T 1基极时,即可满足相位平衡条件。

(3) 由电路(c)中的瞬时极性可知,该电路满足相位平衡条件。

图题4.1.4题4.1.5 电路如图题4.1.5所示,稳压管D z 起稳幅作用,其稳定电压±V Z =±6V 。

《数字集成电路基础》作业答案第一次作业1、查询典型的TTL与CMOS系列标准电路各自的VIH、VIL、VOH和VOL,注明资料出处。

2、简述摩尔定律的内涵,如何引领国际半导体工艺的发展。

第二次作业1、说明CMOS电路的Latch Up效应;请画出示意图并简要说明其产生原因;并简述消除“Latch-up”效应的方法。

答:在单阱工艺的MOS器件中(P阱为例),由于NMOS管源与衬底组成PN结,而PMOS 管的源与衬底也构成一个PN结,两个PN结串联组成PNPN结构,即两个寄生三极管(NPN 和PNP),一旦有因素使得寄生三极管有一个微弱导通,两者的正反馈使得电流积聚增加,产生自锁现象。

影响:产生自锁后,如果电源能提供足够大的电流,则由于电流过大,电路将被烧毁。

消除“Latch-up”效应的方法:版图设计时:为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;工艺设计时:降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。

为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。

工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数;具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。

2、什么是器件的亚阈值特性,对器件有什么影响?答:器件的亚阈值特性是指在分析MOSFET时,当Vgs<Vth时MOS器件仍然有一个弱的反型层存在,漏源电流Id并非是无限小,而是与Vgs呈现指数关系,这种效应称作亚阈值效应。

影响:亚阈值导电会导致较大的功率损耗,在大型电路中,如内存中,其信息能量损耗可能使存储信息改变,使电路不能正常工作。

3、什么叫做亚阈值导电效应?并简单画出logI D-V GS特性曲线。

答:GS在分析MOSFET时,我们一直假设:当V GS下降到低于V TH时器件会突然关断。

第一章数字逻辑习题1.1 数字电路与数字信号图形代表的二进制数1.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%数制将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)解:(2)(127)D= 27 -1=()B-1=(1111111)B=(177)O=(7F)H(4)()D=B=O=H二进制代码将下列十进制数转换为 8421BCD 码:(1)43 (3)解:(43)D=(01000011)BCD试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为 0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为 1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本 1111001,1101111,1110101,对应的十六进制数分别为 79,6F,75(4)43 的ASCⅡ码为 0110100,0110011,对应的十六紧张数分别为 34,33逻辑函数及其表示方法在图题 1. 中,已知输入信号 A,B`的波形,画出各门电路输出 L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

用逻辑代数定律证明下列等式(3)A+ABC ACD C D E A CD E++ +( ) = + +解:A+ABC ACD C D E++ +( )=A(1+BC ACD CDE)+ += +A ACD CDE+= +A CD CDE+ = +A CD+ E用代数法化简下列各式 (3)ABC B( +C)解:ABCB( +C)= + +(A B C B C)( + )=AB AC BB BC CB C+ + + + +=AB C A B B+ ( + + +1)=AB C+(6)(A + + + +B A B AB AB ) ( ) ( )() 解:(A + + + +B A B AB AB ) () ( )( )= A B ⋅+ A B ⋅+(A + B A )(+ B )=AB(9)ABCD ABD BCD ABCBD BC + + + +解:ABCD ABD BCD ABCBD BC +++ +=ABC D D ABD BC D C ( + +) + ( + ) =B AC AD C D ( + + + ) =B A C AD ( + + + ) =B A C D ( + + ) =AB BC BD + +画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门B AB AB = + + AB B = + A B = +(1)L AB AC =(2) ( ) L DAC = +已知函数L (A ,B ,C ,D )的卡诺图如图所示,试写出函数L 的最简与或表达式用卡诺图化简下列个式(3) ( )() L ABCD=+ +解: ( , , , ) L ABCDBCDBCDBCDABD = + + +(1)ABCD ABCD AB AD ABC+ + + +解:ABCD ABCD AB AD ABC+ + + +=ABCD ABCD ABC C D D AD B B C C ABC D D++ ( + )( + +)( + )( + +)( + )=ABCD ABCD ABCD ABCD ABCD ABCD ABCD+ + + + + +(6)L A B C D( , , , )=∑m(0,2,4,6,9,13)+∑d(1,3,5,7,11,15)解:L= +A D(7)L A B C D( , , , )=∑m(0,13,14,15)+∑d(1,2,3,9,10,11)解:L AD AC AB= + +已知逻辑函数L AB BC CA=+ + ,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表用摩根定理将与或化为与非表达式L = AB + BC + AC = AB BC AC ⋅ ⋅4>由已知函数的与非-与非表达式画出逻辑图2> 由真值表画出卡诺图3> 由卡诺图,得逻辑表达式 LABBCAC = + +第三章习题MOS 逻辑门电路根据表题所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。

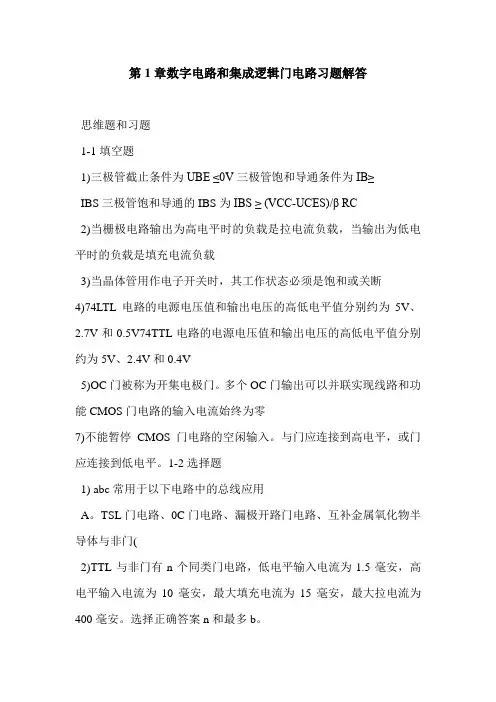

第1章数字电路和集成逻辑门电路习题解答思维题和习题1-1填空题1)三极管截止条件为UBE ≤0V三极管饱和导通条件为IB≥IBS三极管饱和导通的IBS为IBS ≥ (VCC-UCES)/β RC2)当栅极电路输出为高电平时的负载是拉电流负载,当输出为低电平时的负载是填充电流负载3)当晶体管用作电子开关时,其工作状态必须是饱和或关断4)74LTL电路的电源电压值和输出电压的高低电平值分别约为5V、2.7V和0.5V74TTL电路的电源电压值和输出电压的高低电平值分别约为5V、2.4V和0.4V5)OC门被称为开集电极门。

多个OC门输出可以并联实现线路和功能CMOS门电路的输入电流始终为零7)不能暂停CMOS门电路的空闲输入。

与门应连接到高电平,或门应连接到低电平。

1-2选择题1) abc常用于以下电路中的总线应用A。

TSL门电路、0C门电路、漏极开路门电路、互补金属氧化物半导体与非门(2)TTL与非门有n个同类门电路,低电平输入电流为1.5毫安,高电平输入电流为10毫安,最大填充电流为15毫安,最大拉电流为400毫安。

选择正确答案n和最多b。

a . n = 5b . n = 10c . n = 20d . n = 403)与TTL数字集成电路相比,CMOS数字集成电路的突出优势是ACD A。

当三极管用作开关时,为了提高开关速度,da .降低饱和深度b .增加饱和深度c .采用有源漏极电路d .采用反饱和三极管5)进行TTL与非门空闲输入处理,可以使用ABDa。

连接到电源b,连接到电源c,连接到地d,通过电阻3kω并联连接到有用输入6)。

光盘可以在以下电路中实现“线和”功能当A与非门b三态输出门c打开集电极门d打开漏极门7)三态门输出高阻抗状态时,ABD是正确的a .使用电压表测量指针不动b .相当于暂停c .电压不是高或低d .测量电阻指针不动8)已知正向电压降UD = 1.7V,参考工作电流ID = 10mA,TTL门的输出高和低电平分别为UOH = 3.6V,UOL = 0.3V,允许充电电流和牵引电流分别为IOL = 15mA,IOH = 4mA那么电阻r应该选择d。

P4.1. Problem should refer to Figure P4.2.a. All inverters but the CMOS inverter consume static power then the output is high.Notice that in the first three inverters when the input is high, there is always a directconnection from V DD to G ND .b. None of the static inverters consumes power when the input is low because there is nopath from V DD to G ND .c. All inverters but the saturated enhancement inverter has a V OH of 1.2 V.d. Only the CMOS inverter has a V OL of 0 V.e. Except for the CMOS inverter, all the other inverte rs’ functionality depend on therelative sizes of the transistors.P4.2. Problem should refer to Figure P4.1a. Resistive loadb. Saturated-enhancement loadIterate to produce:To compute V OL we can ignore body effect and equate currents:Solve for 0.03OL V V ≈c. Linear-enhancement loadIterate to produce:This tells us that V GG should have been above 1.6V <closer to 1.7 V>.To compute V OL we can ignore body effect and equate currents. Note that the load issaturated even though we call it a linear-enhancement load. The driver is alsosaturated due to the device sizes used.Solve for 0.69V OL V ≈d. CMOSP4.3. For this problem, you are required to use the formulae:We already know that V OH =1.2 V and V OL =0 V. For V S use:Next V IL and V IH are estimated as follows:ThereforeWhen we cut the size of the PMOS device in half, the VTC shifts to the left. So V IL , V S , and V IH will all shift to the left. The recalculation of the switching threshold produces V S =0.566V. We can compute V IL to be roughly 0.533V and V IH to be roughly 0.667V.ThereforeP4.4. Similar approach as in P4.3. Run SPICE to check results.P4.5. First, set up the equation.Now solve for χ.This implies that a very large <W/L>P is needed to reach the desired value. It also reveals the limitations of the models. SPICE would be needed to obtain an acceptable solution if the switching threshold of 0.9V is truly desired.P4.6. SPICEP4.7. The advantages of the pseudo-PMOS is that it can reach a V OH of V DD while the pseudo-NMOS V OH can never reach that value. Additionally, the pseudo-NMOS’s V OH dependson the relative sizings of the inverters.The disadvantage is the dual of its advantage. The pseudo-PMOS inverter can never reach a V OL of 0 V. In addition, the pseudo-PMOS device will have to be approximately twice as large as a pseudo-NMOS device with comparable characteristics. This is due to the unequal mobility of holes and electrons. The pseudo-PMOS’s NMOS pull -down device is twice as strong as the pseudo-NMOS’s PMOS pull -up device, that means that the pseudo-PMOS’s PMOS wi ll have to be bigger than the NMOS device in a pseudo-NMOS.P4.8. a> Circuit is a buffer with degraded outputs.Output swing calculation:When IN DD V V =, output voltage is OH DD TN V V V =-. Since the source of NMOS transistor is not connected to substrate <ground>, we must take into account body effect.When 0IN V V =, output voltage is ||OL TP V V =. Since the source of PMOS transistor is not connected to substrate <V DD >, we must take into account body effect.Therefore the output swing is DD TN V V - to ||TP V with full accounting for body effect.b> Assume that the input is at 0 and the output is at |V TP |. As the input is increased, the output will stay constant until the NMOS device turns on. That will occur at V IN =|V TP |+V TN . The upper transistor behaves as a source follower and will pull the output along as the input rises until the output reaches V DD -V TN . However, as the input is reduced in value the output stays at its highvalue until the PMOS device turns on. This occurs at V IN=V DD-< |V TP|+V TN>. Then the PMOS device acts as a source follower and the output drops linearly to |V TP| as the input is reduced.c> The gain of the circuit is close to unity but slightly below this value. The circuit has poor noise rejection properties as it lacks the regenerative properties <this is a consequence of low gain>.d> SPICE run.P4.9.Resistive Load inverter:Saturated Enhancement Load inverter <ignoring body-effect>:Linear Enhancement Load inverter <ignoring body-effect>:The linear enhancement load inverter requires the largest pull-down device since it has the strongest pull up device. The resistive load inverter is next and the saturated enhancement load requires the smallest pull-down device.P4.10.We will illustrate the process and estimate the solutions for this problem.We already know that V OH=1.2 V and V OL=0 V. For V S use:Next V IL and V IH are estimated as follows:We can compute V IL to be roughly 0.533V.We can compute V IH to be roughly 0.667V.When we double the size of the PMOS device, the VTC shifts to the right. So V IL, V S, and V IH will all shift to the right. The recalculation of the switching threshold produces V S=0.6V.We can compute V IL to be roughly 0.55V and V IH to be roughly 0.65V.P4.11.The peak current would occur when both devices are in saturation and when V out=V in=V S.We can easily compute V S as:P4.12.As the required V OL becomes smaller, the W D/W L ratio becomes larger.P4.13.SPICEP4.14.The expression for the switching threshold of a CMOS inverter is:Solving for χ.Now solving for the ratio of sizes.Solving for χ.Now solving for the ratio of sizes.In the first case <0.6S DD V V >, the PMOS is much larger than the NMOS, so t PLH issmaller and t PHL is larger. The reverse is true for the second case.P4.15 <a> It does not have the regenerative property since the gain is less than one.<b> The last inverter would have an output of about 0.8V.<c> It is not possible to define the noise margin for this gate. Even a properinput eventually produces the incorrect output.P4.16 Both gates would work as a tristate buffer. However, as we shall find out in Chapter 7, the second one is prone to charge-sharing. That is, when the output is high and the EN signal is low, if the input goes high, the output may drop slightly in value due to loss of charge to the adjacent internal node.。

CH11.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律?晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。

MOORE定律2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。

拥有设计人才和技术,但不拥有生产线。

特点:电路设计,工艺制造,封装分立运行。

环境:IC产业生产能力剩余,人们需要更多的功能芯片设计3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义?MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。

意义:降低成本。

4.集成电路设计需要哪四个方面的知识?系统,电路,工具,工艺方面的知识CH21.为什么硅材料在集成电路技术中起着举足轻重的作用 ?原材料来源丰富,技术成熟,硅基产品价格低廉2.GaAs和InP材料各有哪些特点? P10,11 3.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触?接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触4.说出多晶硅在CMOS工艺中的作用。

P13 5.列出你知道的异质半导体材料系统。

GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6.SOI材料是怎样形成的,有什么特点?SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。

特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低7. 肖特基接触和欧姆型接触各有什么特点?肖特基接触:阻挡层具有类似PN结的伏安特性。

欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。

8. 简述双极型晶体管和MOS晶体管的工作原理。

P19,21CH31.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。

意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。

外延方法:液态生长,气相外延生长,金属有机物气相外延生长2.写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制造方法。

习题参考答案注:参考答案,并不是唯一答案或不一定是最好答案。

仅供大家参考。

第一章习题2. C B A D B A C B A F ⋅⋅+⋅⋅+⋅⋅=3. 设:逻辑变量A 、B 、C 、D 分别表示占有40%、30%、20%、10%股份的四个股东,各变量取值为1表示该股东投赞成票;F 表示表决结果,F =1表示表决通过。

F =AB +AC +BCD4. 设:A 、B 开关接至上方为1,接至下方为0;F 灯亮为1,灯灭为0。

F =A ⊙B5. 设:10kW 、15kW 、25kW 三台用电设备分别为A 、B 、C ,设15kW 和25kW 两台发电机组分别为Y 和Z ,且均用“0”表示不工作,用“1”表示工作。

C AB Z BA B A Y ⋅=⋅=6.输入为余3码,用A 、B 、C 、D 表示,输出为8421BCD 码,用Y 0、Y 1、Y 2、Y 3表示。

D C A B A Y CB DC BD B Y DC Y DY ⋅⋅+⋅=⋅+⋅⋅+⋅=⊕==32107. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时为1,灯灭时为0;输出用F 表示,灯正常工作时为0,灯出现故障时为1。

C A B A C B A F ⋅+⋅+⋅⋅=8. D C B D A H DC B AD C B A D C B A D C B A G DC B AD C A B A F DC B A E ⋅⋅+⋅=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅⋅+⋅⋅+⋅=⋅⋅⋅=第二章习题1. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时其值为1,灯灭时其值为0;输出报警信号用Y 表示,灯正常工作时其值为0,灯出现故障时其值为1。

AC AB C B A Y ⋅⋅=2. 设:烟、温度和有害气体三种不同类型的探测器的输出信号用A 、B 、C 表示,作为报警信号电路的输入,有火灾探测信号时用1表示,没有时用0表示。

报警信号电路的书躇用Y 表示,有报警信号时用1表示,没有时用0表示。

CH11.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律?晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。

MOORE定律2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。

拥有设计人才和技术,但不拥有生产线。

特点:电路设计,工艺制造,封装分立运行。

环境:IC产业生产能力剩余,人们需要更多的功能芯片设计3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义?MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。

意义:降低成本。

4.集成电路设计需要哪四个方面的知识?系统,电路,工具,工艺方面的知识CH21.为什么硅材料在集成电路技术中起着举足轻重的作用 ?原材料来源丰富,技术成熟,硅基产品价格低廉2.GaAs和InP材料各有哪些特点? P10,11 3.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触?接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触4.说出多晶硅在CMOS工艺中的作用。

P13 5.列出你知道的异质半导体材料系统。

GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6.SOI材料是怎样形成的,有什么特点?SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。

特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低7. 肖特基接触和欧姆型接触各有什么特点?肖特基接触:阻挡层具有类似PN结的伏安特性。

欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。

8. 简述双极型晶体管和MOS晶体管的工作原理。

P19,21CH31.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。

意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。

外延方法:液态生长,气相外延生长,金属有机物气相外延生长2.写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制造方法。

第4章 集成运算放大电路一 填空题1、集成运放内部电路通常包括四个基本组成部分,即、、和。

2、为提高输入电阻,减小零点漂移,通用集成运放的输入级大多采用_________________电路;为了减小输出电阻,输出级大多采用_________________ 电路。

3、在差分放大电路发射极接入长尾电阻或恒流三极管后,它的差模放大倍数ud A 将 ,而共模放大倍数将 ,共模抑制比将 。

uc A CMR K 4、差动放大电路的两个输入端的输入电压分别为和,则差模mV 8i1-=U mV 10i2=U 输入电压为 ,共模输入电压为 。

5、差分放大电路中,常常利用有源负载代替发射极电阻,从而可以提高差分放大电e R 路的 。

6、工作在线性区的理想运放,两个输入端的输入电流均为零,称为虚______;两个输入端的电位相等称为虚_________;若集成运放在反相输入情况下,同相端接地,反相端又称虚___________;即使理想运放器在非线性工作区,虚_____ 结论也是成立的。

7、共模抑制比K CMR 等于_________________之比,电路的K CMR 越大,表明电路__________越强。

答案:1、输入级、中间级、输出级、偏置电路;2、差分放大电路、互补对称电路;3、不变、减小、增大;4、-18mV, 1mV ;5、共模抑制比;6、断、短、地、断;7、差模电压放大倍数与共模电压放大倍数,抑制温漂的能力。

二 选择题1、集成运放电路采用直接耦合方式是因为_______。

A .可获得很大的放大倍数B .可使温漂小C .集成工艺难以制造大容量电容2、为增大电压放大倍数,集成运放中间级多采用_______。

A . 共射放大电路 B. 共集放大电路 C. 共基放大电路3、输入失调电压U IO 是_______。

A .两个输入端电压之差B .输入端都为零时的输出电压C .输出端为零时输入端的等效补偿电压。

第一章 放大电路的动态和频响分析题 对于放大电路的性能指标,回答下列问题:(1) 已知某放大电路第一级的电压增益为40dB ,第二级的电压增益为20dB ,总的电压增益为多少dB(2) 某放大电路在负载开路时输出电压为4V ,接入3 k Ω的负载电阻后输出电压降为3V ,则该放大电路的输出电阻为多少(3) 为了测量某CE 放大电路的输出电压,是否可以用万用表的电阻档直接去测输出端对地的电阻解:(1) 60 dB ;(2) 1 k Ω;(3) 不可以。

题 一学生用交流电压表测得某放大电路的开路输出电压为,接上24 k Ω的负载电阻后测出的电压值为4V 。

已知电压表的内阻为120 k Ω。

求该放大电路的输出电阻R o 和实际的开路输出电压V oo 。

】解:由题意列方程组: 420208.4120120=+⋅=+⋅o DD o BB R V R V解得:V 5k 5=Ω=OO o V R ,题 在图题所示CS 放大电路中,已知静态工作点为V GSQ =,I DQ =2mA ,V DSQ =5V ,R s =3kΩ。

设电压放大倍数为vA =-20,发生截止失真时输出电压的正向幅值为5V ,发生饱和失真时输出电压的负向幅值为3V 。

(1) 当输入信号为v i =ωt (V)时,画出g 、d 点的电压波形v G 、v D ,并标出峰、谷电压的大小;(2) 当输入信号为v i =ωt (V)时,画出g 、d 点的电压波形v G 、v D ,并标出峰、谷电压的大小。

图题解:(1) 当v i =ωt (V)时,栅极的静态电压为:V 5.5325.0=⨯+-=+=s DQ GSQ GQ R I V V栅极的瞬态电压为:(V)t 0.1sin 5.5ω+=+=i GQ G v V v|漏极的瞬态电压为:(V) sin 211sin 1.0)20(325t t v A R I V v V v V v iv s DQ DSQ o DQ d DQ D ω-=ω⨯-+⨯+=++=+=+=因此,v G 、v D 电压波形如图(a )所示。

《数字电子技术基础》课后习题答案《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:1.3、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10所以:(45C)16=(10001011100)2=(2134)8=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:(6DE.C8)16=6*162+13*161+14*160+13*16-1+8*16-2=(1 758.78125)10所以:(6DE.C8)16=(011011011110. 11001000)2=(3336.62)8=(1758.78125)10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*1 6-2=(2302.98828125)10所以:(8FE.FD)16=(100011111110.11111101)2=(4376.772)8=(2302.98828125)10(4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16 -2=(1950. 98828125)10所以:(8FE.FD)16=(011110011110.11111101)2=(3636.772)8=(1 950.98828125)101.5、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD (45.36)10=(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10=(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10=(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD1.8、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则二、2、×4、×三、1、B3、D5、C练习题:2.2:(4)解:Y=AB̅+BD+DCE+A̅D=AB̅+BD+AD+A̅D+DCE=AB̅+BD+D+DCE=AB̅+D (B +1+CE ) =AB̅+D (8)解:Y =(A ̅+B ̅+C ̅)(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅(A ̅+B ̅+C ̅+DE ) =[(A ̅+B ̅+C ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅+(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅](A ̅+B ̅+C ̅+DE ) =(ABC +DE )(ABC ̅̅̅̅̅̅+DE ) =DE 2.3:(2)证明:左边=A +A ̅(B +C)̅̅̅̅̅̅̅̅̅̅̅̅ =A +A ̅+(B +C)̅̅̅̅̅̅̅̅̅̅=A +B̅C ̅ =右式所以等式成立(4)证明:左边= (A̅B +AB ̅)⨁C = (A̅B +AB ̅)C ̅+ (A ̅B +AB ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅C = (A ̅BC ̅+AB ̅C ̅)+A ̅B ̅̅̅̅⋅AB̅̅̅̅̅⋅C =A̅BC ̅+AB ̅C ̅+(A +B ̅)(A ̅+B )C =A̅BC ̅+AB ̅C ̅+(AB +A ̅B ̅)C =A̅BC ̅+AB ̅C ̅+ABC +A ̅B ̅C 右边= ABC +(A +B +C )AB ̅̅̅̅⋅BC ̅̅̅̅⋅CA̅̅̅̅ =ABC +(A +B +C )[(A̅+B ̅)(B ̅+C ̅)(C ̅+A ̅)] =ABC +(A +B +C )(A̅B ̅+A ̅C ̅+B ̅+B ̅C ̅)(C ̅+A ̅)=ABC +(A +B +C )(A̅B ̅C ̅+A ̅C ̅+B ̅C ̅+A ̅B ̅) =ABC +AB̅C ̅+A ̅BC ̅+A ̅B ̅C 左边=右边,所以等式成立 2.4(1)Y ′=(A +B ̅C ̅)(A ̅+BC) 2.5(3)Y ̅=A ̅B ̅(C ̅+D ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ C ̅D ̅(A ̅+B ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ 2.6:(1)Y =AB +AC +BC=AB (C +C̅)+AC (B +B ̅)+BC (A +A ̅) =ABC +ABC ̅+AB ̅C +A ̅BC 2.7:(1)Y =A ̅B ̅+B ̅C ̅+AC +B ̅C 卡诺图如下: B C A 00 0111100 1 1 1111所以,Y=B̅+AC2.8:(2)画卡诺图如下:B C A 0001 11 100 1 1 0 11 1 1 1 1Y(A,B,C)=A+B̅+C̅2.9:(1)画Y(A,B,C,D)=∑m(0,1,2,3,4,6,8)+∑d(10,11,12,13,14)如下:CDAB00 01 11 1000 1 1 1 101 1 111 ×××10 1 ××Y (A,B,C,D )=A̅B ̅+D ̅ 2.10:(3)解:化简最小项式: Y =AB +(A̅B +C ̅)(A ̅B ̅+C ) =AB +(A̅B A ̅B ̅+A ̅BC +A ̅B ̅C ̅+C ̅C ) =AB (C +C̅)+A ̅BC +A ̅B ̅C ̅ =ABC +ABC ̅+A ̅BC +A ̅B ̅C ̅ =∑m (0,3,6,7)最大项式:Y =∏M(1,2,4,5) 2.13:(3)Y =AB̅+BC ̅+AB ̅C ̅+ABC ̅D ̅ =AB̅(1+C ̅)+BC ̅(1+AD ̅) =AB̅+BC ̅ =AB̅+BC ̅̿̿̿̿̿̿̿̿̿̿̿̿ = AB̅̅̅̅̅∙BC ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅技能题:2.16 解:设三种不同火灾探测器分别为A 、B 、C ,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:B C A 00 01 11 10 0 0 0 1 0 1 0 1 1 1Y =AB +AC +BC=AB +AC +BC ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿=AB ̅̅̅̅⋅AC ̅̅̅̅⋅BC ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=(A ̅+B ̅)(A ̅+C ̅)(B ̅+C ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅+B ̅̅̅̅̅̅̅̅̅+A ̅+C ̅̅̅̅̅̅̅̅̅+B ̅+C ̅̅̅̅̅̅̅̅̅第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空;二、1、√8、√;三、1、A4、D练习题:3.2、解:(a)因为接地电阻4.7k Ω,开门电阻3k Ω,R>R on ,相当于接入高电平1,所以Y =A ̅B ̅1̅̅̅̅̅̅=A +B +0=A +B(e) 因为接地电阻510Ω,关门电0.8k Ω,R<R off ,相当于接入高电平0,所以、Y =A +B +0̅̅̅̅̅̅̅̅̅̅̅̅̅=A̅⋅B ̅∙1̅̅̅̅̅̅̅̅̅̅=A +B +0=A +B3.4、解:(a) Y1=A+B+0̅̅̅̅̅̅̅̅̅̅̅̅̅=A+B̅̅̅̅̅̅̅̅(c) Y3=A+B+1̅̅̅̅̅̅̅̅̅̅̅̅̅=1̅=0(f) Y6=A⋅0+B⋅1̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=B̅3.7、解:(a) Y1=A⨁B⋅C=(A̅B+AB̅)C=A̅BC+AB̅C3.8、解:输出高电平时,带负载的个数2020400===IHOHOH I I NG 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===ILOLOL I I NG 反相器可带17个同类反相器3.12EN=1时,Y 1=A , Y 2=B ̅EN=0时,Y 1=A ̅, Y 2=B3.17根据题意,设A为具有否决权的股东,其余两位股东为B、C,画卡诺图如下,BCA00 01 11 100 0 0 0 01 0 1 1 1则表达结果Y的表达式为:Y=AB+AC=AB+AC̿̿̿̿̿̿̿̿̿̿̿̿=AB̅̅̅̅⋅AC̅̅̅̅̅̅̅̅̅̅̅̅̅̅逻辑电路如下:技能题:3.20:解:根据题意,A、B、C、D变量的卡诺图如下:CD AB00 01 11 1000 0 0 0 001 0 0 0 011 0 1 1 110 0 0 0 0Y =ABC +ABD =ABC +ABD ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿=ABC ̅̅̅̅̅̅⋅ABD ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、3、√4、√三、5、A7、C练习题:4.1;解:(a) Y =A⨁B +B ̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅B +AB ̅+B ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅B +B ̅̅̅̅̅̅̅̅̅̅̅=A ̅+B̅̅̅̅̅̅̅̅̅=AB ,所以电路为与门。

第 1 章习题答案1-1 .按照集成度分类,试分析以下集成器件属于哪种集成度器件:( 1)触发器;( 2)中央处理器;( 3)大型存储器; ( 4)单片计算机; ( 5)多功能专用集成电路; ( 6)计数器;( 7 )可编程逻辑器件。

解:( 1)小规模;( 2)大规模;( 3)超大规模;( 4)超大规模;( 5)甚大规模;( 6)中规模;( 7)甚大规模。

1-2 .将下列十进制数转换为二进制数、八进制数和十六进制数。

( 1) 45( 2) 78( 3) 25.125 ( 4) 34.25 ( 5)65 ( 6) 126解 :( 1 ) (45) 10=(101101) 2=(55) 8=(2D) 16 ( 2 ) (78) 10=(1111000) 2=(170) 8=(78) 16 ( 3 ) (25.125) 10=(11001.001)2=(170.1) 8=(78.2)16( 4 ) (34.25) 10 =(100010.01) 2=(42.2) 8=(22.4)16( 5) (65) 10=(1100101) 2=(145) 8=(65) 16 ( 6) (126) 10=(1111110) 2=(176) 8=(7E) 16 1-3 .将下列十六进制数转换为二进制数和十进制数。

解:(1)(49) 16=(1001001) 2=(73) 10(2)(68) 16=(1101000) 2=(104) 10( 3)(22.125) 16=(1100101) 2=(145) 10( 4 ) (54.25) 16=(1010100.00100101) 2=(84.14453125) 10 ( 5 ) (35) 16=(110101) 2=(53) 10 ( 6 ) (124) 16=(100100100) 2=(292) 101-4 .将下列八进制数转换为二进制数和十进制数。

解:( 1)(27) =(010111) =(23) ( 2)(56) =(101110) =(46) (3)(12.34) =(1010.011100) =(10.4375)108210 82 10 82( 4 ) (74.25)8 =(111100.010101) =(84.328125)10 ( 5 ) (35) 8=(11101) 2=(29)10( 6 )2(124) 8=(1010100) 2=(84) 101-5 .将下列二进制数转换为十六进制数、八进制和十进制数。