第七章 半导体存储器习题

- 格式:doc

- 大小:399.50 KB

- 文档页数:3

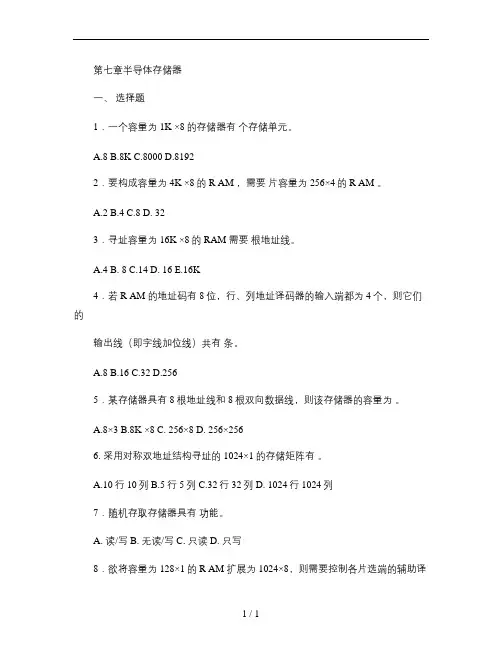

第七章半导体存储器一、选择题1.一个容量为1K ×8的存储器有个存储单元。

A.8B.8KC.8000D.81922.要构成容量为4K ×8的R AM ,需要片容量为256×4的R AM 。

A.2B.4C.8D. 323.寻址容量为16K ×8的RAM 需要根地址线。

A.4B. 8C.14D. 16E.16K4.若R AM 的地址码有8位,行、列地址译码器的输入端都为4个,则它们的输出线(即字线加位线)共有条。

A.8B.16C.32D.2565.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

A.8×3B.8K ×8C. 256×8D. 256×2566. 采用对称双地址结构寻址的1024×1的存储矩阵有。

A.10行10列B.5行5列C.32行32列D. 1024行1024列7.随机存取存储器具有功能。

A. 读/写B. 无读/写C. 只读D. 只写8.欲将容量为128×1的R AM 扩展为1024×8,则需要控制各片选端的辅助译码器的输出端数为。

A.1B.2C.3D. 89.欲将容量为256×1的R AM 扩展为1024×8,则需要控制各片选端的辅助译码器的输入端数为。

A.4B.2C.3D. 810.只读存储器ROM 在运行时具有功能。

A. 读/无写B. 无读/写C. 读/写D. 无读/无写11.只读存储器R OM 中的内容,当电源断掉后又接通,存储器中的内容。

A. 全部改变B. 全部为0C. 不可预料D. 保持不变12.随机存取存储器RAM 中的内容,当电源断掉后又接通,存储器中的内容。

A. 全部改变B. 全部为1C. 不确定D. 保持不变13.一个容量为512×1的静态RAM 具有。

A. 地址线9根,数据线1根B. 地址线1根,数据线9根C. 地址线512根,数据线9根D. 地址线9根,数据线512根14.用若干R AM 实现位扩展时,其方法是将相应地并联在一起。

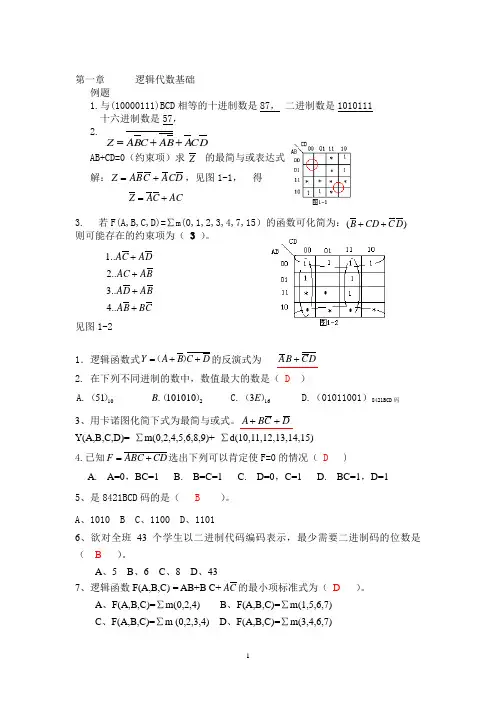

第一章 逻辑代数基础 例题1.与(10000111)BCD 相等的十进制数是87, 二进制数是1010111 十六进制数是57,2.AB+CD=0(约束项)求 的最简与或表达式。

解:D C A C B A Z +=,见图1-1, 得3.若F(A,B,C,D)=∑m(0,1,2,3,4,7,15)的函数可化简为: 则可能存在的约束项为( 3 )。

见图1-21.逻辑函数式Y A B C D =++()的反演式为 D C B A + 2. 在下列不同进制的数中,数值最大的数是( D )1051A.() .101010B 2() 163E C.() D.(01011001)8421BCD 码 3、用卡诺图化简下式为最简与或式。

D C B A ++ Y(A,B,C,D)= ∑m(0,2,4,5,6,8,9)+ ∑d(10,11,12,13,14,15) 4.已知F ABC CD =+选出下列可以肯定使F=0的情况( D )A. A=0,BC=1B. B=C=1C. D=0,C=1D. BC=1,D=1 5、是8421BCD 码的是( B )。

A 、1010 B C 、1100 D 、11016、欲对全班43个学生以二进制代码编码表示,最少需要二进制码的位数是( B )。

A 、5B 、6C 、8D 、437、逻辑函数F(A,B,C) = AB+B C+C A 的最小项标准式为( D )。

A 、F(A,B,C)=∑m(0,2,4)B 、F(A,B,C)=∑m(1,5,6,7)C 、F(A,B,C)=∑m (0,2,3,4)D 、F(A,B,C)=∑m(3,4,6,7)Z A BC A B AC D =++Z Z AC AC =+()B C D C D ++1..2..3..4..AC A DA C AB A D A B A B B C++++8、用代数法化简下式为最简与或式。

A+CC B BC C B A BCD A A F ++++=判断题1.若两个函数具有不同的真值表,则两个逻辑函数必然不相等。

第七章:存储系统一、选择题1、外存储器与内存储器相比,外存储器( 速度慢,容量大,成本低)。

2、EPROM是指(光擦除可编程只读存储器)。

3、没有外存储器的计算机初始引导程序可以放在(ROM ) 。

4、存储单元是指(存放一个机器字的所有存贮元集合)。

5、主存储器是计算机系统中的记忆设备,它主要用来(存放数据和程序)。

6、软磁盘、硬磁盘、磁带机、光盘属于(外存储器)设备。

7、主存贮器和CPU之间增加cache的目的是(解决CPU和主存之间的速度匹配问题)。

8、采用虚拟存贮器的主要目的是(扩大主存贮器的存贮空间,并能进行自动管理和调度)。

9、单片机或单板机要扩展8K的EPROM需要( 13)条地址线。

10、假设V1和V2是用DW定义的变量,下列指令中正确的是( A )。

A、MOV V1,20HB、MOV AL,V1C、MOV V1,V2D、MOV 2000H,V211.下列( A )指令不合法。

A、IN AX,0278HB、RCR DX,CLC、CMPSBD、RET 412.为了使MOV AX,VAR指令执行后,AX寄存器中的内容为4142H,数据定义(C )是错误的。

A、VAR DW 4142H B、VAR DW 16706C、VAR DB 42H,41HD、VAR DW,‘AB’13.在下列指令中,隐含使用AL寄存器的指令有( 4)条。

SCASB;XLAT;MOVSB;DAA;NOP;MUL BH;14.下列描述不正确的是( A )。

A.汇编语言即是机器语言B.汇编语言程序不可直接运行C.汇编语言的指令语句与机器指令一一对应D.汇编语言程序运行速度快,阅读方便,但仍属于面向机器的程序设计语言15.下列描述正确的是( B )。

A.汇编语言是由若干条指令语句构成B.汇编语言包括指令语句和伪指令语句C.指令语句和伪指令语句的格式是完全相同的D.指令语句和伪指令语句需经汇编语言翻译成机器代码后才能运行16.汇编语言程序经汇编后不能直接生成( A )。

第一章数制和码制2.(单选题) 与二进制数等值的十进制数为()。

A. 9.21B. 9.3125C. 9.05D. 9.5参考答案:B3.(单选题) 与二进制数等值的十六进制数为()。

A. B0.C3B. C. 2C.C3D. 参考答案:D参考答案:B5.(单选题) 与二进制数等值的十进制数为()。

A. 6.11B. 6.21C. 6.625D. 6.5参考答案:C6.(单选题) 与二进制数等值的八进制数为()。

A. 6.44B. 6.41C. 3.44D. 3.41参考答案:A13.(单选题) 的原码、反码、补码分别是()。

A.11011、00100、00101 B.11011、10100、10101C.01011、00100、00101 D.01011、10100、10101参考答案:B第二章逻辑代数基础1.(单选题) 将函数式化成最小项之和的形式为()。

参考答案:D2.(单选题) 函数的反函数为()。

参考答案:B3.(单选题) 将函数式化成最小项之和的形式为()。

参考答案:A4.(单选题) 函数的反函数为()。

参考答案:B5.(单选题) 已知函数的卡诺图如图2-1所示, 则其最简与或表达式为()。

参考答案:A6.(单选题) 某电路当输入端A或B任意一个为高电平时,输出Y为高电平,当A和B均为低电平时输出为低电平,则输出Y与输入A、B之间的逻辑关系为Y=()。

参考答案:B7.(单选题) 全体最小项之和为()。

参考答案:C8.(单选题) 以下与逻辑表达式相等的式子是()。

参考答案:D9.(单选题) 和与非-与非逻辑表达式相等的式子是()。

参考答案:C11.(单选题) 某电路当输入端A或B任意一个为低电平时,输出Y为低电平,当A和B均为高电平时输出为高电平,则输出Y与输入A、B之间的逻辑关系为Y=()。

参考答案:A12.(单选题) 任何两个最小项的乘积为()。

参考答案:A13.(单选题) 以下与逻辑表达式相等的式子是()。

![数字电路与逻辑设计习题学生常见问题答疑[1]](https://uimg.taocdn.com/fe7dfaf63086bceb19e8b8f67c1cfad6195fe988.webp)

数字电路与逻辑设计习题学生常见问题答疑[1]第一章绪论1、数字电路有什么优点?答:首先数字电路能产生更廉价,更可靠的数字处理系统。

其次数字处理硬件允许可编程操作,同时数字硬件和软件实现与模拟电路和模拟信号处理系统相比,通常具有更高的精度。

2、数字电路与模拟电路有什么区别?答:数字电路与模拟电路同等重要,构成数字电路与模拟电路的基本元件都是半导体器件。

但是它们工作状态不同,实现功能不同,工作信号不同,如:数字电路中三极管工作在饱和区和截止区,模拟电路中三极管工作在放大区。

数字电路实现逻辑功能,完成逻辑运算,模拟电路主要是放大电信号。

数字电路处理离散信号,模拟电路处理连续信号。

3、数字电路设计的趋势?答:当前数字电路设计的趋势是,越来越大的设计,越来越短的推向市场的时间,越来越低的价格,设计方法越来越依赖于电子设计自动化(EDA)工具。

多层次的设计表述,集成电路的设计与制造分离,芯片生产厂家提供模型或标准单元库,设计公司负责电路功能设计。

电路功能设计已进入片上系统(SOC)时代,知识产权模块(IP 核)产品化。

第二章逻辑函数及其简化1、逻辑函数为什么要化简?答:一个逻辑函数可以写成不同的表达式形式,表达式越简单,所表示的逻辑关系越明显。

化简电路的目的,就是为了降低系统的成本,提高电路的可靠性,以用最少的逻辑门实现逻辑函数。

2、公式法化简中那么多公式怎么记?它有什么优缺点?答:逻辑代数的常用公式,反映了逻辑代数运算的基本规律,是化简逻辑函数、分析和设计逻辑电路的基本公式,必须熟悉和掌握。

公式法化简没有固定的步骤。

能否以最快的速度进行化简,与经验、技巧和对公式掌握及运用的熟练程度有关。

该方法的优点是输入变量个数不受限制,缺点是结果是否为最简有时不易判断。

3、卡诺图法化简的优点?答:利用卡诺图可以直观、方便地化简逻辑函数,并且克服了公式化简法对最终化简结果难以确定等缺点。

第三章集成逻辑门1、第三章感觉和其它章节没关系,是否不重要?答:第三章介绍了常用逻辑门的内部电路结构以及外部特性,对后续学习非常重要。

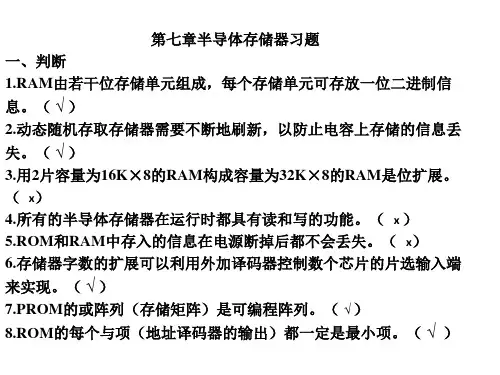

第七章半导体存储器习题[本次习题要求6月4日交]7.1填空题:1.半导体存储器从读、写的功能上可分为ROM和()两大类。

2.工作中既可以读出信息,又可写入信息的存储器称为()。

3.根据存储单元电路结构和工作原理的不同,将RAM分为静态RAM和()RAM 两类。

4.一个ROM共有10根字线(地址线),8根位线(数据线),则其存储容量为()。

A.10×28;B.102×8;C.10×82;D.210×8。

5.容量为8K×8位的RAM芯片,其地址线和数据线各为()。

A.8和8根;B.10和8根;C.13和8根;D.8和13根。

6.要扩展成32K×16位的ROM,需要()片32K×8位的ROM。

7.为了构成4096×8位的RAM,需要()片1024×2位的RAM。

8.关于半导体存储器的描述,下列哪种说法是错误的是()。

A.RAM读写方便,但一旦掉电,所存储的内容就会全部丢失。

B.ROM掉电以后数据不会丢失。

C.RAM可分为静态RAM和动态RAM。

D.动态RAM不必定时刷新。

9.二极管ROM的电路结构如图所示,当地址为A1A=10时,该字单元的内容d3d2d1d为()。

10.ROM阵列逻辑图如图所示,当地址为A1A=10时,该字单元的内容D3D2D1D为()。

A.1l10;B.0111;C.1010;D.0100。

7.2试用2片1024×4位的RAM(2114)接成1024×8位的存储器。

7.3试用2片1024×4位的RAM(2114)接成2048×4位的存储器。

7.4用4×6位的ROM设计一个六段显示译码器。

六段显示器如图所示(图中e 是水平线,f是垂直线)。

它可以显示东南西北四个方向之一,实心线表示亮,虚心线表示不亮。

显示东南西北四个方向之一由ROM的两位地址输入码A1和A控制,控制要求如下表所示。

半导体存储器一、填空题1.半导体存储器从器件原理的角度可分为____和____。

2.磁盘是____存储器,磁带是____存储器。

3.用下列RAM 芯片构成32K ×8存储器模块,各需多少片RAM 芯片?(a )1K ×1 RAM 芯片; _____ (b )1K ×4 RAM 芯片;_____ (c )4K ×8 RAM 芯片;_____ (d )16K ×4 RAM 芯片;_____ 4.一台8位微机地址总线16条,其读写存储器RAM 容量为32KB ,首地址为4000H ,且地址是连续的,可用的最高地址是____。

二、选择题1.存储字长是指____。

A .存放在一个存储单元中的二进制代码组合B .寄存器的位数C .存放在一个存储单元中的二进制代码个数D .存储单元的个数 2.某计算机的主存为3KB ,则内存地址寄存器需____位就足够了。

A .10 B .11 C .12 D .13 3.EPROM 是指____。

A .只读存储器B .可编程的只读存储器C .可擦除可编程的只读存储器D .电可改写只读存储器4~6.微机系统的存储器由两片容量不同的静态RAM 芯片1#和2#组成,如下图所示。

芯片1#RAM 的地址范围是__4__H ,芯片2#RAM 的地址范围是__5__H ,存储器总容量是__6__字节。

注意:两片存储器的寻址范围不可重叠。

4. A .0000H ~0FFFH B .1000H ~1FFFH C .2000H ~2FFFH D .3000H ~3FFFH 5. A .0000H ~07FFH B .1000H ~17FFH C .2000H ~27FFH D .3000H ~37FFH 6. A .2KB B .3KB C .4KB D .6KB 7.主存和CPU 之间增加高速缓冲的目的是____。

A .解决CPU 和主存之间的速度匹配问题 B .扩大主存容量C .既扩大主存容量,又提高存取速度D .提高存取速度8.采用虚拟存储器的目的是____。

思考题与习题7.1 选择题7.14 选择题1)存储容量为8K×8位的ROM 存储器,其地址线为 条。

CA 、8B 、12C 、13D 、142)只能按地址读出信息,而不能写入信息的存储器为 。

bA 、 RAMB 、ROMC 、 PROMD 、EPROM3)一片ROM 有n 根地址输入,m 根位线输出,则ROM 的容量为 。

a A 、m n⨯2 B 、n m ⨯ C 、mn 22⨯ D 、n m⨯24)一个6位地址码、8位输出的ROM ,其存储矩阵的容量为 。

A 、46B 、64C 、512D 、256 5)为构成4096×8的RAM ,需要 片2024×2的RAM ,并需要有 位地址译码以完成寻址操作。

A 、8 ,15B 、16,11C 、10,12D 、8,12 6)PAL 是一种的 可编程逻辑器件。

A 、与阵列可编程,或阵列固定B 、与阵列列固,或阵可编程定C 、与阵列、或阵列固定D 、与阵列、或阵列可编程7.2 试写出如图7-27所示阵列图的逻辑函数表达式和真值表,并说明其功能。

1F 2F 3图6-1 例6-1逻辑图图7-27 题7.2图解:根据与阵列的输出为AB 的最小项和阵列图中有实心点“·”为1,无“·”为0,可以写出:AB W F ==30B A AB B A B A W W W F +=++=++=3211B A B A B A F ⊕=+=2AB B A B A B A B A W W W F =+=++=++=2103从上述逻辑表达式可以看出,图7-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。

列出真值表如表7-1所示。

7.3 若存储器芯片的容量为128K×8位,求:表7-1 例7-1真值表1)访问芯片需要多少地址?2)假定该芯片在存储器中首地址为A00000H ,末地址为多少? 解:存储器容量=字数×位数=m n⨯21)128K×8=8282217107⨯=⨯⨯,所以需要17根地址。

第七章半导体存储器习题

[本次习题要求6月4日交]

7.1填空题:

1.半导体存储器从读、写的功能上可分为ROM和()两大类。

2.工作中既可以读出信息,又可写入信息的存储器称为()。

3.根据存储单元电路结构和工作原理的不同,将RAM分为静态RAM和()RAM 两类。

4.一个ROM共有10根字线(地址线),8根位线(数据线),则其存储容量为()。

A.10×28;

B.102×8;

C.10×82;

D.210×8。

5.容量为8K×8位的RAM芯片,其地址线和数据线各为()。

A.8和8根;

B.10和8根;

C.13和8根;

D.8和13根。

6.要扩展成32K×16位的ROM,需要()片32K×8位的ROM。

7.为了构成4096×8位的RAM,需要()片1024×2位的RAM。

8.关于半导体存储器的描述,下列哪种说法是错误的是()。

A.RAM读写方便,但一旦掉电,所存储的内容就会全部丢失。

B.ROM掉电以后数据不会丢失。

C.RAM可分为静态RAM和动态RAM。

D.动态RAM不必定时刷新。

9.二极管ROM的电路结构如图所示,当地址为A

1A

=10时,该字单元的内容d

3

d

2

d

1

d

为()。

10.ROM阵列逻辑图如图所示,当地址为A

1A

=10时,该字单元的内容D

3

D

2

D

1

D

为

()。

A.1l10;

B.0111;

C.1010;

D.0100。

7.2试用2片1024×4位的RAM(2114)接成1024×8位的存储器。

7.3试用2片1024×4位的RAM(2114)接成2048×4位的存储器。

7.4用4×6位的ROM设计一个六段显示译码器。

六段显示器如图所示(图中e 是水平线,f是垂直线)。

它可以显示东南西北四个方向之一,实心线表示亮,虚心线表示不亮。

显示东南西北四个方向之一由ROM的两位地址输入码A

1和A

控制,控制要

求如下表所示。

即六段显示译码器的输入为A

1和A

,并使输出a~f中适当的段

亮。

设输出逻辑1表示亮,逻辑0表示不亮。

要求列出ROM

7.5试用8×2位容量的ROM设计一个能实现两个一位二进制数全加的逻辑电路。

输入为被加数A

i 、加数B

i

及来自低位的进位C

i-1

;输出为和S

i

及向高位的进位C

i。

要求:(1)列出真值表;(2)直接在下图中画出用ROM点阵图实现全加的电路。

7.6由一片256×8位的EPROM 构成的数码转换器,将8位二进制原码转换成等值的补码,最高位为符号位。

问:当地址输入A 7……A 1A 0分别为0000 0000、0000 0001、1000 0001、1111 1111时,EPROM 中对应地址中的数据D 7……D 1D 0各为何值?将你的答案填写地下表中。