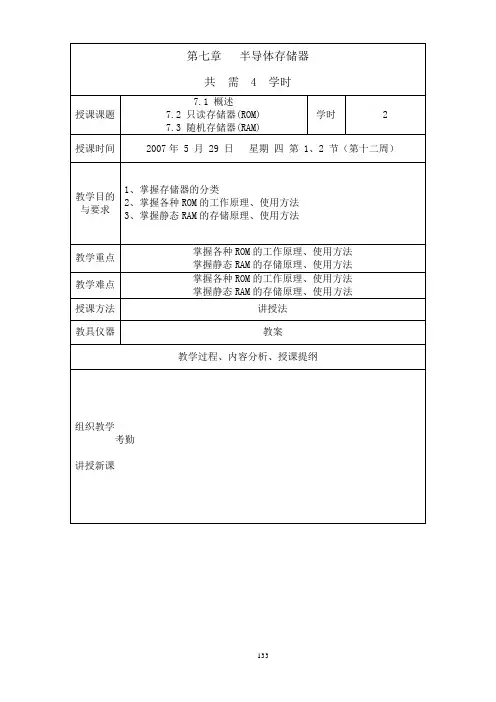

第七章 半导体存储器

- 格式:ppt

- 大小:6.90 MB

- 文档页数:37

第七章 半导体存储器数字信息在运算或处理过程中,需要使用专门的存储器进行较长时间的存储,正是因为有了存储器,计算机才有了对信息的记忆功能。

存储器的种类很多,本章主要讨论半导体存储器。

半导体存储器以其品种多、容量大、速度快、耗电省、体积小、操作方便、维护容易等优点,在数字设备中得到广泛应用。

目前,微型计算机的内存普遍采用了大容量的半导体存储器。

存储器——用以存储一系列二进制数码的器件。

半导体存储器的分类根据使用功能的不同,半导体存储器可分为随机存取存储器(RAM —Random Access Memory )和只读存储器(ROM —Read-Only memory )。

按照存储机理的不同,RAM 又可分为静态RAM 和动态RAM 。

存储器的容量存储器的容量=字长(n )×字数(m )7.1随机存取存储器(RAM )随机存取存储器简称RAM ,也叫做读/写存储器,既能方便地读出所存数据,又能随时写入新的数据。

RAM 的缺点是数据的易失性,即一旦掉电,所存的数据全部丢失。

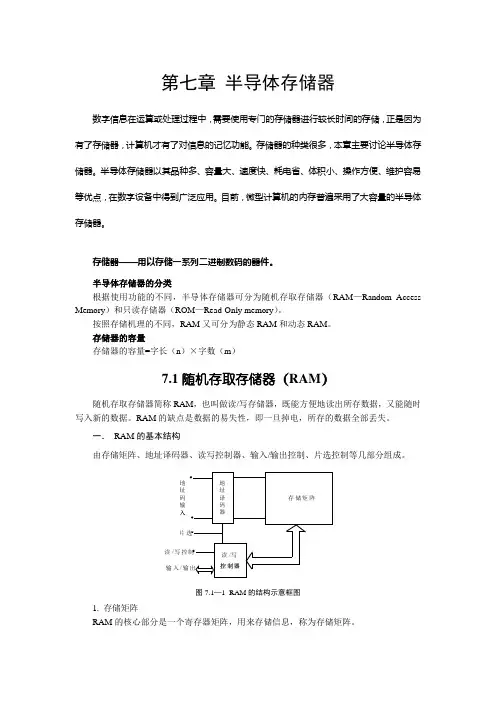

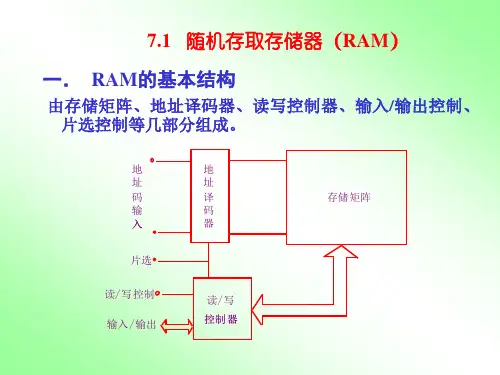

一. RAM 的基本结构由存储矩阵、地址译码器、读写控制器、输入/输出控制、片选控制等几部分组成。

存储矩阵读/写控制器地址译码器地址码输片选读/写控制输入/输出入图7.1—1 RAM 的结构示意框图1. 存储矩阵RAM 的核心部分是一个寄存器矩阵,用来存储信息,称为存储矩阵。

图7.1—5所示是1024×1位的存储矩阵和地址译码器。

属多字1位结构,1024个字排列成32×32的矩阵,中间的每一个小方块代表一个存储单元。

为了存取方便,给它们编上号,32行编号为X 0、X 1、…、X 31,32列编号为Y 0、Y 1、…、Y 31。

这样每一个存储单元都有了一个固定的编号(X i 行、Y j 列),称为地址。

11113131131********列 译 码 器行译码器...........位线位线位线位线位线位线.......X X X Y Y Y 0131131A A A A A A A A A A 地 址 输 入地址输入0123456789D D数据线....图7.1-5 1024×1位RAM 的存储矩阵2. 址译码器址译码器的作用,是将寄存器地址所对应的二进制数译成有效的行选信号和列选信号,从而选中该存储单元。

第7章半导体存储器内容提要半导体存储器是存储二值信息的大规模集成电路,本章主要介绍了(1)顺序存取存储器(SAM)、随机存取存储器(RAM)、只读存储器(ROM)的工作原理。

(2)各种存储器的存储单元。

(3)半导体存储器的主要技术指标和存储容量扩展方法。

(4)半导体存储器芯片的应用。

教学基本要求掌握:(1)SAM、RAM和ROM的功能和使用方法。

(2)存储器的技术指标。

(3)用ROM实现组合逻辑电路。

理解SAM、RAM和ROM的工作原理。

了解:(1)动态CMOS反相器。

(2)动态CMOS移存单元。

(3)MOS静态及动态存储单元。

重点与难点本章重点:(1)SAM、RAM和ROM的功能。

(2)半导体存储器使用方法(存储用量的扩展)。

(3)用ROM 实现组合逻辑电路。

本章难点:动态CMOS 反相器、动态CMOS 移存单元及MOS 静态、动态存储单元的工作原理。

7.1■■■■■■■■■半导体存储器是存储二值信息的大规模集成电路,是现代数字系统的 重要组成部分。

半导体存储器分类如下:I 融+n 右西方性翼静态(SRAM )(六管MO 白静态存储单元) 随机存取存储器〔^^'{动态侬^1口3网又单管、三管动态则□吕存储单元) 一固定艮cmil 二极管、M 口号管) 可编程RDM (PROM )[三极管中熠丝上可擦除可编程ROM (EPROM )[叠层栅管、雪崩j1-电可擦除可编程良口财(EEPROM^【叠层栅管、隧道)按制造工艺分,有双极型和MOS 型两类。

双极型存储器具有工作速度快、功耗大、价格较高的特点。

MOS 型存储器具有集成度高、功耗小、工艺简单、价格低等特点。

按存取方式分,有顺序存取存储器(SAM )、随机存取存储器(RAM )和只读存储器(ROM )三类。

(1)顺序存取存储器(简称SAM ):对信息的存入(写)或取出(读)是按顺序进行的,即具有“先入先出”或“先入后出”的特点。

(2)随机存取存储器(简称RAM ):可在任何时刻随机地对任意一个单元直接存取信息。

第七章半导体存储器7.1 概述半导体存储器是一种能存储大量二值信息(或称为二值的数据)的半导体器件。

在电子计算机以及其他一些数字系统的工作过程中,都需要对大量的数据进行存储。

因此,存储器也就成了这些数字系统不可少的组成部分。

由于计算机处理的数据量越来越大,运算速度越来越快,这就要求存储器具有更大的容量和更快的存取速度。

通常都把存储量和存取速度作为评价存储器性能的重要指标。

目前动态存储器的容量已达到109位每片,一些高速随机存储器的存取时间为10ns左右。

因为半导体存储器的存储单元数目极其庞大而器件的引脚数目有限,所以在电路结构上就不可能像寄存器那样把每个存储单元的输入和输出直接引出。

为了解决这个问题,在存储器中给每个存储单元编了一个地址,只有被输入地址代码指定的那些存储单元才能与公共的输入/输出引脚接通,进行数据的读出或写入。

半导体存储器的种类很多,从功能上可以分为只读存储器和随机存储器两大类。

只读存储器在正常工作状态上只能从中读取数据,不能快速地随时修改或重新写入数据。

ROM的优点是电路结构简单,而且在断电以后数据不会丢失,它的缺点是只适用于存储那些固定数据的场合。

只读存储器中又有掩模ROM、可编程ROM和可擦除的可编程ROM几种不同类型。

掩模ROM 中的数据在制作时已经确定,无法更改。

PROM中的数据可以由用户根据自己的需要写入,但一经写入以后就不能再修改了。

EPROM里的数据则不但可以由用户根据自己的需要写入,而且还能擦除重写,所以具有更大的使用灵活性。

随机存储器与只读存储器的根本区别在于,正常工作状态下就可以随时向存储器里写入数据或从中读出数据。

根据所采用的存储单元工作原理的不同,又将随机存储器分为静态存储器和动态存储器。

由于动态存储器存储单元的结构非常简单,所以它能达到的集成度远高于静态存储器。

但是动态存储器的存取速度不如静态存储器快。

7.2 只读存储器(ROM)7.2.1掩模只读存储器ROM根据用户要求专门设计的掩模板把数据:“固化”在ROM中电路结构ROM的电路结构框图地址译码器:将输出的地址代码翻译成相应的控制信号,把指定单元选出,其数据送输出缓冲器输出缓冲器❖提高存储器带负载的能力❖实现输出状态三态控制,与系统总线连接地址译码器存储矩阵输出缓冲器WW1W2-1nAA1An-1三态控制信息单元(字)存储单元……………存储矩阵是存放信息的主体,它由许多存储单元排列组成。