第11章 逻辑代数基础与组合逻辑电路[23页]

- 格式:doc

- 大小:533.00 KB

- 文档页数:23

第11章逻辑代数基础与组合逻辑电路【重点】常用数制与码制、不同数制之间的转换。

常用逻辑门的符号、表达式及逻辑关系;【难点】数制之间的转换。

逻辑关系。

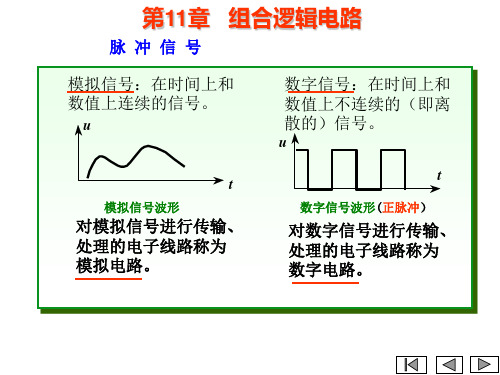

11.1 数制与编码11.1.1 数字信号数字信号只有两个离散值(代表某种对应的逻辑关系),常用数字0和1来表示。

0和1只代表两种对立的状态,称为逻辑0和逻辑1,也称为二值数字逻辑。

数字信号是一种二值信号,用两个电平(高电平和低电平)分别来表示两个逻辑值(逻辑1和逻辑0)。

正逻辑规定高电平为逻辑1,低电平为逻辑0。

负逻辑规定低电平为逻辑1,高电平为逻辑0。

11.1.2 数制数制是一种计数的方法,它是进位计数制的简称,也称为进制。

采用何种计数方法应根据实际需要而定。

1.常用的几种进制(1)十进制十进制是以10为基数的计数制。

在十进制中,有0、1、2、3、4、5、6、7、8、9十个数码,它的进位规律是逢十进一。

数码与权的乘积,称为加权系数,十进制数的数值为各位加权系数之和。

(2)二进制二进制是以2为基数的计数制。

在二进制中,只有0和1两个数码,它的进位规律是逢二进一。

(3)八进制和十六进制八进制是以8为基数的计数制。

在八进制中,有0、1、2、3、4、5、6、7八个不同的数码,它的进位规律是逢八进一。

十六进制是以16为基数的计数制。

在十六进制中,有0、1、2、3、4、5、6、7、8、9、A (10)、B (11)、 C (12)、D (13)、E (14)、F (15)十六个不同的数码,它的进位规律是逢十六进一。

2.不同数制间的转换 (1)各种数制转换成十进制二进制、八进制、十六进制转换成十进制时,只要将它们按权展开,求出各加权系数的和(称为按权展开求和法),便得到相应进制数对应的十进制数。

(11010.011)2=1×24+1×23+0×22+1×21+0×20+0×2-1+1×2-2+1×2-3=(26.375)10(4C2)16=4×162+12×161+2×160=(1218)10 (2)十进制转换为二进制十进制数转换为二进制数时,由于整数和小数的转换方法不同,因此,需将整数部分和小数部分分别进行转换,再将转换结果合并在一起,就得到该十进制数转换的完整结果。

将十进制数的整数部分转换为二进制数采用“除基数,取余法,逆排列”的方法,即将整数部分逐次除2,依次记下余数,直到商为0。

第一个余数为二进制数的最低位,最后一个余数为最高位。

将十进制数的小数部分转换为二进制数采用“乘基数,取整法,顺排列”的方法,即将小数部分逐次乘以2,取乘积的整数部分作为二进制数的各位。

乘积的小数部分继续乘ii K N 8i8⨯=∑+∞-∞=ii K N 16i16⨯=∑+∞-∞=以2,直到乘积的小数部分为0或达到要求的精度为止。

(3)二进制与八进制、十六进制相互转换二进制数转换为十六进制数的方法是:整数部分从低位开始,每四位二进制数为一组,最后不足四位的,则在高位加0补足四位;小数部分从高位开始,每四位二进制数为一组,最后不足四位的,在低位加0补足四位。

然后每组二进制数用对应的十六进制数来代替,再按顺序排列得出结果。

二进制数转换为八进制数的方法与二进制数转换为十六进制数的方法相同,只是每三位二进制数为一组。

11.1.3 二进制代码将若干个二进制数码0和1按一定规则排列起来表示某种特定含义的代码,称为二进制代码,或称二进制编码。

二-十进制码又称为BCD码是一种常用的二进制代码。

BCD码是用二进制数表示十进制数的0~9十个数。

由于十进制数有十个不同的数码,因此,需用四位二进制数来表示。

而四位二进制代码有16种不同的组合,从中取出10种组合来表示0~9十个数可有多种方案,所以BCD码也有多种。

(1)8421BCD码这种代码每一位的权值是固定不变的,为恒权码。

它取了四位自然二进制数的前10种组合,即0000~1001,从高位到低位的权值分别为8、4、2、1,所以称为8421BCD码。

(2)5421BCD码和2421BCD码这两种也是恒权码,从高位到低位的权值分别是5、4、2、1和2、4、2、1。

每组代码各位加权系数的和为其代表的十进制数。

2421(A)码和2421(B)BCD码的编码状态不完全相同,2421(B)BCD码具有互补性,0和9、1和8、2和7、3和6、4和5这五对代码互为反码。

(3)余3BCD码这种代码没有固定的权,为无权码,它比8421BCD码多余3(0011),所以称为余3码。

0和9、1和8、2和7、3和6、4和5这五对代码互为反码。

BCD码用四位二进制数表示的只是十进制数的一位,如果是多位,应先将每一位用BCD码表示,然后组合起来。

(4)格雷码它是一种无权码。

它的特点是任意两组相邻代码之间只有一位不同,其余各位都相同(即按照“相邻原则”进行编码),而0和最大数(2 n -1)之间也只有一位不同。

因此,它是一种循环码。

格雷码的这个特性使它在形成和传输过程中引起的误差较小。

11.2 基本逻辑运算逻辑关系是指某事物的条件(或原因)与结果之间的关系。

11.2.1 基本逻辑运算逻辑代数中只有三种基本运算与、或、非。

1.与运算只有当决定一件事情的条件全部具备之后,这件事情才会发生,我们把这种因果关系称为与逻辑。

(1)可以用列表的方式表示上述逻辑关系,称为逻辑状态表。

(2)如果用二值逻辑0和1来表示,并设1表示开关闭合或灯亮,0表示开关不闭合或灯不亮,则得到逻辑真值表。

(3)若用逻辑表达式来描述,则可写为与运算的规则为输入有0,输出为0;输入全1,输出才为1。

(4)在数字电路中能实现与运算的电路称为与门电路。

2.或运算决定一件事情的几个条件中,只要有一个或一个以上条件具备,这件事情就会发生,我们把这种因果关系称为或逻辑。

或运算的规则为:输入有1,输出为1;输入全0,输出才为0。

在数字电路中能实现或运算的电路称为或门电路。

3.非运算某事情发生与否,仅取决于一个条件,而且是对该条件的否定,即条件具备时事情不发生,条件不具备时事情才发生。

当开关A闭合时,灯不亮;而当开关A不闭合时,灯亮。

ABY=BAY+=非运算的规则为:输入1,输出为0;输入0,输出为1。

11.2.2 其他逻辑运算任何复杂的逻辑运算都可以由三种基本逻辑运算组合而成。

由三种基本逻辑运算组合 而成的逻辑运算称为组合逻辑运算。

与非运算或非运算与或非运算异或运算和同或运算异或运算:当两个变量取值相同时,逻辑函数值为0;当两个变量取值不同时,逻辑函数值为1。

AY =Y A B C D=⋅+⋅同或运算:当两个变量取值相同时,逻辑函数值为1;当两个变量取值不同时,逻辑函数值为0。

【重点】逻辑代数基本公式,基本规则及其化简。

【难点】逻辑代数化简。

11.3 逻辑代数及化简11.3.1 逻辑代数的基本公式1.逻辑常量运算公式2.逻辑变量、常量运算基本公式0—1律互补律重叠律交换律结合律分配律反演律吸收律AA=1·AA=+000·=A11=+A=AA1=+AAAAA=AAA=+BAAB=ABBA+=+CABBCA)()(=CBACBA++=++)()(ACABCBA+=+)())((CABABCA++=+BAAB+=BABA=+ABAA=+)(ABBAA=+)())()((CBCABA+++))((CABA++=对合律【例】 证明11.3.2 逻辑代数的基本规则1.代入规则对于任一个含有变量A 的逻辑等式,可以将等式两边的所有变量A 用同一个逻辑函数替代,替代后等式仍然成立。

这个规则称为代入规则。

利用代入规则,可以把基本定律加以推广。

2.反演规则对任何一个逻辑函数式Y ,如果将式中所有的“·”换成“+”,“+”换成“·”,“0”换成 “1”,“1”换成“0”,原变量换成反变量,反变量换成原变量,则得逻辑函数Y 的反函数。

这种变换原则称为反演规则。

在应用反演规则时必须注意以下两点:(1)保持变换前后的运算优先顺序不变,必要时可加括号表明运算的先后顺序。

(2)规则中的反变量换成原变量只对单个变量有效。

反演规则常用于求一个已知逻辑函数的反函数。

3.对偶规则对任何一个逻辑函数式Y ,如果把式中的所有的“·”换成“+”,“+”换成“·”,“0”换成 “1”,“1”换成“0”,这样就得到逻辑函数Y 的对偶式Y ′。

变换时要注意保持变换前后运算的优先顺序不变。

对偶规则的意义在于若两个函数式相等,则它们的对偶式也一定相等。

11.3.3 逻辑表达式的化简进行逻辑设计时,根据逻辑问题归纳出来的逻辑函数式往往不是最简逻辑函数式,并且可以有不同的形式。

因此,实现这些逻辑函数就会有不同的逻辑电路。

对逻辑函数进行化简和变换,可以得到最简的逻辑函数式和所需要的形式,设计出最简洁的逻辑电路。

最简与-或式的标准(1)逻辑函数式中的乘积项(与项)的个数最少。

(2)每个乘积项中的变量数最少。

B A B A A +=+AAB A =+CA AB BC C A AB +=++AA =C A AB BC C A AB +=++)(A A BC C A AB BC C A AB +++=++CA AB BC A C AB BCA ABC C A AB +=+++=+++=)1()1(运用逻辑代数的基本定律和公式对逻辑函数式进行化简的方法称为代数化简法(公式化简法)。

基本的化简方法有以下几种: (1)并项法 将两项合并为一项,同时消去一个变量。

(2)吸收法运用吸收律消去多余的与项.。

(3)消去法运用吸收律消去多余因子。

(4)配项法在不能直接运用公式、定律化简时,可通过乘 或加入零项 进行配项,再化简。

1=+A A ()ABC ABC AB C C AB+=+=B A B A A +=+CA AB BC C A AB +=++()AB AB E F AB++=BA B A A +=+CAB C AB AB C B A AB C B C A AB +=+=++=++)(1=+A A 0=A A )(B B D C A C B AB D C A C B AB +++=++CB AB ADC BD C AB DC B AD C AB C B AB +=+++=+++=)1()1(【重点】逻辑门电路功能、符号及应用。

【难点】TTL与非门电路分析。

11.4 集成逻辑门电路11.4.1 TTL集成逻辑门电路1.TTL与非门电路的基本结构输入全为高电平3.6V时:VT2、VT3导通,V B1=0.7×3=2.1V,从而使VT1的发射结因反偏而截止。

此时VT1的发射结反偏,而集电结正偏,称为倒置工作状态。