第十六章组合逻辑电路解析

- 格式:ppt

- 大小:335.00 KB

- 文档页数:74

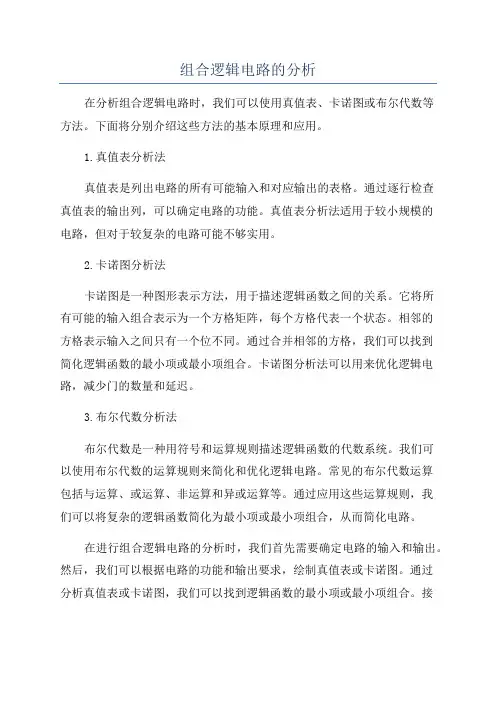

组合逻辑电路的分析在分析组合逻辑电路时,我们可以使用真值表、卡诺图或布尔代数等方法。

下面将分别介绍这些方法的基本原理和应用。

1.真值表分析法真值表是列出电路的所有可能输入和对应输出的表格。

通过逐行检查真值表的输出列,可以确定电路的功能。

真值表分析法适用于较小规模的电路,但对于较复杂的电路可能不够实用。

2.卡诺图分析法卡诺图是一种图形表示方法,用于描述逻辑函数之间的关系。

它将所有可能的输入组合表示为一个方格矩阵,每个方格代表一个状态。

相邻的方格表示输入之间只有一个位不同。

通过合并相邻的方格,我们可以找到简化逻辑函数的最小项或最小项组合。

卡诺图分析法可以用来优化逻辑电路,减少门的数量和延迟。

3.布尔代数分析法布尔代数是一种用符号和运算规则描述逻辑函数的代数系统。

我们可以使用布尔代数的运算规则来简化和优化逻辑电路。

常见的布尔代数运算包括与运算、或运算、非运算和异或运算等。

通过应用这些运算规则,我们可以将复杂的逻辑函数简化为最小项或最小项组合,从而简化电路。

在进行组合逻辑电路的分析时,我们首先需要确定电路的输入和输出。

然后,我们可以根据电路的功能和输出要求,绘制真值表或卡诺图。

通过分析真值表或卡诺图,我们可以找到逻辑函数的最小项或最小项组合。

接下来,我们可以将这些最小项或最小项组合转化为逻辑门的输入方式。

最后,我们可以使用布尔代数的运算规则来简化逻辑函数和电路。

组合逻辑电路的分析是电路设计和优化的重要一步。

通过应用不同的分析方法,我们可以更好地理解电路的功能和性质,从而更好地设计和优化电路。

在分析组合逻辑电路时,我们需要注意电路的输入和输出要求,合理选择和配置逻辑门,以及优化电路的延迟和开销。

组合逻辑电路•组合逻辑电路的概述•组合逻辑电路的分析•组合逻辑电路的设计•常用的组合逻辑电路在数字电路中,数字电路可分为组合逻辑电路和时序逻辑电路两大类。

组合逻辑电路:输出仅由输入决定,与电路当前状态无关,电路结构中无反馈环路(无记忆)。

组合逻辑电路的概述1.特点(1)输入、输出之间没有反馈延迟通路;(2)电路中不含记忆元件;(3)电路任何时刻的输出仅取决于该时刻的输入,而与电路原来的状态无关。

2.描述组合电路逻辑功能的方法逻辑表达式、真值表、卡诺图、逻辑图、波形图。

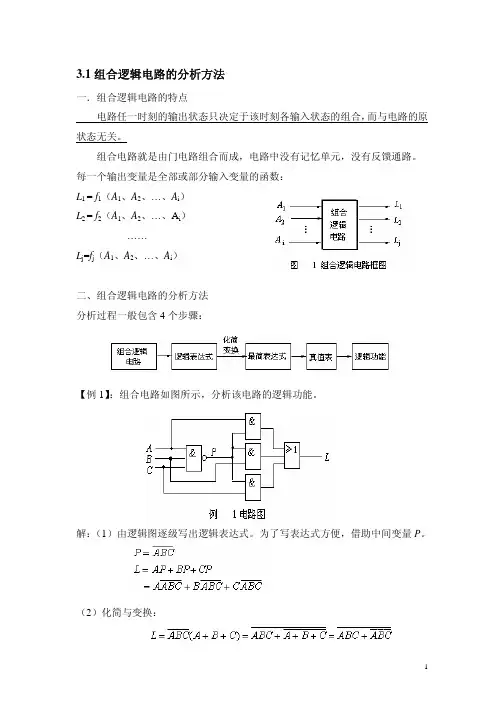

组合逻辑电路的分析[例] 试分析下列组合逻辑电路的功能。

[例] 试分析下列组合逻辑电路的功能。

解:(1)根据给定的逻辑电路,写出所有输出逻辑函数表达式并对其进行变换:(2)根据化简后的逻辑函数表达式列出真值表,如表。

(3)逻辑功能评述该电路是一位二进制数比较器:当A>B时,L1=1;当A<B时,L3=1。

注意在确定该电路的逻辑功能时,输出函数L1、L2、L3不能分开考虑。

组合逻辑电路的设计1.组合逻辑电路设计的目的设计组合电路的目的是根据功能要求设计最佳电路。

即根据给出的实际问题,求出能够实现这一逻辑要求的最简的逻辑电路,这就是组合电路的设计,它是分析的逆过程。

2.设计组合电路的步骤:(1)分析设计要求;(2)根据功能要求列出真值表;(3)根据真值表利用卡诺图进行化简,得到最简逻辑表达式;(4)根据最简表达式画逻辑图。

[例]用与非门设计一个三变量“多数表决电路”。

解:(1)进行逻辑抽象,建立真值表:用A、B、C表示参加表决的输入变量,“1”代表赞成,“0”代表反对,用F表示表决结果,“1”代表多数赞成,“0”代表多数反对。

根据题意,列真值表如表。

(2)根据真值表写出逻辑函数的“最小项之和”表达式:(3)将上述表达式化简,并转换成与非形式:(4)根据逻辑函数表达式画出逻辑电路图,如图。

上述逻辑电路可以用74LS00芯片实现,74LS00为4个2输入与非门芯片,74LS00的逻辑符号和引脚图如图所示。

组合逻辑电路组合逻辑电路是电子电路中最为基础的一种电路类型,其输入变量与输出变量之间的关系完全由它们之间的逻辑关系所决定。

组合逻辑电路可以简单描述为:“输入端口的电信号经过一个逻辑门,输出变量就随之产生并由输出端口发送出去”,组合逻辑电路中不包括概念上的时钟或记忆单元,实现逻辑功能的电路的输出只涉及当前输入状态。

本文将从组合逻辑电路的概念、组成部分及功能三个方面进行介绍。

一、组合逻辑电路的概念组合逻辑电路,是指由一些逻辑门以及它们之间的互连所组成的电路。

其中,逻辑门代表着一种或多种逻辑函数,其输入与输出可以是单个或多个电平或电位信号。

这些逻辑门能够执行特定的布尔运算,其结果可以反映在其输出端口上,也就是根据输入数据的逻辑关系进行处理和输出。

组合逻辑电路的工作原理是使逻辑门之间的信号通过特定逻辑关系进行耦合,形成逻辑闭环,并根据不同的逻辑输出操作信号产生先进的逻辑功能。

同时,组合逻辑电路具有很强的普适性和可扩展性,能够处理各种逻辑运算,是数字电路设计的基本组成部分。

二、组合逻辑电路的组成部分组合逻辑电路共由逻辑门、施密特触发器、数字比较器等构成,每个组合逻辑电路都是由若干个逻辑门以及它们之间的互连所组成,其中逻辑门的种类有三种。

1、与门(AND-Gate):两个或多个输入信号都为高电平时,输出信号才为高电平,否则输出为低电平。

2、或门(OR-Gate):两个或多个输入信号中只要有一个为高电平,则输出信号为高电平,否则输出为低电平。

3、非门(NOT-Gate):只有一个输入信号,当该输入信号为高电平时,输出信号为低电平;反之,输出为高电平。

通常情况下,组合逻辑电路包括三种类型:多路选择器、编码器和译码器。

其中,多路选择器的功能是在输入端口中有多个数据源的情况下选择其中之一的数据源;编码器的功能是将一个多位码转换为其代表的唯一数字;而译码器是将一个数字转换为其代表的多位码。

组合逻辑电路中用到的施密特触发器常常用于扩大输入信号的幅度,同时也可以用于提高抗干扰能力。