vhdl语言常用实例 -回复

- 格式:doc

- 大小:11.75 KB

- 文档页数:3

vhdl 十进制表示数值摘要:1.VHDL简介2.十进制表示法概述3.VHDL中十进制数值的表示方法4.实例演示5.总结与建议正文:【提纲】1.VHDL简介VHDL(VHSIC硬件描述语言)是一种硬件描述语言,用于描述数字电路和模拟混合信号电路。

它在电子设计自动化(EDA)领域具有广泛的应用。

在VHDL中,数值通常用二进制、十六进制或十进制表示。

本文将重点介绍如何在VHDL中表示十进制数值。

2.十进制表示法概述十进制表示法是一种数值表示方法,基于10个基本数字(0-9)。

在计算机系统中,十进制数可以通过位权展开式表示,位权值为10的幂。

例如,数值123可以表示为:1 * 10^2 + 2 * 10^1 +3 * 10^03.VHDL中十进制数值的表示方法在VHDL中,可以使用整数类型(INTEGER)表示十进制整数。

例如,定义一个十进制整数变量:INTEGER :: a = 123;此外,还可以使用STD_LOGIC_VECTOR类型表示十进制数。

通过分配位权值,可以将十进制数转换为二进制表示。

以下是一个例子:INTEGER :: b = 123;STD_LOGIC_VECTOR (3 downto 0) :: binary_b =TO_STD_LOGIC_VECTOR(b);4.实例演示假设我们要设计一个简单的加法器,输入两个十进制整数a和b,输出它们的和。

首先,定义两个整数类型变量a和b:INTEGER :: a, b, sum;然后,使用STD_LOGIC_VECTOR表示法将十进制数转换为二进制:STD_LOGIC_VECTOR (4 downto 0) :: binary_a =TO_STD_LOGIC_VECTOR(a);STD_LOGIC_VECTOR (4 downto 0) :: binary_b =TO_STD_LOGIC_VECTOR(b);接下来,实现加法器逻辑:process (binary_a, binary_b)beginsum = binary_a + binary_b;end process;最后,将二进制和转换回十进制:INTEGER :: sum_decimal = TO_INTEGER(sum);5.总结与建议本文介绍了如何在VHDL中表示十进制数值,并通过一个实例演示了如何使用STD_LOGIC_VECTOR表示法进行十进制与二进制的转换。

vhdl基础及经典实例开发pdf VHDL是一种硬件描述语言,它用于描述和设计数字电路。

VHDL的全称是Very High Speed Integrated Circuit Hardware Description Language,它源于20世纪80年代的美国国防部,是一种为了描述硬件而设计的开发语言。

VHDL的基础知识包括语法、数据类型和结构体。

语法方面,VHDL 有自己的语法规则和词法规则,要正确地描述一个硬件电路,我们需要熟悉这些规则。

数据类型方面,VHDL内置了基本的数据类型,如bit、bit vector、integer等,这些数据类型可以用来描述电路的输入输出和中间信号。

结构体方面,VHDL支持设计者自定义类型,比如用record来描述一个复杂的数据结构。

在VHDL开发中,经典实例是不可或缺的。

经典实例可以帮助我们更好地理解VHDL的使用方法和特点,也可以让我们更好地掌握VHDL的编程技巧。

下面是一些经典实例的介绍。

1.二进制加法器(Binary Adder):二进制加法器可以实现两个二进制数的加法运算。

它是数字电路中常用的基本模块,很多其他的电路都需要用到它。

通过构建一个二进制加法器的实例,我们可以学习到VHDL的语法规则、数据类型的使用以及模块化设计的思想。

2.时钟分频器(Clock Divider):时钟分频器可以将输入的时钟信号分频为较低频率的信号。

在数字电路中,时钟分频器是非常常见的一个模块,它可以用于控制其他电路的时序。

通过构建一个时钟分频器的实例,我们可以学习到VHDL的状态机设计、时序逻辑的实现以及对时钟信号的处理。

3.多路选择器(Multiplexer):多路选择器可以根据选择信号选择其中的一个输入信号输出。

在数字电路中,多路选择器可以用于实现多个输入的选择和切换。

通过构建一个多路选择器的实例,我们可以学习到VHDL的条件语句的使用、信号赋值的方法以及对多个输入信号的处理。

vhdl entity用法VHDL entity用法在VHDL设计语言中,entity是用来定义硬件模块的基本组成单元。

一个entity可以认为是一个顶层模块或一个子模块。

在这篇文章中,我们将详细讲解VHDL entity的用法。

以下是一些常见的用法示例:定义entityentity MyEntity isport (clk : in std_logic;rst : in std_logic;data : in std_logic_vector(7 downto 0);result : out std_logic_vector(3 downto 0));end entity MyEntity;在上面的示例中,我们定义了一个名为”MyEntity”的entity,它有一些输入和输出端口。

输入端口包括”clk”(时钟信号),“rst”(复位信号)和”data”(数据信号),输出端口为”result”(结果信号)。

通过使用这个定义,我们可以创建一个模块来使用这些端口。

设置entity属性entity MyEntity isgeneric (WIDTH : integer := 8);port (clk : in std_logic;rst : in std_logic;data : in std_logic_vector(WIDTH-1 downto 0);result : out std_logic_vector(WIDTH/2-1 downto 0));end entity MyEntity;在上面的示例中,我们使用了一个泛型属性来定义输入和输出端口的宽度。

通过这种方式,我们可以在实例化entity时根据需要设置端口宽度,使其更加灵活。

使用复杂数据类型entity MyEntity isport (clk : in std_logic;rst : in std_logic;data : in std_logic_vector(7 downto 0);result : out complex_type);end entity MyEntity;type complex_type isrecordreal : std_logic_vector(7 downto 0);imag : std_logic_vector(7 downto 0);end record;在上面的示例中,我们使用了VHDL的record类型定义了一个复杂的数据类型”complex_type”,然后在entity中使用了这个复杂数据类型作为输出端口的类型。

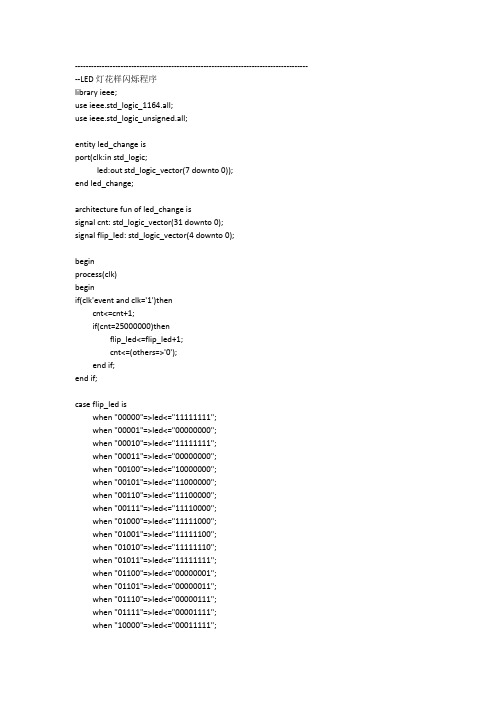

--------------------------------------------------------------------------------------- --LED灯花样闪烁程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led_change isport(clk:in std_logic;led:out std_logic_vector(7 downto 0));end led_change;architecture fun of led_change issignal cnt: std_logic_vector(31 downto 0);signal flip_led: std_logic_vector(4 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thencnt<=cnt+1;if(cnt=25000000)thenflip_led<=flip_led+1;cnt<=(others=>'0');end if;end if;case flip_led iswhen "00000"=>led<="11111111";when "00001"=>led<="00000000";when "00010"=>led<="11111111";when "00011"=>led<="00000000";when "00100"=>led<="10000000";when "00101"=>led<="11000000";when "00110"=>led<="11100000";when "00111"=>led<="11110000";when "01000"=>led<="11111000";when "01001"=>led<="11111100";when "01010"=>led<="11111110";when "01011"=>led<="11111111";when "01100"=>led<="00000001";when "01101"=>led<="00000011";when "01110"=>led<="00000111";when "01111"=>led<="00001111";when "10000"=>led<="00011111";when "10001"=>led<="00111111";when "10010"=>led<="01111111";when "10011"=>led<="11111111";when "10100"=>led<="00000000";when others =>led<="ZZZZZZZZ";end case;if(flip_led>"10100")thenflip_led<="00000";end if;end process;end fun;--拨码开关控制LED程序library ieee;use ieee.std_logic_1164.all;entity switch_led isport(key : in std_logic_vector(1 downto 0);led : out std_logic_vector(7 downto 0)); --八个led灯end switch_led;architecture fun of switch_led isbeginprocess(key)begincase key iswhen "00" => led <="00000000"; -- // "0"when "01" => led <="00001111"; -- // "1"when "10" => led <="11110000"; -- // "2"when "11" => led <="11111111"; -- // "3"when others => led <="ZZZZZZZZ";end case;end process;end;--按键消抖控制LED程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity stable_key isport(clk :in std_logic;key_in:in std_logic;key_out: out std_logic);end ;architecture fun of stable_key issignal cnt : integer range 0 to 1999999;signal key ,key_d : std_logic;beginprocess(clk)beginif clk'event and clk='1' thenif key /= key_in then -----键值变化开始计时10ms key_d <= key_in;cnt <= 0;elsif cnt=1999999 then ---10mskey_out <= not key_d;cnt <= 0;elsecnt <= cnt + 1 ;end if ;key<= key_in;end if ;end process;end ;--蜂鸣器电子琴程序library ieee;use ieee.std_logic_1164.all;entity digital_piano isport(key : in std_logic_vector(7 downto 0); --定义8个按键key1~key8clk : in std_logic; --时钟输入端50Mhzbeep: out std_logic); --蜂鸣器输出端end digital_piano;architecture fun of digital_piano issignal freq : integer range 0 to 50000;signal beep_reg: std_logic;beginbeep_process: process(clk,freq) --分频进程--本工程内核心进程,计数器的大小由counter决定variable cnt : integer range 0 to 50000;beginif clk'event and clk='1' thenif cnt < freq thencnt := cnt + 1;elsecnt := 0 ;beep_reg <=not beep_reg;end if;end if;end process beep_process;freq_process: process(key)begincase key iswhen "11111110" => freq <= 47774; ---------------------------------counter 计算公式:中音do的频率为523.3hz,为了在上个beep_pro进程中得到523的频率counter= 50*1000000/(523*2)when "11111101" => freq <= 42568; --中音re的频率为587.3hzwhen "11111011" => freq <= 37919; --中音mi的频率为659.3hzwhen "11110111" => freq <= 35791; --中音fa的频率为698.5hzwhen "11101111" => freq <= 31888; --中音sol的频率为784hzwhen "11011111" => freq <= 28409; --中音la的频率为880hzwhen "10111111" => freq <= 25309; --中音si的频率为987.8hzwhen "01111111" => freq <= 23912; --高音do的频率为1045.5hzwhen "01111101" => freq <= 21282; --高音re的频率为1174.7hzwhen "01111011" => freq <= 18961; --高音mi的频率为1318.5hzwhen "01110111" => freq <= 17897; --高音fa的频率为1396.9hzwhen "01101111" => freq <= 15944; --高音sol的频率为1568hzwhen "01011111" => freq <= 14205; --高音la的频率为1760hzwhen "00111111" => freq <= 12605; --高音si的频率为1975.5hzwhen others => freq <= 0;end case;end process freq_process;beep <= beep_reg;end;--数码管静态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity static_segled isport(clk : in std_logic;data:out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0));end ;architecture fun of static_segled issignal num : std_logic_vector(3 downto 0);signal cnt : integer range 0 to 12499999 ;beginsel <= "00000000"; --静态显示,全部位选中process(clk)beginif clk'event and clk='1' then --每四秒改变一次数字if cnt=12499999 thencnt<=0;num<= num + 1;elsecnt<= cnt + 1 ;end if ;end if ;end process;process(num)begincase num iswhen "0000" => data<=x"c0"; -- // "0"when "0001" => data<=x"f9"; -- // "1"when "0010" => data<=x"a4"; -- // "2"when "0011" => data<=x"b0"; -- // "3"when "0100" => data<=x"99"; -- // "4"when "0101" => data<=x"92"; -- // "5"when "0110" => data<=x"82"; -- // "6"when "0111" => data<=x"f8"; -- // "7"when "1000" => data<=x"80"; -- // "8"when "1001" => data<=x"90"; -- // "9"when "1010" => data<=x"88"; -- // "a"when "1011" => data<=x"83"; -- // "b"when "1100" => data<=x"c6"; -- // "c"when "1101" => data<=x"a1"; -- // "d"when "1110" => data<=x"86"; -- // "e"when "1111" => data<=x"8e"; -- // "f"when others => data<=x"ff";end case;end process;end ;--数码管动态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity dynamic_segled isport(clk : in std_logic;data: out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0) );end ;architecture fun of dynamic_segled issignal cnt: integer range 0 to 62449;signal flip_led: integer range 0 to 7;beginprocess(clk)beginif clk'event and clk='1' then ----- 动态扫描if cnt=62499 thencnt<=0;flip_led<=flip_led+1; -- 数据改变elsecnt<=cnt + 1;end if ;end if ;end process;process(flip_led)begincase flip_led is ---译码显示when 0 =>sel<="01111111";data<=x"c0";when 1 =>sel<="10111111";data<=x"f9";when 2 =>sel<="11011111";data<=x"a4";when 3 =>sel<="11101111";data<=x"b0";when 4 =>sel<="11110111";data<=x"99";when 5 =>sel<="11111011";data<=x"92";when 6 =>sel<="11111101";data<=x"82";when 7 =>sel<="11111110";data<=x"f8";when others=>sel<="11111111";data<=x"ff"; end case;end process;end ;。

vhdl others用法摘要:1.VHDL简介2.others关键字用法3.实例分析4.总结与建议正文:【1.VHDL简介】VHDL(VHSIC硬件描述语言)是一种硬件描述语言,用于描述数字电路和模拟混合信号电路。

在VHDL中,设计人员可以通过定义实体、结构、行为等描述数字电路的结构和功能。

今天我们将重点关注VHDL中的others关键字。

【2.others关键字用法】others关键字在VHDL中主要有两种用法:1)作为组件端口列表:当我们定义一个组件时,可以使用others关键字来表示组件的端口。

例如:```arduinolibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;entity Example isPort ( A, B, C, D, E, F : in STD_LOGIC;G, H, I : out STD_LOGIC);end Example;architecture Behavioral of Example isbeginprocess (A, B, C, D, E, F)beginif (A = "1" and B = "1") or (C = "1" and D = "1") or (E = "1" and F = "1") thenG <= H;I <= J;end if;end process;end Behavioral;```2)作为范围指定:在其他情况下,others关键字可以用于指定范围。

例如:```arduinolibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;entity Example isPort ( A, B, C, D, E, F : in STD_LOGIC;G, H, I : out STD_LOGIC);end Example;architecture Behavioral of Example isbeginsignal temp : STD_LOGIC_VECTOR (3 downto 0) := (others => "0");process (A, B, C, D, E, F)beginif (A = "1" and B = "1") or (C = "1" and D = "1") or (E = "1" and F = "1") thentemp := (others => "1");G <= temp(1);H <= temp(2);I <= temp(3);end if;end process;end Behavioral;```【3.实例分析】以上代码展示了如何使用others关键字来描述组件端口和范围。

目录1、双向电路的基本格式 (2)2、控制条件 (3)2.1、双向信号作一个信号的输入,作另一信号的输出 (3)2.2、双向信号既做输出又做输出 (4)3、实例说明-INOUT端口仿真暨三态门仿真 (6)3.1、三态门的原理与仿真三态总线 (6)3.3、VHDL 的三态门实现与仿真 (7)参考文献 (12)VHDL语言程序设计中INOUT端口的使用与实例分析摘要:VHDL是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。

与另外一门硬件描述语言Verilog HDL相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且VHDL 具有设计重用、大型设计能力、可读性强、易于编译等优点逐渐受到硬件设计者的青睐。

但是,VHDL是一门语法相当严格的语言,易学性差,特别是对于刚开始接触VHDL的设计者而言,经常会因某些小细节处理不当导致综合无法通过。

VHDL共定义了5种类型的端口,分别是In, Out,Inout, Buffer及Linkage,实际设计时只会用到前四种。

本文主要讨论讨论如何正确使用INOUT端口。

关键词:VHDL;INOUT端口;三态门原理1、双向电路的基本格式工程应用中,双向电路是设计者不得不面对的问题.在实际应用中,数据总线往往是双向的.如何正确处理数据总线是进行时序逻辑电路设计的基础.在程序设计过程中,关键技术在于:实体部分必须对端口属性进行申明,端口属性必须为inout类型,在构造体需要对输出信号进行有条件的高阻控制.在双向电路的处理问题上,常用的处理方式有两种,在介绍双向电路的处理方式之前,先看看双向电路的基本格式:ENTITY bidir_pin IS(bidir : INOUT std_logic;oe, clk, from_core : IN std_logic;to_core : OUT std_logic;……END bidir_pin;ARCHITECTURE behavior OF bidir_pin ISBEGINbidir <= from_core WHEN oe=‘1’ ELSE “ZZZZ”;to_core <= bidir;END behavior;该程序揭示了双向电路的处理技巧,首先在实体部分bidir属于双向信号,在端口定义时,端口属性为inout类型,即把bidir信号作为输入三态输出. 语句“bidir <= from_core WHEN oe=‘1’ ELSE “ZZZZ”;”表示bidir信号三态输出,语句”to_core <= bidir;”把bidir信号作为输入信号.由此可见,双向电路在程序设计中,didir输入当着普通的in类型,而在输出时,需要加一定的控制条件,三态输出.问题的关键在于:如何确定这个条件?2、控制条件2.1、双向信号作一个信号的输入,作另一信号的输出ENTITY bidir ISPORT(bidir : INOUT STD_LOGIC_VECTOR (7 DOWNTO 0);oe, clk : IN STD_LOGIC;from_core : IN STD_LOGIC_VECTOR (7 DOWNTO 0);to_core : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));END bidir;ARCHITECTURE logic OF bidir ISSIGNAL a : STD_LOGIC_VECTOR (7 DOWNTO 0);SIGNAL b : STD_LOGIC_VECTOR (7 DOWNTO 0);BEGINPROCESS (clk)BEGINIF clk = '1' AND clk'EVENT THENa <= from_core;to_core <= b;END IF;END PROCESS;PROCESS (oe, bidir)BEGINIF( oe = '0') THENbidir <= "ZZZZZZZZ";b <= bidir;ELSEbidir <= a;b <= bidir;END IF;END PROCESS;END logic;这种设计方式叫做寄存双向信号的方法.本设计中bidir为双向信号,from_core为数据输入端,to_core为数据输出端,oe为三态输出使能,clk为读写数据的时钟.在程序设计中,需要定义两个signal a和b信号.a信号用于输入数据from_core的寄存器,b用于输出数据to_core的寄存器.采用寄存器的方法需要设计两个进程,一个进程把a,b信号在时钟的控制下负责端口的输入信号from_core和端口输出信号to_core的连接,这一步实现了寄存双向的功能.另外一个进程则负责信号a,b和双向口之间的赋值关系.本设计只揭示了简单的双向信号操作方式,即bidir既可以作为from_core的输出,又可以作为to_core的输入2.2、双向信号既做输出又做输出上例是最简单的双向信号应用的特例.在实际的工程中,双向信号既做信号的输入,又做信号的输出,常见的数据总线就是这种操作模式.library IEEE;use IEEE.STD_LOGIC_1164.all;entity dir_data isport(clk : in STD_LOGIC;rst : in STD_LOGIC;rw : in STD_LOGIC;address : in STD_LOGIC_VECTOR(1 downto 0);data : inout STD_LOGIC_VECTOR(7 downto 0));end dir_data;architecture arc_dir of dir_data issignal data_in : STD_LOGIC_VECTOR(7 downto 0);signal data_out: STD_LOGIC_VECTOR(7 downto 0);signal reg_a: STD_LOGIC_VECTOR(7 downto 0);signal reg_b: STD_LOGIC_VECTOR(7 downto 0);begindata_in<=data;d1:process(clk,rst,rw)beginif rst='1' thenreg_a<= (others=>'0');reg_b<= (others=>'0');elsif clk'event and clk='1' then if rw='1' thenif address="00" thenreg_a<=data_in;elsif address="01" thenreg_b<=data_in;else null;end if;else null;end if;else null;end if;end process d1;d2:process(clk,rw,reg_a,reg_b) beginif clk'event and clk='1' thenif rw='0' thenif address="00" thendata_out<=reg_a;elsif address="01" thendata_out<=reg_b;else null;end if;else null;end if;else null;end if;end process d2;data<=data_out when (rw='0' and address(1)='0') else(others=>'Z');end arc_dir;3、实例说明-INOUT端口仿真暨三态门仿真3.1、三态门的原理与仿真三态总线三态输出缓冲器,即三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。

VHDL的语句常见错误分析赵靖;王延斌;冯光升;马春光【摘要】VHDL is one of the top hardware circuit design languages,and is important in teaching information science.Based on the VHDL features,we describe common problems and their solutions in VHDL teaching.The problem in the teaching are the misusing sequential and concurrent statements,the assigning value of signal and variable,and the variable initialization approach.The improvement in future teaching is prosented.%VHDL是硬件电路设计的首选语言之一,也是信息类专业重要讲授内容。

本文结合VHDL的特点,分别阐述了在VHDL教学中遇到的常见问题,这些相关问题涉及到顺序与并发描述语句错用、信号和变量赋值的区分以及变量初始化的方法及时刻,对每个问题给出了具体的实例和正确的解决方法,并提出了今后教学中的改进。

【期刊名称】《电气电子教学学报》【年(卷),期】2012(034)004【总页数】3页(P98-100)【关键词】VHDL;教学方法;顺序;并发【作者】赵靖;王延斌;冯光升;马春光【作者单位】哈尔滨工程大学计算机学院,黑龙江哈尔滨150001;哈尔滨工业大学机电学院,黑龙江哈尔滨150001;哈尔滨工程大学计算机学院,黑龙江哈尔滨150001;哈尔滨工程大学计算机学院,黑龙江哈尔滨150001【正文语种】中文【中图分类】G424.1;TP391.77在“VLSI及硬件描述语言”课程中,用VHDL语言描述系统硬件行为时,按语句执行顺序对其进行分类,可以分为顺序(Sequential)描述语句和并发(Concurrent)描述语句。

vhdl语言常用实例-回复

VHDL语言常用实例

VHDL是一种硬件描述语言,广泛应用于数字系统的设计与验证中。

它提供了一种结构化的方式来描述电子系统的行为和结构。

在本篇文章中,将详细介绍VHDL语言的常用实例,并一步一步回答与之相关的内容。

1. VHDL的简介

VHDL(VHSIC(Very High-Speed Integrated Circuit)Hardware Description Language)是一种用于描述和设计数字电路的硬件描述语言。

它是由美国国防部在20世纪80年代初提出并发展起来的,旨在解决高速集成电路设计的问题。

2. VHDL实例的编写步骤

在编写VHDL实例之前,首先需要确定所要设计的电路的功能和结构。

接下来,可以根据电路的需求使用VHDL语言的各种特性来编写代码。

编写的过程可分为以下步骤:

步骤一:定义实体

在VHDL中,实体(Entity)用于描述电路的接口和输入输出信号的属性。

在定义实体时,需要指定实体的名称、输入输出端口以及信号类型。

步骤二:定义体(Architecture)

定义体(Architecture)用于描述电路的功能和行为。

在定义体时,需要使用VHDL语言提供的语法和特性来描述所需的功能。

步骤三:模块化设计

在VHDL中,可以使用模块化设计来实现复杂电路的描述和功能。

可

以将电路划分为多个不同的模块,每个模块负责实现不同的功能。

通过将这些模块连接在一起,可以构建复杂的电路。

步骤四:仿真和验证

在编写完VHDL代码后,可以使用仿真工具对代码进行验证。

通过仿真,可以模拟出电路的行为并检查其功能是否符合预期。

3. VHDL语言常用实例

VHDL语言提供了丰富的语法和特性,可用于描述各种不同的电路和功能。

以下是几个常用的VHDL语言实例的示例:

实例一:2-to-1多路选择器

该实例描述了一个基本的2-to-1多路选择器电路。

此电路有两个输入信号A和B,一个选择信号S,一个输出信号Y。

当选择信号为"0"时,输出信号等于输入信号A,反之,输出信号等于输入信号B。

实例二:4位全加器

该实例描述了一个4位全加器电路。

该电路有三个输入信号A、B和Cin,以及两个输出信号Sum和Cout。

输入信号A和B分别代表两个加数,Cin代表进位,输出信号Sum表示和,Cout表示进位。

实例三:16位计数器

该实例描述了一个16位的二进制计数器电路。

该电路有一个时钟信号CLK作为计数器的时钟源,以及一个输入信号RESTART,用于将计数器重置为零。

计数器的输出信号为16位的二进制数值。

这些实例只是VHDL语言中常见的一些例子,VHDL的应用远不止这些。

根据实际需求和功能复杂性,可以使用VHDL语言编写各种不同的电

路和功能。

总结:VHDL语言提供了一种结构化的方式来描述和设计数字系统。

在编写VHDL代码时,可以按照一定的步骤来进行,包括定义实体、定义体、模块化设计和仿真验证。

VHDL语言常用实例包括2-to-1多路选择器、4位全加器和16位计数器等。

这些例子展示了VHDL语言在电路设计中的灵活性和强大功能。

通过使用VHDL语言,设计人员可以快速、准确地描述和设计各种复杂的数字系统。