反激 同步整流设计

- 格式:doc

- 大小:218.50 KB

- 文档页数:7

由于传统开关电源存在对电网造成谐波污染以及工作效率低等问题,因此目前国内外各类开关电源研究机构正努力寻求运用各种高新技术改善电源性能[1]。

其中,在开关电源设计中通过功率因数校正PFC(Power Factor Correction)技术降低电磁污染及利用同步整流技术提高效率的研发途径尤其受到重视。

参考文献[2-3]专题研讨了有源功率因数校正(APFC)技术;参考文献[4]综述了单相并联式技术的最新发展;参考文献[5-6]分别优化设计了带负载电流反馈、并联式PFC芯片的AC/DC变换器和升压式PFC变换器,但所设计的电源效率及功率因数分别在85%和90%以下,其性能还有待进一步提高。

本文设计并制作了一种高效低电磁污染的开关电源样机。

测试结果表明,该电源具有优良的动态性能、较高的功率因数和工作效率,且控制简单,故具有一定的实际应用价值。

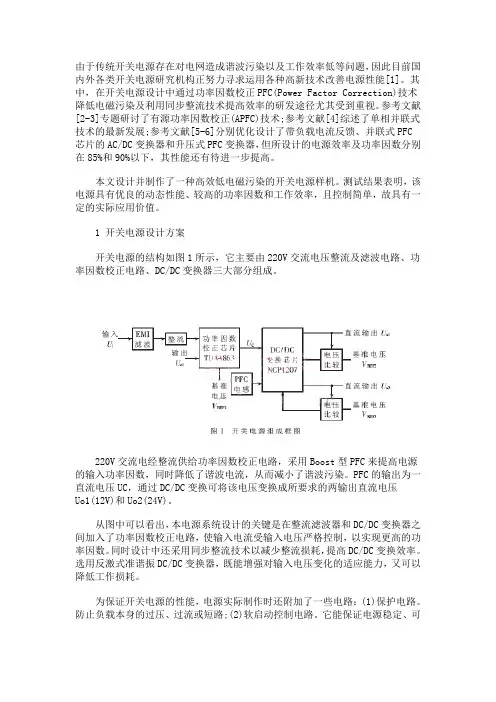

1 开关电源设计方案开关电源的结构如图1所示,它主要由220V交流电压整流及滤波电路、功率因数校正电路、DC/DC变换器三大部分组成。

220V交流电经整流供给功率因数校正电路,采用Boost型PFC来提高电源的输入功率因数,同时降低了谐波电流,从而减小了谐波污染。

PFC的输出为一直流电压UC,通过DC/DC变换可将该电压变换成所要求的两输出直流电压Uo1(12V)和Uo2(24V)。

从图中可以看出,本电源系统设计的关键是在整流滤波器和DC/DC变换器之间加入了功率因数校正电路,使输入电流受输入电压严格控制,以实现更高的功率因数。

同时设计中还采用同步整流技术以减少整流损耗,提高DC/DC变换效率。

选用反激式准谐振DC/DC变换器,既能增强对输入电压变化的适应能力,又可以降低工作损耗。

为保证开关电源的性能,电源实际制作时还附加了一些电路:(1)保护电路。

防止负载本身的过压、过流或短路;(2)软启动控制电路。

它能保证电源稳定、可靠且有序地工作,防止启动时电压电流过冲;(3)浪涌吸收电路。

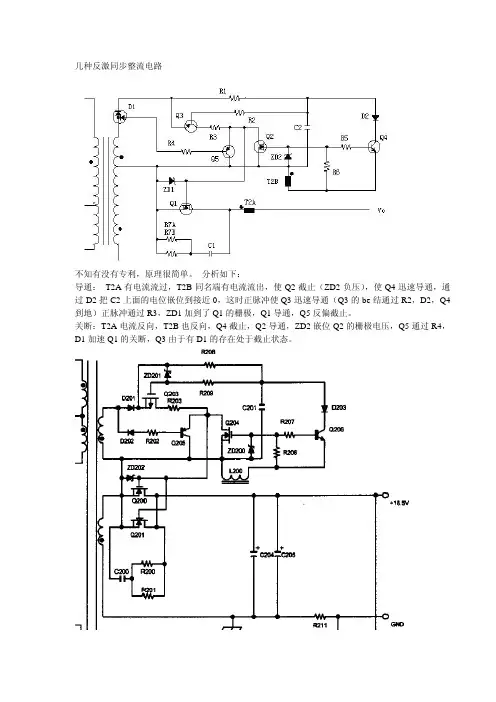

几种反激同步整流电路

不知有没有专利,原理很简单。

分析如下:

导通: T2A有电流流过,T2B同名端有电流流出,使Q2截止(ZD2负压),使Q4迅速导通,通过D2把C2上面的电位嵌位到接近0,这时正脉冲使Q3迅速导通(Q3的be结通过R2,D2,Q4到地)正脉冲通过R3,ZD1加到了Q1的栅极,Q1导通,Q5反偏截止。

关断:T2A电流反向,T2B也反向,Q4截止,Q2导通,ZD2嵌位Q2的栅极电压,Q5通过R4,D1加速Q1的关断,Q3由于有D1的存在处于截止状态。

线路工作过程是这样的:18V正向输出的时候,通过Q200,Q201管体内寄生二极管流过一股小电流,从而在L200上感应出电压,左正右负,Q204负偏截止,Q206正偏导通,促使Q203导通,从而Q200,Q201彻底导通,这样完成正向输出过程。

反之则工作状态相反,完成反向关闭过程。

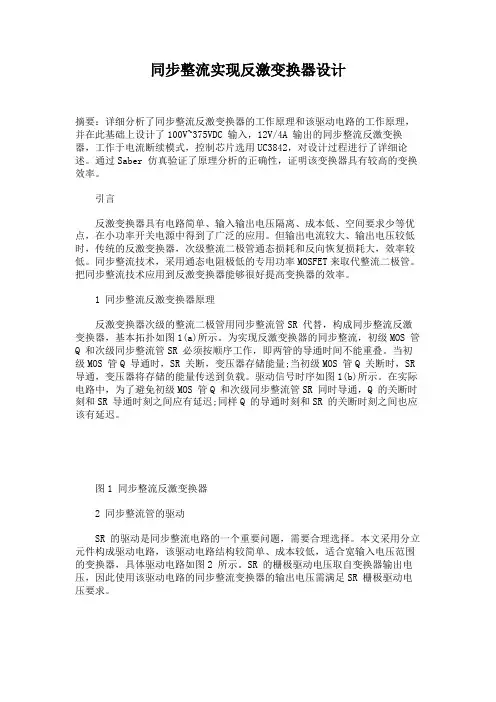

同步整流实现反激变换器设计摘要:详细分析了同步整流反激变换器的工作原理和该驱动电路的工作原理,并在此基础上设计了100V~375VDC 输入,12V/4A 输出的同步整流反激变换器,工作于电流断续模式,控制芯片选用UC3842,对设计过程进行了详细论述。

通过Saber 仿真验证了原理分析的正确性,证明该变换器具有较高的变换效率。

引言反激变换器具有电路简单、输入输出电压隔离、成本低、空间要求少等优点,在小功率开关电源中得到了广泛的应用。

但输出电流较大、输出电压较低时,传统的反激变换器,次级整流二极管通态损耗和反向恢复损耗大,效率较低。

同步整流技术,采用通态电阻极低的专用功率MOSFET来取代整流二极管。

把同步整流技术应用到反激变换器能够很好提高变换器的效率。

1 同步整流反激变换器原理反激变换器次级的整流二极管用同步整流管SR 代替,构成同步整流反激变换器,基本拓扑如图1(a)所示。

为实现反激变换器的同步整流,初级MOS 管Q 和次级同步整流管SR 必须按顺序工作,即两管的导通时间不能重叠。

当初级MOS 管Q 导通时,SR 关断,变压器存储能量;当初级MOS 管Q 关断时,SR 导通,变压器将存储的能量传送到负载。

驱动信号时序如图1(b)所示。

在实际电路中,为了避免初级MOS 管Q 和次级同步整流管SR 同时导通,Q 的关断时刻和SR 导通时刻之间应有延迟;同样Q 的导通时刻和SR 的关断时刻之间也应该有延迟。

图1 同步整流反激变换器2 同步整流管的驱动SR 的驱动是同步整流电路的一个重要问题,需要合理选择。

本文采用分立元件构成驱动电路,该驱动电路结构较简单、成本较低,适合宽输入电压范围的变换器,具体驱动电路如图2 所示。

SR 的栅极驱动电压取自变换器输出电压,因此使用该驱动电路的同步整流变换器的输出电压需满足SR 栅极驱动电压要求。

图2 驱动电路该驱动电路的基本工作原理:电流互感器T2 与次级同步整流管SR 串联在同一支路,用来检测SR 的电流。

APPLYING STSR3 TO SA80T-3115-1412Yukan YuPrepared by :Yukan YuChecked by :Approved by :Name SignaturePRE-xxREV DATE RemarkREF. No. : Dxx-xxx1. ABSTRACTThis report will give you a brief introduction of STSR3. Then it will describe you the IC’s performance when it was used as a controller of the secondary synchronous rectifier in SA80T-3115-1412 (an 80W Flyback topology switched mode power supply).2. STSR3 INTRODUCTIONTable 1: Pin DescriptionPin Number Pin Name Pin Function1N/C Not internally connected2Vcc Supply input from 4V to 5.5V3SETANT Sets the anticipation in turning-off the OUTgate4CK Synchronisation for IC’s operation5INHIBIT Discontinuous Mode Detector6SGLGND Reference for all the control logic signals7OUTGate Output for MOSFET Gate Drive8PWRGND Reference for power signalsFigure 1: Block Schematic3. GENERAL DEVICE DESCRIPTIONFigure 2 shows the typical application schematic. From a synchronising clock input, withdraw on the secondary side of the isolation transformer, STSR3 generates a driving signal with set dead times with respect to the primary side PWM signal. The IC operation prevents secondary side shoot-through conditions at turn-on of the primary switch providing anticipation in turning-off of the output. This smart function is implemented by a fast cycle-after-cycle logic control mechanism, based on a high frequency oscillator synchronised by the clock signal.Comparing with the traditional discrete SR circuit, this device has two advantages. One is that STSR3 can obtain the synchronisation signal directly on the secondary side. We don’t need a current transformer or something else to detect the sync signal, the space are saved. Moreover, this device has some smart functions such as turn-off anticipation, automatic turn-off according to the duty-cycle. These functions will be explained in detail later.Figure 2: Application SchematicTable 2: Components NotesPin Name NotesVcc100nF ceramic capacitor C3 is put between Vcc and PWRGND. U3 (ST78L05) isa standard voltage regulator to provide 5V supply voltage. D7 protects Vcc fromvoltages higher than 5.6V. C7 is ST78L05’s input capacitor (330nF ceramic), C8 isST78L05’s output capacitor (150nF ceramic).SGLGND C4 is a 100nF ceramic bypass capacitor. This capacitor is very close to Vcc and SGLGND pins of STSR3.CK D2 blocks the high voltage coming from the SR Drain. R5 is CK’s series resistor.R1, R2, R4, C2, C5 and U1 make up the external clock detector. (U1, a non-inverting buffer ST74V1T70). D3 protects the device from voltages higher than Vcc(not necessary is U1 is used).INHIBIT Connecting this pin to the Drain of the power mosfet allows operation in DCM. R8 limits the current to diode D6 when SR Drain voltage is higher than Vcc. D6protects INHIBIT pin from voltage higher than Vcc. D5 protects INHIBIT pin fromnegative voltage. D4, R7, R6 and C11 is a circuit to provides a negative voltage anda proper blanking time to cover the ringing caused by primary switch turn off. SETANT When this pin is connected to SGLGND, the anticipation time in turning off the synchronous rectifier mosfet is about 75ns.OUTGate R9 is the Gate series resistor (typically 0ohm). D8 speeds up turn-off of SR Mosfet if R9 is used.PWRGND Q1 is Synchronous Mosfet IRF530. D1 (63CTQ100) is a Schottky Rectifier in parallel to Synchronous Mosfet can increase converter efficiency due to low dropvoltages during dead time. C1 and R3 is a small snubber to reduce SynchronousMosfet turn-off spike.4. SYNCHRONIZATIONIC synchronisation is obtained directly on the secondary side using the voltage across the Synchronisation mosfet as information for the switching transitions. CK pin is the input for the synchronisation signal. The minimum threshold on the CK pin is 2.5V and the maximum voltage on this pin is limited to Vcc. So the input voltage range for this pin is 1:2. Of cause, a resistor divider can provide the correct voltage range for the CK pin. But the adapter works in wide range AC input from 85Vac to 260Vac. Even with a PFC circuit, the input voltage range of the flyback converter is typically 180V to 390V, which is beyond the IC’s guaranteed range.There is another problem during DCM. Since the signal taken on the secondary winding of the transformer is not a square waveform, but presents some oscillations. These oscillationmust not be understood by the IC as switching transitions.(See Fig 3)Figure 3: Without external Peak DetectorRemark: Ch1---CK; Ch2---OUTGateSo we need an external Peak Detector. As Fig 2 shows, when the SR MOSFET is on or its body diode is conducting, Vck is low, when the MOSFET is off, the Vck is 5V. R2 and C2 form a low pass filter; R1 and C5 group reduce the delay caused by the filter. ST741T70 eliminates the noise. This external Peak Detector assures correct operation of STSR3 both in discontinuous and continuous mode providing to CK a pure square waveform. (See Fig 4)Figure 4: With External Peak DetectorRemark: Ch1---SR Mosfet Drain; Ch2---CK; Ch3---OUTGate5. INHIBIT OPERATIONIf discontinuous mode operation is wanted, the synchronous mosfet must be turned of when the current is zero. Then the Inhibit pin is able to turn off synchronous mosfet when its current is approaching zero allowing discontinuous mode operation for the converter. Because there is an internal comparator with a -25mV threshold. At the beginning of the off time (when CK goes to low level), OUTGate goes high. If the voltage on Inhibit is higher than -25mV, OUTGate becomes low; if the voltage on Inhibit is lower than -25mV, OUTGate is kept high until the voltage reaches -25mV. (See Fig 5)Although INHIBIT pin allows operation in Discontinuous Mode, the –25mV threshold could be sensitive to the ringing present at the SR Mosfet drain, causing incomplete turn on of OUTGate. (See Fig 6) This inconvenient can be avoided using the clock signal to provide a negative voltage to INHIBIT pin acting as a blanking time. (See Fig 7) As Fig 2 shows, C6 and R6 determine the blanking time value. This time has to last the necessary time to cover the ringing caused by primary switch turn off. (Typically 500ns in this adapter)Figure 5: Inhibit operationRemark: Ch1---INHIBIT; Ch2---OUTGate Figure 6: Without blanking timeRemark: Ch1---INHIBIT; Ch2---OUTGateFigure 7: Without blanking timeRemark: Ch1---INHIBIT; Ch2---OUTGate6. ANTICIPATIONWhen the primary Mosfet is turned-on, the voltage Vs tends to go negative. If the synchronous mosfet is turned off with some delay a short circuit loop between primary side and secondary side occurs. In order to avoid this bad condition, synchronous mosfet must be turned off, that's the function of the Anticipation.And the Ant is possible to choose from 75ns to 250ns using SETAnt pin under different voltage. (See Fig 7 and Fig 8)Figure 8: SETAnt is connected to GNDRemark: Ch1---CK; Ch2---OUTGateFigure 9: SETAnt is connected to VccRemark: Ch1---CK; Ch2---OUTGate7. NO LOAD AND LIGHT LOAD OPERATIONWhen the duty-cycle is lower than 15%, an internal feature of the STSR3 allows a total shutdown of OUTGate and of most parts of the device, causing a reduction of the power consumption. The IC starts to operate again when duty-cycle is higher than 18%, therefore having a 3% of hysteresis.Applying a surge load, we can see this operation. (See in Fig 9 and Fig 10)Figure 10: The waveform of output current (2A/10mV)Figure 11: The OUTGate under a varying duty-cycleRemark: Ch1---CK (without external detector); Ch2---OUTGate; Ch3---output current8. MEASUREMENT8.1.Turn-off SpikeDue to the bad performances of the synchronous Mosfet in terms of Trr and Qrr a big voltage spike is present at turn-off the Mosfet. This spike is dependent on the amount of current carried by the body diode during turn-off. So, once the converter steps into continuous mode, the big spike will occur. (See Figure 12)Figure 12: Turn-off spike (without SK-diode)Remark: Ch1--- SR Mosfet Drain; Ch2---OUTGateThis spike can be reduced by adding a schottky and a snubber circuit. But due to the stray inductance of the leads and of the tracks, the current takes some time to pass from the body diode to the schottky diode. Then the spike can not be eliminated completely. (See Fig 13) So a good PCB layout is very important here.Figure 13: Turn-off spike (with SK-diode)8.2. EfficiencyIn order to avoid the big turn-off spike, efficiency was measured at full load (19V/4.2A) with 230Vac input in comparison with schottky rectification (two MBR20100CT-1 in parallel). Then the converter was running in a discontinuous mode.Table 3: Efficiency test resultRunning Time (minute)SR Rectification (%)SK Rectification (%)1083.9186.132083.9686.13083.986.24083.9786.19From above test data, we can not see the advantage of the synchronous rectification. Because the power saved due to low Rds (on) of the mosfet, is lost in gate drive losses, switching losses andSTSR3 power consumption. On the other hand, the 5V drive voltage is not high enough to get a low Rds(on). Significant improvement of synchronous rectification versus diode rectification can be achieved with higher output current (>5A) and DCM.9. CONCLUSION-External peak detector is necessary when input voltage varies by 2:1 or higher.-Converter can work properly in DCM due to the use of INHIBIT pin.-Smart turn-off anticipation timing can avoid secondary side shoot-through condition.-STSR3 has an automatic turn off for dutycycle less than 13%-Turn-off spike is a problem when converter works in CCM.-Io>5A, DCM is recommended in applying STSR3 to get a better efficiency.。

反激同步整流MOS短路尖峰高一、简介反激同步整流MOS短路尖峰高是指在反激同步整流MOS电路中,当短路故障发生时,尖峰电流较高的现象。

在工程实践中,这种现象会导致电路的不稳定和损坏,因此需要对其进行深入的分析和研究。

二、反激同步整流MOS电路1. 反激同步整流MOS电路是一种常用于电源转换器中的电路拓扑结构。

它利用同步整流MOS管来代替常规二极管,实现更高的效率和更低的功耗。

2. 反激同步整流MOS电路通常由反激变压器、开关管、滤波电感、输出电容等组成。

其工作原理是利用变压器的缓冲作用,使得开关管能够按照一定的频率进行通断,从而实现电能的转换和输出。

三、短路故障1. 短路故障是指两个或多个电器设备或电路组件之间产生直接或间接的短路,使得电流绕开正常的路径,直接流通而导致电路的短路现象。

在反激同步整流MOS电路中,由于短路故障引起的异常电流会使得电路元件的工作状态发生改变,进而影响整个电路的正常工作。

四、短路故障引起的尖峰电流1. 短路故障引起的尖峰电流是指在反激同步整流MOS电路中,由于短路故障引起的瞬态电压和电流急剧变化所造成的高峰值电流现象。

这种尖峰电流会对电路中的元件和元器件产生不可忽视的影响。

2. 尖峰电流的产生原因主要包括:反激变压器中的互感耦合变压器效应、电容和电感元件的瞬态响应、开关管的快速开关等。

这些因素共同作用,导致了短路故障产生的尖峰电流。

五、影响1. 短路故障引起的尖峰电流会对反激同步整流MOS电路及其所在的电源转换器系统造成多方面的影响。

高峰值电流会导致电路元件承受较大的压力,可能造成元件的损坏甚至烧毁。

尖峰电流也会引起电源转换器系统的不稳定,甚至引发系统失效。

在一些对电流波形要求较高的应用中,尖峰电流也可能引起电路的性能不达标。

六、解决方案1. 针对短路故障引起的尖峰电流问题,可以采取以下一些解决方案:一是增加电路中的限流电感和限流电容等元件,通过限制电流的瞬时变化来降低峰值电流;二是改进反激同步整流MOS电路的控制算法和参数设计,使得在短路故障发生时能够及时限制尖峰电流的产生并保护电路元件;三是优化电源转换器系统的设计和结构,减小短路故障对整个系统的影响。

张恒浩(1989—),男,高级工程师,主要从事开关电源研究。

宋浩谊(1977—),男,高级工程师,主要从事开关电源研究。

黄 超(1985—),男,高级工程师,主要从事开关电源研究。

一种反激变换器自驱同步整流设计张恒浩, 宋浩谊, 黄 超(中国电子科技集团公司第二十四研究所,重庆 400060)摘 要:在小功率开关电源中反激变换器应用广泛,同步整流技术的引入使反激变换器的工作效率得到显著提升。

基于自驱同步整流技术原理,提出一种改进的反激变换器电压自驱同步整流线路。

功率开关具备自动开通和定时关断功能,实现了宽输入电压范围的高可靠同步整流,最后实验验证了设计方案。

关键词:反激变换器;同步整流;自驱;功率开关中图分类号:TM46 文献标志码:A 文章编号:2095 8188(2021)11 0080 05DOI:10.16628/j.cnki.2095 8188.2021.11.012DesignofSelf drivenSynchronousRectificationforFlybackConverterZHANGHenghao, SONGHaoyi, HUANGChao(SichuanInstituteofSolidStateCircuits,ChinaElectronicsTechnologyGroupCorporation,Chongqing400060,China)Abstract:Flybackconverteriswidelyusedaslowpowerswitchingpowersupply.Theefficiencyofflybackconverterisgreatlyimprovedwiththeintroductionofsynchronousrectificationtechnology.Basedontheprincipleofself drivensynchronousrectificationtechnology,animprovedvoltageself drivensynchronousrectificationcircuitofflybackconverterispresented.Thedesignschemeisverifiedbyexperiments.Keywords:flybackconverter;synchronousrectification;self driven;powerswitch0 引 言直流稳压电源主要分为线性电源和开关电源两种,线性电源存在体积大、效率低、质量大等缺点,因此应用受到限制[1]。

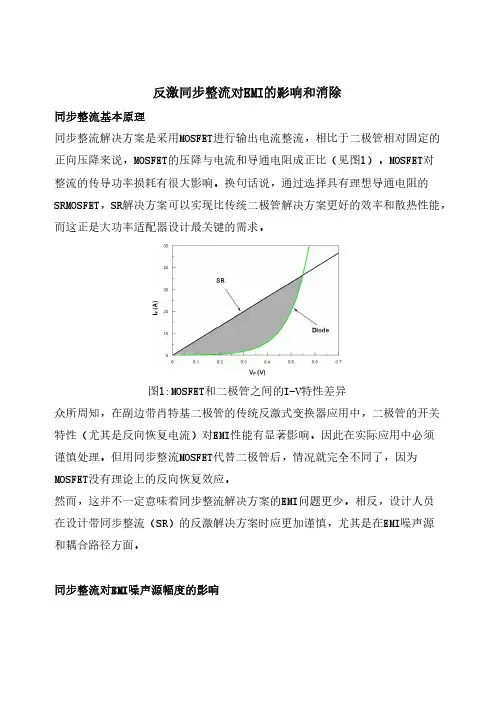

反激同步整流对EMI的影响和消除同步整流基本原理同步整流解决方案是采用MOSFET进行输出电流整流,相比于二极管相对固定的正向压降来说,MOSFET的压降与电流和导通电阻成正比(见图1)。

MOSFET对整流的传导功率损耗有很大影响。

换句话说,通过选择具有理想导通电阻的SRMOSFET,SR解决方案可以实现比传统二极管解决方案更好的效率和散热性能,而这正是大功率适配器设计最关键的需求。

图1:MOSFET和二极管之间的I-V特性差异众所周知,在副边带肖特基二极管的传统反激式变换器应用中,二极管的开关特性(尤其是反向恢复电流)对EMI性能有显著影响。

因此在实际应用中必须谨慎处理。

但用同步整流MOSFET代替二极管后,情况就完全不同了,因为MOSFET没有理论上的反向恢复效应。

然而,这并不一定意味着同步整流解决方案的EMI问题更少。

相反,设计人员在设计带同步整流(SR)的反激解决方案时应更加谨慎,尤其是在EMI噪声源和耦合路径方面。

同步整流对EMI噪声源幅度的影响要了解同步整流对EMI噪声源的影响,首先要详细了解同步整流的工作原理。

大多数控制器基于漏源电压(VDS)的直接检测来驱动同步整流(SR)MOSFET,因为它不需要与原边进行通信且降低了总BOM成本。

图2显示出SRMOSFET的导通和关断通常由两个阈值来控制。

它们都是负电压阈值,可以确保SRMOSFET在反向偏置时始终安全关断。

图2:反激SR解决方案的基本工作原理由上图可以看出,两端的二极管有很短的导通时间:刚好在器件导通之前和同步整流(SR)MOSFET关断之后。

因此,时序控制对同步整流(SR)控制器来说至关重要,因为这两个导通时间会引入额外的传导损耗(时间越长损耗越严重)。

而且如果关断时间过长,则可能会因为MOSFET二极管比较差的特性而导致SR关断后出现严重的反向恢复电流。

图3:SR提前关断导致的高尖峰电流和电压图3显示了二极管的反向恢复电流由于SR提前400ns关断而上升到9A,然后由于漏电感又导致80V高压尖峰。

一种反激式同步整流线路的研究摘要:本文介绍了一种反激式同步整流线路的设计方案,对电路损耗及改进措施进行了分析,并通过对线路的试验验证及实际产品测试,该线路能够有效提高单端反激式产品的转换效率。

线路稳定,能够广泛应用于电源产品的设计中。

关键词:反激式;同步整流;转换效率1引言随着电子技术的不断发展,人们对电子设备的性能要求越来越高,与此同时,电子设备对配套电源的要求也越来越高,供电电源的小型化、高功率密度化尤为突出,使得我们对设计高效率电源产品的紧迫感越来越强。

电源产品的损耗主要由3部分组成:即功率MOSFET的损耗,变压器的磁损和铁损,以及输出整流管的损耗。

由于目前使用的整流管的导通压降普遍较大,导致输出整流管的损耗尤为突出。

以致电源在低压大电流输出场合效率很难提升,在此背景下,寻求低压降的输出整流方案迫在眉睫,而采用低导通压降MOSFET来代替二级管整流成为一种解决方案。

本文介绍一种应用于单端反激式线路的同步整流技术,能够有效降低线路损耗,提高产品的转换效率。

2同步整流线路的研究2.1同步整流反激变换器工作原理基于同步整流技术的反激式线路如图1所示。

线路的基本工作原理为:当MOS管T1导通时,整流MOS管T2关断,变压器B1储存能量,输出电容C O给负载R L供电;当MOS管T1截止时变压器绕组电压反向,T2导通充电整流管的作用,实现同步整流,变压器将储存的能量传递到次级,给负载供电,同时也给电容C O充电,进入下一个周期后重复上述过程。

图12.2同步整流损耗分析同步整流线路的整流损耗主要为MOS管的损耗,它的损耗主要包括三个方面:导通损耗P on、驱动损耗P dr及开关损耗P sw。

(1)导通损耗分析功率MOS管的导通损耗P on是指当MOS管打开的时候,并且驱动和开关波形达到稳定时,功率MOS管处于导通状态时的损耗。

P on=I in2×R on /2,式中I in为输入端的稳态电流,R on为MOS管的导通电阻。

同步整流反激电路同步整流反激电路是一种常用的电路结构,用于将交流电源转换为直流电源。

本文将介绍同步整流反激电路的工作原理、优点和应用。

同步整流反激电路是一种将交流电源转换为直流电源的电路结构。

它主要由一个MOSFET开关管、一个输出电感、一个输出滤波电容和一个二极管组成。

在工作时,MOSFET开关管会周期性地开关,使得电感储能和输出滤波电容充电,然后二极管导通,将储能的电荷传递给输出滤波电容,从而形成直流输出。

同步整流反激电路的工作原理是利用MOSFET开关管的导通和截止来实现电感储能和输出电容充电的过程。

当MOSFET开关管导通时,电感的电流线性增加,储存能量;当MOSFET开关管截止时,电感的能量会转移到输出滤波电容上。

通过控制MOSFET的开关时间,可以实现对输出电压的调节。

同步整流反激电路相较于传统的整流电路有一些显著的优点。

首先,同步整流反激电路的效率更高。

由于MOSFET开关管的导通和截止时间可以精确控制,可以使电路的开关损耗最小化。

其次,同步整流反激电路的输出纹波更小。

传统的整流电路在输出时会产生较大的纹波,而同步整流反激电路通过电感和输出滤波电容的储能和传递过程,可以有效地降低输出纹波。

此外,同步整流反激电路还具有体积小、重量轻、成本低等优点。

同步整流反激电路在实际应用中有广泛的用途。

首先,它常被用于交流-直流电源转换器中。

交流-直流电源转换器是电子设备中常见的电源模块,同步整流反激电路在其中起到关键作用。

其次,同步整流反激电路也被广泛应用于LED驱动电路中。

由于LED对电压和电流的要求较高,同步整流反激电路的高效率和低纹波特性使其成为LED驱动电路的理想选择。

此外,同步整流反激电路还可以用于太阳能充电器、电动汽车充电器等领域。

总结来说,同步整流反激电路是一种常用的电路结构,可以将交流电源转换为直流电源。

它具有高效率、低纹波等优点,并在交流-直流电源转换器、LED驱动电路等领域得到广泛应用。

反激式同步整流的工作原理

反激式同步整流是一种通过控制开关管的开关状态来实现的电源转换技术,常用于高效率的电力转换器中。

工作原理如下:

1. 输入电压施加在反激式同步整流器的输入端,开关管S1和S2分别连接到输入端和输出端。

2. 当S1导通时,输入电流通过S1流入整流器的输出端,此时二极管D2导通,电源能量被储存在输出端的电容电压中。

3. 当S1关断时,输入电流被强制中断,此时二极管D1具有正向电压,导通以供给输出负载电流。

4. 当S1关断后,S2导通,此时输出负载电压仍为源状态,二极管D2不导通,电容电压没有被完全放电。

5. 当S2关闭时,输出电容电压通过负载流向输入端,此时D2具有反向电压,始终不导通。

整流器的工作状态回到了初始状态,等待下一次周期的输入电流。

通过控制开关管的开关状态,反激式同步整流器可以实现高效率的电能转换,减

少功耗和热损耗。

它具有电流反馈控制功能,可以根据负载需求精确地调整开关管的导通和关断时间,实现更好的电压稳定性和效率。

一种反激同步整流DC-DC变换器设计摘 要: 对反激同步整流在低压小电流DC-DC变换器中的应用进行了研究,介绍了主电路工作原理,几种驱动方式及其优缺点,选择出适合于自驱动同步整流的反激电路拓扑,并通过样机试验,验证了该电路的实用性。

引 言:低压大电流DC-DC模块电源一直占模块电源市场需求的一半左右,对其相关技术的研究有着重要的应用价值。

模块电源的高效率是各厂家产品的亮点,也是业界追逐的重要目标之一。

同步整流可有效减少整流损耗,与适当的电路拓扑结合,可得到低成本的高效率变换器。

本文针对36V-75V输入,3.3V/15A 输出的二次电源模块,在分析同步整流技术的基础上,根据同步整流的特点,选择出适合于自驱动同步整流的反激电路拓扑,进行了详细的电路分析和试验。

反激同步整流基本的反激电路结构如图1。

其工作原理:主MOSFET Q1导通时,进行电能储存,这时可把变压器看成一个电感,原边绕组电流Ip 上升斜率由dIp/dt=Vs/Lp决定,磁芯不饱和,则Ip 线性增加;磁芯内的磁感应强度将从Br增加到工作峰值Bm;Q1关断时,原边电流将降到零,副边整流管开通,感生电流将出现在副边;按功率恒定原则,副边安匝值与原边安匝值相等。

在稳态时,开关导通期间,变压器内磁通增量△Φ应等于反激期间内的磁通变化量,即:△Φ=VsTon / Np=Vs'Toff / Ns从此式可见,如果磁通增量相等的工作点稳定建立时,变压器原边绕组每匝的伏-秒值必然等于副边每匝绕组的伏-秒值。

反激变换器的拓扑实际就是一个BUCK-BOOST组合的变换器拓扑的应用,而且如果副边采用同步整流,电路总是工作于CCM的模式下,其电压增益M=Vo/Vs=K·D/(1-D)(K为原副边匝数比)用PMOSFET和MOSFET替代图1中的萧特基二极管,可以实现同步整流的4种电路结构如图2和图3 反激电路的开关电压波形见图4,是标准的矩形波,非常适合同步整流驱动。

[收稿日期]2009-01-20 [作者简介]邓于(1960-),男,重庆市人,实验师.E -mail:dydydy120@ 2009年4月重庆文理学院学报(自然科学版)Ap r 1,2009 第28卷 第2期Journal of Chongqing University of A rts and Sciences (Natural Science Editi on )Vol 128 No 12反激同步整流DC -DC 变换器的设计邓 于,廖长荣,周召福(重庆文理学院 电子电气工程学院,重庆 永川 402160)[摘 要]以UC2843芯片为核心,设计出了一种单端反激式、宽电压输入、单路固定电压输出的15W 开关稳压电源,它能有效降低电源损耗、提高调整性能.其电路采用一种有别于RC 缓冲电路的新技术,结合电流型P WM 控制,利用反激变换器中的耦合电感与外加小容量电容器构成LC 谐振电路,能高效地完成关断感性负载的暂态缓冲,并能抑制二极管的反向恢复不良特性.实践证明:该技术能达到设计要求.[关键词]反激开关电源;同步整流;电流型;脉宽控制[中图分类号]T M910.2 [文献标识码]A [文章编号]1673-8012(2009)02-0005-06 随着脉宽调制(P WM )技术的发展,特别是P WM 控制技术的问世,电源效率由线性电源的30%~40%提高到65%~70%,因此,用工作频率为20kHz ~500kHz 之间的P WM 开关电源替代线性电源,可大幅度节约能源.所设计的新型的开关电源(平均功率200k W )具有频率高、动态响应快、可靠性好、稳压范围宽,且有先进的自动控制技术以及体积小等优势,具有非常好的应用前景[1,2].1 功能设计指标变压器的功能设计要求由表1和表2中的参数给出.表1 输入特性参数名称条件单位最小最大输入电压 V in =36~75VDC V3675最大输入电流V in =36VDC,Io =4.5A 0.6遥控ON OFF V in =36VDC,Io =4.5AV 01.2V3.510表2 输出特性参数名称条件单位最小最大输出电压范围V in =36~75VDC,Io =4.5A V 3.243.36负载调整率V in =48VDC,Io =0~4.5A %±0.5±0.6输出纹波(R MS )V in =36~75VDC,Io =4.5A mA 5080输出噪声(峰-峰值)V in =36~75VDC,Io =4.5AmA8010052 系统电路设计主拓扑电路采用成本低、可靠性高及稳压范围宽的反激拓扑电路;系统采取辅助绕组的方式提供辅助电源;启动电路如图1所示.采用晶体管Q 1、稳压二极管Z 1、电阻R 1、R 2、R 3、R 4、R 5以及二极管D 1和电容C 3组成的线性稳压电路来实现系统的启动.当系统完全启动起来且输出电压建立起来之后,由辅助绕组提供T 1-C 通过二极管D 2给UC2843提供辅助电源(Vcc ).此系统针对36V ~75V 直流输入,3.3V /4.5A 直流输出的二次电源模块,在分析同步整流技术的基础上,根据同步整流技术的特点,选择适合于自驱动同步整流的反激电路拓扑,进行了详细的电路分析和试验.图1 启动电路图 系统框图如图2所示.在系统启动的一刻由启动部分给P WM 控制芯片提供启动电压.当系统输出电源建立起来后,由辅助绕组给P WM 控制芯片脉宽,停止系统工作达到保护的作用;过流保护部分在输出电流超过5A 时控制P WM 控制芯片的3脚限制输出功率,达到过流保护的效应;电压采样部分和反馈环路共同作用,当负载调整或者输入电压变化时通过调整P WM 控制芯片输出脉宽的占空比来实现稳压的作用.图2 系统框图 反激同步整流原理如图3所示.主MOSFET在Q 1导通时进行电能储存,这时可把变压器看成一个电感,初级绕组电流I P 上升,斜率由d ip /d t =V s /L p 决定,磁芯不饱和时I P 线性增加,磁芯内的磁感应强度将从B r 增加到工作峰值B m ;Q 1关断时,初级电流从I P 开始下降,次级整流管开通,感生电流将出次级,由功率恒定原则可知次级安匝值与初级安匝值相等;在稳态时,开关导通期间变压器内磁通增量为Δφ=V r T on /N P =V S T off /N S .可以看出,如果磁通增量相等的工作点稳定建立,时变压器初级每匝的V /S 值和次级每匝的V /S 值相等.反激变换器的拓扑实际就是一个BUCK -BOOST 组合的变换器拓扑的应用.如果次级采用同步整流,电路总6是工作于CC M 的模式下,其电压增益M =V o /V s =K ・D /(1-D ),其中K 为匝数比.用MOSFET替代二极管实现同步整流[3].同步整流管的驱动方式有3种,第1种是半自驱动电路[4];第2种是自驱动同步整流[1];基于波形质量和调试方便,采取第3种外加驱动控制电路,如图4所示.其优点是驱动波形的质量高、调试方便,缺点是电路复杂、成本高.第3种电路在同步整流管的门限较小时可以使用,Q 1和Q 3是一对相反的信号.当P WM 控制片输出为高时,Q 1开通Q 3关断T 1存储能量;当P WM 控制片输出为低时,Q 1关断Q 3开通,此时T 1将能量传送到次级,经过Q 3整流后供给负载[5].图3 反激同步整流原理图图4 外驱电路图反激变压器工作频率设定在20kHz ~500kHz 之间,具体频率的选择应根据其成本、体积、效率等因素综合考虑.工作频率越高,则变压器的尺寸越小,但开关损耗会增加,因此频率确定在300kHz .电源的总输出功率包括所有次级输出功率、辅助输出(反馈回路)功率和输出整流管的损耗,其计算公式为[6]p o =(v o +v d )×I o +(v b +v db )×I b .(1)其中v o 为输出电压,I o 为输出电流,v d 为整流管压降,v b 为反馈电压,v db 为反馈整流管压降,I b 为反馈电流.采用的是同步整流的方式,在计算总输出功率时可设v b 、v db 为0,这时输出功率p o =(3.3+1)×4.5=19.35W.图5给出了反激开关电源的初级电流波形[7].从图中看出,在t 0导通期间有一斜坡电流,其上升斜率图受直流输入电压和初级电感L p 控制,最终达到峰值电流i p ;在t 1关断期间初级无电流流过,在I =i p 处出现峰值磁通,t 0与t 1的比例依赖于输出负载和输入电压初级平均电流I av .后者计算公式为[8]I av =p o /ηV m in .(2)图5 反激开关电源的初级电流波形图设计要求效率≥85%,所需总输出功率p o ,已经由(1)式计算出,最小直流输入电压V m in 为36V,初级平均电流可按(2)式算出:I av =19.350.85×36=0.64A.通过平均输入电流,初级峰值电流I P 可由下式算出:I P =2I av /D m .(3)为了使反激变压器有足够的恢复时间防止磁饱和,最大占空比D m 应小于50%,最大占空比为0.49,由此计算出初级峰值电流i p =2.56A.变压器的初级电感L p 的计算公式如(4)式,计算时可以按变压器的最低工作频率、最低直流输入电压和最大负载的情况计算出L p [9]:L p =(V m in T )2/2.5Tp o .(4)频率为300kHz,最低直流电压为36V,最大负载为4.5A,由此可以计算出初级电感L p =89μH .反激电源的工作模式是单向激励,为防止磁饱和,磁芯应加气隙,气隙由下式计算:l g =(0.4πL p I 2p /A e △B 2m )×109(mm )(5)7其中L p 单位为H,I p 单位为A,A e 为磁芯有效截面积,单位为mm.△B m 为有效磁通密度,单位为mT .由(5)式可计算出l g =1900mm.初级匝数计算公式为N p =ΔB m l g /0.4πI P .(6)由(6)式可以看出,为防止变压器饱和,ΔB m应小于300mT,l g 由(5)式计算出,为1900mm.I p 由(3)式计算出为,2.56A,代入(6)式计算得N p =15匝.初级N p 和次级N s 匝比的关系公式为N s =N p /(V m inV o +V D ×D m1-D m).(7)式中的V o 是次级输出电压,为3.3V,V D 是次级输出整流管的正向压降,为1V.初级的匝数N p 已由(6)式计算出,为15匝,由此可计算出次级的匝数N S =1.7匝,这里N s 取整数为2匝;辅助电源选用10V,辅助绕组的匝数N B 可依下式算出:N B =N s V /(V 0+V D ).(8)由(8)式算出结果为4.6匝,这里取整数5匝.变压器磁芯的选择:由初级电感L p 和初级匝数N P 可以计算出带气隙磁芯的有效电感系数A lg 为A lg =1000L P /N 2p .(9)变压器磁芯的选择可根据(9)式计算出的A lg 值从生产厂家的标准磁芯中选取,选择A lg 最接近的磁芯,通过研磨中间磁芯得到所需的A lg 值[9].也可以由有效截面积A e 计算出最大磁通密度B m ,作为磁芯选择依据[5]:B m =N p I p A ig /100A e .(10)(10)式中的B m 应在200mT ~300mT 之间,低于200mT 磁芯未被充分利用.如果选用铁氧体材料的磁芯,则可能发生磁饱和.在选择磁芯时也可由B m (例如取250mT ),计算出所需磁芯的最小A e ,根据最小有效截面积来选择合适的磁芯.A e 的计算公式为[10]A e =N p I p A ig /100B m .(11)导线尺寸根据峰值工作电流计算结果选择,直径为1m il 的金属丝其面积用圆密耳数来表示,单位为c .m ,在选择导线时,电流密度在200c .m /A ~500c .m /A 之间.初级所需总圆密耳数可以由(12)式计算出[11]:500I m s (f )=500I p3T on T.(12)次级所需总圆密耳数可由(13)式计算出:I m s (s )=I p (N P /N S )3T R T.(13)导线选择应充分考虑电源工作环境、峰值工作电压、绝缘电阻等要求,使绕组充满整个磁芯骨架,如果计算值低于200c m ,需增加绕组层数或选择大一个规格的磁芯.若大于500c m ,则相反.在选择初级绕组导线规格时,应充分注意趋肤效应的影响,此时选择大规格的导线,没有明显效果,可用多股导线并绕来解决这一问题[12].图6 采用光耦和电压基准进行反馈控制的电路图 反馈回路的设计:UC2843是一种高性能电流型控制器件,是专为脱线式直流变换电路设计.它集成了振荡器,温度补偿的高增益误差放大器,电流检测比较器,图腾柱输出、输入和基准8欠压锁定电路及P WM锁存器电路[13].该芯片的主要性能是:可调整振荡器的放电电流产生精确的占空比;最高开关频率可达500kHz;带锁定的P WM可以实现逐个脉冲电流限制;具有内部可调整参考电源,可以进行欠压锁定;图腾柱输出电路能够提供1A电流输出,并直接对MOS2 FET进行驱动;启动电流和工作电流低,电流小于1mA,正常工作电流为15mA.用UC2843实现常规的反馈控制方法是在UC2843的脚1、2之间加RC网络,如图6所示.把光耦的集电极直接连到UC3842的脚1作为输出的电压反馈,脚2直接接地.T L431内部有一个高增益误差放大器,它与高压侧隔离,因此反馈信号经T L431内的放大器和光耦后直接控制UC3842内部误差放大器的输出端(脚1),其控制精度并不会降低.该电路通过输出端采样,然后通过光电隔离反馈到UC2843的脚1,略过UC2843内部放大器,使电源动态响应更快,同时利用T L431内部高增益误差放大器,保证了高控制精度.这种拓扑电路结构简单、外接元件较少,且在电压采样电路中采用了三端可调电压基准,使输出电压在负载发生较大的变化时,输出电压基本没有变化.实验测试证明:该电路具有很好的动态效应和良好的稳压效果[14].3 调试及性能测试分析1)测试得到的负载调整率参数如表3所示.当输入电压不变时,输出电压随负载变化的百分比就是负载调整率.2)电压调整率参数:测试得到的电压调整率参数如表4所示.当负载不变时,输出电压随着输入电压变化的百分比就是电压调整率.3)测试得到的效率参数如表5所示.效率为输出功率与输入功率的百分比.表3 负载调整率参数输入电压输出电流输出电压电压调整率48V0A3.34V48V2.5A3.32V48V3.5A3.31V48V4.5A3.30V1.2%表4 电压调整率参数输入电压输出电流输出电压负载调整率36V4.5A3.31V48V4.5A3.32V56V4.5A3.34V75V4.5A3.35V0.1%表5 效率参数输入电压输入电流输出电压输出电流效率36V0.5A3.31V4.5A82.75%45V0.39A3.30V4.5A83.12%52V0.34A3.329V4.5A84.0%75V0.233A3.31V4.5A85.1%94 结语从测试的输出特性中可以看出,反激开关电源具有以下特点:1)有很好的负载调整率,其范围可以保持在±1%内;2)可达到±1%的稳压精度,而其他整流方式很难做到;3)电压调整率为±0.5%,可实现36V到78V宽电压出入的转化;4)有较快的响应速度;5)具有较小的纹波噪声,可让后级设备工作更加稳定可靠.[参考文献][1]沙占友.新型单片开关电源设计与应用技术[M].北京:电子工业出版社,2004:12.[2]赵负图.电源集成电路手册[M].北京:化学工业出版社,2004:136.[3]程红丽.开关电容boost-buck功率因数校正组合开关变换器[J].微电子学,2001(6):38-40.[4]王婷婷,谢运祥.一种带隔离的单相三电平功率因数校正电路[J].电力电子技术,2004(3):8-9.[5]刘胜利.现代高频开关电源实用技术[M].北京:电子工业出版社,2004:23,153.[6]陈伟,马金平,杜志江.基于DSP的P WM型开关电源的设计[J].微计算机信息,2006(9):20-22.[7]艾红,王捷,李正熙.集散控制系统中阀门监视以及局部开关综合应用[J].微计算机信息,2006(8):5-6. [8]谢万新,贾少锐,李丽宏.基于DSP的高精度开关电源的实现[J].微计算机信息,2006(6):56-60.[9]张占松,蔡宣三.开关电源的原理与设计[M].北京:电子工业出版社,1998:125.[10]姜桂宾,裴云庆,刘海涛.一种新型隔离变压器的Boost变换器[J].电力电子技术,2002(8):38-40. [11]李建国,刘文华,宋强.基于变压器隔离链式逆变器的D-ST AT C O M及其控制[J].清华大学学报(自然科学版),2005(2):3-4.[12]张盛旺,林风.电力系统微机保护装置的抗干扰措施[M].北京:电力自动化设备出版社,2005:86.[13]张方华,严仰光.带隔离变压器的DC/DC变换器零电流转换方案[J].中国电机工程学报,2003(6):5-6. [14]S m ith K M.A ne w P WM contr oller with one cycle re2s ponse[J].I EEE Transacti ons on Power Electr onics, 1999(8):10-16.D esi gn of fly-back synchronous recti f i ca ti on DC-DC convertorDENG Yu,L IAO Chang-r ong,ZHOU Zhao-fu(Schoo l of El ectr oni c and El ectri ca l Engi nee ri ng,Chongqi ng Uni ve rsity of Arts and Sci ence s,Y ongchuan Chongqi ng402160,Chi na) Abstract:Taking C MOS chi p of UC2843as the core,a ne w15W s witch stabilized voltage supp ly has been devised,single-ter m inal,fly-back,wide input range,one-way fixed voltage out put.It can effectively reduce the power l osses and i m p r ove the adjustability.I n the circuit,a ne w technique of weak cushi on cir2 cuit has been adop ted,different fr om RC cushi on circuit;it is co mbined with current mode P WM contr ol, coup ling induct or in the fly-back converter coup led with S MV capacit or,and f or med LC res onant circuit;it can efficiently accomp lish the turn-off sensibility l oaded transient cushi on,and li m it the di ode’s reverse recovery bad features.The fact shows:the technique could reach the design require ment.Key words:fly-back s witch power supp ly;synchr onous rectificati on;current-mode;P WM(责任编辑 吴 强) 01。

一种反激同步整流DC-DC变换器设计引言:低压大电流DC-DC模块电源一直占模块电源市场需求的一半左右,对其相关技术的研究有着重要的应用价值。

模块电源的高效率是各厂家产品的亮点,也是业界追逐的重要目标之一。

同步整流可有效减少整流损耗,与适当的电路拓扑结合,可得到低成本的高效率变换器。

本文针对36V-75V输入,3.3V/15A输出的二次电源模块,在分析同步整流技术的基础上,根据同步整流的特点,选择出适合于自驱动同步整流的反激电路拓扑,进行了详细的电路分析和试验。

反激同步整流基本的反激电路结构如图1。

其工作原理:主MOSFET Q1导通时,进行电能储存,这时可把变压器看成一个电感,原边绕组电流Ip上升斜率由dIp/dt=Vs/Lp决定,磁芯不饱和,则Ip 线性增加;磁芯内的磁感应强度将从Br增加到工作峰值Bm;Q1关断时,原边电流将降到零,副边整流管开通,感生电流将出现在副边;按功率恒定原则,副边安匝值与原边安匝值相等。

在稳态时,开关导通期间,变压器内磁通增量△Φ应等于反激期间内的磁通变化量,即:△Φ=VsTon / Np=Vs'Toff / Ns从此式可见,如果磁通增量相等的工作点稳定建立时,变压器原边绕组每匝的伏-秒值必然等于副边每匝绕组的伏-秒值。

反激变换器的拓扑实际就是一个BUCK-BOOST组合的变换器拓扑的应用,而且如果副边采用同步整流,电路总是工作于CCM的模式下,其电压增益M=Vo/Vs=K·D/(1-D)(K为原副边匝数比)用PMOSFET和MOSFET替代图1中的萧特基二极管,可以实现同步整流的4种电路结构如图2和图3反激电路的开关电压波形见图4,是标准的矩形波,非常适合同步整流驱动。

设计的关键点在于同步整流管的位置与驱动电路的结构配合、波形的整形限幅和死区控制。

反激同步整流驱动电路选择同步整流管的驱动方式有三种:第一种是外加驱动控制电路,优点是其驱动波形的质量高,调试方便。

反激同步整流技术解密同步整流同步整流(SR)是采用通态电阻极低的功率MOSFET取代整流二极管以降低损耗的一项新技术。

它能显著提升转换效率,并可利用其二次侧的优势改善电源指标,符合开关电源小型化、高能效、智能化的发展趋势。

随着六级能效的实施及快速充电技术的普及,同步整流在反激变换器中被电源工程师们广泛应用。

然而,同步整流如何分类及选型?其控制算法是如何解决振铃误开通等技术难题?系统应用时是否需要外部并联二极管及RC吸收……芯朋微技术团队分享原创观点,为您一一解答!同步整流分类从拓扑架构角度,同步整流可分为High side和Low side两大类。

High side特点:由于SR驱动电流大,SR参考地与输出地分开,EMC较好;高压自供电影响轻载转换效率;难以监控输出电压。

Low side特点:SR参考GND与输出共地,EMC稍差;输出电压直接供电,转换效率高;监控输出电压,易改善电源指标。

从控制策略角度,同步整流可分为DCM模式和CCM模式,而CCM模式又以预测关断和快速关断为主导。

DCM模式优点:算法简单可靠,外围精简。

缺点:控制算法与MOSFET通态电阻相关;SR须与原边芯片配合,仅能工作在不连续导电模式。

CCM模式--预测关断由SR开关波形扑捉Vg/n、Vo、T1信息,根据负秒平衡原理,估算SR关断点:优点:控制算法与MOSFET通态电阻无关,应用灵活;SR深度导通,转换效率高。

缺点:需采用电阻及积分电容提取相关信息,外围复杂、误差大;伏秒不平衡工况下(模式切换)有技术风险。

CCM模式--快速关断优点:算法简单可靠,外围精简。

缺点:控制算法与MOSFET通态电阻相关;SR在t1~t2区间非深度导通,转换效率有所降低。

同步整流关键技术以DCM同步整流技术为例,分别讨论同步整流控制算法的五大难题:1.由于振铃可能会产生负电压,如何避免振铃误开通造成直通炸机?2.关断阀值是固定不变的吗?如何自适应负载量和Rds(on)的温度特性?3.SR如何做好配角,避免损坏?4.SR关断点会引起反射电压突变,如何避免影响PSR采样?5.由于二极管整流与SR整流的温度特性完全相反,如何改善电压调整率?避免振铃误开通为了避免振铃引起的负电压(<-400mV)导致SR开通而引起与原边开关管直通现象,SR开通须附加条件,基于以下考虑:•单个振铃面积远远小于矩形波面积•振铃是以输出电压为中心正弦振荡,最高振幅在2*Vo附近自适应关断阈值SR须在去磁时间T2内关断:关断点过于提前轻则降低转换效率,重则影响PSR采样;关断点滞后轻则引起电流倒灌,重则可能导致直通。

PSR 反激开关电源同步整流问题解析

本文将详细解析PSR 反激开关电源同步整流是怎样实现的,希望对大家有所帮助。

大家都知道同步整流相比功率二极管整流损耗小,效率高,相同功率下电源尺寸可以更小。

同步整流的驱动方式有电压型驱动和电流型驱动两种。

按照SR 门级驱动电压的来源,又分为自驱动和外驱动。

这里要介绍的是在充电器领域内常见的电压型其驱动的同步整流,知识点包含以下几个小节,结合芯片内部结构力求全面讲细讲清楚以及设计过程中遇到的一些坑,不过还不知道何为PSR 架构的童鞋可以先自行了解一下,本章先不展开来讲了。

知识点:

1.同步整流MOS 什幺时候开通?什幺时候该关断?

2.整流芯片是怎幺辨别原边导通的波形和RING 的?它的逻辑是怎样?靠

电路是怎幺实现的?

3.除了同步整流功能外,它还可以用来监控次级侧电压,犹如SSR 里面的TL341,可以使其动态响应远远优于普通的PSR 架构

一. SR 何时开通,何时关断?

(附上BCD 芯片的线路图)

图1

图2

图1 中次级侧的APR3415 是本章的主角了,图2 是其内部方框图,可以看。

由于传统开关电源存在对电网造成谐波污染以及工作效率低等问题,因此目前国内外各类开关电源研究机构正努力寻求运用各种高新技术改善电源性能[1]。

其中,在开关电源设计中通过功率因数校正PFC(Power Factor Correction)技术降低电磁污染及利用同步整流技术提高效率的研发途径尤其受到重视。

参考文献[2-3]专题研讨了有源功率因数校正(APFC)技术;参考文献[4]综述了单相并联式技术的最新发展;参考文献[5-6]分别优化设计了带负载电流反馈、并联式PFC

芯片的AC/DC变换器和升压式PFC变换器,但所设计的电源效率及功率因数分别在85%和90%以下,其性能还有待进一步提高。

本文设计并制作了一种高效低电磁污染的开关电源样机。

测试结果表明,该电源具有优良的动态性能、较高的功率因数和工作效率,且控制简单,故具有一定的实际应用价值。

1 开关电源设计方案

开关电源的结构如图1所示,它主要由220V交流电压整流及滤波电路、功率因数校正电路、DC/DC变换器三大部分组成。

220V交流电经整流供给功率因数校正电路,采用Boost型PFC来提高电源的输入功率因数,同时降低了谐波电流,从而减小了谐波污染。

PFC的输出为一直流电压UC,通过DC/DC变换可将该电压变换成所要求的两输出直流电压

Uo1(12V)和Uo2(24V)。

从图中可以看出,本电源系统设计的关键是在整流滤波器和DC/DC变换器之间加入了功率因数校正电路,使输入电流受输入电压严格控制,以实现更高的功率因数。

同时设计中还采用同步整流技术以减少整流损耗,提高DC/DC变换效率。

选用反激式准谐振DC/DC变换器,既能增强对输入电压变化的适应能力,又可以降低工作损耗。

为保证开关电源的性能,电源实际制作时还附加了一些电路:(1)保护电路。

防止负载本身的过压、过流或短路;(2)软启动控制电路。

它能保证电源稳定、可

靠且有序地工作,防止启动时电压电流过冲;(3)浪涌吸收电路。

防止因浪涌电压电流而引起输出纹波峰-峰值过高及高频辐射和高次谐波的产生。

2 开关电源主要器件选择

2.1 APFC芯片及控制方案

电源中功率因数校正电路以Infineon(英飞凌)公司生产的TDA4863芯片为核心,电路如图2所示。

开关管VT1选用增强型MOSFET。

具体控制方案为:从负载侧A点反馈取样,引入双闭环电压串联负反馈,以稳定DC/DC变换器的输入电压和整个系统的输出电压。

2.2 准谐振DC/DC变换器

DC/DC变换器的类型有多种[7],为了保证用电安全,本设计方案选为隔离式。

隔离式DC/DC变换形式又可进一步细分为正激式、反激式、半桥式、全桥式和推挽式等。

其中,半桥式、全桥式和推挽式通常用于大功率输出场合,其激励电路复杂,实现起来较困难;而正激式和反激式电路则简单易行,但由于反激式比正激式更适应输入电压有变化的情况,且本电源系统中PFC输出电压会发生较大的变化,故本设计中的UC/UO变换采用反激方式,有利于确保输出电压稳定不变。

本设计采用ONSMEI(安森美)准谐振型PWM驱动芯片NCP1207,它始终保持在MOSFET漏极电压最低时开通,改善了开通方式,减小了开通损耗。

图3是利用NCP1207芯片设计的DC/DC反激式变换器电路,其工作原理为:PFC输出直流电压UO,一路直接接变压器初级线圈L1,另一路经电阻R3接到NCP1207高压端8脚,使电路起振,形成软启动电路;NCP1207的5脚输出驱动脉冲开通开关管VT,L1存储能量,当驱动关闭时,线圈L2和L3释放能量,次级

经整流滤波后供电给负载,辅助线圈释放能量,一部分经整流滤波供电给VCC,形成自举电路,另一部分经电阻R1和R2分压后送到NCP1207的1脚,来判断VT软开通时刻;光耦P1反馈来自输出电压的信号,经电阻R7和电容C2组成积分电路滤波后送入NCP1207的2脚,以调节输出电压的稳定,此为电压反馈环节。

电阻R6取样主电流信号,经串联电阻R5和电容C4组成积分电路滤波后送入NCP1207的3脚,此为电流反馈环节。

2.3 同步整流管

电源系统采用电流驱动同步整流技术[8],基本思路是通过使用低通态电阻的MOSFET代替DC/DC变换器输出侧的整流二极管工作,以最大限度地降低整流损耗,即通过检测流过自身的电流来获得MOSFET驱动信号,VT1在流过正向电流时导通,而当流过自身的电流为零时关断,使反相电流不能流过VT1,故MOSFET 与整流二极管一样只能单向导通。

选择同步整流管主要是考虑管子的通态电流要大,通态电阻小,反向耐压足够大(应按24V时变压器次级变换反向电压计算),且寄生二极管反向恢复时间要短。

经对实际电路的分析计算,选用ONSEMI公司生产的MTY100N10E的MOSFET 管,其耐压100V,通态电流为100A,通态电阻为11MΩ,反向恢复时间为145ns,开通延迟时间和关断延迟时间分别为48ns和186ns,能满足系统工作要求。

3 降耗及降电磁污染的手段

3.1 降耗措施

(1)利用TDA4863芯片优越性能

TDA4863的性能特点是:当输入电压较高时,片内APFC电路从电网中吸取较多的功率;反之,当输入电压较低时则吸收较少的功率,这就抑制了产生谐波

电流,使功率因数接近单位功率因数;片内还包含有源滤波电路,能滤除因输出电压脉动而产生的谐波电流;芯片的微电流工作条件也降低了元器件的损耗。

(2)电压电流双闭环反馈

因整机系统形成双闭环系统,DC/DC变换器输出稳定电压时既增大了输入电阻又减小输出电阻,达到了闭环控制的目的。

变换器在较大功率时呈现同步整流方式,较小功率时开关管、整流管均为零电压开通,同步整流或零电压开通都极大地降低了管耗。

3.2 降低电磁污染措施

(1)交流侧设置电磁干扰(EMI)滤波器

设置EMI滤波器的目的是抑制电源线上传导的高频干扰,同时防止电源装置产生的谐波污染电网。

(2)直流侧安装滤波电容器

在整流桥的两端并联了四只滤波电容器,可削弱整流部分对系统工作的影响。

(3)优化元器件布局减小连线距离

在一次整流回路中将二极管与变压器接近,而在二次整流回路中将二极管与变压器和输出电容都设置得比较靠近。

(4)合理接地

一方面为降低接地阻抗、消除分布电容的影响,安装时将需要接地部分就近接到该端;另一方面分别将低频电路、高频电路和功率电路的公共端单独连接后,再接到参考地端。

4 样机测试结果分析

4.1 整流桥和开关管测试波形

采用泰克(Tektronix)示波器TDS5034B对实验电路进行测试,图4是后级DC/DC变换器负载为12V/1.53A及24V/1.70A时的波形。

其中,udr和ud分别为开关管VT1驱动电压及其漏极电压,u5为TDA4863的5脚电压,即电感零电流检测电压,ui为整流桥正弦半波输出电压。

由图可知,ud幅值因为钳位而基本不变,呈高频矩形波;u5的包络线显现出电感平均电流波形接近于正弦波形。

当ui为谷点时振荡频率f0明显降低,因此时电流基准信号也处于低谷,且输出功率一定时很小的峰值电流无法使u5升高;在ui峰值附近f0也较低,因为电流基准信号亦处于峰值附近,电感电流峰值和输出功率都较大,但因输出平均功率一定,故f0降低。

4.2 不同输入交流电压时的开关管电压波形

图5是负载为12V/1.1A、24V/3.2A时,不同的ui下实测的开关管VT1漏极电压ud的波形。

由图可知,当ui在90V~150V低压段时,ud为252V,并保持不变;当ui在210V~260V高压段时,ud一直保持382V不变。

由此说明,电源系统实现了输出电压跟随输入交流电压变化的目标。

4.3 输出纹波电压波形

图6为APFC的输出高频和低频纹波电压。

由图可知,高频纹波电压约为3V 左右,低频纹波频率为100Hz时,波动电压约为10V。

因后级为反激式DC/DC变换器,故对输出电压无影响。

4.4 开关电源主要项目测试数据

不同负载和输入交流电压下测试的实验数据如表1所示,表中,Ui、Ii;UO、IO;Pi、PO分别表示整个电源系统的交流输入电压、输入电流;输出电压、输出电流;输入功率、输出功率。

样机功率因数cosΦ是采用WT3000型高精度功率分析仪测试得到。

具体测试情况是:电源系统未启动时,cosΦ只有0.625左右,但当系统工作后,cosΦ逐渐升高并达到0.952以上,峰值点可达0.989,可见电源系统对功率因数的提升是明显的。

本文所设计的反激式开关电源与普通开关电源相比,具有更低的功耗和电磁污染,而且对样机实测的功率因素cosΦ高于0.95;在输出端电压分别为12V和24V时,对应系统输出纹波电压实测约为104mV和185mV;THD值低至3.75%以下,符合EMI国家标准,整个电源系统的效率范围为85.8%≤η≤87.9%。

因此,所设计的开关电源具有较高的实际应用价值,可以将其应用于各种中小功率的电子设备中。