DDR电源芯片文档

- 格式:doc

- 大小:478.50 KB

- 文档页数:11

深入研究DDR电源作者:飞思卡尔公司Norman KW Chan(营销经理)和WS Wong(系统工程师) 时间:2008-04-18 来源:电子产品世界浏览评论DDR存储器的发展历程由于几乎在所有要求快速处理大量数据(可能是计算机、服务器或游戏系统)的应用中都要求具有RAM(随机存储器),因而DDR存储器也变得日益重要,其应用也更加广泛。

自问世以来,RAM就已经变得至关重要,主要因为它是一种能够保存易失性信息的存储器,并且可以以一种更快速、更直接的方式存取信息。

当在数据计算的世界里谈及系统速度和效率时,这一点显得尤为重要。

DDR SDRAM(双数据速率同步动态随机存储器),其可以通过在时钟周期的上升和下降沿上分别提取数据而使数据率加倍,现在看来它正发展成为最先进的RAM芯片集。

这与以往的SDR SDRAM大不相同,因为后者仅能在时钟周期的一个边沿上提取数据。

从图1可以看出,DRAM正在向着速度和数据传输率都不断提高的方向发展。

近些年来,CPU时钟频率经历了指数增长,从而为RAM存储器的时钟频率增长提供了动力。

在1997年,SD RAM在市场亮相,它可以取代DRAM和SRAM两种存储器并提供更快的时钟速率。

这主要源于SDRAM具有更简捷的通信协议;所有指令、地址和数据都由一个单独的时钟信号控制并且工作在突发模式,可以在66MHz的时钟频率下突发一系列数据字。

在1998年,SD RAM频率已经增长到100MHz 的突发脉冲速率。

在1999年,英特尔和AMD间的企业竞争升级,在CPU时钟速度方面也不例外。

处理器行业的蓬勃发展进一步加大了CPU时钟速度与其它系统组件间的差距。

在此期间,尽管存储器总线速度已经全力达到了133MHz,但却仍然远远落后于CPU所能完成的速度,因此,总的来说,这也成为提高整体应用速度的瓶颈。

为了解决这个问题,DDR RAM(双数据速率传输)的设计应运而生。

DDR RAM允许分别在时钟的上升沿和下降沿上提取数据,从而加倍了时钟的有效传输速率。

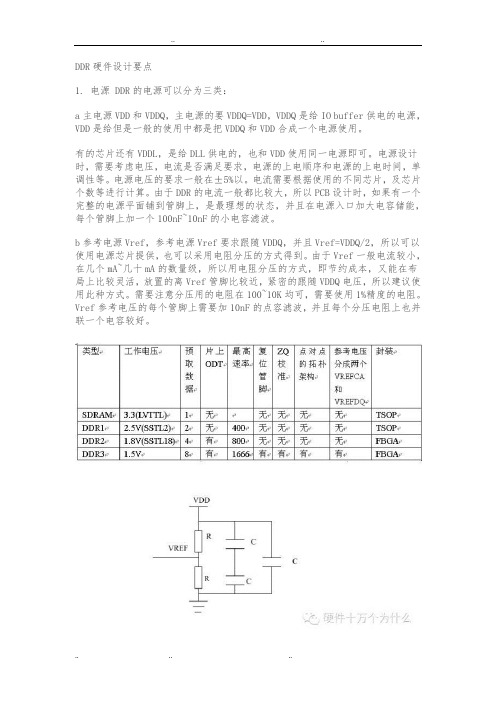

DDR硬件设计要点1. 电源 DDR的电源可以分为三类:a主电源VDD和VDDQ,主电源的要VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给但是一般的使用中都是把VDDQ和VDD合成一个电源使用。

有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。

电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以。

电流需要根据使用的不同芯片,及芯片个数等进行计算。

由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波。

b参考电源Vref,参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。

由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。

需要注意分压用的电阻在100~10K均可,需要使用1%精度的电阻。

Vref参考电压的每个管脚上需要加10nF的点容滤波,并且每个分压电阻上也并联一个电容较好。

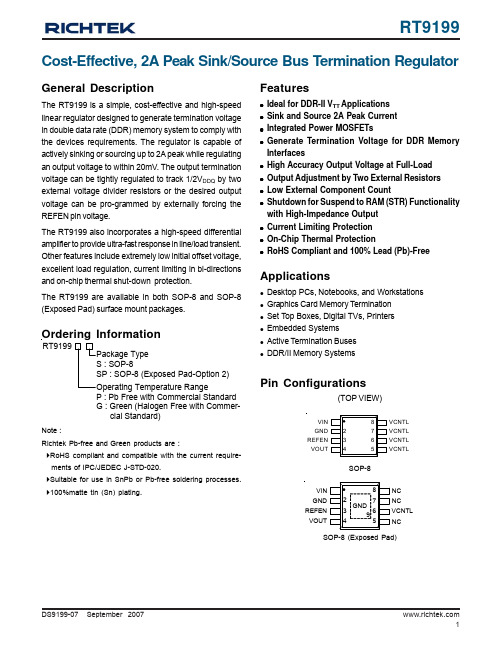

C、用于匹配的电压VTT(Tracking Termination Voltage)VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。

如果使用VTT,则VTT的电流要比较大的,所以需要走线使用铜皮铺过去。

并且VTT要求电源即可以吸电流,又可以灌电流才可以。

一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求。

而且,每个拉到VTT的电阻旁一般放一个10Nf~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

目录1存储器 (2)1.1存储器分类 (2)1.2RAM(Randm Access Memory随机存取存储器) (2)1.3SRAM (Static RAM静态RAM) (3)1.4DRAM(Dynamic RAM动态RAM) (3)1.5SDRAM(Synchronous Dynamic Random Access Memory同步动态随机存储器) (3)1.6DDR SDRAM(Double Data Rate SDRAM双倍速率同步动态随机存储器) (3)1.7RDRAM (3)2SDRAM 内存模组 (4)2.1物理Bank (4)2.2芯片位宽 (5)3SDRAM内部结构 (6)3.1逻辑 Bank (6)3.2内存容量 (8)3.3DIMM设计 (8)4引脚定义 (9)5基本操作与时序 (11)5.1芯片初始化 (11)5.2行选址 (12)5.3列选址与读写命令 (13)5.4读操作 (14)5.5写操作 (16)5.6突发长 (17)5.7预充电 (19)5.8刷新 (21)5.9数据掩码 (22)5.10形象的例子 (23)6DDR SDRAM (26)6.1DDR 基本原理 (26)6.2DDR SDRAM 与 SDRAM 的不同 (28)6.3差分时钟 (29)6.4数据选取脉冲(DQS) (29)6.5写入延迟 (32)6.6突发长度与写入掩码 (33)6.7延迟锁定回路(DLL) (34)DDR系统学习资料1存储器存储器是计算机系统中的记忆设备,用来存放程序和数据,是计算机系统中不可或缺的组成部分。

计算机中的全部信息,包括输入的原始数据、计算机程序、中间运行结果和最终运行结果都保存在存储器中。

1.1存储器分类按读写功能可分为ROM和RAM1.2RAM(Randm Access Memory随机存取存储器)主要特点:(1) 随机存取当存储器中的消息被读取或写入时,所需要的时间与这段信息所在的位置无关。

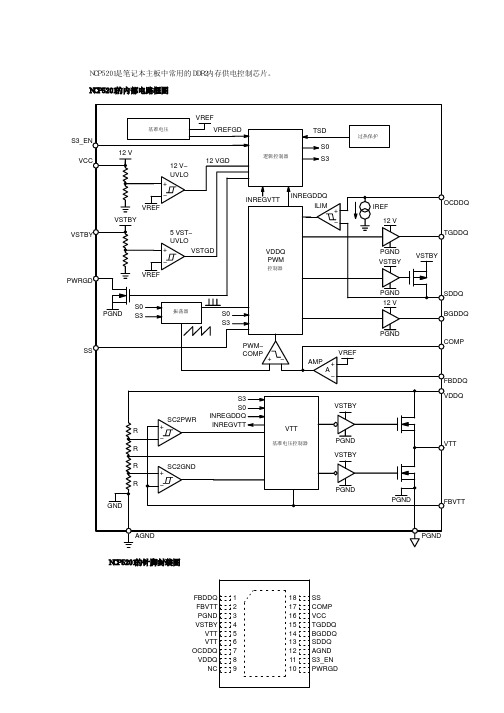

123456789181716151413121110FBDDQ FBVTT PGND VSTBY VTT VTT OCDDQ VDDQ NC SS COMP VCC TGDDQ BGDDQ SDDQ AGND S3_EN PWRGD

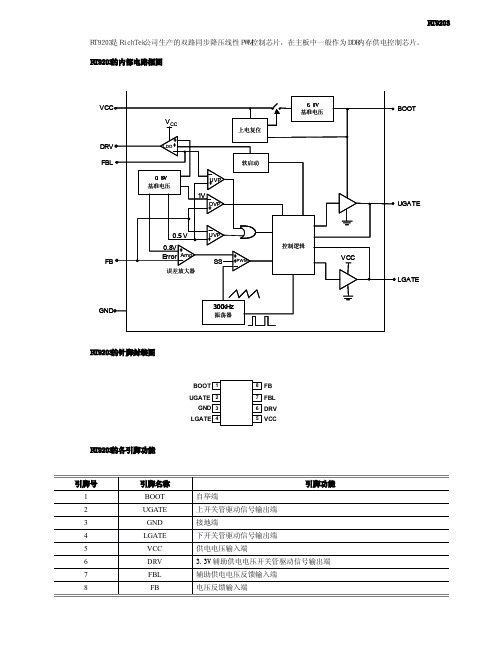

NCP5201是笔记本主板中常用的DDR2内存供电控制芯片。

NCP5201的内部电路框图

NCP5201的针脚封装图

NCP5201的各引脚功能

引脚号引脚名称引脚功能1FBDDQ VDDQ反馈输入端

2FBVTT VTT电压检测输入端

3PGND接地端

4VSTBY5V待机电源输入端

5,6VTT VTT供电电压输出端

7OCDDQ VDDQ过流检测信号输入端

8VDDQ VDDQ反馈输入端

9NC空脚

10PWRGD POWER GOOD信号输出端

11S3-EN S3模式控制信号输入端,正常工作时为低电平12AGND模拟电路接地端

13SDDQ电流检测输入端

14BGDDQ VDDQ下开关管驱动信号输出端

15TGDDQ VDDQ上开关管驱动信号输出端

16VCC12V供电电压输入端

17COMP VDDQ误差放大器输出端

18SS软驱动控制端

NCP5201的典型应用电路图

L1 1.0 m H。

s478芯片参数佳能SG-E1 SG-S478:1、电源:SG-E1基于DDR3,VDD为1.8V和VDDQ为1.5V,使用高压VTT技术,芯片支持多范围电压,使芯片在不同的系统电源中运行更加稳定。

SG-S478的电源支持1.2V~1.8V。

2、容量:SG-E1支持最大8GB容量,支持高速标准:DDR3L-1066/1333/1600;SG-S478支持4GB容量,支持高速标准:DDR3L-800/1066/1333/1600。

3、封装:SG-E1封装为FBGA,SG-S478封装为FBGA-156。

4、热释电:SG-E1支持热释电技术,有效减少整体系统体积,SG-S478也支持热释电技术,有效减小系统功耗。

5、使用寿命:SG-E1表示操作温度范围为-40℃~+95℃,SG-S478表示操作温度范围为-40℃~+85℃。

6、结构布局:SG-E1芯片结构比较简单,使用8个64M×8bit DDR3 SDRAM;SG-S478芯片采用14层高密布线,使用8个64M×8bit DDR3 SDRAM,支持双通道。

7、电压:SG-E1的VDD为1.8V和VDDQ为1.5V,SG-S478的电源支持1.2V~1.8V,支持低电压技术,使得芯片可以在低电压环境下运行。

8、抗干扰:SG-E1芯片提供抗干扰设计,加强数据位纠错功能,芯片和元件之间的衍生装置能够有效地抑制芯片的抗干扰能力,确保芯片的稳定性和可靠性;SG-S478芯片也具备良好的抗干扰性能,能够有效地确保系统的可靠性。

9、功耗:SG-E1芯片提供低功耗技术,其功耗标准为0.384W(1.5V时)、0.192W(1.35V 时);SG-S478芯片提供低功耗技术,其功耗标准为1.168W,使得芯片在低功耗环境下仍可正常工作。

10、工作速率:SG-E1最大工作速率为1600MHz,最大隔存率为800MHz;SG-S478最大工作速率为1600MHz,最大隔存率为933MHz。

DDF的基础知识i.电源DDR的电源可以分为三类:主电源VDD和VDDQ ,主电源的要求是VDDQ=VDD , VDDQ是给10buffer供电的电源,VDD是给但是一般的使用中都是把VDDQ和VDD合成一个电源使用。

有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。

电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以内。

电流需要根据使用的不同芯片,及芯片个数等进行计算。

由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100 nF〜10 nF 的小电容滤波。

参考电源Vref,参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2 ,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。

由于Vref —般电流较小,在几个mA〜几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ 电压,所以建议使用此种方式。

需要注意分压用的电阻在100〜10K 均可,需要使用1%精度的电阻。

Vref参考电压的每个管脚上需要加10nF的点容滤波,并且每个分压电阻上也并联一个电容较好。

VTT为匹配电阻上拉到的电源,VTT=VDDQ/2 。

DDR的设计中,根据拓扑结构的不同, 有的设计使用不到VTT,如控制器带的DDR 器件比较少的情况下。

如果使用VTT,则VTT 的电流要求是比较大的,所以需要走线使用铜皮铺过去。

并且VTT 要求电源即可以吸电流,又可以灌电流才可以。

一般情况下可以使用专门为DDR 设计的产生VTT 的电源芯片来满足要求。

而且,每个拉到VTT的电阻旁一般放一个10Nf〜100nF 的电容,整个VTT电路上需要有uF 级大电容进行储能。

一般情况下,DDR 的数据线都是一驱一的拓扑结构,且DDR2 和DDR3 内部都有ODT 做匹配,所以不需要拉到VTT 做匹配即可得到较好的信号质量。

VTT其实跟VREF的电平是一样的,对DDR2来说就是0.9V,但是VREF消耗的电流很小,可以通过一个电阻网络从1.8V转出来;而VTT是端接用的,电流会比较大,能达到百毫安级,还是需要用单独的电源芯片生成。

VTT:端接电阻,Termination resister对DDR SDRAM的控制管理iMX23通过EMI控制器管理DDR,EMI控制器通过四个内部AHB/AXI总线与DDR连接。

EMI控制器包括两个部分:DDR控制器和延时补偿电路(DCC)。

EMI只支持两种扩展内存类型:1.8V的mDDR和标准2.5V DDR1。

对于iMX23的不同封装形式,其EMI支持的DRAM的容量也不同:1、128-pin LQFP只支持一片DRAM,且DRAM的最大容量为64MB;2、169-pin BGA可支持两片DRAM,每片DRAM的最大容量为128MB。

EMI使用双时钟:AHB总线时钟HCLK和DRAM源时钟EMI_CLK。

EMI 理论上可以支持512MB的地址空间(因为它有13根行地址线),但是实际上只能支持256MB的DRAM,因为IMX23上只有两个芯片使能信号:EMI_CE0N 和EMI_CE1N,每个DRAM只有一个芯片使能引脚CE#,因此只能控制两片DRAM(在BGA封装下。

在LQFP封装里只支持单片DRAM)。

延迟补偿电路的作用:从SDRAM中读数据时:EMI控制器需要与时钟信号同步的DQS选通信号来捕捉从DRAM中传输过来的数据信号,并且要尽量保证采样的DQS信号的上升沿与下降沿跟DQ数据信号窗的中间对齐,确保采样的误差最小。

但是对于DRAM,它把输出数据DQ和数据选通信号DQS同时传输给EMI控制器,即DQ与DQS的边界是对齐的,这种情况下必须采用延迟电路对DQS信号进行延迟,以使其边界对齐于DQ信号窗中间。

DQS与时钟信号是同频率的,通常延迟时间取系统时钟的25%左右。

延迟补偿电路对于读取DRAM数据的作用如下图所示:写入数据到SDRAM:在写入数据时,EMI控制器向DRAM中同步发送DQS信号,而DQS信号是与时钟信号边界对齐的,而对于DRAM,要正确的从输入的DQ数据中进行采样,要求采样的DQS信号窗的中间部分与DQ的中间部分对齐,因此在EMI 控制器端传送DQS信号时要进行延迟补偿,延迟的时间为tdqss,其值一般取±0.25 和0.2个系统时钟周期。

DDR再谈--DDR的几个要点2011-10-26 09:08:22| 分类:Memorizer | 标签:|字号大中小订阅1. 电源DDR的电源可以分为三类:a>主电源VDD和VDDQ,主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给但是一般的使用中都是把VDDQ 和VDD合成一个电源使用。

有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。

电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以内。

电流需要根据使用的不同芯片,及芯片个数等进行计算。

由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波。

b>参考电源Vref,参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。

由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。

需要注意分压用的电阻在100~10K均可,需要使用1%精度的电阻。

Vref参考电压的每个管脚上需要加10nF的点容滤波,并且每个分压电阻上也并联一个电容较好。

c>用于匹配的电压VTT(Tracking Termination Voltage)VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。

如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。

并且VTT要求电源即可以吸电流,又可以灌电流才可以。

一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求。

而且,每个拉到VTT的电阻旁一般放一个10Nf~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。

而地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T点的结构,所以常常需要使用VTT进行信号质量的匹配控制。

2. 时钟DDR的时钟为差分走线,一般使用终端并联100欧姆的匹配方式,差分走线差分对控制阻抗为100ohm,单端线50ohm。

需要注意的是,差分线也可以使用串联匹配,使用串联匹配的好处是可以控制差分信号的上升沿缓度,对EMI可能会有一定的作用。

3. 数据和DQSDQS信号相当于数据信号的参考时钟,它在走线时需要保持和CLK信号保持等长。

DQS在DDR2以下为单端信号,DDR2可作为差分信号,也可做单端,做单端时需要将DQS-接地,而DDR3为差分信号,需要走线100ohm差分线。

由于内部有ODT,所以DQS不需要终端并联100ohm电阻。

每8bit数据信号对应一组DQS信号。

DQS信号在走线时需要与同组的DQS信号保持等长,控制单端50ohm的阻抗。

在写数据时,DQ和DQS 的中间对齐,在读数据时,DQ和DQS的边沿对齐。

DQ信号多为一驱一,并且DDR2和DDR3有内部的ODT匹配,所以一般在进行串联匹配就可以了。

4. 地址和控制地址和控制信号速度没有DQ的速度快,以时钟的上升沿为依据采样,所以需要与时钟走线保持等长。

但如果使用多片DDR时,地址和控制信号为一驱多的关系,需要注意匹配方式是否适合。

5. PCB布局注意事项PCB布局时,需要把DDR颗粒尽量靠近DDR控制器放置。

每个电源管脚需要放置一个滤波电容,整个电源上需要有10uF以上大电容放在电源入口的位置上。

电源最好使用独立的层铺到管脚上去。

串联匹配的电阻最好放在源端,如果是双向信号,那么要统一放在同一端。

如果是一驱多的DDR匹配结构,VTT上拉电阻需要放在最远端,注意芯片的排布需要平衡。

下图是几种DDR的拓扑结构,首先,一驱二的情况下分为树状结构,菊花链和Fly-by结构,Fly-by是一种STUB很小的菊花链结构。

DDR2和DDR3走菊花链结构都是比较适合的。

走树状结构可以把两片芯片贴在PCB的正反两面,对贴减小分叉的长度。

一驱多的DDR拓扑结构比较复杂,需要仔细进行仿真。

6. PCB布线注意事项PCB布线时,单端走线走50ohm,差分走线走100ohm阻抗。

注意控制差分线等长±10mil以内,同组走线根据速度的要求也有不同,一般为±50mil。

控制和地址线及DQS线和时钟等长,DQ数据线和同组的DQS线等长。

注意时钟及DQS和其他的信号要分开3W以上距离。

组间信号也要拉开至少3W宽的距离。

同一组信号最好在同一层布线。

尽量减少过孔的数目。

7. EMI问题DDR由于其速度快,访问频繁,所以在许多设计中需要考虑其对外的干扰性,在设计时需要注意一下几点原理有性能指标要求的,易受干扰的电路模块和信号,如模拟信号,射频信号,时钟信号等,防止DDR对其干扰,影响指标。

DDR的电源和不要与其他易受干扰的电源模块使用同一电源,如必须使用同一电源,要注意使用电感、磁珠或电容进行滤波隔离处理。

在时钟及DQS信号线上,预留一些可以增加的串联电阻和并联电容的位置,在EMI超出标准时,在信号完整性允许的范围内增大串联电阻或对地电容,使其信号上升延变缓,减少对外的辐射。

进行屏蔽处理,使用金属外壳的屏蔽结构,屏蔽对外辐射。

注意保持地的完整性。

8. 测试方法注意示波器的探头和示波器本身的带宽能够满足测试要求。

测试点的选择要注意选到尽量靠近信号的接受端。

由于DDR信令比较复杂,因此为了能快速测试、调试和解决信号上的问题,我们希望能简单地分离读/写比特。

此时,最常用的是通过眼图分析来帮助检查DDR信号是否满足电压、定时和抖动方面的要求。

触发模式的设置有几种,首先可以利用前导宽度触发器分离读/写信号。

根据JEDEC规范,读前导的宽度为0.9到1.1个时钟周期,而写前导的宽度规定为大于0.35个时钟周期,没有上限。

第二种触发方式是利用更大的信号幅度触发方法分离读/写信号。

通常,读/写信号的信号幅度是不同的,因此我们可以通过在更大的信号幅度上触发示波器来实现两者的分离。

测试中要注意信号的幅度,时钟的频率,差分时钟的交叉点,上升沿是否单调,过冲等。

时序中最重要,最需要注意的就是建立时间和保持时间。

要为便携式设备的DDR内存选择一款合适的电源,就必须权衡性能和其他技术参数,如输入电压或输出电流之间的代价。

对于DDR2内存而言,VTT来自于电源芯片,飞思卡尔的MC34716正式合适之选。

MC34716是一款集成了N通道功率MOSFET,具有高度集成、节省空间、低成本等特点的双通道同步降压开关稳压器。

它是一款高性能负载点(PoL)电源,其第二路输出具有跟踪外部参考电压的功能。

它为双数据速率(DDR)存储器提供了全面的电源解决方案。

通道1只提供5.0A 供电电流的驱动性能,而通道2可以提供/吸收高达3.0A 的电流。

两个通道都有精密的输出调节功能,可达到很高的效率。

利用其高电流驱动性能,通道1可以用来向存储器芯片组提供VDDQ。

通道2跟踪参考电压的能力特别适用于为现代数据总线提供端电压(VTT)。

MC34716也为存储器芯片组提供了缓冲输出参考电压(VREFOUT)。

MC34716使得设计者能够灵活地实现众多控制、监视和保护功能,从而轻松实现复杂设计。

MC34716的特性包括:·集成式N通道功率MOSFET 输出电压范围:3.0V~6.0V;·精确的输出电压,其范围为0.7V~3.6V;·第2路输出跟踪1/2的外部参考电压;·1%的精确缓冲参考输出电压;·可编程开关频率范围:200kHz ~1.0MHz;·通道1的可编程软启动时序;·两个通道的过流限制和短路保护功能;·过热关断;·输出过压和欠压检测;·低有效Power Good输出信号;·低有效待机和关断输入控制M axim > 产品> 汽车电子> MAX1510, MAX17510Maxim > 产品> 电源和电池管理> MAX1510, MAX17510MAX1510, MAX17510低电压、DDR线性稳压器低成本、低电压DDR线性稳压器,可源出、吸入3A峰值电流(典型值),内置n沟道M 概述技术文档定购信息相关产品用户说明(0)所有内容状况状况:生产中。

概述MAX1510/MAX17510 DDR线性稳压器使用内部n沟道MOSFET,可以供出或吸入最高3A (典至3.6V)可以提供精确的0.5V至1.5V输出。

MAX1510/MAX17510使用独立的3.3V偏置电源为MAX1510/MAX17510具有电流和温度限制功能,以防线性稳压器损坏。

另外,MAX1510/MAX1围。

启动时,PGOOD在输出稳定2ms (典型值)之前保持低电平。

内部软启动限制了输入浪涌电MAX1510/MAX17510为需要跟踪输入基准的有源DDR终端总线供电。

MAX1510还可用于MAX1510/MAX17510采用10引脚、3mm x 3mm薄型DFN封装。

DDR内存供电电路DDR内存需要两种供电电压:2.5V的主供电压和1.25的基准供电电压(又称参考电压).2.5V供电电压用来为内存芯片提供工作电压,1.25V供电电压用来为内存总线的数据线和地址线提供上拉工作电压.DDR内存供电电路主要有下面几种形式.1\单场效应管60N03+基准电压源LM431(可以用XX431代换)+比较器LM358构成的2.5V供电电路.2\单场效应管Q110+基准电压源Q31(SC431\SOT23)构成的2.5V供电电路3\专用芯片(ISL6520\RT9214)构成的2.5V内存供电电路4\双场效应管Q71(15N03)和Q70(15N03)+比较器U42A(LM358)和U42B(LM358)构成的1.25V供电电路5\双三极管Q4(HA8050DD)\Q5(HA8550DD)+比较器构成的1.25V供电电路6\多端稳压器(RT9173或RT9173B)构成的1.25V供电电中路7\专用芯片LP2995构成的1.25V供电电路8\专用芯片ISL6537构成的混合型内存供电电路DDR2内存需要两种供电电压:1.8V的主供电电压和0.9V的基准电电压(又称参考电压),1.8V 供电电压来为内存芯片提供工作电压,0.9V供电电压用来为内存总线的数据线和地址线提供上拉工作电压.常用DDR2内存供电芯片有NCP5201\ISL6537等型号论是采用分立元件系统还是高度集成的系统级芯片(SoC),许多嵌入式消费电子系统都利用了现有系统(如PC或其它成熟的通用系统)的架构。