1.5V工作电压带隙基准电路的设计

- 格式:pdf

- 大小:82.58 KB

- 文档页数:4

哈尔滨理工大学软件学院课程设计报告指导老师董长春2013年6月28日.课程设计题目描述和要求二.课程设计报告内容2.1课程设计的计算过程2.2带隙电压基准的基本原理2.3指标的仿真验证结果2.4网表文件三.心得体会四.参考书目课程设计题目描述和要求1.1电路原理图:CDMQ MSMlO Ml IMI2^ ——I 匚13 M 匚11jir Ml Tl ----M4------1M2TC1.2 设计指标放大器:开环增益:大于 70dB相位裕量:大于 60 度 失调电压: 小于 1mV带隙基准电路:温度系数小于 10ppm/ C1.3 要求1>手工计算出每个晶体管的宽长比。

通过仿真验证设计是否正确, 是否满足 指标的要求,保证每个晶体管的正常工作状态。

2>使用Hspice 工具得到电路相关参数仿真结果,包括:幅频和相频特性(低 频增益,相位裕度,失调电压)等。

3>每个学生应该独立完成电路设计, 设计指标比较开放, 如果出现雷同按不 及格处理。

4>完成课程设计报告的同时需要提交仿真文件,包括所有仿真电路的网表, 仿真结果。

二. 课程设计报告内容由于原电路中增加了两个BJT 管,所以Vref 需要再加上一个Vbe ,导致最 后结果为M(In n) 8.6,最后Vref 大概为1.2V ,且电路具有较大的电流,可以驱动较大的负载。

2.1 课程设计的计算过程1> M8, M9 , M10, M11, M12 , M13 宽长比的计算 (W/L)8=(W/L)9=20uA为了满足调零电阻的匹配要求,必须有 Vgs13=Vgs6 ->因此还必须满足 (W/L)13=(Im8/I6)*(W/L)6 即(W/L)13/(W/L)6=(W/L)9/(W/L)7 取(W/L)13=27取(W/L)10=(W/L)11=(W/L)13=27因为偏置电路存在整反馈,环路增益经计算可得为1/(gm13*Rb),若使环路5>相关问题参考教材第六章,仿真问题请查看 HSPICE 手册。

1.5-V高阶曲率补偿CMOS带隙基准源摘要此报告中设计了一种新的低电平,低噪声,高阶曲率补偿CMOS带隙基准源。

此带隙电路用两个电阻串来减小电源电压。

此外,由高阻抗的多晶硅电阻和扩散电阻产生的热敏电阻比来提供高阶补偿。

此所设计的带隙基准电压源能在1.5V电源电压下工作(此时0℃时V th=0.9V),它的温度系数小于15.2ppm/℃,平均电源调整率为5.5mV/V。

1.简介基准电压源是许多电子元器件的主要组成,例如电源转换器,数字转化器,射频电路。

温度对带隙基准电压源的影响毫无疑问会影响它的性能。

因此低电平,低功率,低温飘带隙基准电压源在工业生产中越来越重要。

事实上,许多现有的技术都能减小基准电压源的温度系数,如Song等人提出的二次温度补偿, Rincon-Mora等人提出的分段线性曲率校正。

Audy和Lewis等人分别提出了更简单的基于热敏电阻比来加以实现的二阶和三阶曲率补偿带隙基准源。

这个方法被Leung等人进一步发展为高阶曲率补偿用于CMOS带隙基准电压源的设计。

曲率补偿CMOS带隙基准电压源利用一个负温度系数的高阻抗多晶硅电阻和一个正温度系数的扩散电阻来产生一个热敏电阻比,以此能够有效地减少此带隙基准源的温度漂移。

以上电阻都能在CMOS工艺中实现。

有过报道的最低工作电源电压为2V,这对于将来的应用还远不够低。

为了未来应用中进一步减小所要求的电源电压,这里提出一种基于以上理论的低电压曲率补偿带隙基准源。

它利用两个完全相同的电阻串来同时提供曲率补偿和电压电平摆幅。

在文章中,我们所设计的低电压带隙基准电压源将在第2章节中介绍。

影响基准电压源精确度的重要设计因素,包括如电流镜匹配,放大器的偏移电压和输出噪声。

章节3中的实验结果证实了这一结论。

章节4为最后的总结。

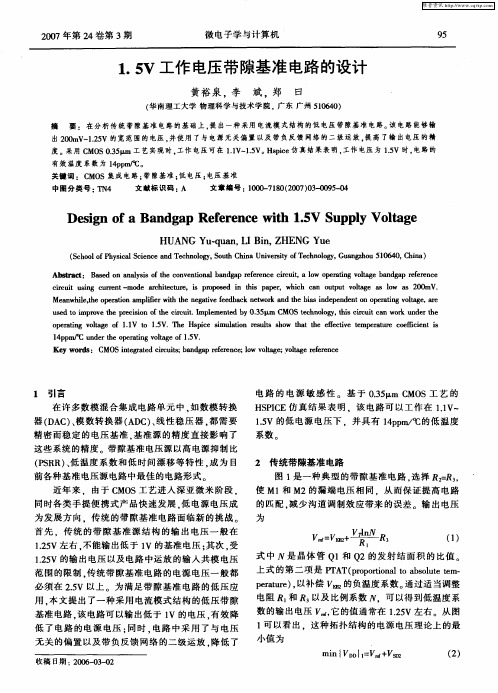

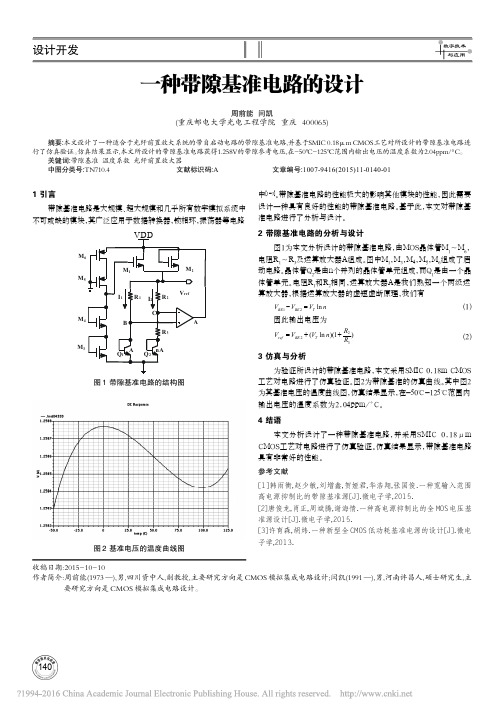

2.我们所设计的曲率补偿带隙基准源此低电压,高阶曲率补偿带隙基准源的电路结构和完整原理图分别如图1.和图2.所示。

图1.高阶曲率补偿带隙基准源的电路结构图2. 高阶曲率补偿带隙基准源的原理图在常规设计中,电源电压被误差放大器的PMOS输入级电压V GS所制约,而为了降低电源电压,应使用NMOS作为误差放大器的输入级。

帯隙基准电路设计(东南大学集成电路学院)一.基准电压源概述基准电压源(Reference Voltage)是指在模拟电路或混合信号电路中用作电压基准的具有相对较高精度和稳定度的参考电压源,它是模拟和数字电路中的核心模块之一,在DC/DC,ADC,DAC以及DRAM等集成电路设计中有广泛的应用。

它的温度稳定性以及抗噪性能影响着整个电路系统的精度和性能。

模拟电路使用基准源,是为了得到与电源无关的偏置,或是为了得到与温度无关的偏置,其性能好坏直接影响电路的性能稳定。

在CMOS技术中基准产生的设计,着重于公认的“帯隙”技术,它可以实现高电源抑制比和低温度系数,因此成为目前各种基准电压源电路中性能最佳、应用最广泛的电路。

基于CMOS的帯隙基准电路的设计可以有多种电路结构实现。

常用的包括Banba和Leung结构带薪基准电压源电路。

在综合考虑各方面性能需求后,本文采用的是Banba结构进行设计,该结构具有功耗低、温度系数小、PSRR高的特点,最后使用Candence软件进行仿真调试。

二.帯隙基准电路原理与结构1.工作原理带隙基准电压源的设计原理是根据硅材料的带隙电压与电源电压和温度无关的特性,通过将两个具有相反温度系数的电压进行线性组合来得到零温度系数的电压。

用数学方法表示可以为:2211V V V REF αα+=,且02211=∂∂+∂∂TV T V αα。

1).负温度系数的实现 根据双极性晶体管的器件特性可知,双极型晶体管的基极-发射极电压BE V 具有负温度系数。

推导如下:对于一个双极性器件,其集电极电流)/(ex p T BE S C V V I I =,其中q kT V T /=,约为0.026V ,S I 为饱和电流。

根据集电极电流公式,得到:SC T BE I I V V ln= (2.1) 为了简化分析,假设C I 保持不变,这样: TI I V I I T V T V S S T S C T BE ∂∂-∂∂=∂∂ln (2.2) 根据半导体物理知识可知:kT E bT I gm S -=+ex p 4 (2.3)其中b 为比例系数,m ≈−3/2,Eg 为硅的带隙能量,约为1.12eV 。

1.5-V高阶曲率补偿CMOS带隙基准源摘要此报告中设计了一种新的低电平,低噪声,高阶曲率补偿CMOS带隙基准源。

此带隙电路用两个电阻串来减小电源电压。

此外,由高阻抗的多晶硅电阻和扩散电阻产生的热敏电阻比来提供高阶补偿。

此所设计的带隙基准电压源能在1.5V电源电压下工作(此时0℃时V th=0.9V),它的温度系数小于15.2ppm/℃,平均电源调整率为5.5mV/V。

1.简介基准电压源是许多电子元器件的主要组成,例如电源转换器,数字转化器,射频电路。

温度对带隙基准电压源的影响毫无疑问会影响它的性能。

因此低电平,低功率,低温飘带隙基准电压源在工业生产中越来越重要。

事实上,许多现有的技术都能减小基准电压源的温度系数,如Song等人提出的二次温度补偿, Rincon-Mora等人提出的分段线性曲率校正。

Audy和Lewis等人分别提出了更简单的基于热敏电阻比来加以实现的二阶和三阶曲率补偿带隙基准源。

这个方法被Leung等人进一步发展为高阶曲率补偿用于CMOS带隙基准电压源的设计。

曲率补偿CMOS带隙基准电压源利用一个负温度系数的高阻抗多晶硅电阻和一个正温度系数的扩散电阻来产生一个热敏电阻比,以此能够有效地减少此带隙基准源的温度漂移。

以上电阻都能在CMOS工艺中实现。

有过报道的最低工作电源电压为2V,这对于将来的应用还远不够低。

为了未来应用中进一步减小所要求的电源电压,这里提出一种基于以上理论的低电压曲率补偿带隙基准源。

它利用两个完全相同的电阻串来同时提供曲率补偿和电压电平摆幅。

在文章中,我们所设计的低电压带隙基准电压源将在第2章节中介绍。

影响基准电压源精确度的重要设计因素,包括如电流镜匹配,放大器的偏移电压和输出噪声。

章节3中的实验结果证实了这一结论。

章节4为最后的总结。

2.我们所设计的曲率补偿带隙基准源此低电压,高阶曲率补偿带隙基准源的电路结构和完整原理图分别如图1.和图2.所示。

图1.高阶曲率补偿带隙基准源的电路结构图2. 高阶曲率补偿带隙基准源的原理图在常规设计中,电源电压被误差放大器的PMOS输入级电压V GS所制约,而为了降低电源电压,应使用NMOS作为误差放大器的输入级。

带隙电压基准源的设计与分析摘要介绍了基准源的发展和基本工作原理以及目前较常用的带隙基准源电路结构。

设计了一种基于Banba结构的基准源电路,重点对自启动电路及放大电路部分进行了分析,得到并分析了输出电压与温度的关系。

文中对带隙电压基准源的设计与分析,可以为电压基准源相关的设计人员提供参考。

可以为串联型稳压电路、A/D和D/A转化器提供基准电压,也是大多数传感器的稳压供电电源或激励源。

基准源广泛应用于各种模拟集成电路、数模混合信号集成电路和系统集成芯片中,其精度和稳定性直接决定整个系统的精度。

在模/数转换器(ADC)、数/模转换器(DAC)、动态存储器(DRAM)等集成电路设计中,低温度系数、高电源抑制比(PSRR)的基准源设计十分关键。

在集成电路工艺发展早期,基准源主要采用齐纳基准源实现,如图1(a)所示。

它利用了齐纳二极管被反向击穿时两端的电压。

由于半导体表面的沾污等封装原因,齐纳二极管噪声严重且不稳定。

之后人们把齐纳结移动到表面以下,支撑掩埋型齐纳基准源,噪声和稳定性有较大改观,如图1(b)所示。

其缺点:首先齐纳二极管正常工作电压在6~8 V,不能应用于低电压电路;并且高精度的齐纳二极管对工艺要求严格、造价相对较高。

1971年,Widlar首次提出带隙基准结构。

它利用VBE的正温度系数和△VBE的负温度系数特性,两者相加可得零温度系数。

相比齐纳基准源,Widlar型带隙基准源具有更低的输出电压,更小的噪声,更好的稳定性。

接下来的1973年和1974年,Kujik和Brokaw分别提出了改进带隙基准结构。

新的结构中将运算放大器用于电压钳位,提高了基准输出电压的精度。

以上经典结构奠定了带隙基准理论的基础。

文中介绍带隙基准源的基本原理及其基本结构,设计了一种基于Banba结构的带隙基准源,相对于Banba结构,增加了自启动电路模块及放大电路模块,使其可以自动进入正常工作状态并增加其稳定性。

1 带隙基准源工作原理由于带隙电压基准源能够实现高电源抑制比和低温度系数,是目前各种基准电压源电路中性能最佳的基准源电路。

带隙基准电路设计

嘿,朋友们!今天咱来聊聊带隙基准电路设计。

这玩意儿啊,就像是电路世界里的定海神针!

你想想看,在那复杂纷繁的电路海洋中,要是没有一个可靠的基准,那不就像船在大海上没了指南针,瞎转悠嘛!带隙基准电路就是那个能给其他电路指明方向、提供稳定参照的宝贝。

它就好比是一场比赛中的裁判,公正公平地给出标准,让其他电路元件能按部就班地工作。

要是没有它,那电路里还不得乱套呀!各种信号乱跑,功能都没法正常实现了。

设计带隙基准电路可不容易哦!得像个细心的工匠,一点一点地雕琢。

从选择合适的元件开始,这就跟挑食材做饭一样,得挑新鲜的、好的食材,才能做出美味的菜肴。

元件选不好,那后面可就难办咯!

然后呢,还得精心设计电路的布局,这可不是随便摆摆就行的。

就好像搭积木,得考虑怎么搭才最稳固、最合理。

每个元件的位置都有讲究,牵一发而动全身呐!

在调试的过程中,那可得有耐心。

有时候就像解谜一样,一点点地找问题,解决问题。

要是没耐心,那肯定不行呀!难道遇到点困难就打退堂鼓啦?那可不行!

而且啊,这带隙基准电路还得适应各种环境呢!就像人一样,得能经得住各种考验。

热了不行,冷了也不行,得始终保持稳定可靠。

你说它容易吗?

咱再想想,要是没有带隙基准电路,那些电子设备还能这么好用吗?手机说不定一会儿信号好,一会儿信号差;电脑可能会时不时地出故障。

哎呀,那可太糟糕了!

所以说呀,带隙基准电路设计真的太重要啦!咱可得重视起来,好好研究,把它设计得稳稳当当的。

让我们的电子世界因为它而更加精彩,更加可靠!这就是我对带隙基准电路设计的看法,你们觉得呢?。

设计1.5VCMOS高阶曲率补偿带隙基准源摘要本文提出了一种低压低噪声高阶曲率补偿CMOS带隙参考源。

为了降低基准电压,增加了两个电阻式。

此外,由高值电阻和扩散电阻提供的高阶温度补偿。

提供的带隙基准电源可以提供1.5V温度系数低于15.2ppm/℃电源调整率为5.5mV的基准电压(Vth=0.9V,0℃)。

1 介绍基准电压源是许多电子器件不可缺少的一部分,比如电源转换,数据转换和射频电路。

基准电压源对温度的依赖无疑影响了这些应用的表现。

所以,低压低温度系数的基准电压源在商业产品中变得越来越重要。

实际上,有很多技术可以减小基准电压源的温度系数,比如由Song et al提出的二次温度补偿技术及由Rincon-Mora et al发展的分段线性曲率校正技术。

基于电阻率随温度改变,Lewis et al. 和Audy分别提出了二阶和三阶曲率补偿技术。

这一思路由Leung et al扩展到高阶曲率校正并应用到CMOS基准电压源的设计中。

温度补偿CMOS带隙基准电源利用负温度系数,高值多晶硅电阻和正温度系数的扩散电阻实现电阻系数与温度相关。

从而有效地减少带隙基准电压的漂移。

以上电阻都可以用CMOS技术实现,最小的供应电压为2V,作为将来的应用来说还不够低。

为了进一步减小电源电压,本文提出了一种低压曲率补偿技术。

它通过两个相同的电阻串同时提供曲率补偿和电平转换。

在这篇文章中,在第二节提出了低压基准电压方案,这个重要的设计考虑到了一些会影响精度的因素,包括电流镜匹配,放大器的偏移电压以及输出噪音。

第三节显示了实验结果并证实了这一想法,最后,第四节提出了结论。

2 提出曲率补偿带隙基准电源电路结构和低压高阶曲率补偿基准源原理图分别如图1和图2所示。

为了降低电源电压,在传统设计中的误差放大器电压Vgs有限,我们使用了NMOS输入级放大器。

电阻串R2A、R2B和R3B使用偏移电压可以工作在高增益区的输入直流电压。

电阻的值设为R2A=R2B,R3A=R3B。

带隙基准参数设计基准源核心电路参数设计首先,考虑两个三极管发射极面积之比N的选取。

由上述公式可知:N值越大,则R2/R3的比例就越小,从而可以减小电阻的版图面积。

但是N值越大,也会导致三极管的静态电流增大。

折中选取N=8,这样版图可以采用中心对称布局,有利于减少匹配误差。

假设选取的工艺下的三极管的电流大于1uA时,V BE的输出曲线较为平滑。

从节省功耗的角度,假定流过三极管集电极的电流为1uA。

由上述公式可知,当N=8、IR3=1uA、T=300K时,计算得:考虑到R1和R2的数值数倍于R3,则电阻值太大,消耗版图面积太大。

因此,作为折中,选取R3为10K,电流值为5uA左右。

确定了以上参数后,考虑一阶补偿时R2的取值。

对上述公式在T0处求导可得:令上式为零,即进行一阶补偿,可得:化简得:代入参数,V G0=1.205V,查图可知V EB1在5uA的偏执电流下约为716mV,300K温度下V T0=26mV,r=3.2,a=1(三极管的偏置电流为PTA T),N=8,计算得:为了产生600mV的输出电压,需要调整R4的值。

由上式可以推出:在T=300K条件下代入各值,求得R4=48.5K。

考虑到各个电阻阻值偏大,故将各电阻设为高阻多晶型。

然而,高阻多晶虽然有很高的方阻,但是工艺稳定性不太好,故后期的Trimming 工序是必不可少的。

最后,确定电流镜的尺寸。

采用适当偏小的宽长比,可以提高电流镜的过驱动电压,进而可以减小电流镜阈值电压失配所带来的影响。

另外,沟道长度调制效应也是一个重要影响因素,考虑到低压应用不能使用Cascode结构,可以增大器件的栅长来减小沟道长度调制效应的影响。

但是过大的沟道长度会导致版图的面积的增加,需要在性能和版图面积之间做出折中。

经过计算与迭代仿真,选取M1、M2和M3的宽长比为10um/1um。

注意电流镜的版图设计中需采用中心对称布局以减小误差。

综上,通过理论分析,确定带隙核心电路的器件参数为:运算放大器设计运放的性能对带隙的性能有着直接的影响。