CMOS版图设计技巧之一

- 格式:ppt

- 大小:1.58 MB

- 文档页数:39

CMOS反相器的电路仿真及其工艺模拟和版图设计摘要:CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

本文主要通过简单的介绍基于Cadence的CMOS反相器的电路仿真和版图设计及基于SILV ACO的CMOS反相器的工艺仿真,体现了集成电路CAD 的一种基本方法和操作过程。

关键词:CMOS反相器、Cadence、SILV ACO、仿真、工艺、版图0引言:电子技术的发展使计算机辅助设计(CAD)技术成为电路设计不可或缺的有力工具。

国内外电子线路CAD软件的相继推出与版本更新,是CAD技术的应用渗透到电子线路与系统设计的各个领域,如电路图和版图的绘制、模拟电路仿真、工艺模拟与仿真、逻辑电路分析、优化设计、印刷电路板的布线等。

CAD 技术的发展使得电子线路设计的速度、质量、精确度得以保证。

顺应集成电路发展的要求,集成电路CAD,确切地说是整个电子设计自动化必须要有更大的发展。

随着集成电路与计算机的迅速发展,以CAD为基础的EDA技术一渗透到电子系统和专用集成电路设计的各个环节。

一个能完成比较复杂的VLSI设计的EDA系统一般包括10~20个CAD工具,涉及从高层次数字电路的自动综合、数字系统仿真、模拟电路仿真到各种不同层次的版图设计和校验工具,完成自顶向下的VLSI设计的各个环节和全部过程。

为满足日益增大的信息处理能力的需求,主要从实现图形最小尺寸的工艺精度和提高单位面积晶体管数目的集成度两个方面来努力,还要综合考虑满足电路功能以及工作频率和功耗的性能指标。

CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

1基于Cadence的CMOS反相器的设计:1.1 Cadence简介:Cadence是一个大型的EDA软件,它几乎可以完成电子设计的方方面面,包括ASIC设计、FPGA设计和PCB板设计。

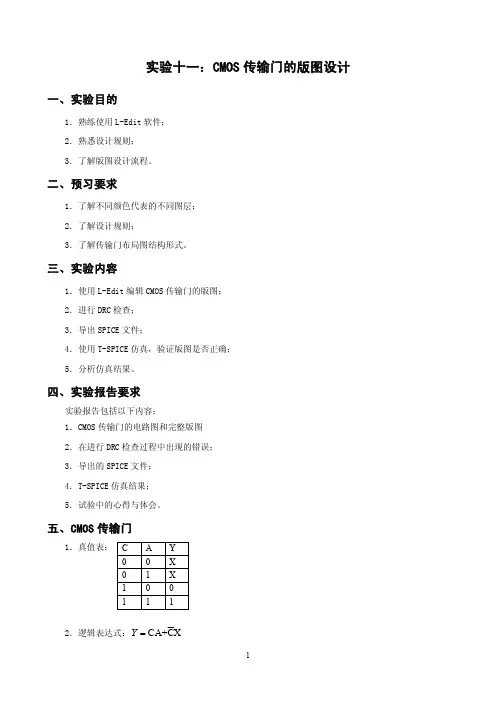

实验十一:CMOS 传输门的版图设计一、实验目的1.熟练使用L-Edit 软件; 2.熟悉设计规则; 3.了解版图设计流程。

二、预习要求1.了解不同颜色代表的不同图层; 2.了解设计规则;3.了解传输门布局图结构形式。

三、实验内容1.使用L-Edit 编辑CMOS 传输门的版图; 2.进行DRC 检查; 3.导出SPICE 文件;4.使用T-SPICE 仿真,验证版图是否正确; 5.分析仿真结果。

四、实验报告要求实验报告包括以下内容:1.CMOS 传输门的电路图和完整版图 2.在进行DRC 检查过程中出现的错误; 3.导出的SPICE 文件; 4.T-SPICE 仿真结果; 5.试验中的心得与体会。

五、CMOS 传输门1.真值表:2.逻辑表达式:CA+CX YC A Y 0 0 X 0 1 X 1 0 0 111A Y5.波形图:六、操作步骤:1.新建文件夹:在电脑E盘新建文件夹,文件夹名为ex11。

2.打开L-Edit软件:在桌面上双击L-Edit v13.0快捷键,打开L-Edit v13.0软件,如图所示。

3.另存新文件:选择File——Save As命令,打开“另存为”对话框,在“保存在”下拉列表框中选择存储目录(存储在刚才新建的文件夹ex11中),在“文件名”文本框中输入新文件名称,例如:ex11。

4.取代设定:选择File——Replace Setup命令,单击出现的对话框的From file下拉列表右侧的Browser按钮,选择d:\My Documents\Tanner EDA\Tanner Toolsv13.0\L-Edit and LVS\SPR\Lights\Layout\lights.tdb文件,如图所示,再单击OK按钮。

接着出现一个警告对话框,按确定按钮,就可将lights.tdb文件的设定选择性应用在目前编辑的文件,包括格点设定、图层设定等。

5.重新命名:将Cell0的名称重新命名,可选择Cell——Rename命令,打开Rename Cell Cell0 对话框,将cell0名称改成CMOSTG。

XXXXXXX实验报告课程名称:集成电路设计实验名称:CMOS反相器版图设计学号姓名:指导教师评定:____________________________ 签名:_____________________________一、实验目的1、了解集成电路版图设计流程。

2、利用L-Edit 进行NMOSFET 版图设计。

3、利用L-Edit 进行CMOS反相器设计。

二、实验器材计算机一台,Tanner L-Edit软件三、实验原理CMOS 反相器由PMOS 和NMOS 晶体管组成,利用PMOS晶体管版图和NMOS 晶体管版图可以完成COMS反相器版图的设计。

四、实验步骤1、设计PMOS晶体管版图。

2、设计N MOS晶体管版图。

3、设计CMOS反相器版图:(1)启动版图编辑器L-Edit。

(2)新建文件。

新建一个Layout 文件,文件的设置信息可以从前面创建的文件中复制。

(3) 对文件进行重命名。

将L-Edit 编辑器默认的文件名Layout 改为Inverter。

(4) 设置格点与坐标。

格点与坐标的设定方式与创建PMOS 晶体管时设定的方法一致。

(5) 调用PMOS 和NMOS 晶体管作为例化单元。

使用Cell---Instance 命令来调用PMOS 单元。

在出现的Select Cell to Instance 对话框中,通过点击Browse按钮浏览到“MOS”文件,可以看到该文件下面有PMOS 和NMOS 两个单元,点击PMOS,然后点击“OK”,可以看到Inverter 文件cell0 单元的版图已经添加了PMOS 单元。

利用同样的方法,可以将NMOS 单元也添加进来。

(6) 连接PMOS 和NMOS 晶体管的栅极。

从CMOS 反相器电路可知,PMOS晶体管和NMOS 晶体管的栅极要连在一起作为反相器的输入端,所以在放置这两个晶体管的时候可以将两者的栅极对准,以便连接。

具体操作是,选择Layer的多晶硅(Poly)层和方框绘图工具后,在版图区域中画一个宽度与晶体管栅极相等的多晶硅矩形,如图1 所示。

CMOS IC 版图设计技巧1、布局要合理(1)引出端分布是否便于使用或与其他相关电路兼容,是否符合管壳引出线排列要求。

(2)特殊要求的单元是否安排合理,如p阱与p管漏源p+区离远一些,使βpnp↓,抑制Latch-up,尤其是输出级更应注意。

(3)布局是否紧凑,以节约芯片面积,一般尽可能将各单元设计成方形。

(4)考虑到热场对器件工作的影响,应注意电路温度分布是否合理。

2、单元配置恰当(1)芯片面积降低10%,管芯成品率/圆片可提高15~20%。

(2)多用并联形式,如或非门,少用串联形式,如与非门。

(3)大跨导管采用梳状或马蹄形,小跨导管采用条状图形,使图形排列尽可能规整。

3、布线合理•布线面积往往为其电路元器件总面积的几倍,在多层布线中尤为突出。

•扩散条/多晶硅互连多为垂直方向,金属连线为水平方向,电源地线采用金属线,与其他金属线平行。

•长连线选用金属。

•多晶硅穿过Al线下面时,长度尽可能短,以降低寄生电容。

•注意VDD、VSS布线,连线要有适当的宽度。

•容易引起“串扰”的布线(主要为传送不同信号的连线),一定要远离,不可靠拢平行排列。

4、CMOS电路版图设计对布线和接触孔的特殊要求(1)为抑制Latch up,要特别注意合理布置电源接触孔和VDD引线,减小横向电流密度和横向电阻RS、RW。

∙采用接衬底的环行VDD布线。

∙增多VDD、VSS接触孔,加大接触面积,增加连线牢固性。

∙对每一个VDD孔,在相邻阱中配以对应的VSS接触孔,以增加并行电流通路。

∙尽量使VDD、VSS接触孔的长边相互平行。

∙接VDD的孔尽可能离阱近一些。

∙接VSS的孔尽可能安排在阱的所有边上(P阱)。

(2)尽量不要使多晶硅位于p+区域上多晶硅大多用n+掺杂,以获得较低的电阻率。

若多晶硅位于p+区域,在进行p+掺杂时多晶硅已存在,同时对其也进行了掺杂——导致杂质补偿,使ρ多晶硅↑。

(3)金属间距应留得较大一些(3λ或4λ)因为,金属对光得反射能力强,使得光刻时难以精确分辨金属边缘。

集成电路版图设计入门主要内容:•版图设计概念;•CMOS VLSI制造工艺;•Tanner版图流程举例(反相器)。

版图设计概念定义:版图设计是创建工程制图(网表)的精确的物理描述过程,而这一物理描述遵守有制造工艺、设计流程以及通过仿真显示为可行的性能要求所带来的一系列约束。

双极集成电路版图设计MOS集成电路版图设计电压比较器运算放大器CMOS VLSI制造工艺(略)参见相关资料Tanner版图流程举例(反相器)集成电路设计近年来发展相当迅速,许多设计需要借助计算机辅助设计软件。

作为将来从事集成电路设计的工作人员,至少需要对版图有所了解,但是许多软件(如cadence)实在工作站上执行的,不利于初学者。

L-Edit软件是基于PC上的设计工具,简单易学,操作方便,通过学习,掌握版图的设计流程。

Tanner Pro简介:Tanner Pro是一套集成电路设计软件,包括S-EDIT,T-SPICE,W-EDIT,L-EDIT,与LVS ,他们的主要功能分别如下:1、S-Edit:编辑电路图2、T-Spice:电路分析与模拟3、W-Edit:显示T-Spice模拟结果4、L-Edit:编辑布局图、自动配置与绕线、设计规则检查、截面观察、电路转化5、LVS:电路图与布局结果对比设计参数的设置Setup>Design •该对话框共有六页,分别是:Technology(工艺参数)、Grid(网格参数)、Selection(选择参数)、Drawing(绘图参数)、Curves(曲线参数)、Xref files(外部交叉引用参数)•网格分为显示网格、鼠标网格(跳跃、平滑)、定位器网格设计规则的作用•设计规则规定了生产中可以接受的几何尺寸的要求和达到的电学性能。

•对设计和制造双方来说,设计规则既是工艺加工应该达到的规范,也是设计必循遵循的原则•设计规则表示了成品率和性能的最佳折衷设计规则的设置(一)、设计的类型•Minimum Width•Exact Width•Not Exist•Spacing•Surround•Overlap•Extension•Density(1)Minimum Width 该层上所有object在任意方向上的宽度(2) Exact width 该层上所有object在特定方向上的准确宽度(3)Not Exist在指定的层上,所有object都不能存在.这是唯一不含距离的规则(4)Spacing在指定的层上或者在指定的两层之间的object的最小间距(5)Surround 一个层上的物体,在每个方向上,被另一层上的物体至少要环绕x各单位(6)Overlap 一个层上的物体必须与另一个层上的物体交叠的最小尺寸。

CMOS反相器的版图设计实验一:CMOS反相器得版图设计一、实验目得1、创建CMOS反相器得电路原理图(Schematic)、电气符号(symbol)以及版图(layout);2、利用’gpdk090’工艺库实例化MOS管;3、运行设计规则验证(Design RuleCheck,DRC)确保版图没有设计规则错误。

二、实验要求1、打印出完整得CMOS反相器得电路原理图以及版图;2、打印CMOS反相器得DRC报告。

三、实验工具Virtuoso四、实验内容1、创建CMOS反相器得电路原理图;2、创建CMOS反相器得电气符号;3、创建CMOS反相器得版图;4、对版图进行DRC验证。

1、创建CMOS反相器得电路原理图及电气符号图首先创建自己得工作目录并将/home/iccad/cds、lib复制到自己得工作目录下(我得工作目录为/home/iccad/iclab),在工作目录内打开终端并打开virtuoso(命令为icfb&)、在打开得icfb –log中选择tools->LibraryManager,再创建自己得库,在当前得对话框上选择File->New->Library,创建自己得库并为自己得库命名(我得命名为lab1),点击OK后在弹出得对话框中选择Attach to an exiting techfile并选择gpd k090_v4、6得库,此时Library manager 得窗口应如图1所示:图1创建好得自己得库以及inv创建好自己得库之后,就可以开始绘制电路原理图,在Library manager 窗口中选中lab1,点击File->New->Cell view,将这个视图命名为inv(CMOS反相器)。

需要注意得就就是Library Na me一定就就是自己得库,View Name就就是schematic,具体如图2所示:图2inv电路原理图得创建窗口点击OK后弹出schematic editing得对话框,就可以开始绘制反相器得电路原理图(schematic view)。

Lab 9 CMOS反相器版图设计1.实验目的1.1 学会版图自动生成方法1.2 掌握CMOS电路版图设计流程1.3 了解数字模块设计方法2.实验内容版图自动生成如果在lab7与lab8中,绘制nmos、pmos、npn等单元版图存在困难,可使用版图自动生成命令来产生版图,以便后续实验的进行。

nmos版图生成法①在CIW中,选择File→Open,选项设置如下:Library Name designCell Name nmosView Name layout打开nmos的空白视图。

②在CIW中,输入如下命令:hiReplayFile(“LOG/nmos.log”)③按Return键。

④选择Window→Fill All,完成自动生成nmos版图。

⑤存档。

pmos版图生成法①在CIW中,选择File→Open,选项设置如下:Library Name designCell Name pmosView Name layout打开pmos的空白视图。

②在CIW中,输入如下命令:③按Return键。

④选择Window→Fill All,完成自动生成pmos版图。

⑤存档。

npn版图生成法与nmos生成法相同,仅仅在①、②步骤中将nmos改为npn即可。

Inverter版图设计Inverter版图设计规则①单元高度18.0u②power与ground宽度1.8u③ndiff到pdiff间距0.5u④metal1之间间距0.8u⑤metal1宽度0.8u安置mos版图①在CIW中,选择File→Open,设置如下:Library Name designCell Name inverterView Name layout点击OK,弹出Inverter的设计窗口。

②在设计窗口中,选择Create→Instance[i],在Create Instance窗口中,改变设置如图9.1所示。

图9.1 Create Instance窗口图9.2 Create Shape Pin窗口③设置结束后,在设计窗口中,点击LMB完成添加nmos版图。