CMOS电路与逻辑设计

- 格式:ppt

- 大小:12.84 MB

- 文档页数:111

CMOS逻辑电路设计CMOS(Complementary Metal-Oxide-Semiconductor)逻辑电路是现代集成电路中广泛应用的一种电路结构。

它由N沟道MOS(NMOS)和P沟道MOS(PMOS)互补组成,具有低功耗、高噪声抑制和高速运算等优势。

在本文中,我们将探讨CMOS逻辑电路的设计原理和方法。

一、CMOS逻辑门的基本结构CMOS逻辑门是由一对互补的MOS管组成的。

其中,NMOS管是由N沟道与P+掺杂的互补金属氧化物半导体(CMOS)结构形成,而PMOS管是由P沟道与N+掺杂的CMOS结构形成。

CMOS逻辑电路通过控制这些NMOS管和PMOS管的某些管子通断来实现逻辑运算。

二、CMOS逻辑门的基本原理CMOS逻辑门的基本原理是利用MOS管在开关状态时流过的电流来实现信号的逻辑运算。

当NMOS管的门极接收到高电平信号(逻辑1)时,通常情况下,NMOS管导通,PMOS管截止。

相反,当NMOS 管的门极接收到低电平信号(逻辑0)时,NMOS管截止,PMOS管导通。

通过这种控制逻辑,CMOS逻辑门可以实现与门、或门、非门等基本逻辑运算。

三、CMOS逻辑电路的设计方法在进行CMOS逻辑电路设计时,需要遵循以下步骤:1. 确定逻辑功能:根据所需的逻辑运算,确定需要设计的CMOS逻辑门类型。

2. 绘制逻辑图:根据所需的逻辑功能,用逻辑符号绘制电路的逻辑图。

3. 分析逻辑功能:根据逻辑图,分析逻辑门输入和输出之间的关系,确定每个逻辑门的输入和输出真值表。

4. 选择器件尺寸:根据所需的逻辑门延迟、功耗和面积等要求,选择合适的管子尺寸。

5. 进行布线:根据所选用的管子尺寸,进行电路的布线设计。

6. 进行模拟仿真:使用电路设计软件,进行CMOS逻辑电路的仿真,验证其功能和性能。

7. 进行物理实现:根据设计结果,进行CMOS逻辑电路的物理实现,包括掩膜制作、晶圆制作和封装测试等过程。

四、CMOS逻辑电路的优势与应用CMOS逻辑电路具有以下优势:1. 低功耗:由于CMOS逻辑电路的特殊结构,只有在发生信号变换时才会有较大电流流过。

CMOS组合逻辑门的设计CMOS(互补金属氧化物半导体)是一种集成电路技术,由P型和N型MOS(金属氧化物半导体)组成。

CMOS技术被广泛应用于数字逻辑门的设计中。

本文将详细介绍CMOS组合逻辑门的设计过程。

组合逻辑门是一种不带有存储元件的数字电路,根据输入的状态产生相应的输出状态。

CMOS组合逻辑门由MOS场效应晶体管和电阻组成。

在CMOS技术中,MOS晶体管可以工作在两种模式下:通过模式和截止模式。

通过模式下的晶体管导通,截止模式下的晶体管断开。

CMOS逻辑门的设计过程通常包括以下步骤:1.需求分析:首先确定需要设计的逻辑门的功能和特性。

了解输入输出关系和逻辑表达式。

2.逻辑表达式转换:将逻辑表达式转换为布尔代数表达式。

根据布尔代数原理,使用布尔代数运算符对逻辑表达式进行化简和转化。

3.逻辑电路设计:根据逻辑表达式,使用MOS晶体管和电阻等元件设计逻辑电路。

4.原理图绘制:根据逻辑电路设计,使用电路设计软件绘制电路原理图。

将所需的逻辑门、晶体管和电阻等组件进行布局。

5.模拟仿真:使用电路设计软件进行模拟仿真,验证逻辑门的设计是否正确。

通过输入信号,验证输出信号是否符合逻辑表达式。

6.物理布局设计:根据电路原理图和仿真结果,进行逻辑门的物理布局设计。

确保信号传输的最佳路径和减小电路延迟。

7.版图布线:根据物理布局设计,进行电路的版图布线。

将各个组件进行布线,保证信号传输的稳定性和最短路径。

8.工艺制造:根据版图布线,转化为切割、离子注入或敏感处理等工艺制造步骤。

生产出需要的CMOS逻辑门。

CMOS技术在逻辑门设计中具有许多优点,如低功耗、高集成度、高噪声抑制能力等。

CMOS逻辑门由于其优势得到了广泛应用,如在微处理器、数字信号处理器和存储器中。

总之,CMOS组合逻辑门的设计过程包括需求分析、逻辑表达式转换、逻辑电路设计、原理图绘制、模拟仿真、物理布局设计、版图布线和工艺制造等步骤。

CMOS技术在逻辑门设计中具有优越性能,得到了广泛应用。

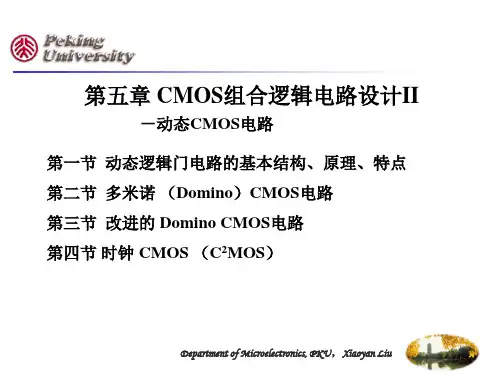

第五章CMOS组合逻辑电路设计II -动态CMOS电路第一节动态逻辑门电路的基本结构、原理、特点第二节多米诺(Domino)CMOS电路第三节改进的Domino CMOS电路第四节时钟CMOS (C2MOS)第一节动态逻辑门电路的基本结构、原理、特点一、预充-求值动态CMOS的基本结构和工作原理二、动态CMOS的特点三、动态CMOS的问题四、动态CMOS的级联静态电路:靠管子稳定的导通、截止来保持输出状态除状态反转外,输出始终与VDD和GND保持通路。

动态电路:靠电容来保存信息一、预充-求值动态CMOS 的基本结构和工作原理In 1In 2PDN In 3M e M p Clk Clk Out C L 预充-求值动态CMOS 电路的基本结构工作过程:➢预充阶段:Clk =0,Out 被Mp 预充到VDD ,Me 截止,无论输入何值,均不存在直流通路。

此时的输出无效。

➢求值阶段:Clk =1,Mp 截止,Me 导通,Out和GND 之间形成一条有条件的路径。

具体由PDN 决定。

若PDN 存在该路径,则Out 被放电,Out 为低电平,“0”。

如果不存在,则预充电位保存在CL 上,Out 为高电平“1”。

➢求值阶段,只能有与GND 间的通路,无与VDD 间的,一旦放电,不可能再充电,只能等下次。

预充FET 求值FET预充-求值动态CMOS 电路的工作原理预充预充求值输出只在此时有效),2,1(Xn X X F Y ⋅⋅⋅=当Clk =1时Clk OutClk =0时,输出为1,与输入无关OutClk Clk ABCM p M e on off 1off on((AB)+C)例PUNPUN 构成的动态CMOS 电路),2,1(Xn X X F Y ⋅⋅⋅=Clk =1时,输出为0,与输入无关当Clk =0时一般不用PUN 网络二、动态CMOS的特点•逻辑功能由下拉网络PDN实现。

其结构和设计与互补CMOS 和类NMOS的一样。

【精品】数字集成电路--电路、系统与设计(第二版)课后练习题第六章CMOS组合逻辑门的设计第六章 CMOS组合逻辑门的设计1.为什么CMOS电路逻辑门的输入端和输出端都要连接到电源电压?CMOS电路采用了MOSFET(金属氧化物半导体场效应管)作为开关元件,其中N沟道MOSFET(NMOS)和P沟道MOSFET(PMOS)分别用于实现逻辑门的输入和输出。

NMOS和PMOS都需要连接到电源电压,以使其能够正常工作。

输入端连接到电源电压可以确保信号在逻辑门中正常传递,输出端连接到电源电压可以确保输出信号的正确性和稳定性。

2.为什么在CMOS逻辑门中要使用两个互补的MOSFET?CMOS逻辑门中使用两个互补的MOSFET是为了实现高度抗干扰的逻辑功能。

其中,NMOS和PMOS分别用于实现逻辑门的输入和输出。

NMOS和PMOS的工作原理互补,即当NMOS导通时,PMOS截止,当PMOS导通时,NMOS截止。

这样的设计可以在逻辑门的输出上提供高电平和低电平的稳定性,从而提高逻辑门的抗干扰能力。

3.CMOS逻辑门的输入电压范围是多少?CMOS逻辑门的输入电压范围通常是在0V至电源电压之间,即在低电平和高电平之间。

在CMOS逻辑门中,低电平通常定义为输入电压小于0.3Vdd(电源电压的30%),而高电平通常定义为输入电压大于0.7Vdd(电源电压的70%)。

4.如何设计一个基本的CMOS逻辑门?一个基本的CMOS逻辑门可以由一个NMOS和一个PMOS组成。

其中,NMOS的源极连接到地,栅极连接到逻辑门的输入,漏极连接到PMOS的漏极;PMOS的源极连接到电源电压,栅极连接到逻辑门的输入,漏极连接到输出。

这样的设计可以实现逻辑门的基本功能。

5.如何提高CMOS逻辑门的速度?可以采取以下方法来提高CMOS逻辑门的速度:•减小晶体管的尺寸:缩小晶体管的尺寸可以减小晶体管的电容和电阻,从而提高逻辑门的响应速度。

•优化电源电压:增加电源电压可以提高晶体管的驱动能力,从而加快逻辑门的开关速度。

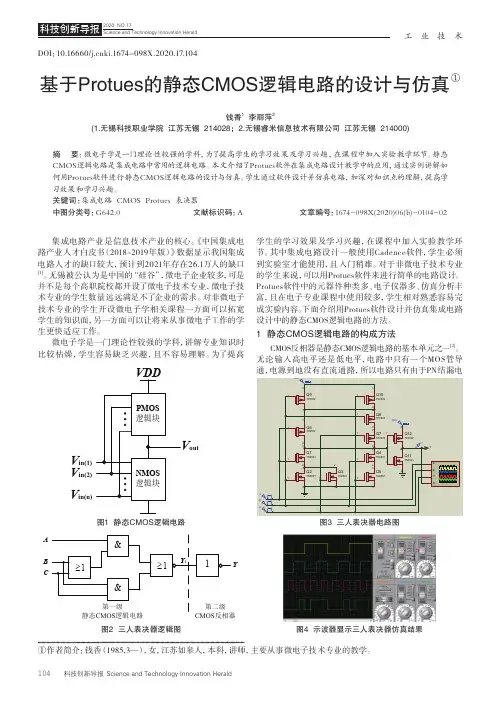

工业技术科技创新导报 Science and Technology Innovation Herald104DOI:10.16660/ki.1674-098X.2020.17.104基于Protues的静态CMOS逻辑电路的设计与仿真①钱香1 李丽萍2(1.无锡科技职业学院 江苏无锡 214028;2.无锡睿米信息技术有限公司 江苏无锡 214000)摘 要:微电子学是一门理论性较强的学科,为了提高学生的学习效果及学习兴趣,在课程中加入实验教学环节。

静态CMOS逻辑电路是集成电路中常用的逻辑电路。

本文介绍了Protues软件在集成电路设计教学中的应用,通过实例讲解如何用Protues软件进行静态CMOS逻辑电路的设计与仿真。

学生通过软件设计并仿真电路,加深对知识点的理解,提高学习效果和学习兴趣。

关键词:集成电路 CMOS Protues 表决器中图分类号:G642.0 文献标识码:A 文章编号:1674-098X(2020)06(b)-0104-02①作者简介:钱香(1985,3—),女,江苏如皋人,本科,讲师,主要从事微电子技术专业的教学。

集成电路产业是信息技术产业的核心。

《中国集成电路产业人才白皮书(2018-2019年版)》数据显示我国集成电路人才的缺口较大,预计到2021年存在26.1万人的缺口[1]。

无锡被公认为是中国的“硅谷”,微电子企业较多,可是并不是每个高职院校都开设了微电子技术专业,微电子技术专业的学生数量远远满足不了企业的需求。

对非微电子技术专业的学生开设微电子学相关课程一方面可以拓宽学生的知识面,另一方面可以让将来从事微电子工作的学生更快适应工作。

微电子学是一门理论性较强的学科,讲解专业知识时比较枯燥,学生容易缺乏兴趣,且不容易理解。

为了提高学生的学习效果及学习兴趣,在课程中加入实验教学环节。

其中集成电路设计一般使用Cadence软件,学生必须到实验室才能使用,且入门稍难。

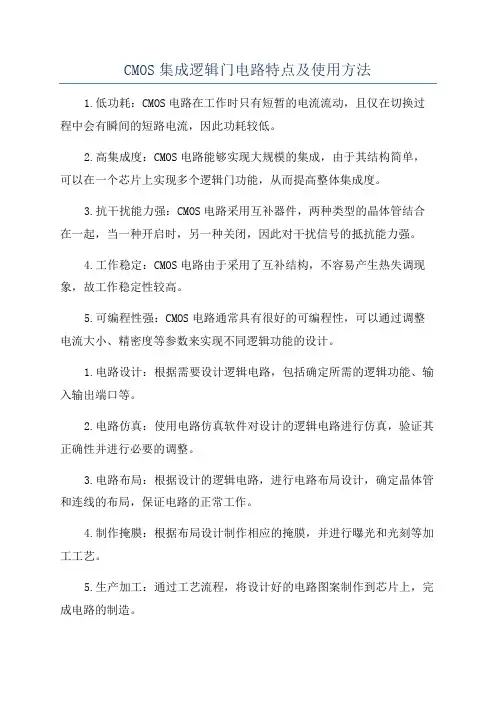

CMOS集成逻辑门电路特点及使用方法

1.低功耗:CMOS电路在工作时只有短暂的电流流动,且仅在切换过程中会有瞬间的短路电流,因此功耗较低。

2.高集成度:CMOS电路能够实现大规模的集成,由于其结构简单,可以在一个芯片上实现多个逻辑门功能,从而提高整体集成度。

3.抗干扰能力强:CMOS电路采用互补器件,两种类型的晶体管结合在一起,当一种开启时,另一种关闭,因此对干扰信号的抵抗能力强。

4.工作稳定:CMOS电路由于采用了互补结构,不容易产生热失调现象,故工作稳定性较高。

5.可编程性强:CMOS电路通常具有很好的可编程性,可以通过调整电流大小、精密度等参数来实现不同逻辑功能的设计。

1.电路设计:根据需要设计逻辑电路,包括确定所需的逻辑功能、输入输出端口等。

2.电路仿真:使用电路仿真软件对设计的逻辑电路进行仿真,验证其正确性并进行必要的调整。

3.电路布局:根据设计的逻辑电路,进行电路布局设计,确定晶体管和连线的布局,保证电路的正常工作。

4.制作掩膜:根据布局设计制作相应的掩膜,并进行曝光和光刻等加工工艺。

5.生产加工:通过工艺流程,将设计好的电路图案制作到芯片上,完成电路的制造。

6.测试验证:对制作好的CMOS电路进行测试验证,检查其性能和功能是否符合设计要求。

总的来说,CMOS集成逻辑门电路具有低功耗、高集成度、抗干扰能力强、工作稳定等优点,广泛应用于数字电路、微处理器、存储器、通信电路、模拟电路等领域。

在使用CMOS集成电路时,需要进行电路设计、仿真、布局、制作掩膜、生产加工和测试验证等步骤,以确保电路的正常工作和性能达到设计要求。

CMOS技术的不断发展将为电子行业带来更多的创新和发展机遇。

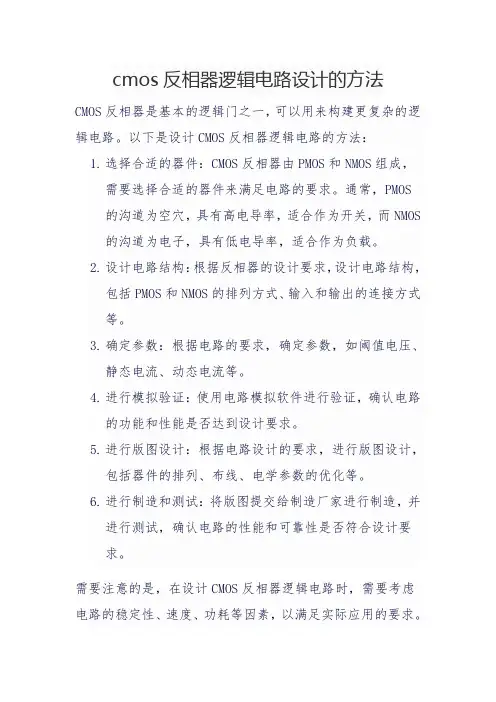

cmos反相器逻辑电路设计的方法CMOS反相器是基本的逻辑门之一,可以用来构建更复杂的逻辑电路。

以下是设计CMOS反相器逻辑电路的方法:

1.选择合适的器件:CMOS反相器由PMOS和NMOS组成,

需要选择合适的器件来满足电路的要求。

通常,PMOS

的沟道为空穴,具有高电导率,适合作为开关,而NMOS

的沟道为电子,具有低电导率,适合作为负载。

2.设计电路结构:根据反相器的设计要求,设计电路结构,

包括PMOS和NMOS的排列方式、输入和输出的连接方式

等。

3.确定参数:根据电路的要求,确定参数,如阈值电压、

静态电流、动态电流等。

4.进行模拟验证:使用电路模拟软件进行验证,确认电路

的功能和性能是否达到设计要求。

5.进行版图设计:根据电路设计的要求,进行版图设计,

包括器件的排列、布线、电学参数的优化等。

6.进行制造和测试:将版图提交给制造厂家进行制造,并

进行测试,确认电路的性能和可靠性是否符合设计要

求。

需要注意的是,在设计CMOS反相器逻辑电路时,需要考虑电路的稳定性、速度、功耗等因素,以满足实际应用的要求。

同时,还需要遵循基本的电路设计规则和安全规范,如避免电流过大、避免信号过冲等。

cmos数字集成逻辑电路设计CMOS数字集成逻辑电路设计是现代数字电路设计领域的一项关键技术。

随着数字电路应用不断发展与普及,对于此类技术的追求与优化也愈加重要。

本文将分步骤阐述CMOS数字集成逻辑电路设计的一般过程。

第一步是确定设计需求。

这一步需要明确设计的目标和功能,包括输入与输出引脚、工作时钟周期、功耗、延迟和芯片尺寸等因素。

在实际设计过程中,需求的明确和合理性直接影响到最终设计的成败。

第二步是进行逻辑设计。

在此步骤中,需要确定数字逻辑电路的功能和实现方法,如AND, OR, NOT等基本逻辑门的组合,以及具体的逻辑条件。

此外,还需要进行布尔代数化简、卡诺图化简等工作,用以简化电路结构,减少电路面积和功耗,提高电路速度。

第三步是进行电路原理图设计。

在此步骤中,需要按照逻辑设计的结果,利用EDA工具进行电路原理图的绘制。

电路原理图绘制的关键在于结构的清晰和细节的精确,避免因细节失误导致后续的时间和金钱资源浪费。

第四步是电路模拟与验证。

通过电路模拟与验证,可验证电路设计在特定时钟周期和环境下是否达到了设计目标。

此步骤中所使用的EDA工具需要具备较高的仿真性能和准确性。

第五步是版图设计。

在此步骤中,需要将电路原理图转换成实际布局的物理结构。

在版图设计中,需要考虑诸如电路线路规则、布局约束、电压降等实际问题。

此外,芯片面积的大小也是版图设计的关键课题,需权衡面积与功能的平衡。

第六步是芯片制造。

此时,制造工厂将按照版图所示输出芯片端口线路,并且附有一层层次膜的还原模式。

在制造过程中,需考虑工艺的纯度和稳定性,以确保芯片符合设计要求。

总的来说,CMOS数字集成逻辑电路设计的过程复杂而繁琐,需要开发者的技术水平、设计经验和耐心等多方面素质的加持。

然而,强大的数字电路设计工具和准确而稳定的工艺技术,也使得CMOS数字集成逻辑电路设计的困难被逐步克服。

cmos 开关电路设计CMOS 开关电路设计CMOS (互补金属氧化物半导体) 开关电路是数字集成电路设计中非常重要的基本构建模块。

它们广泛应用于存储器、数据通路和控制逻辑等领域。

CMOS 开关电路具有低功耗、高噪声免疫性和良好的可扩展性等优点。

1. CMOS 传输门传输门是最基本的 CMOS 开关电路,由一个 NMOS 和一个 PMOS 晶体管并联组成。

当控制信号为逻辑高电平时,传输门打开,输入端与输出端之间传输数据;当控制信号为逻辑低电平时,传输门关闭,输入端与输出端之间断开连接。

2. CMOS 复传输门复传输门由两个并联的传输门组成,可以在输入端和输出端之间传输补码信号对。

这种结构常用于设计存储单元、多路复用器/解复用器等电路。

3. CMOS 三态门三态门是一种特殊的开关电路,除了开路和关路两种状态外,还有一种高阻抗状态。

它由一个传输门和一个反相器组成。

当使能信号为逻辑高电平时,三态门处于开路状态;当使能信号为逻辑低电平时,三态门处于关路状态;当使能信号处于高阻抗状态时,三态门的输出端也处于高阻抗状态。

三态门常用于构建总线结构。

4. CMOS 开关电容器开关电容器是一种采样数据的电路,由一个传输门和一个电容器组成。

当时钟信号为高电平时,传输门导通,输入端的电压值被采样存储在电容器中;当时钟信号为低电平时,传输门关闭,电容器保持之前采样的电压值。

开关电容器广泛应用于模数转换器、滤波器和模拟信号处理电路中。

CMOS 开关电路的设计需要考虑信号完整性、可靠性、功耗和布局等多方面因素。

正确的电路拓扑结构、尺寸和布局布线对于获得良好的性能至关重要。

一、CMOS异或电路的基本原理CMOS异或电路是指一种采用CMOS技术实现的异或逻辑门电路。

在数字电路中,异或门是一种常见的逻辑门,它的输出为两个输入信号中恰好有一个为高电平时才为高电平,否则为低电平。

CMOS技术是一种集成电路制造工艺,其特点是低功耗、高集成度和稳定性好,因此广泛应用于数字电路和逻辑门的设计中。

在CMOS异或电路中,通常采用nMOS和pMOS管子构成,nMOS 管子作为传输门使得当输入为低电平时,电路能够正常工作。

由于nMOS管子具有较小的开漏电阻和较大的电导,因此在CMOS异或电路中,nMOS管子经常被用来设计传输门。

而pMOS管子则通常用来实现逻辑门的输出驱动。

通过精心设计和布局nMOS和pMOS管子,可以实现高性能、低功耗的CMOS异或电路。

二、CMOS异或电路的设计方法在CMOS异或电路的设计中,首先需要明确电路的功能需求,包括输入输出信号的特性、工作电压和功耗限制等。

然后根据这些需求,确定电路的整体结构和原理图。

通常可以采用常用的逻辑门电路设计软件进行仿真和优化,以实现最佳的性能和功耗平衡。

在具体的nMOS和pMOS管子的选择和布局上,需要考虑到电路的输入输出特性、驱动能力和功耗等方面的权衡。

通常可以通过模拟电路仿真软件进行模拟和分析,以找到最佳的设计方案。

另外,对于CMOS异或电路的布线和布局也是非常重要的。

合理的布线和布局可以减小电路的传输延迟和功耗损耗,提高电路的可靠性和稳定性。

三、CMOS异或电路的应用领域CMOS异或电路广泛应用于数字逻辑电路和系统中。

由于其优秀的性能和低功耗特性,CMOS异或电路在计算机、通讯、嵌入式系统等领域得到了广泛的应用。

在计算机的CPU中,CMOS异或电路常常用于实现数据的异或运算,以实现逻辑运算、加密解密等功能。

在通讯系统中,CMOS异或电路常常被用于实现信号的处理和编码解码等功能。

另外,在嵌入式系统中,CMOS异或电路也常常被用于实现各种控制和逻辑功能。

写出下列CMOS电路逻辑表达式在现代数字电子电路设计中,CMOS(Complementary Metal-Oxide-Semiconductor)技术被广泛应用于集成电路的设计和制造。

CMOS电路由N型MOS(NMOS)和P型MOS(PMOS)两种互补型MOSFET(金属-氧化物-半导体场效应晶体管)组成。

CMOS技术以其低功耗、高集成度和良好的抗干扰能力而闻名。

本文就笔者提供的CMOS电路进行详细的逻辑表达式分析,对其进行深度和广度的探讨。

1. CMOS电路1逻辑表达式根据提供的CMOS电路1图纸,其逻辑表达式为:Y = (A+B) * (C+D)对于该逻辑表达式,我们可以简要分析其工作原理。

当A、B、C、D 均为低电平(逻辑0)时,NMOS管截止,PMOS管导通,输出Y为高电平(逻辑1);当A、B、C、D中任意一个或多个为高电平(逻辑1)时,对应的NMOS管导通,PMOS管截止,输出Y为低电平(逻辑0)。

2. CMOS电路2逻辑表达式根据提供的CMOS电路2图纸,其逻辑表达式为:Y = A * (B+C) + (D*E)根据提供的逻辑表达式,我们可以进行进一步分析。

当A为高电平(逻辑1)时,NMOS导通,PMOS截止,B、C中任意一个或多个为高电平时,对应的NMOS导通,PMOS截止,输出Y为高电平;当D为高电平时,对应的NMOS导通,PMOS截止,E为低电平时,对应的NMOS截止,PMOS导通,输出Y为高电平。

通过对这两个CMOS电路逻辑表达式的分析,我们可以看到CMOS技术的优势在于其能够实现低功耗和高性能的数字电路设计。

CMOS电路的逻辑表达式也能够通过简单的分析,清晰地描述其逻辑功能和工作原理。

总结而言,CMOS电路逻辑表达式的分析不仅有助于理解数字电子电路的设计和工作原理,还能够帮助我们更好地应用CMOS技术进行集成电路设计。

通过本文的探讨,相信读者已经对CMOS电路的逻辑表达式有了更深入的理解,也对CMOS技术有了更全面的认识。