交叉耦合电容在LNA和MIXER中的应用 ieee

- 格式:pdf

- 大小:118.38 KB

- 文档页数:4

伊娜耦合专用电容是一种电子元件,通常用于电路中的耦合、滤波、去耦等作用。

这些电容器的特点是具有较小的体积、高稳定性和高精度,因此在各种电子设备中得到了广泛的应用。

伊娜耦合专用电容的型号和规格有很多种,不同的型号和规格具有不同的参数和特点,例如电容量、电压、耐温范围、尺寸等。

在选择伊娜耦合专用电容时,需要根据具体的电路要求和应用场景来选择合适的型号和规格。

此外,需要注意的是,伊娜耦合专用电容虽然具有很多优点,但在使用过程中也需要注意一些事项,例如避免过度加热、避免过度电压等,以保证其正常工作和稳定性。

总之,伊娜耦合专用电容是一种重要的电子元件,具有广泛的应用和重要的作用。

在使用时,需要根据具体的要求和场景选择合适的型号和规格,并注意一些使用事项,以保证其正常工作和稳定性。

耦合电容【标题:深入解析耦合电容】耦合电容,这一术语对于非电子专业的朋友来说,可能十分陌生。

然而,在电子电路、通信设备、计算机等领域,耦合电容却有着不可替代的地位。

首先,我们引入一个概念,也就是“耦合”。

“耦合”一词在物理学中,是指两个或两个以上的物频振荡过程在一定条件下,由于存在相互作用或某种联系而使得这些振荡过程之间存在相互影响。

在物理学、电子电路、化学等领域都有着广泛的应用。

那么,何谓耦合电容呢?简单来说,耦合电容是一种特殊的电容,它主要用于将输入信号从一个电路部分传输到另一个电路部分,同时阻止直流成分继续通过的过程。

耦合电容承担着电信号的传输功能,而且能够阻止直流信号,只让交流信号通过,这种特性决定了耦合电容在电子电路中的重要地位。

其实,能做到这一点的就是电容本身的特性,电容对直流是开路的,而对交流是通路的。

只不过我们在电路中,将电容这个元件用于连接两个电路部分,起到耦合作用的时候,我们就称之为耦合电容。

接下来我们再简单说说耦合电容的工作原理。

在两个通过耦合电容连接在一起的电路部分中,当一个部分产生交流信号时,由于电容对交流通路的特性,此时的耦合电容可以很好地将这个交流信号导入另一个电路部分。

当导入的是直流信号时,由于电容对直流开路的特点,通过耦合电容的直流信号就会被阻断,这样就实现了只通交流,不通直流的效果。

耦合电容在我们平日使用的电子产品中占据了重要的位置。

在电视,音响,计算机等家用电器中,以及火箭,卫星,雷达等高新科技设备中,都离不开耦合电容的使用。

比如,在电视中,图像信号和声音信号是分开传输的,它们需要通过耦合电容来进行联接,以实现声像同步的效果。

耦合电容的选用也需要充分考虑到不同电器的需要。

如选择耦合电容,主要考虑电流频率、工作电压、容量大小、泄漏电流大小、零件可靠性等因素。

只有充分对这些因素进行考虑和把握,才能选出真正适合的耦合电容,使其在电路中起到最好的作用。

当然,任何东西都有其两面性,耦合电容在起到其正面作用的同时,也存在一定的问题和局限性,比如电容的大小不能过大或过小,过大会导致电路启动和关闭的时间过长,过小则容易出现失真,并且电容还有寿命问题,因此选用电容时应充分考虑其性能和实际应用需求。

伊娜耦合电容伊娜耦合电容是电子电路中常见的一种耦合方式,它通过电容器将两个电路的信号进行耦合。

本文将对伊娜耦合电容的原理和应用进行详细介绍。

一、伊娜耦合电容的原理伊娜耦合电容是以伊娜电路为基础的一种电路耦合方式。

伊娜电路是一种差分放大电路,它由两个相同的放大器组成,通过一个共模信号输入端和两个差分信号输入端来实现放大器的工作。

而伊娜耦合电容是在伊娜电路的基础上加入了一个电容器,用来实现两个电路之间的信号耦合。

伊娜耦合电容的原理如下:首先,在输入端,信号经过一个电阻分成两个信号,一个经过一个电容器输入到一个放大器,另一个经过另一个电容器输入到另一个放大器。

然后,两个放大器将信号放大后再通过一个电容器输出到输出端。

这样,通过电容器的耦合,输入端的信号可以传递到输出端,实现了两个电路之间的信号耦合。

伊娜耦合电容在电子电路中有着广泛的应用。

下面将介绍它在几个典型电路中的应用。

1. 电路隔离伊娜耦合电容可以实现电路之间的隔离,防止干扰信号的传递。

在一些噪声较大的环境下,为了保证信号的纯净性,可以通过伊娜耦合电容将输入信号和输出信号隔离开,减少噪声对信号的影响。

2. 信号放大伊娜耦合电容可以实现信号的放大,提高信号的幅度。

在一些需要对信号进行放大的电路中,可以通过伊娜耦合电容将输入信号放大后再输出,增强信号的强度,提高电路的灵敏度。

3. 信号匹配伊娜耦合电容可以实现信号的匹配,使得输入端和输出端的电阻、容抗等参数相互匹配,提高电路的适配性。

在一些需要将信号从一个电路传递到另一个电路的应用中,通过伊娜耦合电容可以实现输入端和输出端的参数匹配,确保信号的传递效果。

4. 信号滤波伊娜耦合电容可以实现对信号的滤波,去除掉噪声信号和干扰信号。

在一些需要对输入信号进行滤波处理的电路中,可以通过伊娜耦合电容将输入信号经过滤波器滤波后再输出,去除掉不需要的信号成分,提高信号的纯净度。

三、总结伊娜耦合电容是一种常见的电路耦合方式,通过电容器实现两个电路之间的信号耦合。

阻容耦合放大电路中,耦合电容的作用嘿,咱来聊聊阻容耦合放大电路里耦合电容那点事儿。

这耦合电容啊,就像是电路里的“快递员”。

你想啊,在阻容耦合放大电路这个大社区里,不同的放大级就像是住在不同楼里的住户。

而耦合电容呢,它负责把前一级的信号这个“包裹”准确无误地送到下一级去,而且还得保证包裹完好无损呢,要是没有它,这信号可就被困在前一级,没办法继续在电路里“旅游”啦。

它又像是一个神奇的“信号桥梁”。

你看啊,放大电路的各级就像被河流隔开的小岛,而耦合电容就是那横跨河流的桥梁。

信号这个调皮的小生物,就靠着这座桥,从一个小岛(一级放大电路)蹦跶到另一个小岛(下一级放大电路),要是没这座桥,信号就只能在自己的小岛上干瞪眼,哪也去不了。

耦合电容还像一个超级有原则的“信号筛选员”。

它只允许交流信号这个“时尚潮流”通过,对于直流信号这个“老古董”,那是坚决不让过的。

就好比在一个超级炫酷的派对门口,只有穿着时尚的交流信号才能进去嗨,而穿着古板的直流信号只能被拒之门外,这可真是把交流信号和直流信号分得清清楚楚,明明白白。

它简直就是电路中的“和平使者”。

在阻容耦合放大电路里,各级放大电路的工作点就像一个个小王国,它们都有自己的脾气和要求。

耦合电容呢,就防止了各级工作点这个“小王国”之间互相干扰,就像一个和平使者在中间斡旋,让每个小王国都能安心地做自己的事情,不会因为隔壁小王国的事情而乱了阵脚。

这个耦合电容呀,还是一个“信号保镖”。

在信号从一级传送到下一级的过程中,周围可能有各种各样的“干扰小怪兽”,比如噪声之类的。

耦合电容就像一个强壮的保镖,护送着信号这个“小明星”安全地到达下一级,把那些干扰小怪兽都挡在外面,确保信号的纯净性。

它又像是一个电路里的“信号翻译官”。

你知道的,前一级输出的信号和下一级需要的信号可能在某些方面不太一样,就像两种不同的语言。

耦合电容就负责把前一级的信号“翻译”成下一级能读懂的形式,这样下一级电路才能顺利地接收并处理这个信号,这“翻译”工作做得那叫一个专业。

一种新型小型化交叉耦合带通滤波器的设计马润波;闫建国;陈新伟;闫丽云;韩丽萍【摘要】本文设计了一种基于阶跃阻抗谐振器的新型嵌入式交叉耦合带通滤波器.为使滤波器小型化,设计了两种紧凑型阶跃阻抗谐振器结构.通过研究和改善谐振器间的耦合机制,可使两种谐振器不仅形成嵌入式结构,而且缩减了馈线占据的面积,进一步减小了含馈线在内整个带通滤波器的尺寸.为验证此方法的可行性,利用滤波器综合法设计了一个中心频率为2.4 GHz,相对带宽FBW为15%的4阶交叉耦合带通滤波器,其最终设计尺寸为28 mm×20 mm(0.37 λg×0.26 λg,λg为中心频率所对应的导波波长).对该滤波器进行了仿真、加工和测试,结果表明该滤波器具有所需的广义切比雪夫特性,且互相吻合得很好.【期刊名称】《测试技术学报》【年(卷),期】2016(030)001【总页数】5页(P69-73)【关键词】阶跃阻抗谐振器;交叉耦合;带通滤波器;传输零点;小型化【作者】马润波;闫建国;陈新伟;闫丽云;韩丽萍【作者单位】山西大学物理电子工程学院,山西太原030006;山西大学物理电子工程学院,山西太原030006;山西大学物理电子工程学院,山西太原030006;山西大学物理电子工程学院,山西太原030006;山西大学物理电子工程学院,山西太原030006【正文语种】中文【中图分类】TN713+.5针对微波通信系统中小型化和高性能滤波器的设计,众多研究者提出了各种有效的方法和结构,其中平面结构滤波器由于具有结构紧凑、易于加工的特点而被广泛应用. 谐振器作为滤波器中的基本单元,对滤波器的尺寸和性能有直接影响. 例如,采用开路半波长平行耦合线作为谐振器是常见的滤波器设计方法,为克服其尺寸过大的缺陷[1],经常将平行耦合线弯折,形成发夹型谐振器以减小尺寸是许多设计采用的方法[2]. 此外, Makimoto等学者提出了阶跃阻抗谐振器(SIR),可以明显减小谐振器尺寸,同时还能够灵活控制第一杂散频率[3]. 文献[4]采用了改进的发夹型SIR,而且谐振器末端的耦合线部分相当于加载了一个电容,实现了进一步减小谐振器尺寸的目的.除谐振器外,滤波器的拓扑结构是影响其尺寸和性能的重要因素. 与传统的巴特沃兹和切比雪夫响应型滤波器相比,广义切比雪夫响应滤波器通过在边带和阻带内引入传输零点的方法来提高滤波器的选择性和带外抑制特性,由Cameron等学者逐渐完善了对应的广义耦合矩阵综合方法[5],并出现了众多的交叉耦合滤波器设计方法[6-8]. 结合谐振器结构和交叉耦合设计方法,文献[9]设计了一种嵌入式的交叉耦合拓扑结构,在较大程度上减小了滤波器的尺寸.为充分满足现代通信系统对微波器件小型化越来越高的需求,本文基于发夹型阶跃阻抗谐振器和一种新颖的弯折小型化阶跃阻抗谐振器,采用嵌入式的交叉耦合拓扑结构,设计了一个中心频率为2.4 GHz,相对带宽为15%的小型化四阶交叉耦合带通滤波器,并经仿真、加工和测试验证了其性能.本文设计的带通滤波器采用了Rogers RO 4350介质基板,其相对介电常数εr=3.48,基板厚度h=0.762 mm,包含上下两层金属,下层金属为地层,上层金属为谐振器层. 图 1 给出了谐振器层所包含的4个谐振器及馈线结构.由于谐振器大小决定着滤波器的整体尺寸,本文设计了两种基于半波长SIR的小型化结构,分别对应图1中类似发夹型的谐振器1与4以及充分弯折的谐振器2和3. 在结构的具体设计中,首先考虑了以下几种方法来减小谐振器尺寸:1) 两种谐振器都采用了阶跃阻抗结构,可以减小谐振器的电长度. 考虑到后面设计的滤波器实际工作于2.4 GHz,并设定两种半波长SIR的阻抗比分别为0.81和0.88,则根据文献[10]提到的SIR特性,可得两种谐振器的物理长度均大约为31 mm;2) 对SIR谐振器进行结构弯折可以充分利用有效面积. 在谐振器总长度不变的情况下,结合CST三维电磁仿真软件,经优化和微调最终确定图1中各谐振器及50 Ω馈线的结构参数分别为:h1=10.6 mm,h2=12.72 mm,h3=1.4 mm,h4=1 mm,h5=1 mm,h6=1.4 mm,w1=0.9 mm,w2=1.14 mm,w3=0.5 mm,w4=0.8 mm,w5=1.73 mm,w6=0.4 mm,l1=4.5 mm,l2=1.5 mm,l3=9.5 mm,l4=1.5 mm,l5=5.5 mm,l6=0.3 mm,l7=0.6 mm,l8=3.45 mm;3) 谐振器2和3中间的平行耦合线间距为g,且靠近谐振器开路端具有明显的电容效应,等效为在谐振器开路端加载电容[4],相当于增加了谐振器有效电长度,减小了物理尺寸. 在保持谐振器2和3金属总长度不变的情况下,图 2 给出了其谐振频率f随间距g的变化曲线. 可以看出,f随g的减小逐渐减小,这有利于谐振器2和3的小型化. 此处选择g=0.72 mm以实现2.4 GHz谐振.此外,在图 1 所示滤波器结构中的谐振器1与4的开路端具有较强的电场分布,它们相互之间经缝隙s14可以实现电耦合;而谐振器2和3的相邻部分具有强电流分布特点,经其间缝隙s23可实现磁耦合. 一般来讲,在利用综合法设计滤波器的过程中,电耦合系数要远小于磁耦合系数和混合耦合系数. 为了得到较小的耦合系数,就需要加大电容耦合两谐振器间的距离,从而增大滤波器的尺寸,不利于小型化. 而本文设计的谐振器1和4之间的耦合面积较小,所以很小的缝隙s14即可满足较小电耦合系数的要求.通过上述方法,谐振器2与3具有很小的尺寸,可以分别被嵌入到谐振器1和4内部. 这不仅能够充分减小整个滤波器的尺寸,而且便于实现各谐振器间的耦合.此处谐振器1与2之间、 3与4之间则通过缝隙s12实现混合电磁耦合. 与传统交叉耦合拓扑结构相比,嵌入式结构的尺寸减小约50%.更进一步,得益于尺寸非常小的谐振器2、 3,发夹型谐振器1、 4即使在分别嵌入它们之后,内部仍然具有很大空隙(如图1虚线所示). 因此,可以将谐振器1、4的中部宽度为w3的传输线向内弯折,一方面实现了空间的充分利用,另一方面可以将馈线向结构内侧牵引,这实现了对含馈线在内整个带通滤波器的充分小型化. 值得一提的是,虽然此时谐振器1的宽度为w3的传输线,与谐振器2的开路端的间距变得较近,但由于它们附近分别呈现出强磁场和强电场的特性,相互之间的耦合很小,因此谐振器1与2之间主要还是通过缝隙s12实现混合电磁耦合,谐振器3与4之间也一样. 由此可见,各谐振器间的耦合可以通过不同的缝隙独立调节,这能够减少设计的复杂性. 此外,由于谐振器1、 4向内弯折,馈电点的位置可以在不改变电路尺寸的情况下进行大范围灵活调节,这使得外品质因数Qe具有较大的可调范围,能够满足不同带宽滤波器的设计需求.本文预设交叉耦合带通滤波器的中心频率为2.4 GHz,相对带宽为15%,以此为指标按图 3 所示拓扑结构设计4阶广义切比雪夫响应滤波器,并具体由图 1 所示滤波器结构来实现. 由文献[11]可得对应的低通原型中各元件值:g1=0.959 7,g2=1.421 9,J1=-0.210 8,J2=1.117 7. 由此计算出满足该指标滤波器所需的耦合系数及外品质因数分别为耦合系数是直接影响滤波器指标及性能的重要参数. 在交叉耦合带通滤波器的设计中,为了实现传输零点,需同时满足3种类型的耦合,即电耦合、磁耦合及混合耦合. 根据文献[11],利用弱耦合法提取谐振器间的耦合系数,若得到的特征频率分别为fa和fb,则可由此计算出图 4 是耦合系数Mij的绝对值(i,j分别代表谐振器编号,其中电耦合系数M14为负值)随对应两谐振器间距离sij的变化曲线. 可以看出,随着谐振器间的距离变大,耦合系数的绝对值逐渐减小.除耦合系数外,滤波器设计过程中另一个关键参数为外品质因数. 外品质因数的提取可利用图 5 所示拓扑结构完成,从而确定抽头的位置t. 由文献[11]可知式中:f0为谐振器的谐振频率;为反射系数s11的相位响应曲线上,相对中心频率处相位偏移±π/2 所对应频率点间的带宽. 利用上述方法可得到外品质因数Qe随t的变化曲线,具体见图 6.t值越小,抽头线越靠近谐振器的虚地位置,耦合就越弱,外品质因数Qe就越大.根据图 4 和图 6 中的曲线,可最终确定谐振器间的间距分别为s12=0.27 mm,s23=0.327 mm,s14=0.28 mm;抽头的位置t=5.22 mm.为了检验本文设计交叉耦合带通滤波器的性能,我们对综合设计出的滤波器进行了仿真、加工和测试. 图 7 为所加工的滤波器实物图,其尺寸为28 mm × 20 mm (0.37λg×0.26λg).使用矢量网络分析仪Agilent N5230A对加工滤波器的S参数进行了测量. 图 8 给出了该滤波器的仿真与测试结果的S参数曲线. 从图中可以看出仿真中心频率位于2.4 GHz处, -3 dB的通频带范围为: 2 207 MHz~2 576 MHz,相对带宽约为15.4%. 通带内的反射系数小于-14 dB,插入损耗为 0.8 dB. 测试的中心频率位于2.37 GHz处, -3 dB通频带范围为: 2 205 MHz~2 545 MHz,相对带宽约为14.5%. 通带内的反射系数小于-10 dB,插入损耗约为1.5 dB. 通带较为平坦,在2.09 GHz和 2.71 GHz 处分别有一个传输零点,从而使边缘变得更加陡峭,提高了滤波器的边缘选择特性,而带外抑制优于25 dB,这表明该滤波器具有良好的通带和阻带特性.表 1 为本文设计的滤波器与文献中设计的滤波器在尺寸及性能方面的对比,其中λg为各滤波器中心频率对应的导波波长. 可见,本文所设计滤波器在具有较小尺寸的条件下,仍然保持了较低的插入损耗,这反映了该滤波器能够满足小型化和高性能的要求,本文提出的滤波器结构具有较小的尺寸和较低的插入损耗.本文利用滤波器综合法设计了一个中心频率为2.4 GHz,相对带宽FBW为15%的小型化4阶平面交叉耦合带通滤波器. 为使滤波器小型化,设计了两种紧凑型阶跃阻抗谐振器结构. 通过研究和改善谐振器间的耦合机制,两种谐振器不仅可实现嵌入式结构,而且能把馈线向结构内侧牵引,进一步实现了含馈线在内整个带通滤波器的小型化. 滤波器最终尺寸为28 mm×20 mm(0.37λg× 0.26λg),且具有结构简单,易于加工的特点. 对该滤波器进行加工测试,实测结果和仿真结果基本吻合,结果表明该设计具有较低插入损耗及良好的边缘选择性和带外抑制特性,能够满足现代通信系统对小型化高性能滤波器的要求.【相关文献】[1] Cohn S B. Parallel-coupled transmission-line-resonator filters[J]. IRE Trans. Microwave Theory Tech., 1958, 6(2): 223-231.[2] Cristal E G, Frankel S. Hairpin-line and hybrid hairpinline/half-wave parallel-coupled-line filters[J]. IEEE Trans. Microwave Theory Tech., 1972, 20(11): 719-728.[3] Makimoto M, Yamashita S. Bandpass filters using parallel coupled strip-line stepped impedance resonators[C]. Microwave symposium Digest, 1980 IEEE MTT-S International, Washington: IEEE, 1980: 141-143.[4] Sagawa M, Takahashi K, Makimoto M. Miniaturized hairpin resonator filters and their application to receiver front-end MIC’s[J]. IEEE Trans. Microwave Theory Tech., 1989,37(12): 1991-1997.[5] Cameron R. General coupling matrix synthesis methods for chebyshev filtering functions[J]. IEEE Trans. Microwave Theory Tech., 1999, 47(4): 433-442.[6] Tsai L C. Design of bandpass filters using miniaturized stepped-impedance resonators[C]. Wireless Communications, Networking and Mobile Computing (WiCOM),2011 7th International Conference, Harbin :IEEE, 2011: 1-4.[7] Nedelchev M. Design of microstrip meander-folded hairpin resonator filters[C]. Microwave Techniques (COMITE), Pardubice: IEEE, 2013: 69-72.[8] Deng Pu Hua, Tsai J T. Design of microstrip cross-coupled bandpass filter with multiple independent designable transmission zeros using branch-line resonators[J]. Microwave and Wireless Components Letters, IEEE, 2013, 23(5): 249-251.[9] Chaimool S, Akkaraekthalinl P. Resonator-embedded four-pole cross-coupled dual-band microstrip bandpass filters[C]. Communications and Information Technologies, 2006. ISCIT '06. International Symposium, Bangkok: IEEE, 2006: 1076-1079.[10] Sagawa M, Makimoto M, Yamashita S. Geometrical structures and fundamental characteristics of microwave stepped-impedance resonators[J]. IEEE Trans. Microw. Theory Tech., 1997, 45(7): 1078-1085.[11] Hong Jia Sheng, Lancaster M J. Microstrip filters for RF/microwave applications[M]. 1st, New York: Wiley, 2001: 235-319.[12] Li Jiankang, Chen Chunhong, Wu Wen. Design of dual-passband cross-coupled filter using stub-loaded open-loop resonators[C]. Microwave Conference, 2009. APMC 2009. Asia Pacific, Singapore: IEEE, 2009: 929-932.[13] Chang K F, Tam K W. Miniaturized cross-coupled filter with second and third spurious responses suppression[J]. Microwave and Wireless Components Letters, IEEE, 2005, 15(2): 122-124.。

收稿日期:2005206206; 定稿日期:2005208219基金项目:国家重点基础研究发展(973)计划资助项目(G2000036508);国家自然科学基金资助项目(60236020);国家高技术研究发展(863)计划资助项目一种应用于超宽带系统的宽带L NA 的设计桑泽华,李永明(清华大学微电子学研究所,北京 100084)摘 要: 结合切比雪夫滤波器,可以实现宽带输入匹配的特性和片上集成窄带低噪声放大器(L NA )的噪声优化方法。

提出一套完整的基于CMOS 工艺的宽带L NA 的设计流程,并设计了一个应用于超宽带(U WB )系统的3~5GHz 宽带LNA 电路。

模拟结果验证了设计流程的正确性。

该电路采用SM IC 0.18μm CMOS 工艺进行模拟仿真。

结果表明,该L NA 带宽为3~5GHz ,功率增益为5.6dB ,带内增益波动1.2dB ,带内噪声系数为3.3~4.3dB ,IIP3为-0.5dBm ;在1.8V 电源电压下,主体电路电流消耗只有9mA ,跟随器电流消耗2mA ,可以驱动1.2p F 容性负载。

关键词: 低噪声放大器;切比雪夫滤波器;超宽带;无线局域网中图分类号: TN722.3 文献标识码: A 文章编号:100423365(2006)0120114204A Wideband Low Noise Amplif ier for U ltra WideB and SystemSAN G Ze 2hua ,L I Y ong 2ming(I nstit ute of Microelect ronics ,Tsinghua Uni versit y ,B ei j ing 100084,P.R.China )Abstract : A new design flow is presented by combining the wideband match network theory with the low noise design technique for integrated narrowband low noise amplifier (L NA ).As a demonstration ,a wideband L NA is de 2signed based on this design flow ,which is validated by simulation using SMIC ’s 0.18μm technology.Results from the simulation show that the L NA circuit has achieved an operating f requency ranging f rom 3GHz to 5GHz ,a pow 2er gain between 4.4dB and 5.6dB ,a noise figure f rom 3.3dB to 4.3dB and an IIP3of -0.5dBm.The circuit dis 2sipates 11mA current f rom a single 1.8V power supply ,and it is capable of driving 1.2p F capacitive load.K ey w ords : Low noise amplifier ;Chebyshev filter ;Ultra wide band ;WL AN EEACC : 1220 1 引 言IEEE 802.15.3是一种无线个人域网(WPAN ,Wireless Personal Area Network )标准,包含MAC和P H Y 两部分。

交叉耦合mos管

交叉耦合(Cross-coupling)是一种设计技术,在此技术中,

多个金属氧化物半导体场效应管(Metal-Oxide-Semiconductor Field-Effect Transistors,MOSFETs)的栅极或漏极通过电容耦

合来相互连接。

交叉耦合mos管可以在集成电路设计中实现

各种功能,如放大、逻辑运算和存储。

交叉耦合mos管的栅极与漏极之间通过电容相连,可以实现

信号传输和增强。

通过控制栅极电压,可以调节通道电流的大小,从而实现信号放大。

此外,由于交叉耦合mos管之间的

电容连接,可以在不同的mos管之间传递信号,从而实现逻

辑运算和存储。

交叉耦合mos管可以用于各种电路设计中,如放大器、开关、多路选择器和存储器。

通过调节栅极电压和选择信号的输入方式,可以实现不同的功能。

然而,交叉耦合mos管也存在一些问题。

例如,由于栅极与

漏极之间的电容连接,可能会导致信号的串扰和噪声。

此外,交叉耦合mos管的设计通常比较复杂,需要考虑到信号的传

输和处理。

因此,在集成电路设计中,需要进行仔细的优化和布线规划,以确保电路的性能和稳定性。

总的来说,交叉耦合mos管是一种重要的设计技术,可以实

现多种电路功能。

在实际应用中,需要综合考虑性能、噪声和布线等因素,以实现高质量的集成电路设计。

耦合电容elect耦合电容(Coupling Capacitor)是一种用于传输信号的电子元件。

它的主要作用是在不同电路之间传递信号,同时阻隔直流信号,使交流信号得以传输。

耦合电容在电子设备中起到了举足轻重的作用。

耦合电容的工作原理是基于其特殊的电容性质。

电容是指在两个导体之间存在一种储存电荷的能力。

而耦合电容则是通过两个电路之间的电容连接,将信号从一个电路传递到另一个电路中。

在电子设备中,不同电路之间常常需要传输信号。

然而,不同电路之间的电位差可能会导致信号传输的困难。

这时,耦合电容就派上了用场。

耦合电容将两个电路之间的信号隔离开来,只传递交流信号,同时阻隔直流信号。

这样,信号就可以在不同电路之间流动,而不会受到电位差的干扰。

耦合电容的容值对信号传输起着重要的影响。

容值过小会导致信号传输的损失,容值过大则会导致信号失真。

因此,选择合适的耦合电容容值对于信号传输的质量至关重要。

在实际应用中,耦合电容有许多不同的类型,如电解电容、陶瓷电容、有机电容等。

不同类型的耦合电容在容值、频率响应、尺寸、成本等方面有所差异,可以根据具体的应用需求选择合适的类型。

耦合电容的使用范围广泛。

在音频设备中,耦合电容被用于传输音频信号,保证音质的清晰和纯净。

在射频设备中,耦合电容则被用于传输无线信号,确保信号的稳定和可靠。

在通信设备中,耦合电容起到了连接不同电路的桥梁作用,实现信号的传递和交流。

除了在电子设备中的应用,耦合电容在电力系统中也有重要的作用。

在高压线路中,耦合电容用于传输电力信号,实现对电力系统的监控和控制。

耦合电容的稳定性和可靠性对于电力系统的运行至关重要。

耦合电容是一种重要的电子元件,用于不同电路之间的信号传递。

它在音频设备、射频设备、通信设备以及电力系统中都有广泛的应用。

通过选择合适的耦合电容类型和容值,可以实现信号的稳定传输和良好的音质效果。

耦合电容的发展和应用将进一步推动电子技术的发展,为我们的生活带来更多的便利和舒适。

基于双交叉耦合电容反馈的超低功耗高线性LNA李相敏;康壮【摘要】提出了一种基于双交叉耦合电容反馈技术的CMOS共栅低噪声放大器(LNA).第一个反馈环路利用交叉耦合技术以提高电路跨导;另一个反馈环路在晶体管的源漏两级之间采用交叉耦合共栅技术实现电压电流反馈.提出的LNA在低功耗的前提下取得了优越的性能,基于0.18 μmCMOS工艺,对该LNA流片实现并测试.测试结果表明LNA芯片在2.4 GHz频率下的增益为18 dB,噪声系数为2.02 dB,输入三阶截止点IIP3为8.3 dBm,输入匹配参数S11和输出匹配参数S22均低于-10 dB,在1.1V电压供电下功耗为2.5 mW.【期刊名称】《中国电子科学研究院学报》【年(卷),期】2018(013)003【总页数】5页(P326-330)【关键词】输入三阶截止点;高线性;低噪声放大器;负反馈【作者】李相敏;康壮【作者单位】长江大学文理学院,湖北荆州 434020;长江大学文理学院,湖北荆州434020【正文语种】中文【中图分类】TN4320 引言反馈的基本作用是利用反馈路径上的线性有源器件,来纠正电路正向路径上的非线性有源器件产生的非线性。

反馈是模拟和射频电路中的一种提高线性度的有效方法,然而,在射频领域,反馈可能引起谐波反馈分量,恶化电路的线性度。

在低频领域,谐波反馈分量通常被高环路增益所抑制,然而,在射频领域,由于开环增益已经很低,较难取得高环路增益。

例如,在共源电路结构中,采用源极退化电感实现的电压电流反馈技术,并不能提高输入三阶截止点IIP3性能,这是因为源极退化电感在放大晶体管的源端产生二次谐波分量,通过晶体管栅源间电容反馈回输入端口,与原始信号相混合转换成三阶交调分量IMD3,退化了电路的IIP3[1-5],在许多射频反馈电路中都存在此类现象[6-7]。

在本文中,首先在线性度改善方面讨论了射频反馈技术,并且提出在全差分共栅放大器中采用双电容反馈技术。

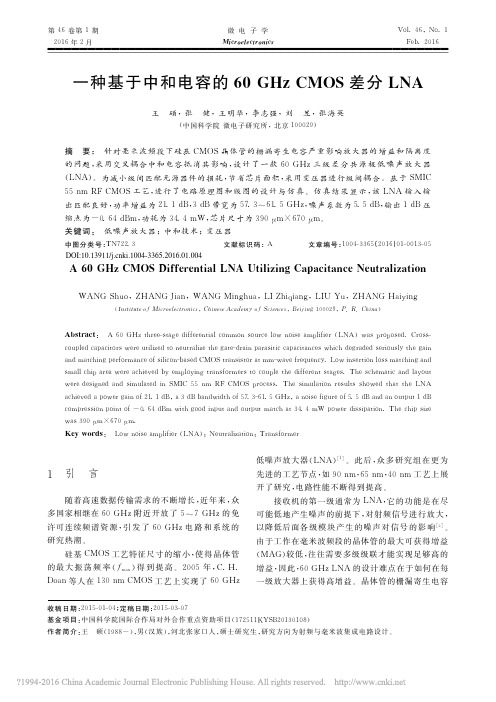

Using Capacitive Cross-Coupling Technique in RF Low Noise Amplifiers and Down-Conversion Mixer DesignWei Zhuo, Sherif Embabi, *José Pineda de Gyvez, Edgar Sánchez-Sinencio Analog Mixed-Signal Center, Texas A&M University, College Station, Texas, U. S. A.* Philips Research Laboratories, Eindhoven, The Netherlands.AbstractWe report an approach to improve the noise performance of RF low noise amplifiers (LNAs) and down-conversion mixers. The technique we described here is based on capacitive cross-coupling across the two sides of a differential input stage. A LNA and mixer have been implemented in 0.5µ CMOS process to demonstrate the viability of this technique. The measurements show that the LNA achieves 3.0dB noise figure and 12.2 dB voltage gain (optimized for the maximum power transfer), and the mixer has 5.2dB DSB noise figure and 13.2 dB voltage conversion gain. Both LNA and mixer operate at 2.7V voltage supply and consume 27mW and 8.1mW power, respectively.1.IntroductionGrowth of the wireless communication market puts increasing demand on low power, low cost and high performance receivers. RF LNAs and mixers are among the most critical building blocks in the receiver chain. The CMOS technology has shown its feasibility for high frequency applications [1-2].This paper describes how a capacitive cross-coupling (CCC) technique can be used for RF amplifiers and mixers to improve the performance. Section II discusses a capacitive cross-coupling (CCC) technique. Section III presents the LNA implementation using the CCC technique. Details of mixer implementation using CCC are described in Section IV. Experimental results are shown in Section V, followed by conclusions in Section VI.2. Capacitive cross-coupling technique for noise reductionCommon gate and common source input stages are structures widely seen in the LNA design. The main drawback of common-gate amplifiers is their relatively high noise figure. Ignoring the noise contribution due to the load, a common-gate LNA has a minimum NF [1]:γ+=1F(1)Where, γ represents the channel thermal noise coefficient. It is usually difficult for common-gate LNAs to provide a NF well below 3dB. A Common source input stage offers the possibility to achieve the best noise performance by increasing their input quality factor Q. However, it degrades the linearity and increases the sensitivity of the input matching. Common-gate amplifiers can be more easily matched and usually exhibit better linearity than common-source amplifiers.F ig.1 Capacit iv e cross-coupl ing t e ch niq ueThe capacitive cross-coupling (CCC) has been used for gain enhancement and matching [3]. In this section, we will demonstrate how the CCC can be used to improve the NF of a common-gate input stage. Fig.1 shows the schematic of a differential common-gate input stage with CCC. It can be shown that the cross-couplingcauses the noise of M1 and M2, namely21nv and 22nv, to produce common-mode noise voltages at the output node d1 and d2. Intuitively, This can be explained as follows. Let’s assume the following instantaneous polarity fornoise source 21nv; positive polarity at the gate terminal of input transistor M1 and negative at the other side (polarity can be exchanged as well). One can easily see that the drain voltage of M1 will decrease due to the positive disturbance at the gate terminal. On the other hand, because of the negative disturbance at S2, the drain voltage of M2 will also decrease. Hence, the input noise source 21nv causes a common-mode voltage at d1 and d2. Similar analysis can be applied to the inputnoise source 22nv.A more rigorous small signal noise analysis was used for a mathematical derivation. Here, only channelthermal noise source is considered, and other noise mechanisms are neglected for simplicity. The cross-coupling capacitors C 1 and C 2 are assumed to be much greater than gate-source capacitance C gs . The derived noise factor expression of the input pair M 1 and M 2 is given by :21γ+=F (2)It can be seen that due to the capacitive cross-coupling the noise contribution from the input transistors is reduced though not completely eliminated.Worthy to mention is that the derivation of the noise factor assumes that the input impedance is matched to the source impedance for maximum power transfer.Matching for the optimal noise performance can reduce the NF value. This can be demonstrated by changing the effective input impedance (1/2×g m ). Fig. 2 illustrates the change of the NF vs. the effective transconductance (2×g m ). The noise performance will be improved as the transconductance is increased. Another advantage of the common gate input stage with CCC is that the input effective transconductance is doubled due to the capacitive cross-coupling. Thus, the current consumption can be reduced. Finally, it is also interesting to note that the capacitive cross-coupling does not add much cost and complexity.F ig. 2 NF of t h e input pair w it hCCC v s. 2g m3. LNA Implementation using the CCC TechniqueThe full schematic of a LNA employing the CCC technique is depicted in Fig.3. The input impedance matching is achieved by sizing and adjusting the bias current of the input transistors M 1 and M 2 such that 1/(2×g m )=50Ω. The cross-coupling capacitors C 1 and C 2are 10pF poly-to-poly capacitors in our implementation.Off-chip inductors L 1 and L 2 are used to resonate with the gate-source capacitor C gs and the input parasitic capacitance at the frequency of interest. Cascode transistors M 3 and M 4 are added to improve the reverseisolation of the LNA. Transistors M 5, M 6, M 7, and M 8are used to realize large resistors to isolate the signal path from the biasing circuitry. The LNA’s load is a 300Ω resistance (assuming an on-chip mixer).F ig. 3 Sch e m at ic of t h e L N A w it hCCC As pointed out in the previous section, the LNA with CCC provides noise advantage over the conventional differential common-gate LNA. However, the dynamic range of a circuit is not only determined by the noise butalso by the linearity. Assuming that the transconductance g m is the only source which causes nonlinearity, the input referred IP3s of the conventional differential common-gate LNA and the LNA with CCC are derived using volterra series. The derived expressions are given in (3)and (4), respectively.)/(3283223s gm gm sG K K G IP +−⋅⋅=(3)gms K G IP 3343⋅=(4)Equations (3) and (4) are simplified expressions evaluated under input matching conditions. The parameters K 2gm and K 3gm are the second-order and third-order transconductance nonlinear coefficients. G s is the source conductance. It is observed that the IP3 of the conventional differential common-gate LNA is not only determined by the third-order nonlinear coefficient but also by the second-order nonlinear coefficient. The IP3of the LNA with CCC is only influenced by the third-order nonlinear coefficient. For a first-order analysis, we may consider the MOSFET transistor to be a square-law device. This means that the third-order nonlinear coefficient is usually much smaller than the second-order one. Thus, the IP3 of the LNA with CCC is higher than that of the conventional differential common-gate LNA.Although the second-order intercept point (IP2) is not important in a heterodyne receiver, it is a limiting factor in a direct conversion receiver. The IP2 of a differential circuit is usually limited by mismatch between differential path. Assuming that only transconductance(g m ) has mismatch (∆g m ) and applying the same procedure for the IP3 modeling, the input-referred IP2s of both LNAs are given by (5) and (6), respectively.mgm sgK G IP ∆⋅⋅≈223162(5)∞≈2IP (6)Due to mismatch, the conventional differential common-gate LNA shows a finite IP2, while the mismatch effect is minimal on the IP2 of the LNA with CCC.4. Mixer Implementation using the CCC Technique F ig. 4 Sch e m at ic of t h e m ixe r w it hCCC In the Gilbert cell mixer, the linearity is usually determined by RF transconductance. Thus, most of the design effort is spent attempting to find better ways of providing V-I conversion. One simple, but powerful technique consists of using degeneration resistors in the source of V-I converter. But, additional resistors will penalize the mixer noise performance, which may, in turn, increase design difficulties for the circuitry preceding it.The capacitive cross-coupling technique depicted in previous sections can be used in RF V-I converter to minimize the noise contribution and improve the linearity simultaneously. The proposed double-balanced Gilbert cell mixer with CCC is shown in Fig. 4.Transistors M 1 and M 2, cross-coupled by capacitors C 1and C 2, form a differential transconductance stage. The drain current of the M 1 and M 2 is steered through M 3 and M 4 or M 5 and M 6 to perform the mixing function. Output capacitors C 3 and C 4 combined with output resistance R 1and R 2 to form a low pass filter. The purpose of this filter is to attenuate high frequency components at the IF output. Biasing of the mixer is similar to that of the LNA.5. Experiment ResultsBoth LNA and mixer have been implemented in an AMI 0.5µ CMOS process. Measurements of the LNA show a 12.2dB voltage gain and a NF of 3.0dB at 900MHz. The 3.0dB NF, which seems higher than recently reported values, can best be explained by the fact that the LNA was designed for maximum power transfer and not optimized for the noise figure. One can achieve better noise performance by increasing the transconductance as illustrated in Fig. 2. The gain and NF of the LNA are plotted in Fig. 5 with frequency swept from 800M to 950M. The input-referred IP3 is extracted by applying two tones test. The power of both tones was swept while the resulting third-order intermodulation product was measured. Fig. 6 shows the fundamental tone and the third-order intermodulation product at 899.5MHz and 900MHz. Since output impedance of LNA is not 50Ω, “VdBm” is defined as voltage corresponding to a power level of 0dBm in a 50Ω system. Because source resistance is 50Ω, the input “VdBm” is same as original “dBm”.The measured mixer DSB noise and conversion gain are 5.2dB and 13.2dB, respectively. The measured NF is lower than most published mixer. The results of a two-tone measurement on the mixer are shown in Fig. 7. For the mixer measurement, the LO drive amplitude is equivalent to 300mV. Both LNA and mixer prototype are measured in TQFP package with ESD protection.The measured LNA and mixer results are summarized in Table.1 and Table.2 respectively. Microphotographs of both circuits are shown in Fig. 8.6. ConclusionIn this paper, we have shown how the capacitive cross-coupling technique can be used to improve the noise performance of a common-gate input stage. A LNA and mixer with CCC have been implemented in 0.5µ CMOS process to verify our theoretical findings.The LNA achieves around 3.0dB NF up to 900MHz, In addition, the LNA has significant +6.7dBm input-referred IP3 and only consume 20mW. The mixer has very low DSB NF at 5.2dB and +13.8dBm output IP3.Yet, both circuits do not rely on using on-chip spiral inductors.Reference[1] A. Rofougaran, J.Y-C.Chang, M. Rofougaran, A. A. Abidi,“A 1GHz CMOS RF front-end IC for a direct conversion wireless receiver ”, IEEE J. Solid-State Circuits , July 1996,vol. 31, pp. 880-889.[2] A. R. Shahani, D. K. Shaffer, and T. H. Lee, “A 12-mW Wide Dynamic Range CMOS Front-End for Portable GPS Receiver ”, IEEE J. Solid-State Circuits , Dec 1997, vol. 32, pp.2061-2069.[3] T. Cho et al, “A Single-Chip CMOS Direct-Conversion Transceiver for 900MHz Spread-Spectrum Digital Cordless Phones”, ISSCC Digest of Technical Papers , Feb 1999, pp.228-229.F ig. 5 M e asure d L N A gain and N F v s. f re q ue ncyF ig. 6 M e asure d L N A I P 3F ig. 7 M e asure d m ixe r t w o t one t e stT abl e .1 Sum m ary of L N A m e asure m e nt sFrequency 900MHz NF3.0dB Gain (voltage)12.2dB IP3 (input)+6.7dBm IP2 (input)+34dBm 1dB (input)-7dBm Power Supply 2.7V Power Consumption20mw Silicon area0.5×0.4mm 2T abl e .2 Sum m ary of m ixe r m e asure m e nt s RF Frequency900MHz LO Frequency 910MHz LO Amplitude 300mV NF (DSB) 5.2dB Gain (voltage)13.2dB IP3 (output)+13.8dBm IP2 (input)+25.6dBm Power Supply2.7V Power Consumption 8.1mw Silicon area0.7×0.5mm 2F ig. 8 M icroph ot ograph of t h eL N A and m ixe r。