新型实时时钟芯片DS12887原理与应用

- 格式:doc

- 大小:196.50 KB

- 文档页数:6

电子世界2005年7期47・・新型元器件DS12887是DALLAS半导体公司新推出的实时时钟芯片,可直接取代DS1287,它功能丰富,应用广泛。

它在工业控制及智能仪器仪表中有广泛用途,一般PC机内的时钟信号就是由DS12887提供的。

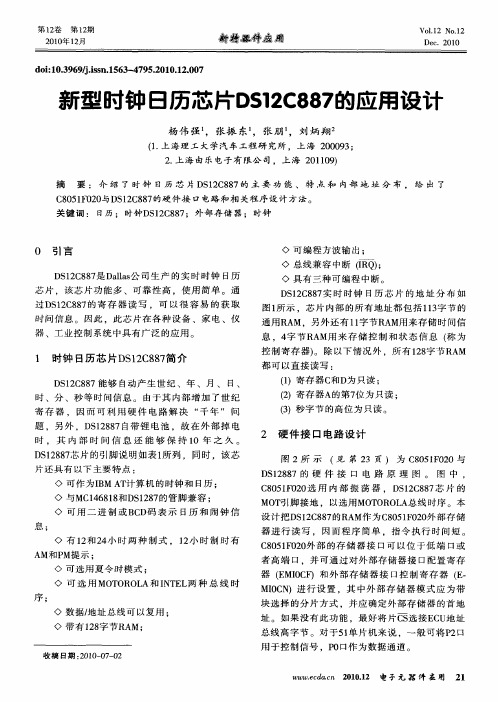

结构框图与特点DS12887的结构框图如图1所示。

DS12887的特点:(1)可作为个人计算机的时钟和日历;(2)与MCl46818B和DS1287的管脚兼容;(3)在没有外部电源的情况下可工作10年;(4)自带晶体振荡器及锂电池;(5)可计算到2100年前的秒、分、小时、星期、日、月、年七种日历信息并带闰年补偿;(6)有二进制码或BCD码代表日历和闹钟信息;(7)有12和24小时两种制式,12小时制时有AM和PM提示;(8)可选用夏令时模式;(9)可以应用于Motorola和Intel两种总线;(10)数据/地址总线复用;(11)内建128字节RAM;(12)14字节时钟控制寄存器;(13)114字节通用RAM;(14)可编程方波输出;(15)总线兼容中断(/IRQ);(16)三种可编程中断,时间性中断可产生每秒一次直到每天一次中断,周期性中断122 ̄500ms,时钟更新结束中断。

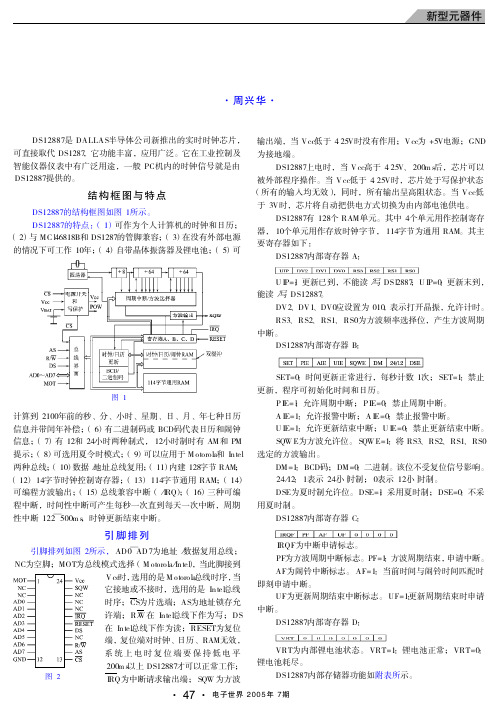

引脚排列引脚排列如图2所示,AD0 ̄AD7为地址/数据复用总线;NC为空脚;MOT为总线模式选择(Motorola/Intel),当此脚接到Vcc时,选用的是Motorola总线时序,当它接地或不接时,选用的是Intel总线时序;CS为片选端;AS为地址锁存允许端;R/W在Intel总线下作为写;DS在Intel总线下作为读;RESET为复位端,复位端对时钟、日历、RAM无效,系统上电时复位端要保持低电平200ms以上DS12887才可以正常工作;IRQ为中断请求输出端;SQW为方波输出端,当Vcc低于4.25V时没有作用;Vcc为+5V电源;GND为接地端。

DS12887上电时,当Vcc高于4.25V、200ms后,芯片可以被外部程序操作。

基于DS12887时钟芯片的时钟闹钟系统设计功能:使用DS12887作为时钟的发生和保持电路,DS12887内部集成晶振和电池,断电情况下可运行10年左右;同时其内部有128字节非易失性RAM,可以保持时钟和闹钟信息;主控电路为AT89S52,p1口用作4位一体数码管的动态显示,p0,p2口作为读写DS 12887总线,同时使用了/WR和/RD,p3.0的LED来实现每秒的闪烁,p3.1控制闹钟显示L ED,p2口虽用作地址总线,但只使用了p2.7连接至DS12887的/CS端,所以使用了p2.0作为蜂鸣器的控制口;p3.3(/INT1)作为DS12887闹钟报警的中断输入端口。

显示模式有:1,仅显示闹钟;2,仅显示分秒;3,一分钟之内先显示年份(只显示后两位),与星期同时显示,再显示月日,其余时间显示时分.调节按钮:P3.0,P3.1,P3.4,P3.5分别接4个按钮开关,分别定义为"A","T","H","M";按下"A","H" /"M",可分别调节闹钟的时分;按下"T","H"/"M",可分别调节时间的时分;时间的其他信息在该版本中不可以调节。

电路图:(/blog/eleclike/4744/photo.aspx);以下为源程序:RG_DLY EQU 2H;延时使用的工作寄存器RG_KEY EQU 30H;存储键盘值RG_KN EQU 33H;存储调节年月日星期的次数按钮。

RG_BT1 EQU 31H;需要显示的数据暂存RAMRG_BT2 EQU 32HBT_DSP BIT 00H;控制显示时间或闹钟的标志位BT_ALM BIT 01H;控制闹钟是否响铃的标志位BT_TM2 BIT 02H;控制显示时间的模式,1:只显示时分,0:还显示年月日,星期BT_MNSC BIT 03H;控制显示时间的分秒RG_TSC EQU 40H;时钟和闹钟暂存RAM,顺序同DS12C887中的RAMRG_ASC EQU 41HRG_TMN EQU 42H;RG_AMN EQU 43H;RG_THR EQU 44HRG_AHR EQU 45HRG_WK EQU 46HRG_DAY EQU 47HRG_MTH EQU 48HRG_YR EQU 49HRG_MS EQU 51HRG_IDL EQU 50HORG 0000HLJMP MAINORG 0013HLJMP SB_ALMORG 0030HMAIN: MOV SP,#60HSETB BT_DSPCLR BT_ALMCLR BT_TM2CLR BT_MNSCCLR IT1SETB EX1SETB IT0SETB EX0SETB EA ;开总中断MOV DPTR,#000BH;闹钟中断允许MOV A,#22HMOVX @DPTR,A;====--------------------最初写入DS12887的时候使用这一条指令。

DS12887时钟芯片及其在LED中的应用DS12887是美国达接斯半导体公司(Dallas)最新推出的串行接口实时时钟芯片,采用CMOS技术制成,具有内部晶振和时钟芯片备份锂电池,同时它与目前IBM AT计算机常用的时钟芯片MC146818B和DS1287管脚兼容,可直接替换。

它所提供的世纪字节在位置32h,世纪寄存器32h到2000年1月1日将从19递增到20。

采用DS12887芯片设计的时钟电路无需任何外围电路和器件,并具有良好的微机接口。

DS12887芯片具有微功耗,外围接口简单,精度高,工作稳定可靠等优点,可广泛用于各种需要较高精度的实时时钟系统中。

ITO芯片在LED中的应用为了提高LED芯片的出光效率,人们想了许多办法。

比如,当前市场上出现了许多亮度较高的ITO芯片的led,GaN基白光LED中如果用ITO替代Ni/Au作为P型电极芯片的亮度要比采用通用电极的芯片高20%-30%。

ITO是英文Indium Tin Oxides的缩写,意思是「氧化铟锡」。

与其它透明的半导体导电薄膜相比,ITO具有良好的化学稳定性和热稳定性。

对衬底具有良好的附着性和图形加工特性。

ITO为一种N型氧化物半导体,作为纳米铟锡金属氧化物,具有很好的导电性和透明性,可以切断对人体有害的电子辐射,紫外线及远红外线。

因此,喷涂在玻璃,塑料及电子显示屏上后,在增强导电性和透明性的同时切断对人体有害的电子辐射及紫外、红外。

ITO透明导电膜是平面显示器上重要之组件,其特性会与镀膜制程中的参数及材料有密切的关系。

在众多可作为透明电极的材料中,ITO(Indium Tin Oxide)是被最广泛应用的一种,ITO薄膜即铟锡氧化物半导体透明导电膜,通常有两个性能指针:电阻率和透光率。

主要是由于ITO可同时具有低电阻率及高光穿透率的特性,符合了导电性及透光性良好的要求。

在氧化物导电膜中,以掺Sn的In2O3(ITO)膜的透过率最高和导电性能最好,而且容易在酸液中蚀刻出细微的图形。

DS12887时钟芯片的应用:RTC时钟在很多系统中广泛的被应用,因为人们对于实时时钟要求越来越大,而很多数据的记录需要提供数据对应的时间等信息。

时钟芯片能在即使没有系统电源的情况下保持时间的走动。

从而在任何时候给系统提供了准确的时间,满足各种不同的对时间的要求。

时钟芯片的接口有串行和并行之分,不同的芯片要根据具体情况设计。

DS12887的说明:DS12887是一款比较高档并常用的时钟芯片,芯片内部自配有可充电电池,在无外部电源时也可保证十年的正常运行。

芯片内部还提供了约100个字节的RAM空间,其存储的数据也可以长期保持不变。

DS12887提供了多种时钟的特殊功能,如定时中断等等。

学习板的原理以及DS12887的操作:为了给大家提供一个了解时钟芯片的条件,在学习板提供了在各种系统应用很广泛的时钟芯片DS12887。

DS12887跟MC146818B管腿是兼容的,被广泛的应用在处主要讲述原理图上的相关操作。

DS12887芯片能工作在两种总线时序,一是MOTOROLA模式,一是INTEL模式。

这个模式的选择是由管腿MOT来控制的,当MOT为高时表示使用MOTOROLA总线时序;当MOT为低时表示使用INTEL 总线时序。

学习板上使用的是INTEL模式,因为MOT管脚接地了。

因为选择了INTEL模式,所以DS管脚对应的就是RD信号。

DS12887的片选信号是由138译码器产生的CS_12887。

从74HC138的原理图可以看出,这个片选信号对应的地址是0xD000H(只要保证高四位是1101),因此无论向DS12887读操作还是写操作,都必须对在地址上加上AD0~AD7的偏移地址来进行操作。

/IRQ端输出定时中断信号INT_12887通过跳线J3连接的CPU的INT1中断信号端,从而给系统提供了定时功能。

关于此方面的知识,可以去三毛电子世界获得更多支持。

图书馆:/souceitem/library.asp产品支持:/shopitem/shopmain.asp论坛:/bbsitem/indexbbs.asp。

DS12887时钟芯⽚_中⽂资料_DS12887时钟芯⽚(中⽂资料⼀)特点·可作为IBM AT 计算机的时钟和⽇历·与MC14681B 和DS1287的管脚兼容·在没有外部电源的情况下可⼯作10年·⾃带晶体振荡器及电池·可计算到2100年前的秒、分、⼩时、星期、⽇期、⽉、年七种⽇历信息并带闰年补偿·⽤⼆进制码或BCD 码代表⽇历和闹钟信息·有12和24⼩时两种制式,12⼩时制时有AM 和PM提⽰·可选⽤夏令时模式·可以应⽤于MOTOROLA 和INTEL 两种总线·数据/地址总线复⽤·内建128字节RAM14字节时钟控制寄存器114字节通⽤RAM·可编程⽅波输出·总线兼容中断(/IRQ )·三种可编程中断时间性中断可产⽣每秒⼀次直到每天⼀次中断周期性中断122ms 到500ms时钟更新结束中断管脚名称AD0-AD7-地址/数据复⽤总线 NC -空脚MOT -总线类型选择(MOTOROLA/INTEL ) CS -⽚选 AS -ALER/W -在INTEL 总线下作为/WR DS -在INTEL 总线下作为/RD RESET -复位信号 IRQ -中断请求输出 SQW -⽅波输出VCC -+5电源 GND -电源地上电/掉电当VCC ⾼于4.25V200ms 后,芯⽚可以被外部程序操作;当VCC 低于4.25V 时,芯⽚处于写保护状态(所有的输⼊均⽆效),同时所有输出呈⾼阻状态;当VCC 低于3V 时,芯⽚将⾃动把供电⽅式切换为由内部电池供电。

管脚功能MOT (总线模式选择)当此脚接到VCC 时,选⽤的是MOTOROLA 总线时序;当它接到地或不接时,选⽤的是INTEL 总线时序。

SQW(⽅波输出)-当VCC低于4.25V时没有作⽤。

周期性中断率和⽅波中断频率表寄存器A中的控制位RS3 RS2 RS1 RS0 P1周期中断周期SQW输出频率0 0 0 0 ⽆⽆0 0 0 1 3.90625ms 256Hz0 0 1 0 7.8125ms 128Hz0 0 1 1 122.070µs 8.192kHz0 1 0 0 244.141µs 4.096 kHz0 1 0 1 488.281µs 2.048 kHz0 1 1 0 976.5625µs 1.024 kHz0 1 1 1 1.953125ms 512 Hz1 0 0 0 3.90625 ms 256 Hz1 0 0 1 7.8125 ms 128 Hz1 0 1 0 15.625 ms 64 Hz1 0 1 1 31.25 ms 32 Hz1 1 0 0 62.5 ms 16 Hz1 1 0 1 125 ms 8 Hz1 1 1 0 250 ms 4 Hz1 1 1 1 500 ms2 HzAD0-AD7(双向数据/地址复⽤总线)AS(地址锁存)ALEDS(Data Strobe or Read Input) RD当系统选择的是INTEL总线模式时,DS被称作RD。

DS12887是美国达拉斯半导体公司最新推出的时钟芯片,采用CMOS技术制成,把时钟芯片所需的晶振和外部锂电池相关电路集于芯片内部,同时它与目前 IBM AT计算机常用的时钟芯片MC146818B和DS1287管脚兼容,可直接替换。

采用DS12887芯片设计的时钟电路勿需任何外围电路并具有良好的微机接口。

DS12887芯片具有微轼耗、外围接口简单、精度高、工作稳定可靠等优点,可广泛用于各种需要较高精度的实时时钟场合中。

其主要功能如下:(1)内含一个锂电池,断电情况运行十年以上不丢失数据。

(2)计秒、分、时、天、星期、日、月、年,并有闰年补偿功能。

(3)二进制数码或BCD码表示时间、日历和定闹。

(4)12小时或24小时制,12小时时钟模式带有PWM和AM指导,有夏令时功能。

(5)MOTOROLA5和INATAEL总线时序选择。

(6)有128个RAM单元与软件音响器,其中14个作为字节时钟和控制寄存器,114字节为通用RAM,所有ARAM单元数据都具有掉电保护功能。

(7)可编程方波信号输出。

(8)中断信号输出(IRQ)和总线兼容,定闹中断、周期性中断、时钟更新周期结束中断可分别由软件屏蔽,也可分别进行测试。

2. DS12887的原理及管脚说明DS12887内部原理如图1所示,由振荡电路、分频电路、周期中断/方波选择电路、14字节时钟和控制单元、114字节用户非易失RAM、十进制/二进制计加器、总线接口电路、电源开关写保护单元和内部锂电池等部分组成。

图2显示了DS12887管脚排列图。

下面分别说明管脚功能:GND,V CC:直流电源+5V电压。

当5V电压在正常范围内时,数据可读写;当V CC低于4.25V,读写被禁止,计时功能仍继续;当V CC下降到3V以下时,RAM和计时器被切换到内部锂电池。

MOT(模式选择):MOT管脚接到V CC时,选择MOTOROLA时序,当接到GFND时,选择INTEL时序。

新型实时时钟芯片DS12887原理与运用

郭凌;姚大红

【期刊名称】《国外电子元器件》

【年(卷),期】1997(000)001

【摘要】DS12887为DALLAS公司生产的实时钟芯片,除具有实时钟功能外,它还具有114字节的这用RAM,内藏锂电池,并与广泛应用的DS1287,MC146818B脚对脚兼容。

本文对应用角度出发,概述了其功能特点,外部特性,内部结构及与微机芯片的接口应用。

【总页数】6页(P14-19)

【作者】郭凌;姚大红

【作者单位】后勤工程学院;后勤工程学院

【正文语种】中文

【中图分类】TN303

【相关文献】

1.并行实时时钟芯片DS12887及其应用 [J], 王祖强;葛敏;王照军

2.实时时钟芯片DS12887特点与应用 [J], 周兴华

3.实时时钟芯片DS12887原理与应用 [J], 薛伦生;戴新生

4.DS12887实时时钟芯片及应用研究 [J], 周向红;范伟

5.利用DS12887时钟芯片实现实时定时电路 [J], 侯崇升

因版权原因,仅展示原文概要,查看原文内容请购买。

Ds12887--内嵌电池的时钟芯片中国器件选型网赵星寒①,DS12887简介时钟芯片DS12887是一个内嵌锂电池的并行通讯芯片,该器件提供完整的实时时钟/日历、定时闹钟,还包含三个可屏蔽中断(共用一个中断输出)以及可编程方波输出。

DS12887内部还提供114字节静态RAM,这些存储器是内部锂电池供电的,因此数据不会丢失。

DS12C887对于少于31天的月份,其日期能够在月末自动调整,带有闰年的月份可以自动补偿。

该器件可配置为24小时或12小时格式。

精确的温度补偿电路用于状态。

一旦检测到主电源失效,器件可自动切换到备用电源。

支持Intel 监视的VCC和Motorola模式。

主要特点是:∙RTC计算秒、分、时、星期、日、月、年信息,具有润年补偿,有效期至2099年;∙用二进制或BCD表示时间;∙具有AM、PM标示的12小时模式或24小时模式;∙可选择Intel或Motorola总线时序;∙内部包含128字节存储单元,其中114字节供用户自由使用;∙三路中断可分别通过软件屏蔽与检测;∙闹钟可设置为每秒一次至每星期一次;∙可编程的方波输出信号;∙自动电源失效检测和切换电路;DS12887是一片24引脚封装的芯片,因内含锂电池高度较一般芯片高得多。

图1是引脚逻辑图,所有引脚定义如下:MOT——引脚1,总线方式选择。

连接到电源时,选择Motorola总线方式;连接到地时,选择Intel总线方式。

因为51系列单片机是Intel产品,所以这个引脚应该连接到地。

NC——引脚2、引脚3、引脚16、引脚20、引脚21和引脚22不使用。

AD0~AD7——引脚4~引脚11,地址/数据复用总线,双向工作。

直接连接到单片机的P0口。

GND——引脚12,地线。

——引脚13,片选信号输入,低电平时芯片工作,高电平时芯片不工作。

AS——引脚14,地址锁存输入,如果引脚出现一个下降沿,总线上的信号将被作为地址信号而锁存。

在对芯片进行读或写操作时,必须先输入地址。

DS12887的原理和应用1.功能特点DS12887是美国达拉斯半导体公司最新推出的时钟芯片,采用CMOS技术制成,把时钟芯片所需的晶振和外部锂电池相关电路集于芯片内部,同时它与目前 IB M AT计算机常用的时钟芯片MC146818B和DS1287管脚兼容,可直接替换。

采用DS12887芯片设计的时钟电路勿需任何外围电路并具有良好的微机接口。

DS1288 7芯片具有微轼耗、外围接口简单、精度高、工作稳定可靠等优点,可广泛用于各种需要较高精度的实时时钟场合中。

其主要功能如下:(1)内含一个锂电池,断电情况运行十年以上不丢失数据。

(2)计秒、分、时、天、星期、日、月、年,并有闰年补偿功能。

(3)二进制数码或BCD码表示时间、日历和定闹。

(4)12小时或24小时制,12小时时钟模式带有PWM和AM指导,有夏令时功能。

(5)MOTOROLA5和INATAEL总线时序选择。

(6)有128个RAM单元与软件音响器,其中14个作为字节时钟和控制寄存器,114字节为通用RAM,所有ARAM单元数据都具有掉电保护功能。

(7)可编程方波信号输出。

(中断信号输出(IRQ)和总线兼容,定闹中断、周期性中断、时钟更新周期结束中断可分别由软件屏蔽,也可分别进行测试。

2. DS12887的原理及管脚说明DS12887内部原理如图1所示,由振荡电路、分频电路、周期中断/方波选择电路、14字节时钟和控制单元、114字节用户非易失RAM、十进制/二进制计加器、总线接口电路、电源开关写保护单元和内部锂电池等部分组成。

GND,VCC:直流电源+5V电压。

当5V电压在正常范围内时,数据可读写;当V CC 低于4.25V,读写被禁止,计时功能仍继续;当VCC下降到3V以下时,RAM和计时器被切换到内部锂电池。

MOT(模式选择):MOT管脚接到VCC时,选择MOTOROLA时序,当接到GND时,选择INTEL时序。

SQW(方波信号同):SQW管脚能从实时时钟内部15级分频器的13个抽头中选择一个作为输出信号,其输出频率可通过对寄存器A编程改变。

新型实时时钟芯片DS12887原理与应用摘要:DS12887为DALLAS公司生产的实时时钟芯片,除具有实时钟功能外,它还具有114字节的通用RAM。

内藏锂电池,并与广泛应用的DS1287、MC146818B脚对脚兼容。

本文从应用角度出发,概述了其功能特点、外部特性、内部结构及与微机芯片的接口应用。

关键词:更新周期;非易失RAM;各总线兼容;定闹中断;周期性中断1. DS12887的功能特点DS12887是美国达拉斯半导体公司最新推出的时钟芯片,采用CMOS技术制成,把时钟芯片所需的晶振和外部锂电池相关电路集于芯片内部,同时它与目前IBM A T计算机常用的时钟芯片MC146818B和DS1287管脚兼容,可直接替换。

采用DS12887芯片设计的时钟电路勿需任何外围电路并具有良好的微机接口。

DS12887芯片具有微轼耗、外围接口简单、精度高、工作稳定可靠等优点,可广泛用于各种需要较高精度的实时时钟场合中。

其主要功能如下:(1)内含一个锂电池,断电情况运行十年以上不丢失数据。

(2)计秒、分、时、天、星期、日、月、年,并有闰年补偿功能。

(3)二进制数码或BCD码表示时间、日历和定闹。

(4)12小时或24小时制,12小时时钟模式带有PWM和AM指导,有夏令时功能。

(5)MOTOROLA5和INA TAEL总线时序选择。

(6)有128个RAM单元与软件音响器,其中14个作为字节时钟和控制寄存器,114字节为通用RAM,所有ARAM单元数据都具有掉电保护功能。

(7)可编程方波信号输出。

(8)中断信号输出(IRQ)和总线兼容,定闹中断、周期性中断、时钟更新周期结束中断可分别由软件屏蔽,也可分别进行测试。

2. DS12887的原理及管脚说明DS12887内部原理如图1所示,由振荡电路、分频电路、周期中断/方波选择电路、14字节时钟和控制单元、114字节用户非易失RAM、十进制/二进制计加器、总线接口电路、电源开关写保护单元和内部锂电池等部分组成。

图2显示了DS12887管脚排列图。

下面分别说明管脚功能:GND,VCC:直流电源+5V电压。

当5V电压在正常范围内时,数据可读写;当VCC低于4.25V,读写被禁止,计时功能仍继续;当VCC下降到3V以下时,RAM和计时器被切换到内部锂电池。

MOT(模式选择):MOT管脚接到VCC时,选择MOTOROLA时序,当接到GFND时,选择INTEL 时序。

SQW(方波信号同):SQW管脚能从实时时钟内部15级分频器的13个抽头中选择一个作为输出信号,其输出频率可通过对寄存器A编程改变。

AD0~AD7(双向地址/数据复用线):总线接口,可与MOTOROLA微机系列和INTEL微机系列接口。

AS(地址选通输入):用于实现信号分离,在AD/ALE的下降沿把地址锁入DS12887。

DS(数据选通或读输入):DS/RD客脚有两种操作模式,取决于MOT管脚的电平,当使用MOTOROLA 时序时,DS是一正脉冲,出现在总线周期的后段,称为数据选通;在读周期,DS指示DS12887驱动双向总的时刻,在写周期,DS的后沿使DS12887锁存写数据。

选择INTEL时序时,DS称作(RD),RD与典型存贮器的允许信号(OE)的定义相同。

R/W(读/写输入):R/W管脚也有两种操作模式。

选MOTOROLA时序时,R/W是一电平信号,指示当前周期是读或写周期,DSO为高电平时,R/W高电平指示读周期,R/W低电平指示写周期;选INTEL时序,R/W信号是一低电平信号,称为WR。

在此模式下,R/W管脚与通用RAM的写允许信号(WE)的含义相同。

CS(片选输入):在访问DS12887的总线周期内,片选信号必须保持为低。

IRQ(中断申请输入):低电平有效,可作微处理的中断输入。

没有中断条件满足时,IRQ处于高阻态。

IRQ线是漏极开路输入,要求外接上接电阻。

RESET(复位输出):当该脚保持低电平时间大于200ms,保证DS12887有效复位。

3. DS12887的内部功能3.1 地址分配图DS12887的地下分配图如图3所示,由114字节的用户RAM,10字节的存放实时时钟时间。

日历和定闹RAM及用于控制和状态的4字节特殊寄存器组成,几乎所有的128个字节可直接读写。

3.2 时间、日历和定闹单元时间和日历信息通过读相应的内存字节来获取,时间、日历和定闹通过写相应的内存字节设置或初始化,其字节内容可以是十进制或BCD形式。

时间可选择12小时制或24小时制,当选择12小时制时,小时字节搞位为逻辑“1”代表PM。

时间、日历和定闹字节是双缓冲的,总是可访问的。

每秒钟这10个字节走时1秒,检查一次定闹条件,如在更新时,读时间和日历可能引起错误。

三个字节的定闹字节有两种使用方法。

第一种,当定闹时间写入相应时、分、秒定闹单元,在定允许闹位置高的条件下,定闹中断每天准时起动一次。

第二种,在三个定闹字节中插入一个或多个不关心码。

不关心码是任意从C到FF的16进制数。

当小时字节的不关心码位置位时,定闹为小时发生一次由于相线小时和分钟定闹字节置不关心位时,每分钟定闹一次;当三个字节都置不关心位时,每秒中断一次。

3.3 非易失RAM在DS12887中,114字节通用非易失RAM不专用于任何特殊功能,它们可被处理器程序用作非易失内存,。

在更新周期也可访问。

3.4 中断RTC实时时钟加RAM向处理器提供三个独立的、自动的中断源。

定闹中断的发生率可编程,从每秒一次到每天一次,周期性中断的发生率可从500ms到122µs选择。

更新结束中断用于向程序指示一个更新周期完成。

中断控制和状态位在寄存器B和C中,本文的其它部分将详细描述每个中断发生条件。

3.5 晶振控制位DS12887出厂时,其内部晶振被关掉,以防止锂电池在芯片装入系统前被消耗。

寄存器A的BIT4~BIT6为010时打开晶振,分频链复位,BIT4~BIT6的其它组合都是使晶振关闭。

3.6 方波输出选择如图1原理图所示,15级分步抽着中的13个可用于15选1选择器,选择分频器抽头的目的是在SQW 管脚产生一个方波信号,其频率由寄存器A的RS0~RS3位设置。

SQW频率选择与周期中断发生器共离15选1选择器,一旦频率选择好,通过用程序控制方波输出允许位SWQE来控制SQW管脚输出的开关。

3.7 周期中断选择周期中断可在IRQ脚产生500ms一次到每122µs一次的中断,中断频率同样由寄存A确定,它的控制位为寄存器B中的PIE位。

3.8 更新周期DS12887每秒执行一次更新周期还比较每一定闹字节与相应的时间字节,如果匹配枵三个字节都是不关心码,则产生一次定闹中断。

4. DS12887状态控制寄存器DS12887有4个控制寄存器,它们在任何时间都可访问,即使更新周期也不例外。

UIP:更新周期正在进行位。

当UIP为1,更新转换将很快发生,当UIP为0,更新转换至少在244µs内不会发生。

DV0,DV1,DV2:用于开关晶振和复位分频链。

这些位的010唯一组合将打开晶振并允许RTC计时。

表1列了邮周期中断率和方波频率。

RS3,RS2,RS1,RS0:频率选择位,从15级频率器13个抽头中选一个,或禁止分频器输入,选择好的抽头用于产生方波(SQW管脚)输出和周期中断,用户可以:(1)用PIE位允许中断:(2)用SQWE位允许SQAW输出;(3)二者同时允许并用相同的频率;(4)都不允许4.2 寄存器SET:SET为0,时间更新正常进行,每秒计数走时一次,当SET位写入1,时间更新被禁止,程序可初始化时间和日历字节。

PIE:周期中断劲旅位,PIE为1,则允许以选定的频率拉低IRQ管脚,产和不足齿数民:PIE为0,则禁止中断。

AIE:定闹中断允许位,PIE为1,允许中断,否则禁止中断。

SQWE:方波允许位,置1选定频率方波从SQW脚输出;为0-时,SQW脚为低。

DM:数据模式位,DM为1青蛙为十进制数据,而0表明是BCD码的数据。

24/12:小时格式位,1表明24小时械,而0表明12小时械。

DSE:P夏令时允许位,当DSE置1时允许两个特殊的更新,在四月份的第一时期日、时间从1:59:59AM时改变为1:00:00AM,当DSE位为0,这种特殊修正不发生。

4.3 寄存器IRQF:中断申请标志位。

当下列表达式中一个或多个为真时,置1。

PF=PIE=1;AF=AIE=1;UF=UIE=1;即:IRQF=PF·PIE+AF·AIE+UF·UIE只要IRQF为1,IRQ管脚输出低,程序读寄存器C以后或RESET管脚为低后,所有标志位清零。

AF:定闹中断标志位,只读,AF为1表明现在时间与定闹时间匹配。

VF:更新周期结束标志位。

VF为1表明更新周期结束。

BIAT0~BIT3:未用状态位,读出总为0,不能写入。

4.4 寄存器DVRT:内部锂电池状态位,平时应总读出1,如出现0,表明内部锂电池耗尽。

BIT0~BIT6:未用状态位,读出总为0,不能写入。

5. 硬件接口电路DS12887时钟芯片和80C31单微机的接口电路如图4所示。

模式选择脚MOT拉地,选择不NTEL时序,选择DS12887时钟芯片的地址总线及AS端口和80C31单片微机的P0及ALE端直接相联;而DS、R/W读写控制线与单片机的RD、WAR控制线相连;DS12887的高位地址由80C31半日片机的P2.7端口来片选,则DS12887的高8位地址定为7FH,而其低8侠地址则由芯片内部各单元的地址来决定(00H~3FH);DS12887的中断输出端IRQ和80C的外部INT0端相联,给单片机提供中断信号;DS12887的SQW端口可编程产生方波输出信号。

6. 接口软件下面为DS12887时钟芯片和80C31单片机的接口软件,假定采用每天24小时制的非夏令时,时间数据格式为BCD码,初始化时间为1996年1月1日9时00分00秒,1k方波输出。

时钟芯片每一秒种向单片机申请中断一次,一方面让单片机修改一次时钟显示,另一方面也给单片微机系统提供时间基准。

(1)DS12887时钟芯片的初始化写入程序MOV DPTR,#7F0AH;寄存器A地址MOV A,#70H:DV2~DV0=111,分频复位MOVX @ DPTR,AAINC DPTR:到寄存器B地址MOV A,#8AH:停止更新,允许更新中断,选BCD码,24小时制MOVX @DPRT,AMOV QPL,#00H,秒单元地址CLR A:00秒MOVX @DPTR,AMOV DPL,#02H;分单元地址CLR A:00分MOVX @DPTR,AMOV DPL,#04H;时单元地址MOV A,#09H;9时MOVX @DPTR,AMOV DPL#07H;日单元地址MOV A,@01H:1日MOVX@DPTR,AINC DPTR:到月单元地址MOV A,#01H;1月MOVX @DPTR,AIC DPTR:到年单元地址MOV A,#96H;1996年MOVX @DPTR,AINC DPTR;到寄存器A地址MOV A,#26H;DV2~DV0=010 RS3~RS0=0110MOVX @DPTR,A:选周期中断率为976.5625µs,允许方波输出,频率1kHzINC DPTR:到寄存器BMOV A,#1AH;每秒更新一次,允许方波输出,24小时制MOVX @DPTR,A:时钟开始运行(2)读取DS12887时钟日历数据程序DS12887的日历时钟通常有中断和查询两种方法读出。