第一章混合集成电路的基片

- 格式:pdf

- 大小:776.65 KB

- 文档页数:36

半导体芯片制造工:半导体芯片制造高级工考试题及答案(最新版)考试时间:120分钟 考试总分:100分遵守考场纪律,维护知识尊严,杜绝违纪行为,确保考试结果公正。

l4、单项选择题器件的横向尺寸控制几乎全由( )来实现。

A.掩膜版 B.扩散 C.光刻 本题答案: 5、填空题钎焊密封工艺主要工艺条件有钎焊气氛控制、温度控制和密封腔体内( )控制。

本题答案: 6、单项选择题pn 结的击穿电压和反向漏电流既是晶体管的重要直流参数,也是评价( )的重要标志。

A.扩散层质量 B.设计 C.光刻 本题答案: 7、单项选择题溅射法是由( )轰击靶材表面,使靶原子从靶表面飞溅出来淀积在衬底上形成薄膜。

A.电子 B.中性粒子姓名:________________ 班级:________________ 学号:________________--------------------密----------------------------------封 ----------------------------------------------线----------------------C.带能离子本题答案:8、单项选择题金属封装主要采用金属和玻璃密封工艺,金属作封装底盘、管帽和引线,()做绝缘和密封。

A.塑料B.玻璃C.金属本题答案:9、判断题没有经济收入或交纳党费有困难的党员,由本人提出申请,经党支部委员会同意,可以少交或免交。

本题答案:10、填空题气中的一个小尘埃将影响整个芯片的()性、()率,并影响其电学性能和()性,所以半导体芯片制造工艺需在超净厂房内进行。

本题答案:11、单项选择题常用胶粘剂有热固性树脂、热塑性树脂和橡胶型胶粘剂3大类。

半导体器件的粘封工艺一般选用()。

A.热塑性树脂B.热固性或橡胶型胶粘剂本题答案:12、填空题外延层的迁移率低的因素有原材料纯度();反应室漏气;外延层的晶体();系统沾污等;载气纯度不够;外延层晶体缺陷多;生长工艺条件不适宜。

混合集成电路介绍混合集成电路(又叫厚膜集成电路)。

是利用如丝网印刷机,膜厚测试仪,烧结炉,激光修调机,自动贴片机等设备在基片上以膜的形式印刷导体、电阻、包封釉等浆料,并通过烘干烧结等工序,再将各种弱电的电子元器件用表面贴装技术高密度地进行组装,然后再行数据写入、调整测试、封装等后期工作做成一个局部电路。

同时还可再采用表面贴装技术(SMT)将各种微型元器件进行二次集成,以及采用裸芯片装配技术制造多芯片电路(MCM)。

它的优点是:1.由于混合集成电路可以使用各种电气元件,一般都采用为它专门生产的电阻、电容、集成电路、继电器、传感器等,这些元器件往往体积小,重量轻,性能千变万化。

使得这种电路具有体积很小,重量很轻,又可实现其强大的功能。

2.可应用各种电路基板,例如印制电路板、电气绝缘塑料板、陶瓷基片等而具有不同的机械性能。

3.能使用各种不同的包装,例如塑封、金属、半金属封装、胶封或裸封等。

因而具有不同的外形、体积和防护性能。

4.通常在自动生产的流水线上生产的,因此它的生产速度快、成本低、性能的一致性好、更适宜于大批量生产。

5.它可应用到不同的领域,例如宇航、军事、汽车行业、电视、程控交换机、通讯、雷达导航、炮弹引信、游戏娱乐设备、移动通信、汽车、摩托车、计算机、数据处理等点火电路、DC/DC电源模块、变频电路、调速电路、网路电路。

1、电路介绍:(1)制造导体串联电阻小,线条间距小(最小达0.2㎜)电阻温度系数低(最低为 50ppm),电阻精度高(达万分之五)。

(2)多层,高密度、高精度、低漂移、体积小、寿命长。

(3)厚膜电路产品性能:基板:96-99%氧化铝,导体:钯银,铂银,金,钯金2、电阻:(1)阻值范围:100毫欧至20兆欧(2)阻值误差:可低至+0.05%(3)温度系数: +50ppm (-55℃~+125℃)(4)稳定性: ≤0.4% (70%满负荷1000小时)(5)功率损耗: 100W/平方英寸3、介质:(1)绝缘电阻: ≥1011Ω(2)介质常数: 9贴装器件: 芯片或各类表面贴装型器件.组装方法: 芯片线焊及回流焊接.包封: 环氧树脂裹封.混合集成技术经过三十多年的发展,已成为微电子技术的两重要组成部分之一。

混合集成电路的组装与封装工艺韩杨锋(陕西国防学院电子系微电3101班)摘要:混合集成电路是由半导体集成工艺与薄(厚)膜工艺结合而制成的集成电路。

混合集成电路是在基片上用成膜方法制作厚膜或薄膜元件及其互连线,并在同一基片上将分立的半导体芯片、单片集成电路或微型元件混合组装,再外加封装而成。

与分立元件电路相比,混合集成电路具有组装密度大、可靠性高、电性能好等特点。

相对于单片集成电路,它设计灵活,工艺方便,便于多品种小批量生产;并且元件参数范围宽、精度高、稳定性好,可以承受较高电压和较大功率。

关键词:混合集成电路、电路互联、导电胶引言:混合集成电路组装所用的工艺,在当今工业界是相当标准的,差别主要是在选择组装材料(粘结胶或冶金贴装)、互联工艺(线焊、倒装片或带式自动键合)和密封方法(缝焊、带式炉密封或塑封)上。

对于厚膜和薄膜、组装工艺一般是相同的。

取决于基片是用合金贴装还是用环氧贴装方法贴到封装内,有几种组装顺序:若用合金贴装,因为这是高温操作(用金—锡焊片时约310~320℃),基片必须首先贴在封装上,随后的芯片和元件贴装是用递减的工艺温度的顺序进行的。

这样,若某些元件是用软焊(铅—锡或铟合金)而其他元件用环氧贴装时,温度较高的焊料贴装应该先进行加工。

自然,为降低成本,人们希望仅采用一种贴装工艺,而且最好是环氧贴装,因为环氧最便宜而且容易返修。

当用环氧作为贴装材料时,有两种顺序可供选择,基片可以先贴装到外壳底座上,然后将芯片贴到基片上;或者可以将全部芯片先贴到基片上,然后再将基片贴到外壳底座上。

对于多单元复合基片(在基片背面有激光划线,以便以后分开),在分开基片和将它们插入到外壳底座上之前,批量制造导体/电阻/介质图形,用丝印或自动分配方法成批施加环氧粘接剂,自动贴装芯片和固化粘接剂是比较经济的。

在贴装以后,芯片(面向上)用几种焊接工艺之一进行电气互联。

最广泛使用的工艺是从器件焊盘到基片上金属化焊区之间用金线或铝线键合。

《集成电路》讲义一、什么是集成电路集成电路,简称 IC,是一种微型电子器件或部件。

它采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。

集成电路具有体积小、重量轻、引出线和焊接点少、寿命长、可靠性高、性能好等优点,同时成本低,便于大规模生产。

它不仅在工、民用电子设备如收录机、电视机、计算机等方面得到广泛的应用,同时在军事、通讯、遥控等方面也得到广泛的应用。

二、集成电路的发展历程集成电路的发展可以追溯到上世纪 50 年代。

1958 年,杰克·基尔比(Jack Kilby)在美国德州仪器公司制作出了世界上第一块集成电路。

这块集成电路由一个锗晶体管、三个电阻和一个电容组成,虽然看起来非常简单,但它却开创了电子技术的新纪元。

在随后的几十年里,集成电路技术不断发展。

从最初的小规模集成电路(SSI),到中规模集成电路(MSI)、大规模集成电路(LSI)、超大规模集成电路(VLSI),再到今天的特大规模集成电路(ULSI),集成电路的集成度越来越高,性能也越来越强大。

在这个发展过程中,制造工艺的不断进步起到了关键作用。

从早期的双极型工艺,到后来的 CMOS 工艺,再到现在的纳米级工艺,制造工艺的进步使得集成电路能够容纳更多的晶体管,同时功耗更低、速度更快。

三、集成电路的制造工艺集成电路的制造是一个极其复杂的过程,涉及到多个学科和技术领域。

下面简单介绍一下集成电路的制造工艺流程。

1、设计首先,需要根据电路的功能和性能要求进行设计。

设计过程包括逻辑设计、电路设计、版图设计等。

设计完成后,生成相应的版图文件,用于后续的制造。

2、晶圆制备晶圆是集成电路制造的基础材料,通常由硅制成。

首先需要将高纯度的硅原料熔化,然后通过拉晶工艺制成单晶硅棒。

接着,将单晶硅棒切割成薄片,经过研磨、抛光等工艺,制成晶圆。

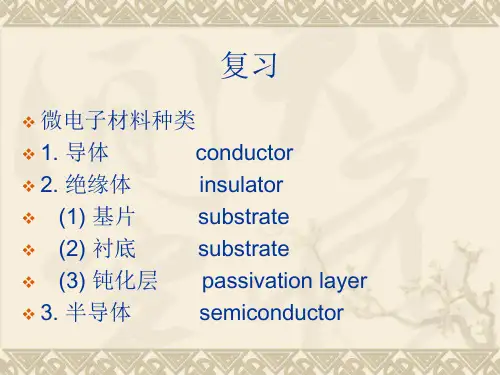

集成电路的基片材料一、引言集成电路是现代电子技术中的重要组成部分,其制造需要使用基片材料。

基片材料是指用于制造半导体器件的单晶硅或其他半导体材料。

本文将详细介绍集成电路的基片材料。

二、单晶硅单晶硅是目前最常用的基片材料之一,其主要原因是单晶硅具有优异的电学性能和物理性能。

单晶硅可以通过Czochralski方法生长,这种方法可以获得高质量的单晶硅。

此外,还可以通过浮区法生长单晶硅,这种方法可以获得更大尺寸的单晶硅。

三、多晶硅多晶硅是由许多小结晶组成的半导体材料。

相对于单晶硅而言,多晶硅具有更高的电阻率和较差的电学性能。

但是,多晶硅具有良好的机械强度和较低的制造成本。

因此,在某些应用场合下,多晶硅也被广泛应用。

四、氮化铝氮化铝是一种新型基片材料,在高功率应用领域有广泛应用。

氮化铝具有优异的热导率和机械强度,同时还具有良好的电学性能。

氮化铝可以通过分子束外延法生长。

五、蓝宝石蓝宝石是一种透明的晶体材料,可以用作基片材料。

蓝宝石具有高硬度和良好的光学性能,因此在LED制造中被广泛应用。

六、其他材料除了上述几种基片材料之外,还有其他一些基片材料。

例如,碳化硅、氮化硅等。

这些材料具有特殊的物理性质,在某些应用场合下也被广泛应用。

七、总结本文详细介绍了集成电路的基片材料。

单晶硅是目前最常用的基片材料之一,多晶硅则在某些特定应用场合下得到广泛应用。

氮化铝和蓝宝石则在高功率LED制造中得到广泛应用。

此外,还有其他一些基片材料,在特定领域也得到了广泛应用。