Altera FPGA带NiosII内核程序的JTAG下载方法总结

- 格式:doc

- 大小:192.00 KB

- 文档页数:5

Quartus II的AS/JATG下载方式教程V1.0版本BY GJH计通学院通信电子实验室二〇一五年八月十二日一、简介1.1 三种方式有些人对于FPGA下JTAG的下载方式有些迷惑,为什么出现配置芯片了,为什么要用不同的下载电缆,不同的下载模式?通过在网上查阅相关资料做了总结和整理如下:FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

●AS模式(active serial configuration mode):FPGA器件每次上电时作为控制器,由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,从配置器件EPCS主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程配置数据通过DATA0引脚送入 FPGA,配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

●PS模式(passive serial configuration mode):则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,EPCS作为控制器件,把FPGA当作存储器,把数据写人到FPGA中,实现对FPGA的编程。

●JTAG:JTAG是直接烧到FPGA里面的由于是SRAM 断电后要重烧,AS是烧到FPGA的配置芯片里保存的每次上电就写到FPGA里。

图1-1 可下载格式一览表1.2 如何选择一般情况下,Cyclone II开发板上应该有两种下载模式,AS和JTAG。

AS 就是下载.pof文件到EPCS中。

而JTAG就是下载.sof或jic文件到FPGA中的RAM中。

实验室红色板子只有JTAG一种,黑色大板子支持两种。

在平时的调试当中,使用默认的JATG会是比较好的方式,当遇到需要保存程序的时候,就可以选择AS。

二、使用方法2.1 JATG方式这是最常见的下载方式,它其实是支持掉电保存的。

下载FPGA里面有三种方式JTAG 下载sof文件,掉电丢失可以将sof转换为jic文件,用EPCSx配置,掉电不丢失AS 下载pof文件,配置EPCSx,掉电不丢失PS 比较老的下载方式,很少使用1.区分CPLD与FPGACPLD是英文Complex Programmable Logic Device的缩写,即复杂可编程逻辑器件,CPLD基于EEPROM工艺(掉电不丢失),集成度相对fpga较低,以MicroCell (包括组合部分与寄存器)为基本单元。

具有非挥发特性,可以重复写入。

cpld 掉电数据不丢失,芯片比较便宜,硬件设计成本比较低。

fpga掉电数据丢失,硬件设计时要而外加配置flash芯片,或者单片机负责上电时把程序写到fpga里面,(如果程序较大,灵活的方案为fpga+单片机+大容量的flash);集成度高,以LE(包括查找表、触发器及其他)为基本单元,有内嵌Memory、DSP等,支持IO标准丰富。

具有易挥发性,需要有上电加载过程。

可以简单的理解为:cpld比较简单,主要是逻辑运算能力,fpga=cpld+算法处理模块。

2 FPGA中,当选用AS 下载pof文件,无法成功时将sof转换为jic文件,用EPCSx配置,下载时选用JTAG 下载转换后的jic文件。

转换过程如下:e the Assembler to generate an SRAM Object File (.sof) containing the FPGA configuration data.1.使用汇编器产生一个包含FPGA配置数据的SRAM目标文件(.sof)。

2.Choose Convert Programming Files (File menu).2.选择转换编程文件(File->Convert Programming Files)。

3.Under Output programming file, select JTAG Indirect Configuration File (.jic) in the Programming file type list.3. 在输出编程文件下面,在编程文件类型列表中选择JTAG间接配置文件(.jic)。

关于Altera器件不能下载的问题总结笔者前一段时间在调试电路板时碰到了器件不能正确下载的问题,无奈之中只能上论坛查找相关帖子,发现遇到类似问题的人不在少数,此类帖子约有好几十,但笔者感觉对于面临问题的新手来说,相关帖子的参考价值还不够充分:一是帖子太分散,不易于查找;二是帖子提出问题和现象的多,解答的少;三是有些问题具有相关性,如果放在一起说明可能会更明白一些。

因此,笔者觉得有必要将相关的帖子中的内容简单综合一下,并将我刚刚遇到的问题及解决方法共享出来,以便其他人参考。

建议其他以前有过相关经验的同志也不吝将自己的经验和解决方法(这对后来者特别有参考意义)拿出来与大家共享。

笔者先抛砖引玉了:器件为cyclone_ep1c20,配置芯片为epcs4,留有AS接口和jatg接口。

遇到的问题为:AS方式下不能下载,但jatg方式下可以正常下载。

采用BBII电缆,在QuartusII中报错为"Error:can't recognize silicon ID for Device1"。

经检查电路连接无错误,fpga与epcs4之间的引脚存在波形,dclk,data,ncs,asdi 脚上都有始终输出,由于epcs4是刚买的芯片,没有配置信息,因此上电时FPGA 始终尝试从epcs4中读取配置信息,conf_done脚始终为高。

接上下载线后下载时,发现nconfig脚不能被拉低。

后换了台机器重试,问题依旧,最后重新找了条下载线,AS方式下下载成功。

经验:一般情况下参考datasheet中的说明和电路图进行连接,应该不会有什么问题;有问题时可以先查时序,确认无误后可以考虑其他的一些因素:下载线、电脑(有的电脑并口坏掉或可能驱动能力不够),软件******是否完全等。

Jatg下载过程中发现偶尔会下载失败,重新上电后正常。

以下为我从以前的帖子中整理的一些注意事项:1、使用下载线之前需要先安装驱动。

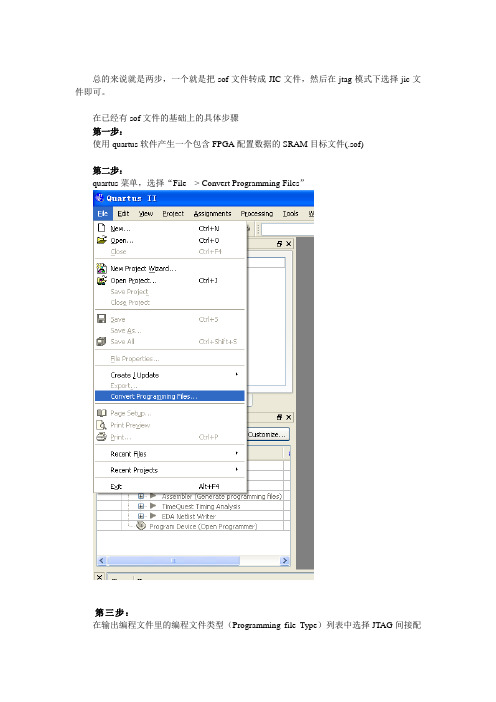

总的来说就是两步,一个就是把sof文件转成JIC文件,然后在jtag模式下选择jic文件即可。

在已经有sof文件的基础上的具体步骤第一步:使用quartus软件产生一个包含FPGA配置数据的SRAM目标文件(.sof)第二步:quartus菜单,选择“File --> Convert Programming Files”第三步:在输出编程文件里的编程文件类型(Programming file Type)列表中选择JTAG间接配置文件(JTAG Indirect Configuration File (.jic))。

第四步:在配置器件列表里(Configuration device),选择你想对之编程的目标EPCS配置器件。

我们这里选择EPCS4,对应配置文件大小是4M第五步:在文件名选择栏(File name:output_file.jic),指定你想生成的JIC文件的名字(把output_file 换成你想要的名字)第六步:选择高级,在弹出的窗口中再选择不检测ID和不检测CONF_DONE信号第七步:指定将要编程的EPCS的FPGA目标器件,选择Flash Loader项,点击Add Device。

在弹出的窗口中选择对应的器件第八步:指定一个现有的SRAM目标文件(.sof)来转换成JIC文件,在Input files to convert下面选择SOF Data,点击Add File...。

第九步:点击Generate,生成JIC文件第十步:加载JIC文件到flash中1)选择JTAG模式2)添加新生成的JIC文件3)在编程列表中EPCS器件的同一行,开启编程/配置选项4)开始编程。

Altera的FPGA下载常见问题经验小结软件部分:对于QUARTUS II 4.0版本软件,在安装完成后,需要做如下设置,软件才能够正常工作。

第一:设置license。

第二:安装驱动:Win2000/XP:1、打开控制面板(开始->设置->控制面板)2、双击“添加/删除硬件”图标,启动添加/删除硬件向导,然后按下一步继续。

3、在“选择一个硬件任务”面板上,选择“添加/排除设备故障”,然后按下一步继续。

WIN2000将会在新的硬件检测窗口里搜索新的即插即用设备。

4、在“选择一个硬件设备”面板上,选择“添加新设备”。

按下一步继续。

5、在“查找新硬件”面板上,选择“否,我想从列表选择硬件“。

按下一步继续。

6、在”硬件类型“面板上,选择”声音、视频和游戏控制器“。

按下一步继续。

7、在”选择一个设备驱动程序“窗口,点击”从磁盘安装“按钮。

8、指定win2000.inf文件的完整路径(例如安装目录>\drivers\win2000)。

按下一步继续。

9、在“没有找到数字签名”窗口,点击“是”按钮。

10、在“选择一个设备驱动程序”窗口,如果您使用ByteblasterMV或AlteraByteBlasterII,请安装相应驱动。

11、在“开始硬件安装”窗口,点击下一步继续。

12、在“没有找到数字签名”窗口,点击“是”按钮,继续安装。

13、在“完成添加/删除硬件向导”窗口,点击“完成”按钮14、在弹出的系统对话选择是否重新启动计算机。

驱动程序要在重新启动后才能使用。

重新启动后,即可在quartusII里进行program了。

第三:programer设置。

点击桌面图标Quartus II 4.0启动软件。

A)在tools菜单下,执行Programer命令。

B)点击hardware setup,点击select hardware,选择Byteblaster,---→add hardware---→close.C)完成后,在Hardware setup 右侧出ByteBlaster[LPT1],mode 的下拉菜单有JTAG,Passive Serial,Active Serial programing为设置正确的标志。

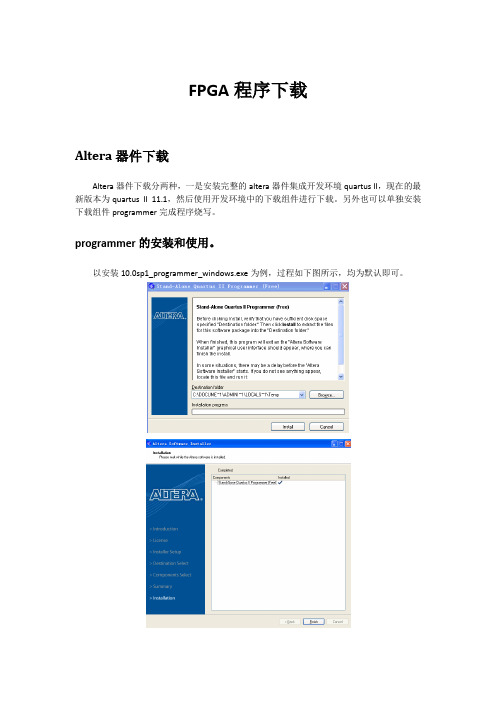

FPGA程序下载Altera器件下载Altera器件下载分两种,一是安装完整的altera器件集成开发环境quartus II,现在的最新版本为quartus II 11.1,然后使用开发环境中的下载组件进行下载。

另外也可以单独安装下载组件programmer完成程序烧写。

programmer的安装和使用。

以安装10.0sp1_programmer_windows.exe为例,过程如下图所示,均为默认即可。

安装完成后,连接usb-blaster下载器,分别连接到PC机的usb接口和板卡的JTAG接口,下载器连接好后再打开电源。

若驱动未安装,需要首先安装usb-blaster的驱动。

打开我的电脑-> 管理-> 设备管理器中找到相应的硬件,按下图所示步骤进行驱动安装,如果出现警告,点击继续。

驱动安装完成后,在安装路径中打开Quartus II 10.0sp1 Programmer。

如下图所示,在hardware setup中找到usb-blaster,然后点击close。

当下载板卡(硬件连接)准备好后,点击autodetect,显示器件列表,双击列表即可弹出文件选择窗口,最后选择相应的jic文件,并勾选program configure,点击start完成下载。

下载完成后需要对板卡进行重新上电。

Lattice器件下载ispVM System的安装和使用。

ispVMSystemV17.9.exe为例,全部过程均为默认,安装lattice器件的USB下载驱动时,也默认安装all drivers。

安装好后将Lattice 下载线的一端连接在PC机的usb口,另一端连接至板卡的JTAG接口(注意线的顺序),然后打开电源。

打开ispVM System,如下图所示。

点击scan按钮,系统会自动检测到器件,并显示器件列表,双击器件列表,弹出device information对话框,在器件部分选择板卡上的器件,在data部分点击browse选择要下载的bit文件。

Nios II Command Shell JTAG调试步骤Description:✓If the device pin JTAG debug port welding is completed, you can skip to the second step, installing quartus II, Nios II software.✓And you have installed quartus II, Nios II soft, you can skip to the third step is to install the JTAG driver.✓If the JTAG driver has been installed, you can jump to the fourth step, directly connected JTAG debug tool chain equipment.Step 1: Welding JTAG interfaceStep 2: Install quartus II 、Nios II◆Install Quartus II 9.1Decompressing files 91sp2_quartus_windows.exe to the current directory to the 91sp2_quartus_windows folder.Open 91sp2_quartus_windows folder, dblclick setup.exe file start the installation program of Quartus II 9.1.Click Next, until appear License Agreement Wind ow, then select “I accept the terms of the license agreement” and click Next.In the Customer Information interface, fill in the User Name and Company Name.Choose the install path. Here you can choose the default C:\Altera\91as installation path, also seting new installation path in yourself. If you setingnew installation path , you must notice: Installation path can't appearSpaces and Chinese characters.Here we choose default installationC:\Altera\91.Click on Next, choose Complete in the Setup Type window. Click on Next installation procedures. The process is slow to wait inside.After the completion of the will pop up a Dialog box of "Create Quartus II 9.1shortcut on desktop?", Prompts you to create desktop shortcut icons, choose"Yes".Pop-up dialog box again, the default settings, click "OK".Click Finish, to complete the installation of the Quartus II 9.1.◆Install Nios II 9.1Run 91sp2_nios2eds_windows.exe file, click Next, click Yes.Choose installation path, This path the same to you install Quartus II 9.1.click Next, installation.Click on Finsh, complele installation.Step 3: Install JTAG Driver◆connection the USB-Blaster◆wait for “find new hardware”if no the “Find new hardwre”message,try to change one USB interface.◆specifies the driver pathIn quartus II environment, specify the driver path can be installed directly. If your Quartus II 9.1installed in C:\altera\91directory, inC:\altera\91\quartus\drivers\usb-blaster\x32directory to find usbblst.inf,point in the file selection can be installed.In Device Manager find the USB-Blaster download cable equipment, the driver directory specified USB-Blaster driver directory.Of course, in order to provide our drivers is copyed into the computer, and then specify the file usbblst.inf on.◆After the installation restart the computer.Step 4: Connect JTAG debug equipment to run Command ShellNote:only you complete the first three steps, You will be able to work for the next.◆Run Command Shell, Start—Programe—Altera--- Nios II EDS 9.1—Nios II 9.1Command Shell.◆Enter the nios2-terminal command in the Command Shell interface and press theEnter Key to display the current operating status.As shown below.。

笔者使用的FPGA硬件平台:不同的平台,只是某些步骤的顺序或者软件的界面不一样罢了,笔者也是看着网络中的各种各样资料走过来的,究其本质所有的设置参数都是通用的,好了不多说,开始介绍怎样把Quartus的程序和Nios的程序同时都下载到FLASH中达到掉电不失,上电自动运行。

1.首先是创建一个工程,选好器件型号,不多说。

(注:工程的路径不要包含中文和空格,同时工程不要创建在桌面后面的flash programmer 不识别桌面工程)2.新建一个block 文件,并立即save as ,文件名不需要改。

3.Tools -> SOPC Builder ,选好型号并设置CPU的工作时钟(输入时钟)。

4.Processor -> Nios II Processor,创建自己的一个Nios II 核。

Nios II/e 经济型最慢最省空间Nios II/s 标准型标准标准Nios II/f 快速性最快最费空间(如果选择此类,需将cache关闭)选好类型之后,即可直接finish5.程序运行都需要memory,而笔者使用的为核心板上的外部ram,且一般情况下on_chip_memory的大小太小不足以跑中大型Nios系统。

Memories and Memory Controllers -> SDRAM -> SDRAM Controller,将数据线改为16,其余不变。

6.因为我们下载程序的过程是,先在FPGA上烧写一个Nios核,然后通过Nios核将quartus和nios工程一次性烧写到flash中去。

所以我们构造的Nios核必然要包含一个CFI控制器。

Memories and Memory Controllers -> Flash -> EPCS Serial Flash Controller,直接finish。

7.为了让程序便于调试,我们再添加一个JTAG串口。

Interface Protocols -> Serial -> JTAG UART,直接finish。

AS PS JTAG 配置方式的区别AS模式: 烧到FPGA的配置芯片里保存的,FPGA器件每次上电时,作为控制器从配置器件EPCS 主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程;PS模式:EPCS作为控制器件,把FPGA当做存储器,把数据写人到FPGA中,实现对FPGA的编程。

该模式可以实现对FPGA在线可编程;JTAG:直接烧到FPGA里面的,由于是SRAM,断电后要重烧;.pof文件可以通过AS方式下载(保证byteblasterII/usb blaster连接正确);.sof文件或者转换的.jic可以通过JTAG方式下载。

1.FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持 Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone期间处于主动地位,配置期间处于从属地位。

配置数据通过DATA0引脚送入 FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。

在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。

在实用系统中,多数情况下必须由FPGA 主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

第一章:关于工具包DE2工具包提供了使用Altera Cyclone II开发高级数字产品需要的所有模块。

此用户指南能使读者在30分钟内迅速浏览许多参考设计。

本章提供了工具包的关键信息。

工具包内容图1.1给出了DE2的图片。

DE2工具包包括以下部分:✓DE2开发板✓用于FPGA编程和控制的USB电缆✓DE2 实验光盘,包括DE2控制面板,参考设计,软件工具以及用户指南✓Altera Quartus II 5.0 网络光盘和Nios II 5.0 光盘✓附件包一个,内含:铜质支架,螺钉,橡皮脚若干✓装配在主板上的树脂玻璃一片✓9V直流Wall-mount电源图1.1. DE2 工具包组装橡皮脚用户可以使用附件袋中的铜脚,硅片和螺丝按照自己的项目组装合适的支架脚。

在DE2板上为每个6螺洞组装螺丝,铜脚和橡胶片,如图1.2所示。

如果需要额外的保护可以装上树脂玻璃片图1.2 橡皮脚安装方式获得帮助遇到问题可以从下几处获取帮助:发邮件至:support@中国台湾& 中国大陆: +886-3-550-8800韩国& 日本: +82-2-512-7661第二章:DE2开发板这一个章节将带你浏览DE2板上的每个部分及其特性DE2开发板DE2开发板使用了与大批量生产的高端产品(如最高QC标准的高密度PC主板和汽车infotainment系统)相一致的严格设计与布线准则。

主要的设计和布线思路如下所示:仔细安排器件及连接走线。

这种良好的排版可增加制造产量,并简化主板调试流程。

无跳线设计提高鲁棒性。

跳线易出错而且为不随时携带手册的用户带来不便。

部件的选择取决于片上容量。

我们选择了在PC 和DVD播放器中最常用的配置确保这些部件将来能够得到持续供应。

电源和IO口保护设计考虑到了大部分的现场意外情况。

开发板检测按图2.1测试开发板图2.1 DE2开发板组件及接口特性DE2主板为用户提供了用于多媒体开发的多种特性。

1、对于Altera FPGA,含Nios II时需要下载的文件有4种:.sof 文件,.pof 文件,.jic 文件,.elf 文件。

下载文件生成工具下载方式下载存储器是否掉电丢失.sof 文件QuartusII编译生成JTAG FPGA(SRAM )丢失

.pof 文件QuartusII编译生成AS(Active Slave)FLSAH(EPCS64)不会丢失

.jic 文件QuartusII “File|Convert

Programming File”

JTAG FLSAH(EPCS64)不会丢失

.elf 文件Nios II IDE JTAG(调式模式)FPGA(SRAM )丢失

.elf 文件Nios II IDE JTAG(烧写模式)FLSAH(EPCS64)不会丢失

2、通常称.sof 文件和.pof 文件为FPGA“硬件”或“固件”文件,在QuartusII中设计编译产生,源文件格式

有VHDL、Verilog HDL、AHDL、Tcl(一般用于引脚定义)、原理图(一般用于顶层)等;.elf文件为“软件”文件,在Nios II IDE中(新版本为Nios II Software Builder Tools for Eclipse)设计编译产生,源文件为C语言。

3、.jic文件为JTAG间接配置文件(JTAG Indirect Configuration File),使用QuartusII File菜单下Convert Programming File命令将.sof文件转换生成,然后使用QuartusII的Tools菜单下Programmer命令下载到FLASH中(注意:.jic文件下载到FLASH后必须关机重新加电!)如下图所示:

4、 .elf文件不能单独下载,必须与“硬件”.sof文件一起下载才能运行(也可先在QuartusII中下载.sof,再在NiosII IDE或Nios II Software Builder Tools for Eclipse中下载.elf),以QuartusII 11.0版本为例,方法如下:

(1)使用Nios II 11.0 IDE

先点击“开始| 程序| Altera|Nios II EDS 11.0 | Legacy Nios II Tools | NiosII11.0 IDE”(注意:11.0版本的“Legacy Nios II Tools”必须单独下载安装!)启动NiosII11.0 IDE,打开或导入工程,在Nios II IDE 中点击Tools->Flash Programmer…,出现如下图所示的界面:

需要勾选的部分如图中红线框所标注,第一部分是将Nios II中的软件程序写到Flash中,注意还需要加载JDI文件,即点击“Load JDI File”,选择本系统中的JDI文件即可。

第二部分是将FPGA的配置文件一起到Flash中,点击“Browse...”选择Quartus II生成的.sof文件,还需选择将配置文件下载到什么地方,此处还是Flash。

最后一部分勾选的是Validata Nios II system ID before software download,即在

下载软件程序之前要确认系统的ID号,这样每次在QuartusII中修改“硬件”(即.sof文件)或在Nios II IDE 中修改“软件”(即.elf文件)后能报警提示,确保硬件与软件最新版本同步。

没有勾选的那一部分是将其它文件下载到Flash中,比如配置数据文件(Lince5M181 CMOS相机就有!)、汉字字库文件、波形文件等等,将这些文件直接存储到Flash中,只需要读取就可以了。

选择好之后,点击“Apply”,然后点击“Program Flash”,就可以进行Flash的烧写了。

若Nios II IDE的Console中有如下提示信息:

#!/bin/sh

………….

Programmed xxxKB +xxxKB in x.xs (xxxKB/s)

Did not attempt to verify device contents

Leaving target processor paused

则表示Flash烧写成功,关机后重新加电运行即可。

(2)使用Nios II Software Builder Tools for Eclipse(简称Nios II SBT for Eclipse)从Altera SOPC Builder的Nios II菜单中启动,或从“开始| 程序| Altera | Nios II EDS xx.x | …”

启动。

然后按下述方法下载程序:

●选择Nios II菜单项中的Flash Programmer(Ctrl+7),弹出Flash Programmer的设置窗口:

●选择File菜单的New,弹出窗口:

●指定setting.bsp文件,sopc information是自动加载的。

●分别添加 .sof文件(在Quartus工程下)和.elf文件(在Nios工程下)

●点击Start命令,进行转换,默认将在software目录下的bsp文件夹下生成flash和script两

个文件夹,并完成烧写,断电重新加电或复位即可。

5、对于有些FPGA,有时用上述4中的两种方法下载程序到FLASH后,加电无法正常运行,这好像是Altera公司Nios II EDS的bugs,许多用户都遇到过,在Altera forum上有人给出解决方法:

(1) 在硬盘根目录下新建一个文件夹。

例如:D:\jic。

(2) 将Quartus II工程、Nios II工程编译生成的sof、elf都拷贝到此文件夹内;

(3) 按如下格式,新建一个sh文件,此处命名为xxx.sh;(sh文件是bash的批处理文件;类

似于DOS的bat文件)

echo "sof>flash …"; sof2flash --epcs --input=demo.sof --output=sof.flash --quiet

echo "elf>flash …"; elf2flash --epcs --after=sof.flash --input=demo.elf --output=elf.flash

echo "cat flash…"; cat elf.flash >> sof.flash

echo "flash>hex…"; nios2-elf-objcopy --input-target srec --output-target ihex sof.flash sof_elf.hex

echo "del flash …"; rm -f *.flash

(4) 运行“开始| 程序| Altera | Nios II EDS 11.0 | Nios II 11.0 Command Shell”,执行:

cd d:\jic

./xxx.sh

(5) 在Quartus II中使用Convert Programming Files把上述命令生成的sof_elf.hex转换成.jic文件即可,类似上述3,只是把SOF Data换成HEX Data(先Remove后Add),点Generate生成jic,再将jic写入Flash即可。