数字逻辑 第6章

- 格式:ppt

- 大小:3.48 MB

- 文档页数:109

数字逻辑简单课程设计一、教学目标本课程的教学目标是使学生掌握数字逻辑的基本概念和基本方法,培养学生分析和解决数字逻辑问题的能力。

具体来说,知识目标包括:掌握数字逻辑的基本概念,如逻辑门、逻辑电路、逻辑函数等;了解数字逻辑的基本运算,如与、或、非、异或等;理解数字逻辑电路的设计方法和步骤。

技能目标包括:能够运用数字逻辑的基本概念和运算方法分析和解决简单的数字逻辑问题;能够设计简单的数字逻辑电路,并进行仿真实验。

情感态度价值观目标包括:培养学生的团队合作意识和科学探究精神,使学生认识到数字逻辑在现代科技领域中的重要地位和作用。

二、教学内容本课程的教学内容主要包括数字逻辑的基本概念、基本运算和电路设计方法。

具体来说,教学大纲安排如下:第1章:数字逻辑概述,介绍数字逻辑的基本概念和特点,理解数字逻辑与模拟逻辑的区别。

第2章:逻辑门,学习逻辑门的种类和性质,掌握逻辑门的符号表示和真值表。

第3章:逻辑电路,了解逻辑电路的组成和功能,学习逻辑电路的设计方法和步骤。

第4章:逻辑函数,掌握逻辑函数的定义和性质,学习逻辑函数的化简方法。

第5章:数字逻辑电路实例,分析常见的数字逻辑电路,如加法器、译码器、触发器等。

第6章:数字逻辑电路仿真实验,通过仿真软件进行数字逻辑电路的设计和实验。

三、教学方法为了实现本课程的教学目标,我们将采用多种教学方法,如讲授法、讨论法、案例分析法和实验法等。

在教学过程中,我们将注重理论与实践相结合,通过生动的案例分析和实验操作,激发学生的学习兴趣和主动性。

同时,我们将鼓励学生积极参与课堂讨论,培养学生的团队合作意识和科学探究精神。

四、教学资源为了保证本课程的顺利进行,我们将准备丰富的教学资源,包括教材、参考书、多媒体资料和实验设备等。

教材方面,我们将采用《数字逻辑》作为主教材,同时推荐《数字逻辑电路》等参考书供学生自主学习。

多媒体资料方面,我们将收集与课程相关的视频、动画和图片等,以直观地展示逻辑电路的工作原理和设计过程。

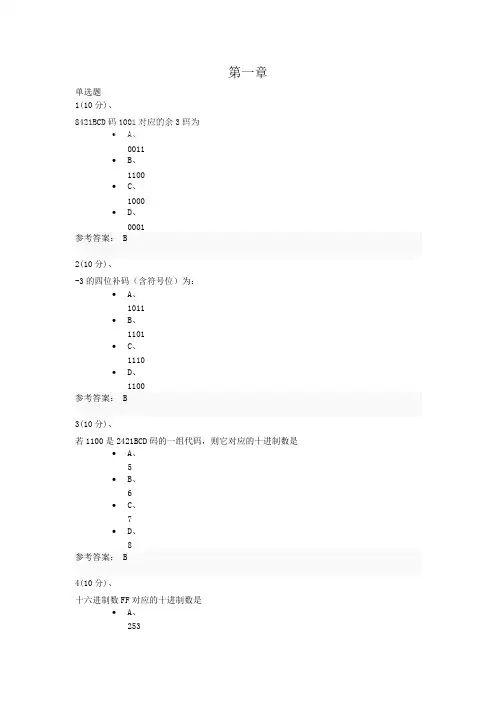

第一章单选题1(10分)、8421BCD码1001对应的余3码为∙A、0011∙B、1100∙C、1000∙D、0001参考答案: B2(10分)、-3的四位补码(含符号位)为:∙A、1011∙B、1101∙C、1110∙D、1100参考答案: B3(10分)、若1100是2421BCD码的一组代码,则它对应的十进制数是∙A、5∙B、6∙C、7∙D、8参考答案: B4(10分)、十六进制数FF对应的十进制数是∙A、253∙B、254∙C、255∙D、256参考答案: C5(10分)、二进制数111011.101转换为十进制数为:∙A、58.625∙B、57.625∙C、59.625∙D、60.125参考答案: C6(10分)、设二进制变量A=0F0H,B=10101111B,则A和B与运算的结果是∙A、10100000∙B、11111111∙C、10101111∙D、11110000参考答案: A7(10分)、-3的四位原码为:∙A、1111∙B、1010∙C、1011∙D、1101参考答案: C第二章单选题1(6分)、逻辑函数L=AB+AC的真值表中,使得L=1的输入变量组合有多少种?摩根定理参考答案: A5(6分)、若1100是2421BCD码的一组代码,则它对应的十进制数是∙A、5∙B、6∙C、7∙D、8参考答案: B6(6分)、存在多少组取值使最小项ABCD的值为0∙A、1∙B、16∙C、3∙D、7参考答案: A7(6分)、奇数个1进行异或运算的结果为:∙A、1∙B、∙C、不确定∙D、还是不确定参考答案: A8(6分)、“或非”门中的某一输入值为“0”,那么它的输出值是∙A、∙B、要取决于其它输入端的值∙C、为“1”∙D、取决于正逻辑还是负逻辑参考答案: B9(6分)、与十进制数12.5等值的二进制数为:∙A、1100.10∙B、1011.11∙C、1100.11∙D、1100.01参考答案: A10(6分)、设二进制变量A=0F0H,B=10101111B,则A和B与运算的结果是∙A、10100000∙B、11111111∙C、10101111∙D、11110000参考答案: A11(6分)、二进制数111011.101转换为十进制数为:∙A、58.625∙B、57.625∙C、59.625∙D、参考答案: C12(6分)、四变量逻辑函数Y(ABCD)的最小项m8为( )∙A、ABCD'∙B、A'BCD'∙C、AB'C'D'∙D、ABCD参考答案: C13(6分)、逻辑函数L=AB+CD的真值表中,L=1的状态有多少个?∙A、2∙B、4∙C、6∙D、7参考答案: D14(6分)、十六进制数FF对应的十进制数是∙A、253∙B、254∙C、255∙D、256参考答案: C15(6分)、-3的四位补码(含符号位)为:∙A、1011∙B、1101∙C、1110∙D、1100参考答案: B判断题16(1分)、全体最大项的和为0,任意两个最小项的乘积为1。

数字逻辑技术试卷-第6章一、填空题1.根据制作工艺的不同,集成555定时电路可分为 TTL 型 和 CMOS 型 两大类。

2.施密特触发器的固有性能指标是 V T+ 、 V T - 和 ΔV T 。

3.CMOS 精密单稳态触发器中,定时元件和可在 较大 范围内选择,定时时间t w 的范围为:取值 2kΩ~30kΩ ,取值 10pF ~10μF 。

4.555定时电路由 分压器 、 比较器 、 RS 触发器 、 放电开关管 以及 输出缓冲级 几部分组成。

5.由555构成的单稳态触发器对输入触发脉冲的要求是: t re <t w 。

6.TTL 型555定时电路中的C 1和C 2是 开环的电压比较器 ,C 1同相端的参考电压是 2V CC /3 ;C 2反相端的参考电压是 V CC /3 。

定时电路构成的多谐振荡器,其振荡周期为 T=0.7(R 1+2R 2)C ,输出脉冲宽8.555定时器可以构成施密特触发器,施密特触发器具有 回差 特性,主要用于脉冲波形的 变换 和 脉冲整形 。

555定时器还可以用作多谐振荡器和 单 稳态触发器。

9.555定时电路的最基本应用电路有: 单稳态触发器 、 施密特触发器 和多谐振荡器。

10.555定时电路构成的应用电路中,当电压控制端管脚5不用时,通常对地接 一个0.01μF 的电容 ,其作用是防止 干扰 。

二、判断题1.用555定时电路构成的多谐振荡器的占空比不能调节。

( 错 )2.对555定时器的管脚5外加控制电压后也不能改变其基准电压值。

( 错 )3.用555定时器构成的施密特触发器,其回差电压不可调节。

( 错 )4.单稳态触发器的暂稳态维持时间的长短只取决于电路本身的参数。

( 对 )5.单稳态触发器只有一个稳态,一个暂稳态。

( 对 ) 6. 555电路的输出只能出现两个状态稳定的逻辑电平之一。

( 对 ) 7.施密特触发器的作用就是利用其回差特性稳定电路。

数字逻辑第四版(欧阳星明著)课后习题答案下载数字逻辑第四版(欧阳星明著)课后答案下载第1章基础概念11.1概述11.2基础知识21.2.1脉冲信号21.2.2半导体的导电特性41.2.3二极管开关特性81.2.4三极管开关特性101.2.5三极管3种连接方法131.3逻辑门电路141.3.1DTL门电路151.3.2TTL门电路161.3.3CML门电路181.4逻辑代数与基本逻辑运算201.4.1析取联结词与正“或”门电路201.4.2合取联结词与正“与”门电路211.4.3否定联结词与“非”门电路221.4.4复合逻辑门电路221.4.5双条件联结词与“同或”电路241.4.6不可兼或联结词与“异或”电路241.5触发器基本概念与分类251.5.1触发器与时钟271.5.2基本RS触发器271.5.3可控RS触发器291.5.4主从式JK触发器311.5.5D型触发器341.5.6T型触发器37习题38第2章数字编码与逻辑代数392.1数字系统中的编码表示392.1.1原码、补码、反码412.1.2原码、反码、补码的运算举例472.1.3基于计算性质的几种常用二-十进制编码48 2.1.4基于传输性质的几种可靠性编码512.2逻辑代数基础与逻辑函数化简572.2.1逻辑代数的基本定理和规则572.2.2逻辑函数及逻辑函数的表示方式592.2.3逻辑函数的标准形式622.2.4利用基本定理简化逻辑函数662.2.5利用卡诺图简化逻辑函数68习题74第3章数字系统基本概念763.1数字系统模型概述763.1.1组合逻辑模型773.1.2时序逻辑模型773.2组合逻辑模型结构的数字系统分析与设计81 3.2.1组合逻辑功能部件分析813.2.2组合逻辑功能部件设计853.3时序逻辑模型下的数字系统分析与设计923.3.1同步与异步933.3.2同步数字系统功能部件分析943.3.3同步数字系统功能部件设计993.3.4异步数字系统分析与设计1143.4基于中规模集成电路(MSI)的数字系统设计1263.4.1中规模集成电路设计方法1263.4.2中规模集成电路设计举例127习题138第4章可编程逻辑器件1424.1可编程逻辑器件(PLD)演变1424.1.1可编程逻辑器件(PLD)1444.1.2可编程只读存储器(PROM)1464.1.3现场可编程逻辑阵列(FPLA)1484.1.4可编程阵列逻辑(PAL)1494.1.5通用阵列逻辑(GAL)1524.2可编程器件设计1604.2.1可编程器件开发工具演变1604.2.2可编程器件设计过程与举例1604.3两种常用的HDPLD可编程逻辑器件164 4.3.1按集成度分类的可编程逻辑器件164 4.3.2CPLD可编程器件1654.3.3FPGA可编程器件169习题173第5章VHDL基础1755.1VHDL简介1755.2VHDL程序结构1765.2.1实体1765.2.2结构体1805.2.3程序包1835.2.4库1845.2.5配置1865.2.6VHDL子程序1875.3VHDL中结构体的描述方式190 5.3.1结构体的行为描述方式190 5.3.2结构体的数据流描述方式192 5.3.3结构体的结构描述方式192 5.4VHDL要素1955.4.1VHDL文字规则1955.4.2VHDL中的数据对象1965.4.3VHDL中的数据类型1975.4.4VHDL的运算操作符2015.4.5VHDL的预定义属性2035.5VHDL的顺序描述语句2055.5.1wait等待语句2055.5.2赋值语句2065.5.3转向控制语句2075.5.4空语句2125.6VHDL的并行描述语句2125.6.1并行信号赋值语句2125.6.2块语句2175.6.3进程语句2175.6.4生成语句2195.6.5元件例化语句2215.6.6时间延迟语句222习题223第6章数字系统功能模块设计2556.1数字系统功能模块2256.1.1功能模块概念2256.1.2功能模块外特性及设计过程2266.2基于组合逻辑模型下的VHDL设计226 6.2.1基本逻辑门电路设计2266.2.2比较器设计2296.2.3代码转换器设计2316.2.4多路选择器与多路分配器设计2326.2.5运算类功能部件设计2336.2.6译码器设计2376.2.7总线隔离器设计2386.3基于时序逻辑模型下的VHDL设计2406.3.1寄存器设计2406.3.2计数器设计2426.3.3并/串转换器设计2456.3.4串/并转换器设计2466.3.5七段数字显示器(LED)原理分析与设计247 6.4复杂数字系统设计举例2506.4.1高速传输通道设计2506.4.2多处理机共享数据保护锁设计257习题265第7章系统集成2667.1系统集成基础知识2667.1.1系统集成概念2667.1.2系统层次结构模式2687.1.3系统集成步骤2697.2系统集成规范2717.2.1基于总线方式的互连结构2717.2.2路由协议2767.2.3系统安全规范与防御2817.2.4时间同步2837.3数字系统的非功能设计2867.3.1数字系统中信号传输竞争与险象2867.3.2故障注入2887.3.3数字系统测试2907.3.4低能耗系统与多时钟技术292习题295数字逻辑第四版(欧阳星明著):内容提要点击此处下载数字逻辑第四版(欧阳星明著)课后答案数字逻辑第四版(欧阳星明著):目录本书从理论基础和实践出发,对数字系统的基础结构和现代设计方法与设计手段进行了深入浅出的论述,并选取作者在实际工程应用中的一些相关实例,来举例解释数字系统的设计方案。

第一章 数制与编码1、二、八、十、十六进制数的构成特点及相互转换;二转BCD :二B 到十D 到BCD ,二B 到十六H ,二B 到八O2、有符号数的编码;代码的最高位为符号位,1为负,0为正3、各种进制如何用BCD 码表示;4、有权码和无权码有哪些?BCD 码的分类:有权码:8421,5421,2421 无权码:余3码,BCD Gray 码 例:1、〔1100110〕B =〔0001 0000 0010〕8421BCD =〔102〕D =〔 66 〕H =〔146〕O〔178〕10=〔10110010〕2=〔0001 0111 1000 〕8421BCD =〔B2 〕16=〔 262〕8 2、将数1101.11B 转换为十六进制数为〔 A 〕A. D.C HB. 15.3HC. 12.E HD. 21.3H 3、在以下一组数中,最大数是〔 A 〕。

A.(258)D1 0000 0010B.(100000001 )B 257C.(103)H 0001 0000 0011259D.(001001010111 )8421BCD 2574、假设用8位字长来表示,〔-62〕D =( 1011 1110)原5、属于无权码的是〔B 〕A.8421 码B.余3 码 和 BCD Gray 的码C.2421 码D.自然二进制码 6、BCD 码是一种人为选定的0~9十个数字的代码,可以有许多种。

〔√〕 第二章 逻辑代数根底1、根本逻辑运算和复合逻辑运算的运算规律、逻辑符号;F=AB 与 逻辑乘 F=A+B 或 逻辑加F=A 非 逻辑反2、逻辑代数的根本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简〔有约束的和无约束的〕。

例:1、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于〔 A 〕逻辑关系。

A 、与B 、或C 、非 2、数字电路中使用的数制是〔 A 〕。

习题一1.1 把下列不同进制数写成按权展开式:⑴(4517.239)10= 4×103+5×102+1×101+7×100+2×10-1+3×10-2+9×10-3⑵(10110.0101)2=1×24+0×23+1×22+1×21+0×20+0×2-1+1×2-2+0×2-3+1×2-4⑶(325.744)8=3×82+2×81+5×80+7×8-1+4×8-2+4×8-3⑷(785.4AF)16=7×162+8×161+5×160+4×16-1+A×16-2+F×16-31.2 完成下列二进制表达式的运算:1.3 将下列二进制数转换成十进制数、八进制数和十六进制数:⑴(1110101)2=(165)8=(75)16=7×16+5=(117)10⑵(0.110101)2=(0.65)8=(0.D4)16=13×16-1+4×16-2=(0.828125)10⑶(10111.01)2=(27.2)8=(17.4)16=1×16+7+4×16-1=(23.25)101.4 将下列十进制数转换成二进制数、八进制数和十六进制数,精确到小数点后5位:⑴(29)10=(1D)16=(11101)2=(35)8⑵(0.207)10=(0.34FDF)16=(0.001101)2=(0.15176)8⑶(33.333)10=(21.553F7)16=(100001.010101)2=(41.25237)81.5 如何判断一个二进制正整数B=b6b5b4b3b2b1b0能否被(4)10整除?解: 一个二进制正整数被(2)10除时,小数点向左移动一位, 被(4)10除时,小数点向左移动两位,能被整除时,应无余数,故当b1=0和b0=0时, 二进制正整数B=b6b5b4b3b2b1b0能否被(4)10整除.1.6 写出下列各数的原码、反码和补码:⑴0.1011[0.1011]原=0.1011; [0.1011]反=0.1011; [0.1011]补=0.1011⑵0.0000[0.000]原=0.0000; [0.0000]反=0.0000; [0.0000]补=0.0000⑶-10110[-10110]原=110110; [-10110]反=101001; [-10110]补=1010101.7 已知[N]补=1.0110,求[N]原,[N]反和N.解:由[N]补=1.0110得: [N]反=[N]补-1=1.0101, [N]原=1.1010,N=-0.10101.8 用原码、反码和补码完成如下运算:⑴0000101-0011010[0000101-0011010]原=10010101;∴0000101-0011010=-0010101。

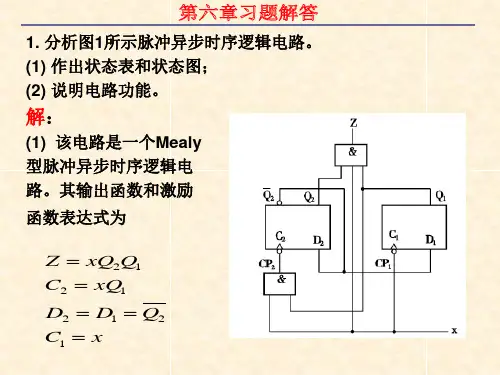

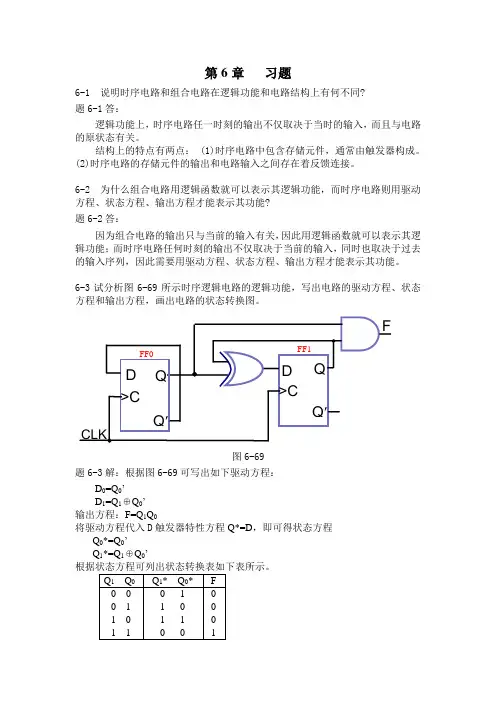

第6章习题参考解答6-3画出74x27三输入或非门的德摩根等效符号。

解:图形如下浒"3 .............. ::BAWD5 ........ :OH6-10在图X6.9电路中采用74AHCT00替换74LS00,利用表6-2的信息,确定从输入端到输出端的最大吋间延迟。

解:该图中从输入到输出需要经过6个NAND2;每个NAND2 (74AHCT00)的最大时间延迟为9 ns;所以从输入端到输出端的最大时间延迟为:54 nso6-31 BUT门的可能定义是:“如果Al和Bl为1,但A2或B2为0,则Y1为1; Y2 的定义是对称的。

”写出真值表并找出BUT门输出的最小“积之和”表达式。

画出用反相门电路实现该表达式的逻辑图,假设只冇未取反的输入可用。

你可以从74x00、04、10、20、30组件中选用门电路。

解:真值表如下利用卡诺图进行化简,可以得到最小积Z 和表达式为Y1=A1B1A2,+A1B1B2, Y2=A 1' • A2 B2+B 1' A2 B2Y2采用74x04得到各反相器 采用74x10得到3输入与非 采用74x00得到2输入与非 实现的逻辑图如下:6-32做出练习题6-31定义的BUT 门的CMOS 门级设计,可以采用各种反相门逻辑的 组合(不一定是二级“积Z 和”),要求使用的品体管数目最少,写出输出表达式并画出 逻辑图。

解:CMOS 反相门的晶体管用量为基本单元输入端数量的2倍;对6・31的函数式进行变换:yi = A1B1-A2'+41 ・ Bl • B2'=(41 • Bl ) •(A2'+B2‘) =(A1 ・ Bl )(A2 • B2) Y2 = A2-B2-AY+A2- B2 • BV=⑷.B2)•⑷+B1) =(A2 • B2)-(A1 • Bl )利用圈■圈逻辑设计,可以得到下列结构:Y\ = ((41 • B1)+(A2 • B2『) Y2 = ((A2 • B2),+(A1 • Bl ))HANDS74X0011H AN Di-Y13(A2 B2 A1 丁 (A2 B2 时“翔此 .....dz >Y2 674X10HANDS 5HANDS5^133 2./1U3㈣D36(A1 EM A2)1此结构晶体管用量为20只(原设计屮晶体管用量为40只)6-20采用一片74x138或74x 139二进制译码器和NAND 门,实现下列单输出或多数 出逻辑函数。

第6章题解:6.1 试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余3BCD 码计数器。

题6.1 解:余3BCD 码计数器计数规则为:0011→0100→…→1100→0011→…,由于采用异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1所示。

CLK13图 题解6.1题6.2 试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2 解:6.3 试用D 触发器和门电路设计一个同步4位格雷码计数器。

题6.3 解:根据格雷码计数规则,Q 3 Q 2Q 1 Q 0计数器的状态方程和驱动方程为:1333031210122202131011110320320100321321321321n n n n n n n nn n n n n n n n n n n n n n n n n n n n n n n n n n n n n n Q D Q Q Q Q Q Q Q Q D Q Q Q Q Q Q Q QD Q Q Q Q Q Q Q QQ D Q Q Q Q Q Q Q Q Q Q Q Q ++++==++==++==++==+++按方程画出电路图即可,图略。

题 6.4 解:反馈值为1010。

十一进制计数器6.5 试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题 6.5 解:可采取同步清零法实现。

电路如图题解6.5所示。

题 6.6 解: 当M=1时:六进制计数器 当M=0时:八进制计数器图题解6.5图题解6.56.7 试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变量M=0时,电路为8421BCD 码十进制计数器,M=1时电路为5421BCD 码十进制计数器,5421BCD 码计数器状态图如下图P6.7所示。

74163功能表如表6.4所示。

图 P 6.7Q 3Q 2Q 1Q 01010题6.7 解:实现8421BCD 码计数器,可采取同步清零法;5421BCD 码计数器可采取置数法实现,分析5421BCD 码计数规则可知,当21Q =时需置数,应置入的数为:32103000D D D D Q =。