第3章存储器及存储系统

- 格式:ppt

- 大小:3.43 MB

- 文档页数:198

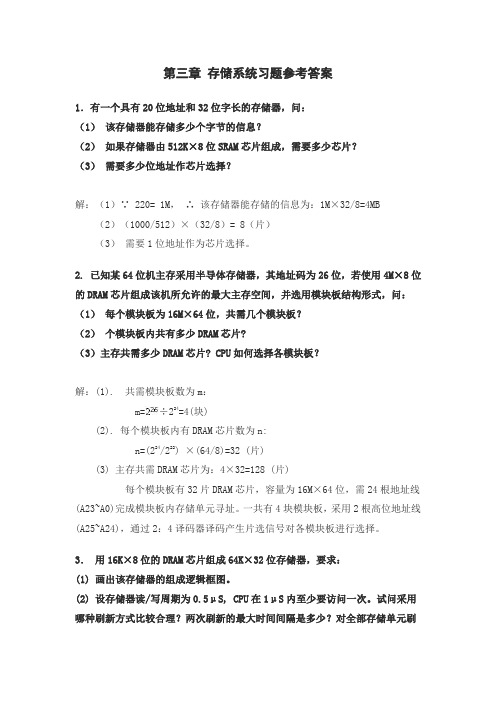

第三章存储系统习题参考答案1.有一个具有20位地址和32位字长的存储器,问:(1)该存储器能存储多少个字节的信息?(2)如果存储器由512K×8位SRAM芯片组成,需要多少芯片?(3)需要多少位地址作芯片选择?解:(1)∵ 220= 1M,∴ 该存储器能存储的信息为:1M×32/8=4MB (2)(1000/512)×(32/8)= 8(片)(3)需要1位地址作为芯片选择。

2. 已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M×8位的DRAM芯片组成该机所允许的最大主存空间,并选用模块板结构形式,问:(1)每个模块板为16M×64位,共需几个模块板?(2)个模块板内共有多少DRAM芯片?(3)主存共需多少DRAM芯片? CPU如何选择各模块板?解:(1). 共需模块板数为m:m=÷224=4(块)(2). 每个模块板内有DRAM芯片数为n:n=(224/222) ×(64/8)=32 (片)(3) 主存共需DRAM芯片为:4×32=128 (片)每个模块板有32片DRAM芯片,容量为16M×64位,需24根地址线(A23~A0)完成模块板内存储单元寻址。

一共有4块模块板,采用2根高位地址线(A25~A24),通过2:4译码器译码产生片选信号对各模块板进行选择。

3.用16K×8位的DRAM芯片组成64K×32位存储器,要求:(1) 画出该存储器的组成逻辑框图。

(2) 设存储器读/写周期为0.5μS, CPU在1μS内至少要访问一次。

试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少?解:(1)组成64K×32位存储器需存储芯片数为N=(64K/16K)×(32位/8位)=16(片)每4片组成16K×32位的存储区,有A13-A0作为片内地址,用A15 A14经2:4译码器产生片选信号,逻辑框图如下所示:(2)依题意,采用异步刷新方式较合理,可满足CPU在1μS内至少访问内存一次的要求。

第3章存储器系统题库和答案第3章存储器系统一.选择题1.计算机工作中只读不写的存储器是( )。

(A) DRAM (B) ROM (C) SRAM (D) EEPROM2.下面关于主存储器(也称为内存)的叙述中,不正确的是( )。

(A) 当前正在执行的指令与数据都必须存放在主存储器内,否则处理器不能进行处理(B) 存储器的读、写操作,一次仅读出或写入一个字节 (C) 字节是主存储器中信息的基本编址单位(D) 从程序设计的角度来看,cache(高速缓存)也是主存储器3.CPU对存储器或I/O端口完成一次读/写操作所需的时间称为一个( )周期。

(A) 指令 (B) 总线 (C) 时钟 (D) 读写 4.存取周期是指( )。

(A)存储器的写入时间 (B) 存储器的读出时间(C) 存储器进行连续写操作允许的最短时间间隔 (D)存储器进行连续读/写操作允许的最短时间3间隔5.下面的说法中,( )是正确的。

(A) EPROM是不能改写的 (B) EPROM是可改写的,所以也是一种读写存储器(C) EPROM是可改写的,但它不能作为读写存储器 (D) EPROM只能改写一次 6.主存和CPU之间增加高速缓存的目的是( )。

(A) 解决CPU和主存间的速度匹配问题 (B) 扩大主存容量(C) 既扩大主存容量,又提高存取速度 (D) 增强CPU的运算能力 7.采用虚拟存储器的目的是( )。

(A) 提高主存速度 (B) 扩大外存的容量 (C) 扩大内存的寻址空间 (D) 提高外存的速度 8.某数据段位于以70000起始的存储区,若该段的长度为64KB,其末地址是( )。

(A) 70FFFH (B) 80000H (C) 7FFFFH (D) 8FFFFH9.微机系统中的存储器可分为四级,其中存储容量最大的是( )。

(A) 内存 (B) 内部寄存器 (C) 高速缓冲存储器 (D) 外存10.下面的说法中,( )是正确的。

计算机系统结构-第三章(习题解答)1. 什么是存储系统?对于一个由两个存储器M 1和M 2构成的存储系统,假设M1的命中率为h ,两个存储器的存储容量分别为s 1和s 2,存取时间分别为t 1和t 2,每千字节的成本分别为c 1和c 2。

⑴ 在什么条件下,整个存储系统的每千字节平均成本会接近于c 2? ⑵ 该存储系统的等效存取时间t a 是多少?⑶ 假设两层存储器的速度比r=t 2/t 1,并令e=t 1/t a 为存储系统的访问效率。

试以r 和命中率h 来表示访问效率e 。

⑷ 如果r=100,为使访问效率e>0.95,要求命中率h 是多少?⑸ 对于⑷中的命中率实际上很难达到,假设实际的命中率只能达到0.96。

现在采用一种缓冲技术来解决这个问题。

当访问M 1不命中时,把包括被访问数据在内的一个数据块都从M 2取到M 1中,并假设被取到M 1中的每个数据平均可以被重复访问5次。

请设计缓冲深度(即每次从M 2取到M 1中的数据块的大小)。

答:⑴ 整个存储系统的每千字节平均成本为:12s 1s 2c 2s 1s 1c 2s 1s 2s 2c 1s 1c c ++⨯=+⨯+⨯=不难看出:当s1/s2非常小的时候,上式的值约等于c2。

即:s2>>s1时,整个存储器系统的每千字节平均成本会接近于c2。

⑵ 存储系统的等效存取时间t a 为:2t )h 1(1t h t a ⨯-+⨯=⑶r)h 1(h 1t )h 1(t h t t t e 211a 1⨯-+=⨯-+⨯==⑷ 将数值代入上式可以算得:h>99.95% ⑸通过缓冲的方法,我们需要将命中率从0.96提高到0.9995。

假设对存储器的访问次数为5,缓冲块的大小为m 。

那么,不命中率减小到原来的1/5m ,列出等式有:m596.0119995.0--= 解这个方程得:m=16,即要达到⑷中的访问效率,缓冲的深度应该至少是16(个数据单位)。